## Vol. 21, No. 2, pp. 41-50 (2012. 6)

# 인라인 EFEM 클러스터 장비 아키텍처의 모델링 및 분석 사례 연구

한용희<sup>1†</sup>

# A Case Study for Modeling and Simulation Analysis of the In-Line EFEM Cluster Tool Architecture

Yong-Hee Han

#### ABSTRACT

In this study we first explain details of the semiconductor manufacturing processes and cluster tools. Then we discuss the problems in current fab layout and cluster tool architecture. As a solution to these problems, we propose the ILE (In-Line EFEM) architecture in which wafer movements are conducted through interconnected EFEMs (Equipment Front End Modules) instead of AMHS (Automated Material Handling System). Then we model the pilot ILE system using discrete event simulation and analyze the cycle time. Finally we compare three different scenarios of equipment layout in the ILE system in terms of cycle time.

Key words: In-line EFEM, Fab layout, Cluster tool, Semiconductor, Simulation

#### 요 약

본 연구에서는 반도체 제조공정 및 클러스터 장비에 대한 상세히 설명하고 현 팹 레이아웃 및 클러스터 장비 아키텍처상의 문제점을 제시하였다. 또한 현 아키텍처상의 대안으로서 클러스터 장비간의 웨이퍼 이동이 상호 연결된 인라인 EFEM (Equipment Front End Module) 을 통해 이루어지는 ILE (In-Line EFEM) 아키텍처의 개념을 제시하였다. 마지막으로 해당 아키텍처를 실제 적용하여 구현된 파일럿 시스템을 시뮬레이션 을 통해 사이클 타임 관점에서 비교 분석하였다.

주요어 : 인라인 EFEM, 팹 레이아웃, 장비 아키텍처, 클러스터 장비, 반도체, 시뮬레이션

# 1. 서 론

#### 1.1. 반도체 제조공정 및 클러스터 장비 개요

2011년 International Technology Roadmap for Semiconductors<sup>[9]</sup>의 공장 운영 항목에 의하면 반도체 제 조업체에 대한 제조 사이클 타임 감소에 대한 압력이 점 점 증가하고 있다. 반도체 생산 라인은 규모나 비용 면에 서 일반 생산 라인 대비 매우 방대하며, 이러한 생산 라인 의 레이아웃이나 장비 아키텍처상의 변화는 반도체 생산 업체에 매우 큰 영향을 미치는 관계로 실제 라인 셋업 전 시뮬레이션 모델이나 페트리넷 등의 수리적 모델을 사용 하여 결과를 예측하고 분석하는 작업이 필수적이다.

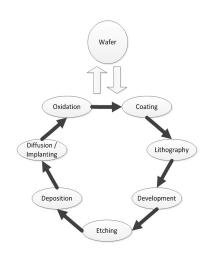

반도체 제조공정은 크게 웨이퍼 제조공정과 조립공정 으로 구성되어 있다. 팹에서 이루어지는 웨이퍼 제조공정 에서는 일련의 공정 스텝의 반복에 의해 최대 수십 층에 달하는 다수의 회로층이 적층되며, 그림 1과 같이 한 층 의 회로층의 생성에는 일반적으로 웨이퍼 표면의 산화막 생성(Oxidation), 웨이퍼 표면에 감광물질 도포(Coating), 광원을 이용한 회로 이미지의 노광(Lithography), 회로 이미지의 현상(Development), 노광되지 않은 감광물질 및 산화막 식각(Etching), 화학약품의 증착(Deposition), 화학약품의 확산(Diffusion) 및 침투(Implanting) 등으로 구성된 일련의 공정 스텝(대부분은 화학 공정) 이 필요하 다. 특정 웨이퍼에 한 회로층의 형성이 완료되면 해당 웨 이퍼는 다음 회로층의 형성을 위해 제조라인에 재투입된다.

주 저 자:한용희 교신저자 : 한용희 E-mail; amade@ssu.ac.kr

<sup>\*</sup>이 연구는 2012년도 숭실대학교 교내연구비 지원에 의한 연구임

접수일(2012년 3월 5일), 심사일(1차 : 2012년 5월 30일), 게재 확정일(2012년 5월 30일)

<sup>&</sup>lt;sup>1)</sup> 숭실대학교 벤처중소기업학과

그림 1. 반도체 회로층 생성 공정 스텝

생산되는 제품의 종류 및 숫자에 따라 팹은 다량 소품 종(low-mix) 팹과 소량 다품종(high-mix) 팹으로 구분할 수 있다. 다량 소품종 팹의 경우 대부분 DRAM과 NAND Flash 등의 메모리 반도체나 CPU 제품을 생산하며 소량 다품종 팹의 경우 대부분 파운드리 등의 주문생산형 제품 이나 아나로그 반도체 제품을 생산한다. 팹내에서 웨이퍼 로트가 준수해야 하는 공정 스텝 순서를 프로세스 흐름이 라 부르며 다량 소품종 팹(~수십 가지)에 비해 소량 다품 종 팹(~수백 가지)에 더 많은 종류의 프로세스 흐름이 존 재한다. 각각의 프로세스 흐름은 수백개의 공정 스텝 및 장비들로 구성되며, 동일한 회로층을 반복하여 적층해야 하는 반도체 제조공정의 특성상 하나의 웨이퍼 로트는 각 장비 그룹을 반복적으로 거쳐야 하므로 반도체 공정은 재 진입 플로우 샵(re-entrant flow shop) 이라 할 수 있다. 웨이퍼의 장비간 이동은 이동의 편의성 및 웨이퍼 오염의 최소화를 위해 FOUP(Front Opening Unified Pod) 이라 부르는 웨이퍼 카세트에 25매 단위로 적재되어 이루어진다.

반도체 제조공정중 식각 공정, 증착 공정 등의 FOUP 내 웨이퍼의 화학 공정 처리시 기존에는 대부분 대형의 공정 챔버(process chamber)에서 복수개의 웨이퍼들을 대상으로 공정을 동시 진행하는 배치 방식을 사용하였다. 하지만 웨이퍼 크기가 200 mm에서 300 mm로 증가하고 지속적으로 반도체 회로 선폭이 축소되면서 화학 공정 진행시 요구되는 품질 수준이 지속적으로 높아짐에 따라 배치 방식으로는 요구되는 품질 관리 수준만큼 챔버 내의 모든 웨이퍼 표면에 균일한 화학적 반응을 일으키기가 매 우 어려워지게 되었다. 따라서 각 웨이퍼별로 공정을 진 행하는 방식인 매엽식 웨이퍼 가공 방식(SWP, single wafer processing) 이 대부분의 반도체 공정에 널리 확산 되었다. SWP 적용시 발생하는 공정 챔버 간의 과도한 웨 이퍼 이동량을 감소시키고 웨이퍼의 오염을 최소화하기 위해 여러 대안이 제시되었으며, 이중 복수의 가공 챔버 와 하나의 웨이퍼 이동 로봇을 외부와 격리된 환경 하에 통합한 시스템인 클러스터 장비와 복수의 가공 챔버와 복 수의 이동 로봇이 통합된 시스템인 트랙 장비 혹은 트랙 시스템이 가장 널리 쓰이고 있다. 클러스터 장비는 기존 의 배치 방식에 비해 공정 제어가 용이하고 자동화된 장 비에 의한 자동화 공정을 구현함으로써 많은 단계의 공정 에서 작업자의 간섭을 줄일 수 있으며 다양한 요구 조건 을 가지는 웨이퍼 가공이 가능하다. 또한 클러스터 장비 내 외부와 격리된 환경(mini-environment)에서는 라인 청 정도 관리가 용이해지며 웨이퍼 오염 가능성이 낮고 대다 수의 공정이 이송장치와 함께 하나의 장비에 통합되어 있 기 때문에 값비싼 팹내 작업 공간 활용도를 크게 향상시 킬 수 있다<sup>[6,8]</sup>. 클러스터 장비는 고객인 반도체 제조업체 의 요구사항에 맞춰 장비 제조업체에 의해 주문 제작되어 납품되거나 다수의 장비업체로부터 납품받은 모듈들을 이용하여 반도체 제조업체에 의해 직접 제작되며[1], 클 러스터 장비내 각 모듈은 모듈 제어기(MC, Module Controller)에 의해 제어된다. 클러스터 장비 전체 시스템 을 제어하는 클러스터 장비 제어기(CTC, Cluster Tool Controller)는 이들 MC들을 제어하며, CTC 및 MC는 일 반적으로 산업용 PC에 기반하여 동작하는 소프트웨어 및 하드웨어 애플리케이션이다.

그림 2와 같이 일반적으로 클러스터 장비는 팹내 물류 시스템과 장비간의 FOUP 이동을 담당하는 LP(Load Port), EFEM, LL(Load Lock), 장비 내 개별 웨이퍼의 이동을 담당하는 진공 로봇, 개별 공정을 수행하는 복수개의 공 정 모듈 등으로 구성되어 있다. 이 중 EFEM은 LP에 위 치한 FOUP의 개별 웨이퍼를 LL에 공급하는 공정 장비 의 표준 인터페이스 모듈로, 다관절 대기압 로봇을 이용 해 로봇이 고정된 상태에서 로봇 팔을 좌우로 이동해 카 세트 내의 웨이퍼를 이송하는 기능을 수행한다<sup>[5]</sup>. 따라서 EFEM은 대부분의 반도체 공정 장비에 널리 사용되며 장 비의 생산성에 큰 영향을 미친다<sup>[13]</sup>. AMHS(Automated Material Handling System) 가 공정을 진행할 웨이퍼들 이 들어있는 FOUP을 LP에 적재하면 EFEM내 대기압 로 봇이 FOUP내 웨이퍼를 하나씩 LL에 이송한다. 적재가 완료되면 LL은 펌핑(pumping)을 통해 대기압에서 진공 상태로 변하고 펌핑이 완료되면 진공 로봇에 의해 지정된 공정 모듈에 이동된다. 공정이 완료된 웨이퍼는 타 공정

**그림 2.** 클러스터 장비의 구성<sup>[12]</sup>

모듈 혹은 상기 순서의 역순(공정 모듈 → 진공 로봇 → LL → 벤팅(venting, 진공에서 대기압 상태로 변화) → EFEM  $\rightarrow$  LP)에 의해 LP로 이동된다.

팹내 장비간 FOUP 운반은 웨이퍼 크기가 300 mm로 증가하면서 인력에 의한 이동이 곤란해짐에 따라 거의 대 부분 OHT(Overhead Transport) 및 OHS(Overhead Shuttle) 를 사용한 AMHS로 바뀌었다<sup>[4]</sup>. AMHS는 특성상 이동 경로와 이동 수단의 수량이 제한되는 관계로 처리 용량 및 유연성이 제한적이다. 따라서 AMHS에는 스토커 등의 대기 장소가 반드시 필요하다. 스토커가 각 베이별로 위 치할 경우 팹내 작업 공간 활용도가 감소하고 FOUP의 장비간 이동시 베이를 거치는 경우가 많아짐에 따라 팹 전체적으로 공정중 재고가 증가하고 이에 따라 사이클 타 임이 증가하는 경우가 많아진다. 이에 대한 해결책으로는 하나의 대형 스토커가 여러 베이를 담당하는 방법이 있으 나 이는 OHT에서의 상당한 정체 및 지체를 유발하여 결 과적으로 팹 전체의 효율 감소를 유발하는 경우가 많다. 다른 해결책으로는 다수의 트랜스퍼 라인 혹은 컨베이어 시스템과 유사하게 하나의 FOUP이 중간 대기나 스토커 경유 없이 일련의 장비들에 의해 순서대로 가공되는 시스 템인 인라인 레이아웃이 있다. SWP의 경우 FOUP내 각 웨이퍼의 처리가 모두 완료된 후 다른 장비로 이동함에 따른 추가적인 대기 시간의 발생이 불가피하나 인라인시 스템을 사용할 경우 해당 대기 시간을 추가적으로 절약하 여 결과적으로 큰 사이클 타임의 감소가 가능하다. 하지 만 인라인 시스템은 생산 계획 변동에 대한 대처 능력이 매우 떨어지는 단점이 있다.

### 2.2 기존 연구

클러스터 장비의 구성 및 웨이퍼 운송 작업에 대한 연 구로는 클러스터 장비의 페트리넷 모델링 및 성능 분석에 대한 연구<sup>[15]</sup>와 클러스터 장비내 웨이퍼 이송을 담당하는 진공 로봇의 팔이 하나인 경우와 둘인 경우에 대한 성능 비교에 대한 연구<sup>[16]</sup>가 있다. [15]의 연구는 2개의 직렬 공정 경로를 가지는 경우 및 3개의 병렬 공정 경로를 가 지는 경우에 대해 각각 페트리넷 모델을 작성하였고, [16] 의 연구는 웨이퍼 이송 작업을 수행하는 로봇의 팔이 하 나인 경우와 둘인 경우의 성능을 시간 진행 도표를 사용 하여 수리적으로 비교하였다.

클러스터 장비 제어 구조 및 프레임워크에 대한 기존 연구로는 CTC와 PMC간의 정보교환을 표준화하여 CTC 가 PMC에 대한 자세한 정보 없이도 제어 시스템을 재구 축할 수 있는 프레임워크 및 그 구현에 대한 연구<sup>[14]</sup>, RPI(Real-Time Performance Inc.) 사의 클러스터 장비 제어기인 ControlPro의 구조에 대한 연구<sup>[2]</sup>, CTC와 MC 간의 통신 구조에 대한 연구<sup>[3]</sup>, 클러스터 장비의 테스트 및 검증을 위한 가상 클러스터 장비 구축 및 스케줄링 프 레임워크에 대한 연구<sup>[10]</sup>, 상위 레벨 필드버스(Fieldbus) 중의 하나인 PROFIBUS-FMS및 상태 모델(state model) 에 기반한 객체 지향 CTC 프레임워크에 대한 연구<sup>[11]</sup>등 이 있다.

상기 모든 연구는 기존 장비 아키텍처에 기반한 연구 이며, 조사 결과 본 연구에서 제안한 ILE 아키텍처에 대 한 기존 연구는 없는 것으로 판단된다. 본 연구에서는 반 도체 생산에서 가장 많이 사용되는 장비인 클러스터 장비 구성에 대한 새로운 아키텍처를 제안하고 페트리넷 및 시 뮬레이션 모델링과 분석을 통해 해당 아키텍처의 효용성 을 검증하고자 한다. 본 논문은 다음의 순서로 구성되어 있다. 2장에서는 현 팹 레이아웃 및 클러스터 장비 아키 텍처상의 문제점 및 그 대안으로서 제시된 클러스터 장비 간의 웨이퍼 이동이 상호 연결된 인라인 EFEM(Equipment Front End Module)을 통해 이루어지는 ILE 아키텍처에 대해 설명한다. 3장에서는 2장에서 제시된 ILE 아키텍처 를 페트리넷 및 시뮬레이션 모델링을 통해 사이클 타임 관점에서 분석하고 기존 아키텍처와 비교한다. 마지막으 로 3장에서는 본 논문의 내용을 간략히 요약한다.

# 2. 현 아키텍처상의 문제점 및 대안 제시

#### 2.1 현 클러스터 장비 아키텍처상의 문제점

팹내 장비의 대부분을 차지하는 클러스터 장비의 경우 장비 내부에서는 웨이퍼가 매엽식으로 가공되는 반면 장 비와 AMHS간의 웨이퍼 이동은 FOUP 단위로 이루어지 는 관계로 FOUP내의 첫 웨이퍼의 가공이 완료되는 시각 부터 FOUP내의 마지막 웨이퍼의 가공이 완료되는 시각 까지의(즉 로트 구성에 소요되는) 추가 대기시간이 발생 한다. 이러한 추가 대기시간의 최소화를 위해서는 FOUP

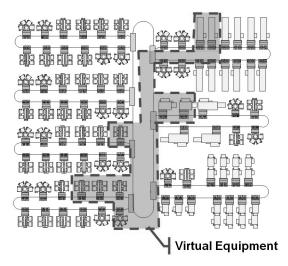

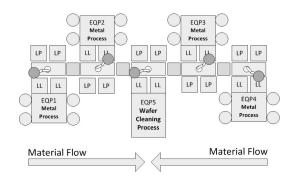

그림 3. 기존 팹 레이아웃

내 평균 웨이퍼 매수의 감축이 필요하나 이미 한계점에 근접한 현 AMHS의 처리 능력을 감안할 경우 대부분의 팹에서는 평균 웨이퍼 매수의 감축을 적용하기 어려운 상 황이다.

# 2.2 현 팹 레이아웃상의 문제점

대부분의 팹의 경우 특정 장비 그룹에 속한 모든 장비 들은 그림 3과 같이 근접한 위치에 집합적으로 설치된다. 소량 다품종 팹의 경우 프로세스 흐름의 종류가 매우 많 은 관계로 상기와 같은 잡 샵에 적합한 팹 레이아웃이 적 합하다. 하지만 다량 소품종 팹의 경우 웨이퍼 제조공정 은 프로세스 흐름의 종류가 많지 않고 그림 1과 같이 대 부분의 프로세스 흐름에서 일련의 공정 스텝이 반복되는 일종의 재진입 플로우 샵이라고 볼 수 있다. 따라서 프로 세스 흐름중 공통적으로 반복되는 일련의 공정 스텝을 논 리적으로 묶어 그림 2와 같이 일종의 가상 장비 단위로 팹을 운영함으로써 관리상의 복잡성을 감소시키는 경우 가 많다. 하지만 장비 그룹별로 배치되어 있는 현재의 팹 레이아웃에서는 가상 장비를 구성하는 실제 장비들간의 웨이퍼 이동 거리가 매우 긴 관계로 여러 문제점(팹 전체 적으로 사이클 타임 증가, AMHS 부하 증가, 시스템 복잡 도 증가 등) 이 발생한다.

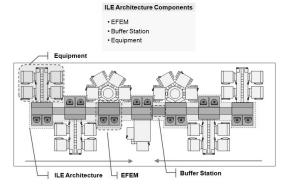

### 2.3 ILE(In-Line EFEM) 아키텍처

이에 대한 대안으로 프로세스 흐름에서 가장 많이 사 용되는 가상 장비들에 대해 가상 장비에 사용되는 실제 장비들을 가상 장비 내 공정 스텝 순서대로 베이에 일렬

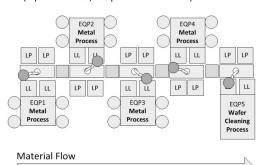

그림 4. ILE 아키텍처

그림 5. ILE 아키텍처를 이용한 팹 레이아웃

로 배치하는 인라인 레이아웃을 채택할 경우 사이클 타임 및 AMHS 부하의 감소가 가능하다. 더 나아가 그림 4 및 그림 5와 같이 가상 장비내 클러스터 장비간의 웨이퍼 이 동이 상호 연결된 인라인 EFEM을 통해 이루어지는 ILE(In-Line EFEM) 아키텍처를 적용할 경우 3장 1절에 서 설명한 FOUP 단위 이동에 따른 장비내 추가 대기시 간을 최소화할 수 있다.

ILE 아키텍처는 장비간 웨이퍼 이동이 항상 AMHS를 통해 FOUP 단위로 이루어지는 기존 장비 아키텍처와 달 리 가상 장비내의 실제 장비들간의 웨이퍼 이동이 이들 장비들을 연결하는 EFEM과 버퍼 스테이션을 통해 웨이 퍼 단위로 이루어지는 장비 아키텍처로 정의할 수 있다. LL, 진공 모듈, 공정 모듈, EFEM, LP가 하나의 독립된 장비로서 AMHS에 연결되는 기존 아키텍처와 달리 ILE 아키텍처에서는 LL, 진공 모듈은 기존과 같이 장비 업체 로부터 제작되어 납품되는 반면 EFEM과 LP는 반도체 제조업체에서 지정된 규격에 따라 별도의 장비 업체를 통 해 제작, 납품된다. 이와 같은 표준화된 EFEM 및 LP를 통해 반도체 제조업체는 복수의 장비 업체로부터 납품받 은 각 장비들을 ILE 시스템내에 수월하게 통합할 수 있 다. 따라서 ILE 아키텍처의 구현을 위해서는 표준화된 EFEM 스펙 정의 및 개발, 장비 업체와의 협업 및 표준 인터페이스 구축 / 개발, EFEM 제어기, ILE 제어기 개발 등이 필요하며, 반도체 제조업체 관점에서의 ILE 아키텍 처의 장점은 아래와 같이 요약할 수 있다.

- 1. 웨이퍼의 장비내 대기 및 장비간 이동 시간 감소

- 2. 공정 스텝 감소

- 3. FOUP내 평균 웨이퍼 수 감소 가능

- 4. AMHS 부하 감소

- 5. 가상 장비내 FOUP 이동시 불확실성 감소

- 6. 장비에 대한 제어/관리 능력 향상 장비 업체와의 협 상력 증가

참고로 반도체 제조시 생산계획 및 제품 믹스의 빈번 한 변동 및 공정 개선으로 인해 많은 장비 개조 및 시스템 수정이 필요하지만 기존 아키텍처상에서는 EFEM 및 LP 까지 일괄적으로 장비 업체에서 제작하여 납품하는 관계 로 내부 구조 및 제어 로직을 파악하기 곤란하였다. 결과 적으로 장비 내부 구조 및 제어 로직의 개조가 곤란했으 며, 장비 제조업체에 개조 의뢰시 대응 속도가 느리고 많 은 비용이 소모되었다. 따라서 EFEM 및 LP가 ILE 아키 텍처에 따라 표준화될 경우 반도체 제조업체의 장비 개조 및 시스템 수정이 용이해진다. 반면 ILE 아키텍처의 단점 은 아래와 같이 요약할 수 있다.

- 1. ILE 시스템을 구성하는 장비간 로드 밸런싱 필요

- 2. 생산 계획 및 제품 믹스 변경에 대한 대응능력 저하

- 3. 장비 재배치 횟수 증가

- 4. 팹내 장비당 차지하는 공간(footprint) 증가

- 5. ILE 아키텍처가 업계 표준으로 정착되기 전까지는 기존 장비 아키텍처를 ILE 아키텍처로 전환하는데 소요되는 비용을 장비 제조업체에 지불해야 하므로

반도체 제조업체의 추가 비용 발생

상기 ILE 아키텍처의 장점 및 단점을 고려하면 ILE 아 키텍처는 소량 다품종 팹에서는 그 효용성이 의심되나 다 량 소품종 팹에서는 단점에 비해 장점에 많은 관계로 충 분히 적용 가능하다고 판단되며, 상기 장/단점중 상대적 으로 객관적인 성능 비교가 가능한 장비내 대기 시간 및 장비간 이동 시간의 비교는 3장에서 논의한다.

## 3. 모델링 및 분석(페트리넷 및 시뮬레이션)

### 3.1 페트리넷 모델링 및 분석

페트리넷은 이산적인 분산 시스템의 수학적 모델이며 시스템의 정확성을 측정하기 위한 여러 가지 기준 등의 정보의 흐름과 기본적 특징들을 분석하기 위해 쓰일 수 있다. 페트리넷은 장소(place), 변이(transition), 화살표로 이루어져 있다. i와 j 두 장소가 주어졌을 때 i와 j를 이어 주는 화살표는 변이 i를 출발하여 j로 들어오는 것을 의미 한다. 실행 과정에서 입력 혹은 다른 시스템의 규칙에 따 라 나타날 수 있는 데이터는 토큰으로 표기된다. 이러한 전달은 각각의 입력 장소들의 토큰을 가지고 있을 때만 발사(fire) 될 수 있다. 변이가 발사되었을 때 토큰이 각각 의 입력 장소에서 상응하는 출력 장소로 이동한다. 페트 리넷의 토큰은 이러한 토큰들이 시스템 상에서 어떻게 분 포하는지를 보여주며 페트리넷의 마킹은 시스템의 현재 상태를 보여준다.

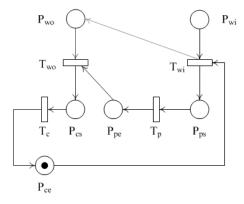

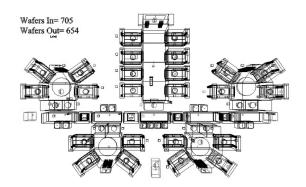

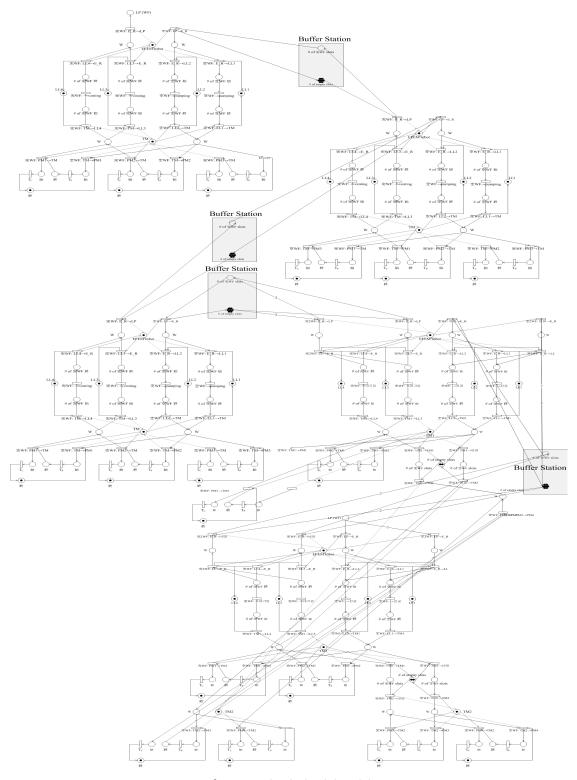

본 연구에서 제시된 ILE 아키텍처의 효용성 분석을 위 해 삼성전자에서 파일럿 프로젝트로 진행중인 ILE 시스 템(그림 7 참조)에 대해 페트리넷 기법을 이용하여 모델 링하고 사이클 타임을 비교 분석하였다. ILE 시스템내 동 작이 주기적으로 반복되고 ILE 시스템에서 한 종류의 제 품만 생산되며 충분한 미가공 웨이퍼 재고가 있고 장비의 고장이 없을 경우 해당 페트리넷 모델의 수리적 분석을 통해 최적 장비 운영 스케줄 도출 및 최소 사이클 타임 계 산이 가능하며(자세한 내용은 [15] 참조), 실제 장비 스펙 및 공정 데이터에 기반한 모델링상의 가정은 하기와 같다.

- AMHS으로부터 ILE 시스템으로 이동된 FOUP내 각 웨이퍼는 1대의 메탈 장비와 1대의 웨이퍼 클리 닝 장비를 거친 후 FOUP에 다시 모여 AMHS로 이동

- 웨이퍼 클리닝 장비의 웨이퍼 처리 속도는 메탈 공 정 장비에 비해 대략 4배인 관계로 전체 시스템의 로드 밸런싱을 위해 ILE 시스템은 4대의 동일한 메 탈 공정 장비와 1대의 웨이퍼 클리닝 장비로 구성됨

- 총 4개의 버퍼 스테이션은 각 장비의 EFEM 사이에 위치하여 웨이퍼의 장비간 이송 통로 및 임시 버퍼 역할 수행

- 진공 / 대기압 로봇의 팔 개수: 2개(dual-blade robot)

- 진공 / 대기압 로봇을 통한 웨이퍼 이동 시간: 6초

- 펌핑 / 벤팅 시간: 30초

- 병렬 처리 공정(즉, 장비내 모든 공정 모듈에서 동일 한 공정을 진행하므로 웨이퍼는 장비내 하나의 공정 모듈만 방문하면 됨)

- 메탈 / 웨이퍼 클리닝 공정 장비내 공정 모듈 개수: 3개 / 6개

- 메탈 / 클리닝 공정 진행 시간: 188초 / 70초

- 메탈 장비내 공정 모듈에서 웨이퍼 1매 공정 진행 후 공정 모듈 클리닝 필요(즉 1x 클리닝)

- 메탈 장비내 공정 모듈 클리닝 소요 시간: 54초

- ILE 시스템내 장비 레이아웃: 시나리오 2

그림 14는 상기 가정에 기반한 ILE 시스템에 대한 페 트리넷 모델이며 그림 14의 일부인 그림 6은 메탈 공정 장비내 각 공정 모듈의 페트리넷 모델이다. 시스템 시작 시 공정 모듈은 비어있으며(페트리넷의 초기 상태에서의 장소 Pcc의 토큰으로 표현되며 해당 토큰은 공정 모듈의 상태를 나타냄) 가공 가능한 웨이퍼가 진공 로봇으로 이 송된 경우(장소 Pwi로 로봇을 나타내는 토큰 이동) 변이  $T_{wi}$ 가 발사되어  $P_{ce}$ 및  $P_{wi}$ 내의 토큰은  $P_{ps}$ 로 이동한다. 이 후 공정 모듈내의 웨이퍼 가공이 완료되면 변이 Tp가 발 사되어 토큰이 Pm로 이동하고 진공 로봇이 가공이 완료 된 웨이퍼를 운송할 준비가 완료되면(장소 Pwo로 로봇을 나타내는 토큰 이동) 변이  $T_{wo}$ 가 발사되어  $P_{pe}$ 및  $P_{wo}$ 내의 토큰은 Pcs로 이동하고, 공정 모듈 클리닝이 완료되면 변

그림 6. ILE 파일럿 시스템

**그림 7.** ILE 파일럿 시스템

그림 8. 페트리넷 모델을 통한 사이클 타임 분석 결과

이  $T_c$ 가 발사되어 장소  $P_{\infty}$ 로 토큰이 이동하여 공정 모듈 내 웨이퍼 가공 관련한 공정 사이클이 완료된다.

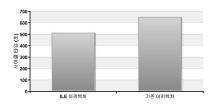

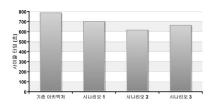

그림 8은 페트리넷 모델에 대한 총 사이클 타임 분석 결과이며, 해당 시스템의 경우 ILE 아키텍처 채용시 기존 아키텍처 대비 사이클 타임이 28% 감소함을 알 수 있다. 참고로 AMHS 경유 시간의 경우 가상 장비 내 실제 장비 의 팹내 위치 및 팹 상황에 많은 영향을 받는 관계로 페트 리넷 모델링이 불가능하여 분석에서 제외하였으며, ILE 적용시 가상 장비내 실제 장비간 이동 거리가 단축되어 AMHS 경유 시간이 감소하는 경우가 대부분이므로 AMHS 경유 시간을 고려할 경우 ILE 아키텍처 적용시의 사이클 타임 감소 효과는 더욱 증가하리라 예상된다.

#### 3.2 시뮬레이션 모델링 및 분석

페트리넷 모델링 및 분석 기법은 3장 1절에서 서술한 여러 가지 장점을 가지고 있으나 AMHS로부터의 FOUP 별 도착 시간이 불규칙적이거나 장비의 고장 발생, 다수 제품의 가공 등의 비정상적 상황에 대한 분석이 불가능하 고 발생 가능한 여러 시나리오 및 선택 가능한 여러 스케 줄링 정책 중 일부만 모델링 및 분석이 가능한 단점이 있 다. 따라서 본 장에서는 반도체 제조공정 분석에 많이 사 용되는 상용 시뮬레이션 패키지인 AutoMod<sup>[7]</sup>를 사용하 여 그림 9와 같이 시뮬레이션 모델링 및 분석을 실시하였 다. 페트리넷 모델링 및 분석 기법은 제한적인 상황(한 종 류의 제품만 생산되며 충분한 미가공 웨이퍼 재고가 있고

그림 9. ILE 시스템의 AutoMod 시뮬레이션 모델

장비의 고장이 없을 경우)에서만 적용이 가능하다는 단점 이 있으나 시뮬레이션 모델과 달리 최적 장비 운영 스케 줄 및 최소 사이클 타임을 계산할 수 있다는 장점이 있다. 따라서 페트리넷 모델링을 통해 계산된 최적 스케줄 및 최소 사이클 타임은 시뮬레이션 모델의 레퍼런스값으로 쓰일 수 있다. 예를 들어, 설비 내부의 상세 스케줄링 로 직은 설비 제조업체의 중요 자산인 관계로 해당 설비의 고객사인 반도체 제조업체에 제공되지 않는다. 따라서 시 뮬레이션 모델링시 설비 내부의 스케줄링 로직은 일종의 블랙 박스 형태로 간략히 모델링되며, 결과적으로 시뮬레 이션 모델의 정확성이 저하되는 요인이 된다. 따라서 시 뮬레이션 모델을 페트리넷 모델과 동일한 상황(장비 고장 없음 등) 으로 설정한 후 실행하는 경우 페트리넷 모델링 으로부터 계산된 최적 스케줄 및 최소 사이클 타임을 이 용하여 시뮬레이션 모델의 정확성 측정 및 스케줄링 로직 보완이 가능하다.

시뮬레이션 모델링을 위해 3장 1절에서 논의한 가정에 추가하여 하기와 같이 가정하였다.

- 버퍼 스테이션의 용량: 40매(웨이퍼)

- 설비 가동률: 90%

- 가공 우선순위: 선입선출

- ILE 시스템의 처리 용량보다 많은 FOUP이 AMHS 로부터 지속적으로 도착

- 시스템의 deadlock 현상을 방지하기 위해 가공후 이 동할 위치가 사전 예약되기 전까지는 가공을 시작하 지 않는 예약 규칙(reservation rule) 적용<sup>[4]</sup>

상기 가정 중 설비 가동률 및 가공 우선순위는 실제 제 조 현장 data에 기반한 것이며 해당 시뮬레이션 모델은 각 시나리오별 ILE 시스템내의 병목현상을 측정하기 위

한 것이므로 ILE 시스템의 처리용량보다 많은 FOUP이 AMHS로부터 지속적으로 도착하도록 가정하였다. 본 시 뮬레이션 모델링에서는 하기 3가지 시나리오에 대해 분석 하였다.

- 시나리오 1(그림 10): FOUP이 ILE 시스템의 한쪽 끝 장비에서 로딩되어 시스템 반대편 끝 장비에서 언로딩 되는 장비 레이아웃

시나리오 1과 같은 레이아웃에서는 ILE 제어기 로직 설계가 용이해지고 장비의 추가 설치 및 제거가 상대적으 로 용이해지는 장점이 있으나 ILE내 장비 숫자에 비례하 여 EFEM간 웨이퍼 흐름에 병목현상이 발생할 가능성이 높아지고 팹내 장비당 차지하는 공간이 증가하는 단점이 있다.

- 시나리오 2(그림 11): FOUP이 ILE 시스템의 양 끝

Scenario 1 Unidirectional Flow within ILE System (Input One Side, Output the Other Side)

**그림 10.** 시나리오 1 - 단방향 흐름(좌측 → 우측)

Scenario 2 Unidirectional Flow within ILE System (Flow from Outside to Inside)

**그림 11.** 시나리오 2 - 단방향 흐름(외부 → 내부)

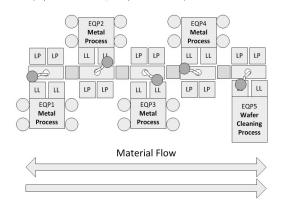

Scenario 3 Bidirectional Flow within ILE System (Input Both Sides, Output One Side)

**그림 12.** 시나리오 3 - 단방향(좌측 → 우측) 및 양방향(우측 → 좌측 → 우측) 흐름

단 장비에서 로딩되어 시스템 중앙에 위치한 장비에서 언 로딩되는 장비 레이아웃

시나리오 2와 같은 레이아웃에서는 시나리오 1과 반대 로 웨이퍼 병목 현상이 감소하고 팹내 장비당 차지하는 공간이 줄어드는 장점이 있는 반면 ILE 제어기 로직 설계 가 복잡해지는 단점이 있다.

- 시나리오 3(그림 12): FOUP이 ILE 시스템의 양 끝 단 장비에서 로딩되어 시스템의 한쪽 끝 장비(그림 11에 서는 웨이퍼 세정 장비)에서 언로딩되는 장비 레이아웃

그림 12의 경우 장비 1에서 로딩된 FOUP은 장비 5에 서 언로딩되고 장비 5에서 로딩된 FOUP은 장비 1~4중 한 곳에서 가공후 장비 5에서 언로딩되므로 시나리오 1과 2가 절충된 형태라고 볼 수 있다(시나리오 1/2의 장/단점 이 절충된 형태).

각 시나리오별 시뮬레이션 모델을 500시간씩 10회 반 복 실험하여 사이클 타임을 분석하였으며, 각 시뮬레이션 모델 시작시 ILE 시스템내 웨이퍼가 존재하지 않는다고 가정한 후 모델 초기화 시간인 50시간 경과 이후 사이클 타임을 측정한 결과가 그림 13과 같다. 따라서 시나리오 1 및 3 대비 시나리오 2를 적용할 경우 사이클 타임이 각 각 14%, 8% 감소하며, 이는 시나리오 2의 장비 레이아웃 구조가 ILE 시스템내 웨이퍼 흐름을 가장 원활하게 하는 구조이기 때문이며 세 시나리오에서의 사이클 타임간 큰 차이가 없는 이유는 대상 파일럿 시스템상의 공정 진행 시간 대비 로봇을 통한 웨이퍼 이동 시간이 매우 짧아 병 목 현상이 자주 발생하지 않았기 때문이다.

그림 13. 시뮬레이션 모델을 통한 사이클 타임 분석

# 4. 결 론

본 연구에서는 반도체 제조공정 및 클러스터 장비에 대한 상세하게 설명하고 현 팹 레이아웃 및 클러스터 장 비 아키텍처상의 문제점을 제시하였다. 또한 현 아키텍처 상의 대안으로서 클러스터 장비간의 웨이퍼 이동이 상호 연결된 인라인 EFEM을 통해 이루어지는 ILE 아키텍처 의 개념을 제시하였다. 마지막으로 해당 아키텍처를 실제 적용하여 구현된 파일럿 시스템을 페트리넷 및 시뮬레이 션 모델링을 통해 사이클 타임 관점에서 비교 분석하였다. 본 논문에서는 기존 아키텍처를 포함하여 ILE 아키텍처 상의 세 가지 장비 배치 레이아웃 시나리오를 시뮬레이션 하였는데, 그 중에서 가장 좋은 결과를 나타낸 것은 시나 리오 2였다. 시나리오 2는 ILE 시스템내 FOUP 이동 거 리를 최소화함으로써 웨이퍼 흐름상 병목 현상을 최소화 함으로써 사이클 타임을 줄일 수 있었다.

# 참 고 문 헌

- 1. 강보경(1998), 「클러스터 툴(Cluster Tool) 제어 시스템」, 월간 반도체, 1월호, pp. 34-42.

- 2. 이환용, 이태억, "두 팔을 가진 화학 박막 증착용 CT의 스 케줄링과 공정 시간 결정", 대한산업공학회/한국경영과학 회 춘계공동학술대회 논문집(2000), pp. 107-110.

- 3. 이진환, 이태억, 박정현(2002), "고수준 필드버스 기반의 클러스터 툴 모듈 통신", 대한산업공학회/한국경영과학회 춘계공동학술대회 논문집, pp. 285-292.

- 4. 이홍순, 한영신, 이칠기(2006), "Direct 반송방식에 기반을 둔 300 mm fab line 시뮬레이션", 한국시뮬레이션학회 논 문지, 19권, 4호, pp. 51-57.

- 5. 조정환, 노희정(2010), "고속 EFEM 의 성능평가시스템 개발", 조명/전기설비학회 논문지 24권, 2호, pp. 27-32.

- 6. 허선, 이현, 박유진(2010), "차세대 웨이퍼 생산시스템을 위한 클러스터 툴 디스패칭 알고리즘 개발", 한국산학기술 협회 추계 학술발표 논문집, pp. 792-796.

- 7. Brooks Automation Inc, [AutoMod User's Manual], 2006.

그림 14. ILE 시스템 페트리넷 모델링

- 8. Burggraaf, P. (1995), "Coping with the high cost of wafer fabs.", Semiconductor International Vol. 18, No. 3, pp. 45-54.

- 9. International Technology Roadmap for Semiconductors, http://www.itrs.net/Links/2011ITRS/Home2011.htm, 2011.

- 10. Joo, Y. J. and T. E. Lee (2004), "Virtual control a virtual cluster tool for testing and verifying a cluster tool controller and a scheduler", IEEE Robotics & Automation Magazine, Vol. 11, No. 3, pp. 33-49.

- 11. Lee, J. H. and T. E. Lee (2004), "SECAM: a supervisory equipment control application model for integrated semiconductor manufacturing equipment", IEEE Robotics and Automation Magazine, Vol. 11, No. 1, pp. 41-58.

- 12. Mőnch, L., J. W. Fowler, S. Dauzere-Peres, S. J. Mason, O. Rose, (2011) "A survey of problems, solution techniques, and future challenges in scheduling semiconductor manufacturing operations", Journal of Scheduling, Vol. 14, pp. 583-599.

- 13. Oomichi, T., T. Nagai, K. Mori, Y. Adachi, T. Teshima (2007), "System architecture for high reliability module mobile robot", Transactions-Society of Instrument and Control Engineers, Vol. 43, No. 8, 689-698.

- 14. Sato, T., E. Yoshida, Y. Kakebayashi, N. Komada, (2004) "CTCSS (Cluster Tool Controller Software System): The flexible control system for the cluster structured semiconductor processing equipment", IEEJ Transactions on Industry Applications, Vol. 124, pp. 160-167.

- 15. Srinivasan, R. S. (1998), "Modeling and performance analysis of cluster tools using Petri nets", IEEE Transactions on Semiconductor Manufacturing, Vol. 11, No. 3, pp. 394-403.

- 16. Venkatesh, S., R. Davenport, P. Foxhoven, J. Nulman (1997), "A steady-state throughput analysis of cluster tools: dual-blade versus single-blade robots", IEEE Transactions on Semiconductor Manufacturing, Vol. 10, No. 4, pp. 418-424.

## 한 용 희 (amade@ssu.ac.kr)

한양대학교 산업공학과 학사

1998 Georgia Institute of Technology, 산업공학 석사

2004 Georgia Institute of Technology, 산업공학 박사

2005~2010 삼성전자 메모리사업부 책임연구원

2011~현재 숭실대학교 벤처중소기업학과 조교수

관심분야: 시뮬레이션, 생산관리, SCM, 반도체