논문 2012-07-26

# 저전력 NAND 플래시 메모리를 위한 필터 버퍼의 효율성 분석

# (Analysis on the Effectiveness of the Filter Buffer for Low Power NAND Flash Memory)

정 보성, 이 정 훈\*

(Bo-Sung Jung, Jung-Hoon Lee)

Abstract: Currently, NAND Flash memory has been widely used in consumer storage devices due to its non-volatility, stability, economical feasibility, low power usage, durability, and high density. However, a high capacity of NAND flash memory causes the high power consumption and the low performance. In the convention memory research, a hierarchical filter mechanism can archive an effective performance improvement in terms of the power consumption. In order to attain the best filter structure for NAND flash memory, we selected a direct-mapped filter, a victim filter, a fully associative filter and a 4-way set associative filter for comparison in the performance analysis. According to the results of the simulation, the fully associative filter buffer with a 128byte fetching size can obtain the bet performance compared to another filter structures, and it can reduce the energy\*delay product(EDP) by about 93% compared to the conventional NAND Flash memory.

Keywords: NAND flash memory, Filter mechanism, Low power, Cache memory

#### 1. 서론

오늘날 휴대 기기들의 급속한 보급화와 고성능화가 이루어지면서 많은 모바일 기기들은 고성능을 요구하는 다양한 프로그램을 수행하기 위해 효과적인 저장 시스템을 요구하고 있다 [1].

이러한 요구에 부합하는 NAND 플래시 메모리는 비록 한번 사용되어진 페이지에 덮어 쓰기가 불가능하며 특히 지우기 동작이 완료된 블록에만 쓰기 동작이 이루어지는 단점을 가짐에도 불구하고빠른 메모리 접근시간, 저전력, 강한 충격에 대한저항력, 안전성, 비휘발성, 그리고 소형화에 따른 높은 집적도등 다양한 장점으로 스마트폰 및 패드, 디

\* 교신저자(Corresponding Author)

논문접수: 2012. 04. 03., 채택확정: 2012. 05. 30. 정보성, 이정훈:경상대학교 ERI 제어계측공학과 ※ 이 논문은 2011년도 정부(교육과학기술부)의 재원으로 한국연구재단의 기초연구사업 지원을 받아 수행된 것임(2011-0009368).

© J. IEMEK 2012 Aug.: 7(4) 201-207

ISSN: 1975-5066

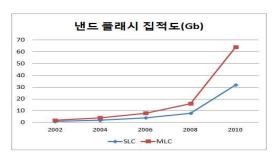

지털 카메라 등 휴대 기기의 보편적인 저장 매체로서 오늘날 그 수요가 급증하고 있다 [2]. 더욱이 암달의 법칙(Amdal's low) 및 황의 법칙(Hwang's law)을 넘어 오늘날 NAND 플래시 메모리는 그림 1과 같이 집적도와 성능향상이 급격하게 발전하고 있다 [3]. NAND 플래시 메모리 동작은 기본적으로 페이지 단위의 읽기/쓰기 동작, 블록 단위의 지우기 동작으로 이루어진다. 이러한 NAND 플래시 메모리의 기본 페이지 크기 증가(512B~8KB)와 지우기 동작의 기본단위인 블록의 크기(16\*512B ~ 128\*8KB) 역시급격하게 증가하고 있다 [4].

NAND 플래시 메모리는 페이지 단위로 쓰기 동작을 수행하지만 하드디스크처럼 덮어 쓰기 동작을 하지 못한다. 따라서 NAND 플래시 메모리의 어떤 블록에 더 이상 쓰기 페이지를 위한 유효 페이지가 없다면, 유휴(invalid) 블록을 만들기 위한 병합 (merge) 동작과 지우기(erase) 동작이 수반된 후 쓰기 동작이 이루어져야한다.

이러한 동작은 NAND 플래시의 용량이 증가할

그림 1. NAND 플래시 집적도에 대한 증가 추세 Fig 1. A growing trend of a NAND flash capacity

수록 NAND 메모리의 접근 시간과 에너지 소비 역 시 급격히 증가하게 된다. 오늘날, NAND 플래시는 셀 당 1비트를 저장할 수 있는 SLC(Single Level Cell)와 셀 당 2비트 저장할 수 있는 MLC(Multi Level Cell) 및 셀 당 3비트까지 저장할 수 있는 TLC(Triple Level Cell)도 상용화가 되고 있다. 단 위 셀 당 저장 용량의 차이로 SLC보다 높은 집적 도를 가지는 MLC와 TLC는 가격면에서 훨씬 저렴 하지만 동작 속도와 에너지 관점에서 매우 불리하 다. 이처럼 비록 NAND 플래시가 높은 집적도에 따 른 대용량화와 소형화로 인해 모바일 기기의 고성 능 저장 매체로 각광받고 있지만, 오히려 이러한 높 은 집적도로 인해 에너지 소비는 급격히 증가하고 있으나 이에 대한 저전력 연구는 현재 미비한 실정 이다. 특히, 오늘날 많이 사용되는 휴대 기기인 스 마트폰과 스마트패드등은 많은 영상처리와 데이터 처리로 인해 에너지 소비가 더욱 중요하게 고려되 고 있다. 따라서 본 논문에서는 필터링 메커니즘을 이용하여 휴대기기에 적합한 저전력 NAND 플래시 메모리 구조를 제안한다.

#### Ⅱ. 관련연구

기존의 NAND 플래시 연구는 주로 플래시 메모리의 가장 큰 단점을 해결하기 위하여 사상 알고리 즉인 FTL(Flash Translation Layer)과 쓰기 및 지우기 동작의 평준화(Wear Leveling)를 위한 다양한 연구가 수행되었다. 하지만 많은 고성능 휴대기기들에 대한 NAND 플래시 사용으로 앞으로 저전력 NAND 플래시에 대한 연구가 활발하게 이루어질 것으로 판단된다. Flashpower [5]은 CACTI 5.3 [6]을 이용하여 NAND 플래시 메모리의 자세한 소비에너지에 대한 시뮬레이터를 개발하였다. 이 시뮬레이터는 CMOS 레벨에서 읽기/쓰기/지우기 동작

시 소비되는 전력 분석뿐만 아니라 플래시가 구동되지 않을 때 소비되는 전력(idle power)까지 모두고려할 수 있는 시뮬레이터이다. 본 연구에서도 이시뮬레이터를 이용하여 시뮬레이션을 수행하였다.

Sun [7]은 PRAM(phase change random access memory)를 이용한 혼합 NAND 플래시 구조로 기존의 로그-기반 NAND 플래시 [8]의 단점인 순차적인 쓰기 동작시 잦은 지우기 연산을 효과적으로 줄일 수 있는 메커니즘을 이용하여 성능 및 저전력의 효과를 얻고자 하였다. Li [9]는 SRAM에 핫캐쉬(HotCache)와 쓰레기 수집 (garbage collection) 정보를 이용하여 NAND 플래시에 잦은 데이터 쓰기를 줄여 저전력 NAND 플래시 메모리를 구현하였다. Sun과 Li의 연구 역시 모두 SRAM 버퍼를 이용하여 NAND 플래시 메모리의 저전력 및 고성능을 이루고자 하였다.

본 연구에서는 복잡한 하드웨어 및 구동 메커니즘 없이 구현이 간단하고 실제 적용이 가능한 저전력 NAND 플래시를 위해 기존의 NAND 플래시에 다양한 필터 구조의 버퍼와 페칭 크기에 따른 필터 버퍼링의 효용성을 이용하여 저전력을 얻고자 한다. 필터 버퍼 크기와 페칭 크기는 전체 시스템의 성능평가와 소비 감소 효과를 고려하여 최적의 필터 버퍼 구조와 페칭 크기를 선택한다.

필터링 메커니즘은 계층적 구조로써 일반적인 주(main) 메모리위에 작은 크기의 필터 버퍼를 위 치시킴으로써 시간적 지역성을 이용하여 소비 전력 을 줄이는 방법이다. 이러한 필터 메커니즘은 현재 까지 다양한 구조 및 동작 메커니즘을 이용하여 저 전력 캐쉬 [10] 및 TLB [11] 연구에 활용되고 있 다. 그러나 캐쉬 메모리의 명령어 캐쉬의 경우 작은 크기에도 불구하고 필터 버퍼의 적중률이 대단히 높기 때문에 성능과 소비 전력 면에서 매우 우수한 성능을 보이고 있으나, 데이터 캐쉬의 경우 필터 버 퍼의 적중률 감소로 성능이 급격히 떨어지는 단점 을 가진다. 그러나 TLB의 경우 명령어 및 데이터 모두 적중률이 매우 높기 때문에 작은 크기를 가진 필터 버퍼를 이용하여 저전력 TLB 구현이 가능하 다. 이에 본 연구에서는 필터 메커니즘을 플래시 메 모리의 상위 버퍼로써 활용하여 소비전력에 대한 필터 버퍼의 효용성을 검증한다. 특히 고려해야 할 중요한 사항은 적중률에 따른 소비전력과 성능 효 과를 극대화시키기 위한 필터 버퍼 크기와 한 엔트 리의 페이지 크기가 중요한 이슈가 된다. 왜냐하면 이들의 변화에 따라 시스템 성능 및 소비전력에 매 우 다양한 결과를 보이기 때문이다.

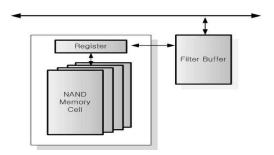

그림 2. 필터 버퍼 NAND형 플래시 구조 Fig 2. NAND flash structure with a filter-buffer

### III. NAND 플래시 메모리를 위한 필터 버퍼 구조 및 버퍼의 효과

그림 2는 필터 버퍼를 내장한 NAND 플래시 메 모리의 구조를 나타낸 그림이다. NAND 플래시 메 모리는 플래시 메모리 셀과 페이지의 읽기/쓰기 동 작을 위한 기본 페이지 크기의 레지스터로 구성된 다. 필터 버퍼는 기본 페이지인 2KB보다 작은 페칭 페이지를 가지며 4KB의 버퍼 크기로 구현하였다. 이는 버퍼 크기를 변화해가면서 시뮬레이션을 수행 한 결과 비용 대 성능 면에서 가장 효과적인 버퍼 크기임을 알 수 있었다. 제안된 필터 버퍼는 NAND 플래시 메모리에서 참조 되어진 페이지중 작은 페 칭 페이지가 저장된다. 만약 CPU로부터 하나의 페 이지가 요청되어지면 먼저 필터 버퍼에서 요청된 페이지를 검색하게 된다. 검색 결과 필터 버퍼에서 접근 실패가 발생하면, NAND 플래시 메모리에서 요청 페이지를 인출하게 되며, 이때 요청되어진 페 이지 중 요청한 명령어 및 데이터를 포함하는 작은 페칭 페이지가 필터 버퍼에 저장된다. 필터 버퍼의 엔트리가 모두 유효(valid) 페이지이면 필터 버퍼의 대치 알고리즘인 FIFO(First-In-First-Out)를 이용 하여 하나의 페이지가 버려지게 된다. 이때 필터 버 퍼의 버려지는 페이지가 이전에 갱신(dirty)되어진 페이지라면 그 갱신 페이지는 NAND 플래시 메모 리에 쓰기 동작이 이루어진다.

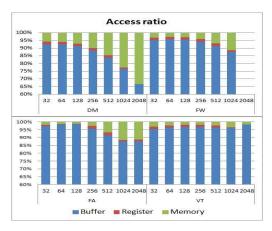

본 논문에서 저전력 및 고성능 NAND 플래시메모리의 필터 버퍼 구조를 선택하기 위해 대표적인 캐쉬 메모리 구조인 직접사상 버퍼(DM)와 4-웨이 연관버퍼(FW), 빅팀 버퍼(VT), 그리고 완전연관버퍼(FA)를 사용하였다. 최적의 필터 버퍼의 페칭페이지를 선택하기 위해 각 필터 버퍼의 페칭 페이지를 32byte에서 NAND 플래시 메모리의 기본 페이지 크기인 2Kbyte까지 증가시키면서 필터 버퍼

그림 3. 필터 NAND 플래시 메모리의 접근 비율 (필터버퍼, 레지스터, NAND 플래시 셀 ) Fig 3. Access ratio of filter-buffer NAND Flash

memory(filter-buffer, register, NAND flash cell)

의 적중률과 NAND 플래시의 접근 비율을 측정하였다. 단 4-웨이 연관버퍼는 2048B의 페칭 페이지를 고려할 경우 버퍼 크기가 8KB가 되기 때문에 시뮬레이션에서 고려하지 않는다.

그림 3은 필터 버퍼 적중률, 순차적 접근에 대한 레지스터 적중률 그리고 마지막 플래시 셀의 접근 비율을 나타낸 그림이다. 전반적으로 32B~128B 페칭 페이지에서 필터 버퍼의 적중률이 90% 이상 으로 가장 높음을 알 수 있다. 이는 필터 페이지의 크기가 작음에 따라 엔트리 증가에 따른 시간적 지 역성의 효과로 필터 버퍼의 적중률이 높다는 것을 알 수 있었다. 결론적으로 플래시 셀 접근(random access) 및 플래시 레지스터 접근(serial access) 대신 빠른 SRAM 버퍼의 적중률을 높여줌으로써 소비전력 뿐 아니라 평균 메모리 접근 시간을 줄일 수 있지만 한편으로는 버퍼의 엔트리가 크면 필터 버퍼 자체의 소비 전력이 증가하기 때문에 소비 전 력적인 측면은 시뮬레이션을 통하여 정확히 산출해 야한다. 대부분의 필터 구조에서 32-, 64-, 128-byte에서 버퍼의 적중률이 가장 높음을 알 수 있었다. 빅팀의 경우 완전연관 구조의 희생버퍼로 2KB가 추가로 사용되어 총 6KB의 버퍼 크기를 가 지며, 페칭 크기와 상관없이 버퍼 크기의 증가에 따 라 대부분의 페칭 크기에서 모두 좋은 결과를 보인 다. 결론적으로 필터 버퍼의 엔트리 개수에 따른 버 퍼 적중률을 고려해볼 때 4KB 버퍼 크기에서는 128B 페이지 페칭 크기가 가장 좋은 결과를 보였 다.

| Parameter         | Value            |

|-------------------|------------------|

| Capacity(Gb)      | 8                |

| Base page size    | 2048(byte)       |

| Block(Pages)      | 1(64)            |

| Serial acsess     | 25( <i>n</i> s)  |

| Random access     | 20( <i>u</i> s)  |

| Programing(write) | 200( <i>u</i> s) |

| Block erase       | 1.5( <i>m</i> s) |

표 1. NAND 플래시 메모리 사양 Table. 1. Parameter of NAND flash memory

#### IV. 실험 결과

다양한 시뮬레이션을 수행하기위해 멀티미디어 벤치마크인 미디어벤치(Media-benchmark)를 이용 하여 시뮬레이션을 수행하였다. 성능 비교를 위하여 평균 메모리 접근 시간(average memory access time)과 에너지 소비(energy consumption)를 사용 하였다.

본 논문에서 NAND 플래시 메모리는 삼성의 NAND 플래시 메모리인 8Gb 크기와 2KB 페이지 크기, 그리고 구동시간을 이용하여 시뮬레이션을 수행하였다 [3]. 또한 플래시 변환 계층은 쓰기 및 지우기 동작에 가장 효율적인 혼합 사상 FTL (hybrid-mapping FTL)을 사용하여 시뮬레이션을 수행하였다. 구체적인 NAND 플래시 메모리의 사양은 표1과 같다.

#### 1. 평균 메모리 접근 시간

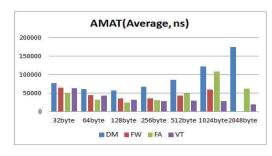

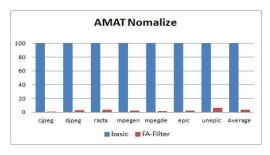

그림 4는 제안된 필터 버퍼들의 페칭 페이지에 따른 평균 메모리 접근 시간(AMAT)을 나타낸 그림이다. 그림 3에서 버퍼 크기가 큰 빅팀(VT) 버퍼를 제외하고는 완전연관 버퍼(FA)의 128B 페칭 페이지에서 가장 좋은 성능 향상을 보였다. 이러한 결과는 완전연관 버퍼에서 높은 접근 적중률을 가지므로 NAND 플래시의 접근을 줄일 수 있다. 특히 완전연관 버퍼의 경우 NAND 플래시에서 가장 큰 단점인 쓰기 동작에 대해서 많은 적중을 보이기 때문에 캐쉬 메모리의 후기입(wirte-back) 동작처럼 버퍼에서 대치되는 수정된 페이지의 수를 효과적으로줄일 수 있으며, 이러한 결과는 블록 지우기 동작까지 줄이는 효과를 얻을 수 있다.

그림 5는 기존 NAND 플래시 메모리를 기준으로 최적의 성능을 보이는 128B 완전연관 필터 버

그림 4. 다양한 폐칭 페이지를 가지는 필터 버퍼들의 평균 메모리 접근 시간

Fig 4. AMAT of filter- buffer NAND flashes with various fetching pages

그림 5. 기존 NAND 플래시 메모리에 대한 평균 메모리 접근시간 정규화.

Fig 5. Normalization of average memory access time compared with the basic flash memory

퍼의 정규화된 평균 메모리 접근 시간을 나타낸 그림이다. 128B 완전연관 필터 버퍼를 내장한 NAND 플래시 메모리는 기존 NAND 플래시 메모리에 비해 약 96%의 성능 향상을 보이고 있다.

#### 2. 평균 에너지 소비

본 연구의 목적은 성능 향상보다 소비전력을 줄이기 위한 최적의 필터 버퍼 구조 및 페칭 페이지를 찾아내는 것이다.

NAND 플래시 메모리의 에너지 소비 측정을 위해서 Flashpower [5]와 Cacti5.3 [12]을 수정하여 사용하였다. 에너지 소비 식은 식(1)과 같다.

$$E = N_{filter} * E_{filter} + N_{register} * E_{register} + N_{flash} * E_{flash} (1)$$

여기서  $N_{filter}$ ,  $E_{filter}$ 는 각각 필터 버퍼에 대한 접근 횟수와 에너지 소비를 나타내며,  $N_{register}$ ,  $E_{remister}$  는 버퍼의 접근 실패시 레지스터에 대한

그림 6. 다양한 페칭 페이지를 가지는 필터 버퍼들의 평균 에너지 소비.

Fig 6. Energy consumption of filter-buffer NAND flash with various fetching pages.

접근 횟수와 에너지 소비를 나타낸다. 그리고  $N_{flash}, E_{flash}$ 는 필터 버퍼 및 레지스터 접근 실패시 (random access) 플래시 메모리 셀에 대한 접근으로 읽기 동작, 쓰기 동작, 그리고 지우기 동작으로 구분되어진다. 이에 대한 식은 다음과 같다.

$$N_{flash} * E_{flash} = N_r * E_r + N_w * E_w + N_e * E_e$$

(2)

여기서  $N_w$ 는 NAND 플래시 메모리 쓰기 동작횟수와 덮어 쓰기 혹은 병합 연산을 위한 지우기 연산 후 쓰기 연산 횟수를 모두 포함한다.

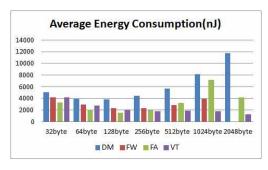

그림 6는 각 필터 버퍼를 내장한 NAND 플래시메모리의 평균 에너지 소비를 나타낸 그림이다. 평균 에너지 소비 역시 128B 페칭 크기에서 가장 좋은 에너지 소비를 보이고 있다.

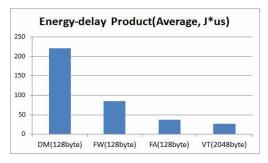

마지막으로 성능과 소비전력을 모두 고려한 에 너지\*성능 지표(energy-delay product(EDP))를 이용하여 성능 분석을 수행하였다. 그림 7은 각 필터 버퍼에 대한 가장 좋은 성능 및 에너지 소비를 가지는 페칭 페이지에서의 EDP를 나타낸 그림이다.

그림 7에서 보듯이, 빅팀 버퍼에서 가장 좋은 성능을 나타내고 있다. 하지만, 버퍼 크기당 성능 향상정도를 고려해야한다. 제안된 모든 구조의 버퍼크기는 4KB인 반면, 빅팀 버퍼의 경우 4KB의 직접사상 버퍼와 2KB의 완전연관 버퍼로 구성되며, 총6KB의 크기를 가진다. 따라서 이러한 버퍼 크기에대한 성능 비교를 위해 버퍼 크기(Kbyte)\*EDP로평가를 수행하였다. 앞선 다양한 시뮬레이션 그림에서 성능과 에너지 소비 그리고 EDP에서 빅팀 버퍼가 가장 좋은 성능을 보였지만, 버퍼 크기를 고려한평가에서 완전연관 버퍼가 더 좋은 성능 향상을 보였다. 시뮬레이션 결과, 에너지\*성능 평가에서 빅팀

그림 7. 가장 좋은 성능을 보이는 폐칭 폐이지에 대한 필터 버퍼 NAND 플래시의 에너지\*성능 지표 Fig 7. Energy\*delay of various filter-buffer NAND flashes with the best fetching page size.

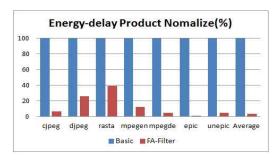

그림 8. 기존 플래시 메모리에 대한 4KB 완전연관 필터 버퍼 플래시 메모리의 에너지\*성능 지표 정규화 Fig 8. Normalization of the Energy\*delay for the NAND flash with the fully associative buffer compared with the conventional NAND flash

버퍼가 완전연관 버퍼에 비해 약 30%의 성능향상을 보이지만, 버퍼 크기에 대한 성능 비교에서는 오히려 완전연관 버퍼가 빅팀 버퍼에 비해 약 8%의성능 향상을 보였다. 그러므로 본 논문에서 비용 대성능향상에서 최적의 필터 버퍼 구조인 128B 완전연관 버퍼를 선택하여 기존 플래시 메모리와 비교분석을 수행하였다. 이에 대한 시뮬레이션 결과는그림8과 같다. 결론적으로 작은 4KB 완전연관 필터 버퍼를 사용하여 EDP 평가에서 기존 NAND 플래시에 비해 평균 약 93%의 성능 향상을 이루었다.

#### V. 결 론

본 논문은 현재 널리 보급되고 있는 고성능 휴대기기를 위하여 저전력 NAND 플래시를 구현하기 위한 필터 버퍼의 효용성을 분석하였다. 이를 위하

여 4KB 필터 버퍼 크기의 다양한 필터 버퍼 구조 (DM, VT, 4W, FA) 및 페칭 페이지(32byte~ 2048byte)에 대한 접근 비율, 평균 메모리 접근 시 간 그리고 에너지\*성능 지표를 이용하여 평가를 수 행하였다. 시뮬레이션 결과, 버퍼의 크기가 큰 빅팀 버퍼도 매우 우수한 결과를 보였으며, 비용 대 성능 향상을 모두 고려할 경우 128B 페칭 페이지를 가 지는 4KB 완전연관 필터 구조가 최고의 성능향상 을 보임을 확인하였다. 따라서 휴대기기를 위한 고 성능/저전력 필터 버퍼로 4KB-128B 완전연관 필 터 버퍼를 NAND 플래시에 적용한 결과 기존 NAND 플래시 메모리에 비해 성능 평가 결과(에너 지\*성능 곱) 약 93%의 성능 향상을 이룰 수 있었 으며, 결론적으로 작은 필터 버퍼만으로도 기존 NAND 플래시 메모리에 대해 높은 소비전력 감소 효과와 성능 효과를 얻을 수 있다.

#### 참고문헌

- [1] J.W. Parck, S.H. Park, C.C. Weems, S.D. Kim, "A hybrid flash translation layer for SLC-MLC flash memory based multibank solid state disk," Microprocesser and Microsystem, Vol. 35, No. 1, pp.48-59, 2011.

- [2] D. Jung, Y.H. Chae, H. Jo, J.S. Kim, J. Lee, "A group-based wear-leveling algorithm for large-capacity flash memory storage system," Proceedings on compilers, architecture, and synthesis for embedded systems, pp.160-164, 2007.

- [3] http://www.samsung.com/sec/business/semiconductor/

- [4] 정보성, 이정훈, "다양한 메모리 셀을 결합한 디 스크형 플래쉬 메모리 시스템," 대한임베디드공 학회논문지, Vol. 4, No. 3, pp.134-138, 2009.

- [5] V. Mohan, S. Gurumurthi, M. R. Stan, "Flash Power: A Detailed Power Model for NAND Flash Memory," Proceedings on Design, Automation and Test in Europe Conference and Exhibition, pp.502–507, 2010.

- [6] http://www.hpl.hp.com/research/cacti/

- [7] G. Sun, Y. S. Joo, "A Hybrid solid-state storage architecture for the performance, energy consumption, and lifetime improvement," Proceedings on High

- Performance Computer Architecture, pp.1–12, 2010.

- [8] 류준길, 박찬익, "로그기반 플래시 메모리 파일 시스템 성능 향상 기법," 대한임베디드공학회논 문지, Vol. 2, No. 3, pp.184-193, 2007.

- [9] H.L. Li, C.L. Yang, H.W. Tseng, "Energy-Aware Flash Memory management in Virtual Memory System," IEEE Transactions on Very Large Scale Integration systems, Vol. 16, No. 8, pp.457-467, 2008.

- [10] X. Jiang, N. Madan, L. Zhao, M. Upton, R. Iyer, S. Makineni, D. Newell, Y. Solihin R. Balasubramonian, "CHOP:Adaptive Filter Based DRAM Caching for CMP Server Platforms," Proceedings on. International Symposium on High-Performance Computer Architecture, 2010.

- [11] Y. Chang "An Ultra Low-Power TLB Design," Proceedings on Design, Automation and Test in Europe, pp.1-6, 2006.

- [12] G. Abandah, "Evaluating Cache Power Dissipation using CACTI 5.3 simulator," Report of the University of Jordan, 2010.

## 저 자 소 개

#### 정보성

2006년 경상대학교 제어계측공학과 학사.

2008년 경상대학교 제어 계측공학과 석사.

현재, 경상대학교 제어계 측공학과 박사과정.

관심분야: 마이크로프로세서, 캐쉬 및 플래 시메모리

Email:blueking80@gnu.ac.kr

#### 이정훈

1999년 성균관대학교 제어계측공학과 학사.

2001년 연세대학교 컴퓨터과학과 석사.

2004년 연세대학교 컴퓨터과학과 박사.

현재, 국립경상대학교 ERI,제어계측공학과 부교수.

관심분야: 임베디드 하드웨어, SOC 시스템

Email: leejh@gsnu.ac.kr