J. KIEEME

Vol. 25, No. 6, pp. 409-413, June 2012 DOI: http://dx.doi.org/10.4313/JKEM.2012.25.6.409

## 4비트 SONOS 전하트랩 플래시메모리를 구현하기 위한 기판 바이어스를 이용한 2단계 펄스 프로그래밍에 관한 연구

### 김병철<sup>1</sup>, 강창수<sup>2</sup>, 이현용<sup>3</sup>, 김주연<sup>4,a</sup>

- <sup>1</sup> 경남과학기술대학교 전자공학과

- 2 유한대학교 전자정보과

- <sup>3</sup> 전남대학교 응용화학공학부

- 4 울산과학대학교 전기전자학부

# A Study on a Substrate-bias Assisted 2-step Pulse Programming for Realizing 4-bit SONOS Charge Trapping Flash Memory

Byungcheul Kim<sup>1</sup>, Chang Soo Kang<sup>2</sup>, Hyun-Yong Lee<sup>3</sup>, and Joo-Yeon Kim<sup>4,a</sup>

- <sup>1</sup> Department of Electronic Engineering, Gyeongnam National University of Science and Technology (GnTECH), Jinju 660-758, Korea

- <sup>2</sup> Department of Electronic Engineering, Yuhan College, Bucheon 422-749, Korea

- <sup>3</sup> School of Applied Chemical Engineering, Chonnam National University, Gwangju 500-757, Korea

(Received March 30, 2012; Revised May 14, 2012; Accepted May 15, 2012)

**Abstract:** In this study, a substrate-bias assisted 2-step pulse programming method is proposed for realizing 4-bit/1-cell operation of the SONOS memory. The programming voltage and time are considerably reduced by this programming method than a gate-bias assisted 2-step pulse programming method and CHEI method. It is confirmed that the difference of 4-states in the threshold voltage is maintained to more than 0.5 V at least for 10-year for the multi-level characteristics.

**Keywords:** 4-bit SONOS memory, 2-step pulse programming, Substrate-bias assisted hot electron, Multi-bit, Multi-level

#### 1. 서 론

IT 기술과 더불어 휴대용 전자제품의 급속한 발전으로 이들 제품의 주요 저장 매체로써 플래시 메모리의 수요가 급속히 증가되고 있다. 고집적 플래시 메모리를 구현하기 위해서는 메모리 셀의 크기를 줄이는 것이 가장 일반적인 방법이다. 국제 반도체기술

로드맵 (international technology road-map for semiconductors, ITRS)에서는 현재 주류인 부유 게이트 (floating gate) 플래시 메모리의 셀 크기를 더 감소하는 것이 한계에 도달할 것이라고 예상하고 있다[1]. 현재의 사진 식각기술을 이용하면서 용량을 증가시킬수 있는 방법은 다중-레벨 (multi-level) 및 다중-비트 (multi-bit) 메모리 셀을 구현하는 것이다. 다중-비트 메모리 셀은 주로 SONOS (silicon-oxide-nitride-oxide-silicon) 메모리와 같이 저장전극이 절연체이거나 전기적으로

409

<sup>&</sup>lt;sup>4</sup> School of Electricity & Electronics, Ulsan College, Ulsan 680-749, Korea

a. Corresponding author; joo@uc.ac.kr

격리된 작은 셀로 구성된 메모리 소자에 적용되고, 다중-레벨 메모리 셀은 저장 전극에 상관없이 기존의 부유게이트나 SONOS 소자에도 적용이 가능하다. 또 한 하나의 메모리 셀이 여러 가지 다른 상태의 문턱 전압 값을 가짐으로써 2 비트, 4 비트, 그리고 그 이 상의 비트를 저장할 수 있는 특징이 있다. 다중-비트 [2,3]와 다중-레벨 메모리 셀 [4,5]을 구현하기 위한 많은 연구가 여러 연구자들에 의하여 진행되고 있다. B. Eitan 등은 물리적으로 각각 분리된 소스와 드레 인 영역에 국소적으로 전자를 주입하는 다중-비트 개 념과 각각의 소스와 드레인 영역에서 4개의 구분된 문턱 전압 상태를 유지하는 다중-레벨 개념을 결합하 여 4비트/1셀 NROM (nitride read-only-memory) 플 래시 메모리를 구현하였다고 발표하였다 [6]. 일반적 으로 4비트 NROM 소자의 프로그램은 CHEI (channel hot electron injection) 방법을 사용한다 [2,3]. 하지만, 이 방법은 실리콘 기판과, 터널 산화막 에 존재하는 3.2 eV의 에너지 장벽을 뛰어 넘을 수 있는 충분한 에너지를 가진 고온 전자 (hot electron) 들을 생성하기 위해서는 높은 드레인 전압이 필요하 다. 이로 인해 과도한 채널전류가 생성되고 전력소비 가 커지는 동시에 터널 산화막의 내구성 특성이 저하 되며, 예상하지 않은 드레인 간섭현상 등 많은 문제 점이 발생한다 [7,8]. SONOS 메모리를 위한 고온전하 주입방법에 대한 여러 연구결과들이 발표되었다 [9]. STHE (substrate transient hot electron)를 이용하는 2단 계 펄스 프로그래밍 방법 [10]은 소스와 드레인 영역으로 고온전하가 동시에 주입되기 때문에 다중-비트 메모리 셀을 구현하기 어렵다는 단점이 있다. 2비트 동작을 실현 하기 위하여 FBEI (forward-bias assisted electron injection) 방법이 보고되었다 [11]. 그러나 이 방법은 4.5 V의 비교적 높은 드레인 전압이 요구되며, 프로그램 시 간도 10 us로 느리다는 단점을 가지고 있다. 4비트 동작 을 위해 FBEI 방법을 적용하여 다중 레벨을 구현하기 위 해서는 높은 문턱전압을 갖는 기억 상태들이 필요한데, 이를 성취하려면 더 큰 드레인 전압이 요구되므로 어레 이 구조에서 드레인 간섭 확률이 매우 커지게 되는 문제 가 있다. 따라서 본 연구에서는 4비트 SONOS 메모리를 구현할 수 있을 뿐만 아니라 위의 문제들이 해결될 수 있는 새로운 프로그램 방법을 조사하기 위하여 기판 바 이어스 (substrate-bias assisted hot electron, SAHE)를 이용한 2단계 펄스 프로그래밍 방법을 제안하고, 그 방법 에 의한 프로그램 특성을 조사하고자 한다.

#### 2. 실험 방법

0.35 µm CMOS (complementary metal-oxidesemiconductor) 공정에 의하여 SONOS 메모리 셀이 제작되었다. ONO (oxide-nitride-oxide) 절연 게이트 공정을 제외한 전체 제작공정은 CMOS 공정과 동일하 다. 게이트 절연막은 실리콘 기판 위에 터널 산화막, 질화막, 그리고 블로킹 산화막을 차례로 적층하였다. 터널 산화막은 900℃에서 질소로 희석시킨 산소 (O2 5%)를 사용하여 상압에서 건식 산화하였다. 770℃에서 SiH<sub>2</sub>Cl<sub>2</sub>와 NH<sub>3</sub>의 혼합 가스 (SiH<sub>2</sub>Cl<sub>2</sub>: NH<sub>3</sub>=30 sccm: 330 sccm)를 반응시켜 터널 산화막 위에 질화막을 증 착하였으며, 증착율은 11.6 Å/min.이다. 950℃ 상압에 서 H<sub>2</sub>:O<sub>2</sub>= 5 L/min. :10 L/min.인 혼합가스를 사용해서 습식 산화방법으로 질화막 위에 블로킹산화막을 성장 시켰다. 적층된 ONO 절연막의 두께는 HR-TEM (high-resolution transmission electron microscopy) △ 로 확인하였으며 터널산화막, 질화막, 블로킹 산화막 의 두께는 각각 3.4 nm, 7.3 nm, 3.4 nm 이다.

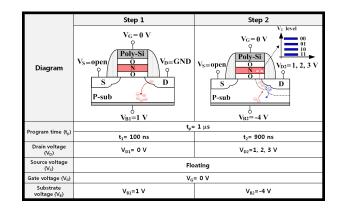

4 비트 동작을 구현하기 위하여 제안한 기판 바이어스 (SAHE)를 이용한 2단계 펄스 프로그래밍 방법과 프로그램 조건을 그림 1에 나타내었다.

Fig. 1. The proposed programming method and conditions.

프로그램 메커니즘은 1단계에서  $t_1$ 시간 동안 기판에 순방향 바이어스  $(V_{BI})$ 를 인가하여 기판단자에 전자를 수집한 후, 2단계에서 곧바로 기판  $(V_{B2})$ 과 드레인  $(V_{D2})$  단자에 역방향 바이어스를 인가하여 드레인 공핍영역으로 전자를 가속시킨다. 가속된 전자들은 공핍영역에서 중성원자들과 충돌을 한 후 에너지를

얻은 고온 전자들이 음의 기판 전압에 의해 게이트로 주입되어 프로그램이 된다. 총 프로그램 시간 (tp= 1 μs)은 1단계 전자수집 시간 (t<sub>1</sub>= 100 ns)과 2단계 전 자주입 시간  $(t_2 = 900 \text{ ns})$  으로 구성된다. 전자수집 시간은 순방향전압으로 인한 전력소비를 최소화하기 위해 100 ns의 빠른 시간으로 하였다. 한편, 프로그램 전압은 전자를 수집하기 위한 기판 전압  $(V_{BI}=1\ V)$ 과 다중-레벨을 실현하기 위하여 전자의 주입량 조절 에 필요한 기판전압  $(V_{B2} = -4 \ V)$ 과 드레인 전압 (V<sub>D2</sub>= 1, 2, 3 V)으로 구성된다. 기존의 2단계 펄스 프로그래밍 방법과의 큰 차이점은 전자를 주입할 때 보통 게이트 전압을 이용하지만, 제안한 프로그래밍 방법은 기판에 전압을 인가하여 기판에 전자를 먼저 수집한 후 드레인 공핍영역으로 전자를 가속시켜 충 분히 에너지를 얻은 고온 전자들이 게이트로 주입되 기 때문에 낮은 드레인 전압에서도 빠른 프로그램이 가능한 장점을 가지고 있다.

#### 3. 결과 및 고찰

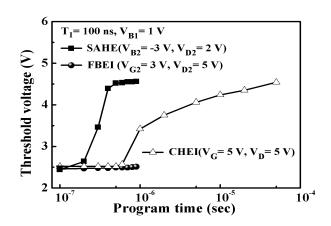

기판과 게이트 중 어떤 단자에 바이어스를 인가하는 것이 더 효과적인 프로그램 방법인가를 확인하기위하여 기판 바이어스 (SAHE)와 게이트 바이어스 (FBEI)를 이용한 2단계 펄스 프로그래밍 방법, 그리고 CHE 주입방법에 의한 프로그램 특성을 각각 조사하였으며, 그 결과를 그림 2에 나타내었다.

그림 2에서 보는바와 같이 SAHE 방법을 이용한 프로그램 특성은 프로그램 시간이 증가함에 따라서 문턱전압도 증가하는 반면 FBEI 방법을 이용한 경우 는 프로그램 시간이 증가함에도 불구하고 문턱전압의 변화가 없음을 알 수 있다. 또한, SAHE 방법과 비교 해서 CHEI 방법의 프로그램 시간이 느린 것은 t<sub>1</sub>의 기판 수집이 없기 때문이다. 즉, SAHE 2단계 펄스 프로그래밍 방법은 순방향 기판 바이어스에 의해 수 집된 다량의 기판전자가 순식간에 드레인-기판에 역 방향 전압이 걸려서 드레인 영역에서 충돌을 바로 일 으키지만, CHEI 방법은 채널이 형성된 후에 소스 영 역에서부터 전자가 채널을 통해 드레인 공핍 영역까 지 이동하여 충돌함으로써 고온전자가 발생되므로 시 간이 많이 필요하다. 따라서 SAHE 방법처럼 빠른 프 로그램 속도를 구현하기 위해서는 드레인 전압이 더 높아져야 한다. 이는 드레인 간섭에 심각한 문제를 초래하게 된다.

**Fig. 2.** Comparison of the program characteristics for 2 step pulse programming method by the proposed substrate-bias (SAHE), gate-bias (FBEI) and the CHEI method.

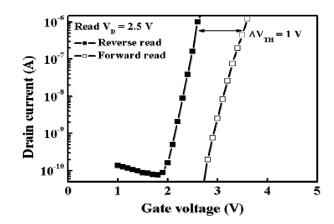

**Fig. 3.** The multi-bit characteristics of the SONOS device.

제안한 프로그래밍 방법을 이용하여 다중-비트 동작을 구현하기 위해서는, 먼저 소스/드레인 영역에 고온 전자들이 국소적으로 주입되는지를 확인하여야 한다. 이를 위하여 드레인 영역에 전자를 주입 한 후, 순방향과 역방향 읽기에 의한 문턱전압의 차이를 조사하였다. 그림 3에 SONOS 소자의 다중-비트 특성을 나타내었다.

그림 3에서 보는바와 같이, 2.5 V의 드레인 읽기전 압에서 순방향과 역방향 읽기에 의한 문턱전압의 차이  $(\Delta V_{TH})$ 가 1 V인 것을 확인하였다. 따라서 제안한 프로그래밍 방법에 의해 드레인 영역에만 전자가 국

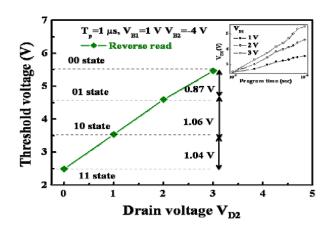

Fig. 4. The multi-level characteristics as a function of drain voltage.

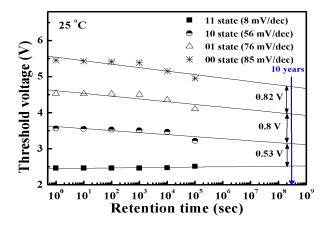

Fig. 5. The retention characteristics of SONOS device for the multi-bit programming states.

소적으로 주입되는 것을 확인할 수 있으며, 제작한 SONOS 소자의 소스와 드레인이 대칭구조이기 때문에 소스 영역의 다중-비트 특성은 생략하였다.

그림 4는 제안한 프로그래밍 방법을 사용하여 드레인 영역으로 주입할 때, 드레인 전압 에 따른 SONOS 소자의 다중-레벨 특성을 조사한 결과이다.

드레인 전압  $(V_{D2})$ 을 1, 2, 3 V로 변화시키면서 프로그램 시간에 따른 SONOS 소자의 문턱전압 조사결과를 그림 4 내의 작은 그림에 나타내었다. 프로그램시간이 증가할수록 문턱전압이 증가함을 보이고 있다. 이 결과를 바탕으로 1단계에서 기판 전압  $(V_{B1})$ 을 1 V, 100 ns 동안 인가하여 전자를 수집한 직후 2단계에서 전자를 주입하기 위해 필요한 -4 V의 기판전

압  $(V_{B2})$ 을 900 ns 동안 인가한 상태에서 드레인 전압  $(V_{D2})$ 을 1, 2, 3 V로 변화시켰다. 총 프로그램 시간은 1단계와 2단계를 합하여  $1~\mu s$ 이다.

드레인 전압을 인가하기 전의 문턱전압 (11 상태) 과 1 V의 드레인 전압을 인가한 후 측정한 문턱전압 (10 상태)의 차이는 1.04 V이다. 2 V의 드레인 전압 을 인가한 후 측정한 문턱전압 (01 상태)과 1 V의 드 레인 전압을 인가한 후 측정한 문턱전압의 차이는 1.06 V이다. 마지막으로 3 V의 드레인 전압을 인가한 후 문턱전압 (00 상태)과 2 V의 드레인 전압을 인가 한 후 측정된 문턱전압의 차이는 0.87 V로 확인되었 다. 일반적으로 다중-레벨 동작을 하기 위해서는 각 문턱전압의 상태가 0.5 V 이상 차이가 나면 문제가 없다고 보고되고 있다 [12]. 따라서 제안한 프로그래 밍 방법을 이용하면 안정적으로 다중-레벨 프로그래 밍 동작이 가능함을 확인할 수 있다. 이러한 전압 조 건은 다음과 같은 장점이 있다. 게이트로 주입하는 FBEI 방법에 의해 다중-레벨을 실현하기 위해서 드 레인 전압은 5, 6, 7 V로 전압이 커지게 때문에 어레 이에서는 드레인 간섭을 피할 수 없는 반면에 제안한 프로그램 방법은 드레인 전압이 1, 2, 3 V의 낮은 전 압으로 인가되기 때문에 어레이 동작에서 드레인 간 섭을 완벽하게 막을 수 있을 뿐 만 아니라 게이트에 인가되는 전압이 없기 때문에 게이트 간섭 현상도 발 생하지 않는 장점이 있다 [13]. 제작한 SONOS 소자 의 소스와 드레인이 대칭구조이기 때문에 소스 영역 의 다중-레벨 특성은 생략하였다.

마지막으로, 제안한 4비트 프로그래밍 방법에 대한 신뢰성을 평가하기 위하여 SONOS 소자의 문턱전압 을 각각 다른 상태의 값을 가지도록 다중-레벨 프로 그래밍 후 시간경과에 따른 문턱전압의 변화를 조사 하였으며 그 결과를 그림 5에 나타내었다.

제안한 프로그래밍 방법에 의해 SONOS 소자의 문 턱전압을 4개의 상태로 만든 후 상온에서  $10^1$ 초,  $10^2$  초,  $10^3$ 초,  $10^4$ 초 그리고  $10^5$ 초 경과한 후의 문턱전압을 각각 측정하였다. 그리고 문턱전압 측정결과를 기본으로 하여  $10^8$ 초 (약 10년)까지 외삽시켜 SONOS 소자의 기억상태가 얼마나 오랫동안 유지될 수 있는지를 예상하였다.

그림 5에서 확인할 수 있는 것처럼 프로그래밍 직후 (10<sup>0</sup>초)의 문턱전압이 가장 높은 00 상태는 문턱전압의 감쇠율이 85 mV/decade, 01 상태에서는 76 mV/decade, 10 상태에서는 56 mV/decade로써 시간이 경과됨에 따라서 초기 전자 주입량이 많을수록 질화막

에 주입된 전자가 빨리 감소되고 있음을 확인할 수 있다. 10년 후에도 11 상태, 10 상태, 01 상태, 그리고 00 상태에서의 문턱전압이 각각 최소한 0.5 V 이상 구분됨으로써 각각의 기억상태가 충분히 구분될 수 있음을 확인하였다.

#### 4. 결 론

본 연구에서 제안한 기판 바이어스를 이용한 2단계 펄스 프로그래밍 방법에 의해 저전압에서도 고속 프 로그래밍이 가능하고 드레인과 게이트 간섭 현상이 없는 4비트 SONOS 메모리를 구현하였다. 제안한 프 로그래밍 방법은 기판단자에 순방향전압을 인가하여 전자를 먼저 기판에 수집한 후 곧바로 기판과 드레인 단자에 역방향 바이어스를 인가하여 드레인 공핍영역 으로 전자를 가속시킨다. 가속된 전자들은 공핍영역 에서 중성원자들과 충돌한 후 에너지를 얻은 고온 전 자들이 음의 기판 전압에 의해 게이트로 주입되어 프 로그램이 된다. 따라서 게이트 바이어스를 이용한 2 단계 펄스 프로그래밍 방법이나 CHEI 방법보다 더 낮은 전압에서 더 빠른 프로그램이 가능한 장점을 가 지고 있다. 프로그램 전압은 전자를 수집하기 위한 1 V의 기판 전압 (VB1)과 다중-레벨을 실현하기 위하여 필요한 전자의 주입량을 조절하기 위하여 -4 V의 기 판전압  $(V_{B2})$ 과 1, 2, 3 V의 드레인 전압  $(V_{D2})$ 으로 구성된다. 총 프로그램 시간 (t<sub>p</sub>)은 1 μs로써, 1단계 전자수집 시간 (t1)은 100 ns이고, 2단계 전자주입 시 간(t<sub>2</sub>)은 900 ns이다. 마지막으로 10년 후에도 11 상 태, 10 상태, 01 상태, 그리고 00 상태에서의 문턱전 압이 최소한 0.5 V 이상 구분됨으로써 다중-레벨에서 의 기억유지 특성이 우수함을 확인하였다.

#### 감사의 글

이 논문은 2011년도 경남과학기술대학교 기성회연 구비 지원에 의하여 연구되었음.

#### REFERENCES

- [1] ITRS, International Technology Roadmap for Semiconductors, http://public.itrs.net (2011).

- [2] B. Eitan, P. Pavan, I. Bloom, E. Aloni, A. Frommer, and D. Finzi, *IEEE Electron Device Lett.*, 21, 543 (2000).

- [3] E. Lusky, Y. Shacham-Diamand, I. Bloom, and B. Eitan, *IEEE Electron Device Lett.*, **22**, 556 (2001).

- [4] T. H. Hsu, M. H. Lee, J. Y. Wu, H. L. Lung, R. Liu, and C. Y. Lu, *IEEE Electron Device Lett.*, 25, 795 (2004).

- [5] G. Zhang, W. S. Hwang, S. H. Lee, B. J. Cho, and W. J. Yoo, *IEEE Trans. Elec. Dev.*, 55, 2361 (2008).

- [6] B. Eitan, G. Cohen, A.Shappir, E. Lusky, A. Givant, M. Janai, I. Bloom, Y. Polansky, O. Dadashev, A. Lavan, R. Sahar, and E. Maayan, *Electron Devices Meeting IEDM Technical Digest* (IEEE International, 2005) p. 539.

- [7] L. Breuil, L. Haspeslagh, P. Blomme, D. Wellekens, J. D. Vos, M. Lorenzini, and J. V. Houdt, *IEEE Trans. Elec. Dev.*, **52**, 2250 (2005).

- [8] Y. Li, R. Huang, Y. Cai, F. Zhou, X. Shan, X. Zhang, and Y. Wang, IEEE Electron Device Lett., 28, 622 (2007).

- [9] M. K. Cho and D. M. Kim, IEEE Electron Device Lett., 24, 260 (2003).

- [10] T. Hsu, J. Wu1, Y. C. King, H. T. Lue, Y. H. Shih, E. Lai, K. Hsieh, R. Liu, and C. Lu, *Solid-State Electron.*, **51**, 1523 (2007).

- [11] S. S. Chung, Y. H. Tseng, C. S. Lai, Y. Hsu, E. Ho, T. Chen, L. C. Peng, and C. H. Chu, *Electron Devices Meeting IEDM Technical Digest* (IEEE International, 2007) p. 457.

- [12] H. C. Chien, C. H. Kao, J. W. Chang, and T. K. Tsai, *Microelectron. Eng.*, 80, 256 (2005).

- [13] G. Zhang and W. J. Yoo, *Solid-State Electron.*, **54**, 14 (2010).