# Harmonics Elimination in a Multilevel Inverter with Unequal DC Sources Using a Genetic Algorithm

Ali Reza Marami Iranaq\*, Mojtaba Bahrami Kouhshahi\*, Mehdi Bahrami Kouhshahi\*, Mohammad Bagher Bannae Sharifian\* and Mehran Sabahi\*

Abstract – In this paper, an optimal solution to the harmonic reduction problem in a cascaded multilevel inverter with non-equal DC sources using a genetic algorithm (GA) is presented. Switching angles are generated for different values of modulation index by the proposed algorithm, considering minimum voltage total harmonic distortion (THD) whereas selected harmonics are controlled within the allowable limits at all desired modulation indices including the point of discontinuity. Results are stored as a look-up table to be used to control the inverter for a certain operating point. The computed angles are used in a simulated circuit in Matlab\Simulink to validate the results.

**Keywords:** Multilevel inverter, Unequal DC source, Harmonics Elimination, THD, Genetic Algorithm

#### 1. Introduction

The main concepts of multilevel inverters, introduced about 3 decades ago [1], [2], entails performing power conversion in multiple voltage steps to obtain improved quality, lower switching power electromagnetic compatibility, higher voltage capability, elimination of the harmonics from the output voltage, and a minimizing of the THD [3]. Several topologies for a multilevel inverter have been proposed over these years, the most popular ones are the diode-clamped [4], [5], flying capacitor [6], [7] and the cascaded H-bridge [8]-[11] structures. Theoretically, multilevel inverters can synthesize an infinite output-voltage level. By increasing the number of levels in the inverter, the output voltage has more step generation, a staircase waveform, which has a reduced harmonic distortion.

However, a large number of levels increase the number of switching devices, diodes, and other passive elements. Moreover, it causes control complexity and introduces voltage-imbalance problems. Consequently, these multilevel inverter schemes are not suitable for increasing the output voltage levels because of their large number of switching devices. To increase the number of the output-voltage levels in order to obtain a high-quality output-voltage waveform by means of multilevel inverter schemes, the above problems should be solved in advanced.

In this work to overcome these problems, an asymmetric topology H-bridge multilevel inverter with three unequal DC sources is used. This topology has the capability of utilizing different DC voltages on the individual H-bridge cells which results in splitting the power conversion amongst higher-voltage lower-frequency and lower-voltage higher-frequency inverters [10], [11].

There have been many attempts at finding an optimal switching sequence for both voltage, and current. The most common method is either pulse width modulation (PWM) or space vector modulation (SVM). While attempts at PWM and SVM have success, it is hard to claim that any have found the absolute best switching sequence solution [12]-[14].

This problem leads to non-linear equations and a direct solution of non-linear equations can lead to discontinuity at certain modulation indices. The prevalent means of solving this problem utilize intelligent methods. In this paper GA is used to solve this problem. The optimal switching angles are generated, selective harmonics are eliminated and consequently THD of output voltage is minimized. To validate the results, the computed switching angles are used in simulated circuit.

## 2. Structure of the Cascade Multilevel Inverter

Generally, conventional multilevel inverters include an array of switching devices and voltage sources which generate voltages with stepped waveform in the output. A cascade multilevel inverter consists of several single-phase

<sup>\*</sup> Dept. of Electrical and Computer Engineering, University of Tabriz, Tabriz, Iran. (m\_bahrami88@ms.tabrizu.ac.ir)

Received 03 July 2011; Accepted 04 November 2011

full bridge inverters connected in series. At an asymmetric H-bridge cascade multilevel inverter, the DC sources that feed the single phase inverters have different values. But to reduce the number of DC sources required for the cascaded H- bridge multilevel inverter, an asymmetric topology with three unequal DC sources is used.

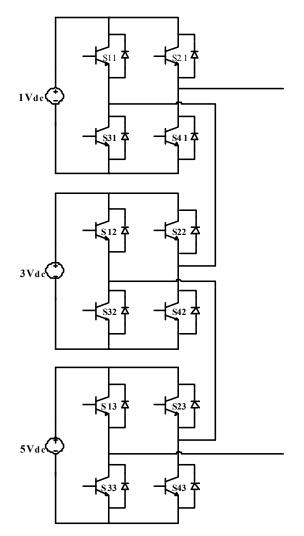

Fig. 1 shows a single phase structure of this multilevel inverter with the following DC-voltage sources:  $V_{dc}$ ,  $3V_{dc}$  and  $5V_{dc}$ .  $V_{dc}$  is smallest DC-voltage that is equal to the step size. Each individual inverter is capable of generating three different outputs  $\pm V_{dc}$  and 0 for 1st inverter,  $\pm 3V_{dc}$  and 0 for 2nd inverter, and  $\pm 5V_{dc}$  and 0 for 3rd inverter.

This configuration uses only three cascade inverters in order to produce a nineteen-level output while in the common configuration of a multilevel inverter, nine cascade inverters are needed to generate a nineteen-level output voltage. The 1st inverter (that contains  $V_{dc}$ ) is used several times more than two others.

**Fig. 1.** Single phase structure of a cascaded multilevel inverter

**Table 1.** The Switching Pattern of Inverters

| Output Level | Inverters State |            |    |

|--------------|-----------------|------------|----|

|              |                 | Inverter 2 |    |

| -9           | -1              | -1         | -1 |

| -8           | 0               | -1         | -1 |

| -7           | 1               | -1         | -1 |

| -6           | -1              | 0          | -1 |

| -5           | 0               | 0          | -1 |

| -4           | -1              | -1         | 0  |

| -3           | 0               | -1         | 0  |

| -2           | 1               | -1         | 0  |

| -1           | -1              | 0          | 0  |

| 0            | 0               | 0          | 0  |

| 1            | 1               | 0          | 0  |

| 2            | -1              | 1          | 0  |

| 3            | 0               | 1          | 0  |

| 4            | 1               | 1          | 0  |

| 5            | 0               | 0          | 1  |

| 6            | 1               | 0          | 1  |

| 7            | -1              | 1          | 1  |

| 8            | 0               | 1          | 1  |

| 9            | 1               | 1          | 1  |

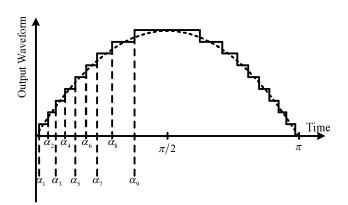

**Fig. 2.** Output voltage waveform of a 19-level multilevel inverter

The switching pattern of inverters to generate nineteenlevels is shown in Table 1. A typical output of inverter with nineteen-levels is shown in Fig. 2.

### 3. Problem Formulation

Fig. 2 shows the output voltage waveform of a multilevel inverter (V(t)) that can be expressed in Fourier series as:

$$V(t) = \sum_{n=1}^{\infty} a_n \sin(n\alpha_n) + b_n \cos(n\alpha_n)$$

(1)

Due to the quarter wave symmetry of the output voltage, the even harmonics are eliminated  $(b_n=0)$  and only odd harmonics are present. The amplitude of the  $a_n$  is calculated from Fourier series factor and due to symmetry only the first quadrant switching angles,  $\alpha_1$ ,  $\alpha_2$ , ...,  $\alpha_m$ , is expressed:

$$a_n = (4V_{dc}/n\pi) \sum_{k=1}^m \cos(n\alpha_k)$$

(2)

and

$$0 < \alpha_1 < \alpha_2 < \dots \alpha_m < \pi/2 \tag{3}$$

For any harmonics, (2) can be expressed up to the  $k^{th}$  term, where m is the number of variables corresponding to switching angles  $\alpha_l$  through  $\alpha_m$  of the first quadrant. In selective harmonic elimination,  $a_n$  is assigned as the desired value for the fundamental component and equals to zero for the harmonics to be eliminated [15].

$$a_{1} = (4V_{dc}/\pi) \sum_{k=1}^{m} \cos \alpha_{k} = M$$

$$a_{5} = (4V_{dc}/5\pi) \sum_{k=1}^{m} \cos 5\alpha_{k} = 0$$

$$a_{n} = (4V_{dc}/n\pi) \sum_{k=1}^{m} \cos (n\alpha_{k}) = 0$$

(4)

where M is the amplitude of the fundamental component.

Solving these equations is tending to compute the  $\alpha_1, \ldots, \alpha_k$ . Whereas triples harmonics are eliminated in a three phase balanced system, computing these harmonics are neglected in the computing of the switching angle. It is evident that with computed m switching angles, (m-1) harmonics can be eliminated. These lead to non-linear equations and the direct solution of the non-linear equations can lead to discontinuity at certain modulation indices. These non-linear equations show multiple solutions and the main difficulty is the solution's convergence at certain points, while no analytical solution is available [15]-[17].

In this work, the complexity of solving the non-linear equations is prevented by converting the selective harmonic elimination problem to an optimization problem as follow:

The %THD of the output voltage can be expressed by:

$$\%THD = \left[\frac{1}{a_1^2} \sum_{n=5}^{\infty} (a_n)^2\right]^{1/2} \times 100$$

(5)

where  $n=6i\pm 1$  (i=1, 2, 3, ...).

Voltage THD is considered as the fitness function  $F(\alpha)$ , that must be minimized with the constraints of selective harmonic elimination to reduce the overall THD in the

output voltage waveform. Mathematically, the problem can be formulated as follows:

$$\begin{aligned} \textit{Minimize} F(\alpha) &= F(\alpha_1, \alpha_2, ..., \alpha_m) \\ \textit{Subject to} : 0 &< \alpha_1 < \alpha_2 < ... \alpha_m < (\pi/2); \\ a_1 &= M; \\ a_5 &< \varepsilon_1; \\ a_7 &< \varepsilon_2; \end{aligned} \tag{6}$$

$$\vdots$$

where  $\varepsilon_1$ ,  $\varepsilon_2$ , ...,  $\varepsilon_m$  are the allowable limits of individual harmonics.

The values of  $\varepsilon_1$ ,  $\varepsilon_2$ , ...,  $\varepsilon_m$  are chosen very close to zero for the selected low-order harmonics to be eliminated completely. In the proposed method based on GA, at the modulation indices of discontinuity for the computation of switching angles  $\alpha_1$  through  $\alpha_n$ , the angles are computed based on minimum possible voltage THD and optimized individual harmonics. With this formulation, the selected harmonics are not completely removed but instead remain within allowable limits; as such. The above mentioned problems can be solved.

#### 4. Genetic Algorithm Method

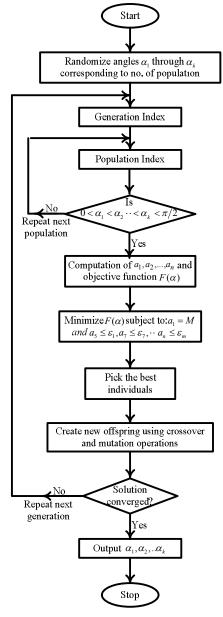

A GA is a search mechanism that imitates the natural selection and the genetics of living organisms. A typical GA consists of three operators, i.e., reproduction, crossover, and mutation [18], [19]. A flowchart of the GA is shown in Fig. 3.

The process of a GA usually begins with a randomly selected population of chromosomes. These chromosomes are representations of the problem to be solved; in this case, switching angles of inverters. Then, to start the search procedure, the switching angles are randomly generated. These values must satisfy the conditions of (6) for the chosen number of population. According to the attributes of the problem, different positions of each chromosome are encoded as bits, characters, or numbers. These positions are sometimes referred to as genes and are changed randomly within a range during evolution. An evaluation function  $(F(\alpha))$  is used to calculate the "goodness" of each chromosome.

In the optimization problem considered, the  $F(\alpha)$  is defined as voltage THD which is presented in (5). During evaluation, two basic operators, crossover and mutation, are used to simulate the natural reproduction and mutation of species. In crossover, randomly selected subsections of two individual chromosomes are swapped to produce the

offspring. In mutation, randomly selected genes in chromosomes are altered by a probability equal to the specified mutation rate. These operators are applied to offspring to generate next generations during optimization process. When the convergence is achieved, the repetition of this process is stopped. With a considerable number of generations and a large population in each generation, the algorithm searches for all probable sets of solutions and finally computes the angles  $\alpha_1$  through  $\alpha_n$ , to contribute the minimum THD, keeping the individual harmonics within the limits as specified by (6).

The program is run for different values of modulation index and the switching angles corresponding to minimum voltage THD are stored as a look-up table.

Fig. 3. Flowchart of the genetic algorithm

#### 5. Simulation Results

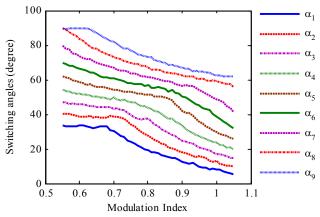

The calculated switching angles are simulated through the simulation of a cascaded multilevel inverter using the software package Matlab/Simulink. The results are presented in this section. The simulation results of the switching pattern with a varying modulation index (*M*) considering a 19-level multilevel inverter is shown in Fig. 4. As can be seen from this figure, the algorithm has found a solution for all modulation indices, including discontinuity points.

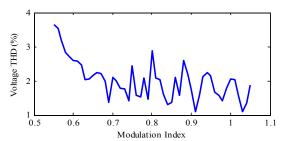

Voltage THD (%) against modulation index related to the optimal switching angles which comes from GA is shown in Fig. 5. As shown, the amount of THD (%) is lower than 4% and even in most points lower than 3%.

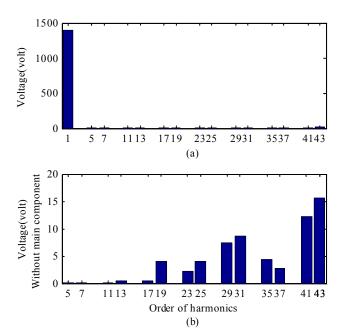

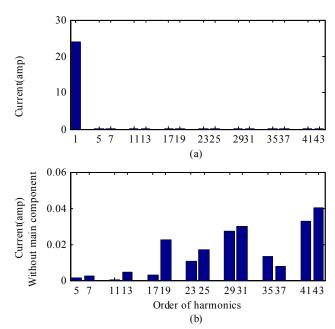

Fig. 6 (a) shows the harmonic spectrum of output-phase voltage up to the 23<sup>rd</sup> level; as expected, selected harmonics, in this case, 5<sup>th</sup>, 7<sup>th</sup>, 11<sup>th</sup>, 13<sup>th</sup>, 17<sup>th</sup>, 19<sup>th</sup>, 23<sup>rd</sup> and 25<sup>th</sup> levels, are minimized. In order to clarify the amplitude of minimized harmonics, this figure is repeated in Fig. 6 (b) without the fundamental component. As the triplen harmonics (odd multiples of the 3 harmonic) will not be present in the line-to-line voltage, they are not shown in the harmonic spectra.

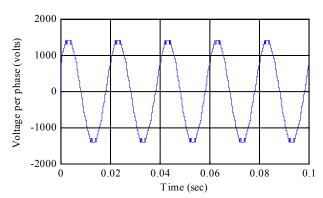

The output phase voltage waveform of the 19-level inverter at M of 0.9 is shown in Fig. 7. The DC source that is used in the simulation is equal to 100 V ( $V_{dc}$ =100 v). The load is connected to the inverter is R= $100 \Omega$  and L=50 mH.

**Fig. 4.** Switching angles against modulation index for a 19-level inverter

**Fig. 5.** Minimum THD against modulation index for a 19-level inverter

**Fig. 6.** Harmonic spectrum of output phase voltage for a 19-level inverter with fundamental switching at M=0.9

**Fig. 7.** Output voltage waveform for a 19-level inverter at M=0.9

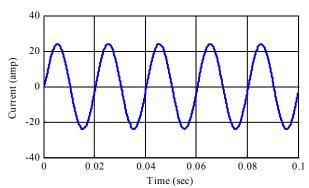

Fig. 8. Current waveform for a 19-level inverter at M=0.9

Fig. 8 shows the current waveform of a three phase delta connected load. The waveform of the current is found to be almost sinusoidal and the corresponding harmonic spectrum is shown in Fig. 9.

Fig. 9. Harmonic spectrum of output current at M=0.9

#### 6. Conclusion

In this paper a method based on GA was applied to eliminate selected order of harmonics and to reduce output voltage THD. Besides controlling individual selected harmonics within the allowable limits, the method also optimizes the other order of harmonics to minimize the overall voltage THD. Moreover, at the points of discontinuity of solutions, the algorithm computes the lowest possible voltage THD through optimization of the objective function and finds solutions for all desired modulation indices. The effectiveness of the applied method has been verified through simulation and the results were presented. The results show that the proposed method effectively minimizes a large number of specific harmonics, and the output voltage results in very low THD. Also the waveform of the current is found to be almost sinusoidal.

#### References

- R. H. Baker, "High-voltage converter circuit," U.S. Patent 4 203 151, May 1980.

- [2] A. Nabe, I. Takahashi, and H. Akagi, "A new neutral-point clamped PWM inverter," in *Proc. IEEE Ind. Appl. Soci. Conf.*, Sept./Oct. 1980, pp. 761–766.

- [3] Keith A. Corzine, Mike W. Wielebski, Fang Z. Peng, Jin Wang, "Control of Cascaded Multilevel Inverters," *IEEE Trans. On Power Elect.*, Vol. 19, No. 3, May 2004, pp. 732-738.

- [4] M. Fracchia, T. Ghiara, M. Marchesoni, and M. Mazzucchelli, "Optimized modulation techniques for the generalized N-level converter", in *Proc. IEEE Power Elect. Spec. Conf.*, Madrid, Spain, 1992, pp. 1205–1213.

- [5] K. A. Corzine and J. R. Baker, "Reduced parts-count multilevel rectifiers", *IEEE Trans. Ind. Electron.*, Vol. 49, Aug. 2002, pp. 766–774.

- [6] F. Richardeau, P. Baudesson, and T. Meynard, "Failurestolerance and remedial strategies of a PWM multicell inverter", in *Proc. IEEE Power Elect. Spec. Conf.*, Vol. 2, Galway, Ireland, June 2000, pp. 649–654.

- [7] F. Z. Peng, "A generalized multilevel inverter topology with self voltage balancing", *IEEE Trans. Ind. Applicat.*, Vol. 37, Mar./Apr. 2001, pp. 611–618.

- [8] P.W. Hammond, "Medium voltage pwm drive and method," U.S. Patent 5 625 545, April 1997.

- [9] F. Z. Peng, J. W. McKeever, and D. J. Adams, "A power line conditioner using cascade multilevel inverters for distribution systems," in *Proc. IEEE Ind. Appl. Soc. Conf.*, Vol. 2, 1997, pp. 1316–1321.

- [10] M. D. Manjrekar, P. K. Steimer, and T. A. Lipo, "Hybrid multilevel power conversion system: a competitive solution for high-power applications," *IEEE Trans. Ind. Applicat.*, Vol. 36, May/June 2000, pp. 834–841.

- [11] K. A. Corzine and Y. L. Familiant, "A new cascaded multilevel H-bridge drive", *IEEE Trans. Power Elect.*, Vol. 17, Jan. 2002, pp. 125–131.

- [12] J. Huang, K.A. Corzine, C.M. Hutson, and S. Lu, "Extending Voltage Range and Reducing Torque Ripple of Five-Phase Motor drives with Added Voltage Harmonics", *IEEE Appl. Power Elect. Conf. and Exp.*, Feb. 2008, pp. 866-872.

- [13] O. Ojo and D. Gan, "Generalized discontinuous carrier-based PWM modulation scheme for multi-phase converter-machine systems", *IEEE Ind. Appl. Soci. Conf.*, Vol. 2, 2005, pp. 1374-1381.

- [14] Chris M. Hutson, Ganesh K. Venayagamoorthy, and Keith A. Corzine, "Optimal SVM Switching for a Multilevel Multi-Phase Machine Using Modified Discrete PSO", *IEEE Swarm Intell. Symp.*, St. Louis MO USA, 2008, Sep. 21-23.

- [15] R.N. Ray, D. Chatterjee, "Harmonics elimination in multilevel inverter using the particle swarm optimization technique", *IET Power Elect.*, Vol. 2, Iss. 6, 2009, pp. 646–652.

- [16] Chiasson J. N., Tolbert L. M., Mckenzie K. J. and Du Z. "Control of a multilevel converter using resultant theory", *IEEE Trans. Control Syst. Technol.*, 2003, Vol. 11 (3), pp. 345–354.

- [17] Chiasson J. N., Tolbert L. M., Mckenzie K. J. and Du Z. "A complete solution to the harmonic elimination problem", *IEEE Trans. Power Electron.*, 2004, 19, (2), pp. 491–499.

- [18] Z. Michalewicz. *Genetic Algorithms* + *Data structures* = *Evolutionary Programs*, 3rd ed., Springer, 1996.

- [19] D. E. Goldberg, Genetic Algorithms in Search, Optimization, and Machine Learning. 1st ed, Addison-Wesley publications, 1989

Ali Reza Marami Iranaq was born in Tabriz, Iran in 1983. He received his B.Sc. degree in Electronic Engineering from Islamic Azad University, Tabriz Branch, Tabriz, Iran in 2006. He received his M.S. degree in Electrical Engineering from University of Tabriz,

Tabriz, Iran, in 2009. He is currently working as a automation engineer in NWSI company, Tabriz, Iran. His research interests are in the Advanced Power Electronic Devices, FACTS Devices and the application of FACTS Devices in Power System.

Mojtaba Bahrami Kouhshahi was born in Sirjan, Iran in 1984. He received his B.Sc. degree in Power Engineering from the Shahid Bahonar University of Kerman, Kerman, Iran in 2008. He is currently working on his M.Sc. degree at the University of

Tabriz, Tabriz, Iran. His research interests include drive and design of electrical machines. He currently focuses on drive and design of Permanent-Magnet Brushless DC machines.

Mehdi Bahrami Kouhshahi was born in Hajiabad, Iran in 1981. He received his B.Sc. degree in Electronics Engineering from the Shahid Bahonar University of Kerman, Kerman, Iran in 2006 and an M.Sc. degree in Power Electronics from Tabriz University,

Tabriz, Iran in 2009. He is currently a lecturer of the Electrical Engineering Department of the Azad University, Kahnouj Branch, Kahnouj, Iran. His research interests include Power Systems, Power Electronics and FACTS Devices

Mohammad Bagher Bannae Sharifian received his B.Sc. and M.Sc. degrees in 1989 and 1992 respectively from University of Tabriz. In 1992 he joined the Electrical Engineering Department of the University of Tabriz as a lecturer. He received his Ph.D. degree in

Electrical Engineering from the same University in 2000. In 2000 he rejoined the Electrical Power Department of Faculty of Electrical and Computer Engineering of the same university as an Assistant Professor. He is currently Professor of the mentioned Department. His research

interests are in the areas of design, modeling and analysis of electrical machines, transformers, liner electric motors, and electric and hybrid electric vehicle drives.

Mehran Sabahi was born in Tabriz, Iran, 1968. He received his B.Sc. degree in Electronic Engineering from University of Tabriz, Tabriz, Iran, and M.Sc. degree in Electrical Engineering from Tehran University, Tehran, Iran and Ph.D. degree in Electrical

Engineering from University of Tabriz, Tabriz, Iran in 1991, 1994 and 2009, respectively.

In 2004, he joined the Faculty of Electrical and Computer Engineering, University of Tabriz, where he has been an Assistant Professor since 2009. His research interests include Power Electronic Converters and Power Electronic Transformers.