**JPE 12-3-4**

http://dx.doi.org/10.6113/JPE.2012.12.3.410

# Direct Current Control Method Based On One Cycle Controller for Double-Frequency Buck Converters

Quanming Luo<sup>†</sup>, Shubo Zhi<sup>\*</sup>, Weiguo Lu<sup>\*</sup>, and Luowei Zhou<sup>\*</sup>

†\*State Key Laboratory of Power Transmission Equipment & System Security and New Technology, Chongqing University, Chongqing, China

#### **Abstract**

In this paper, a direct current control method based on a one-cycle controller (DCOCC) for double frequency buck converters (DF buck) is proposed. This control method can make the average current through the high frequency and low frequency inductors of a DF buck converter equal. This is similar to the average current control method. However, the design of the loop compensator is much easier when compared with the average current control. Since the average current though the high frequency and low frequency inductors is equivalent, the current stress of the high frequency switches and the switch losses are minimized. Therefore, the efficiency of the DF buck converter is improved. Firstly, the operation principle of DCOCC is described, then the small signal models of a one cycle controller and a DF buck converter are presented based on the state space average method. Eventually, a system block diagram of the DCOCC controlled DF buck is established and the compensator is designed. Finally, simulation and experiment results are given to verify the correction of the theory analysis.

**Key words:** DF buck, One cycle controller, Small signal model

## I. INTRODUCTION

In order to improve the performance of a power converter, it is necessary to increase the switching frequency. However, a higher switching frequency means higher switching losses and lower efficiency of the converter. The soft-switching technique is an effective method to solve the contradiction between the performance and efficiency of a converter and has become a hotspot in the research of power electronics [1]-[5]. In [6], a novel DF buck converter was proposed. This converter is composed of two buck cells, where the switching frequency of one of the cells is much higher than the other. Therefore, one of the cells is called the high frequency buck cell and the other one is called the low frequency buck cell. The output characteristics of the DF buck converter are determined by the high frequency cell and can be improved by increasing its switching frequency. Because the current through the high frequency switches is shunted by the low frequency buck cell, the switching losses will not increase too much due to the increases in the switch frequency. As a result, the performance

of the DF buck converter is improved while the efficiency does not decrease. This is another effective way to solve the contradiction mentioned above. To shunt the current through the switches of the high frequency cell effectively, it is necessary to control the current through the inductor of the low frequency buck cell so that it is approximately equal to that of the high frequency buck cell. As a result, a current type control needs to be adopted to control the DF buck converter, such as the average current control [7], the peak current control [8], the hysteretic current control [9], etc. Adopting the average current control can make the average current through the high and low frequency inductors equal and insure that the current stresses of the high frequency switches are theoretically minimal. However, the inner current loop and the outer voltage loop compensator must be designed carefully. When adopting the peak current control, the current stress of the high frequency switch is higher and the sub-harmonic oscillation has to be eliminated. The hysteretic current control is a kind of variable frequency control and the design of the filters is quiet difficult. In this paper, a direct current control method based on a one cycle controller [10] for DF buck converters is proposed. This method has the following characteristics:

The average current value through the high frequency inductor and the low frequency inductor can be controlled to be equal, while the current stress of the high frequency switch and the switch losses are minimized. Therefore,

Manuscript received Feb. 8, 2011; revised Mar. 16, 2012 Recommended for publication by Associate Editor Byung-Cho Choi. <sup>†</sup>Corresponding Author: lqm394@126.com

Tel: +86-023-6510-3558, Fax: +86-023-6510-3558, Chongqing, Univ.

<sup>\*</sup>State Key Laboratory of Power Transmission Equipment & System Security and New Technology, Chongqing University, China

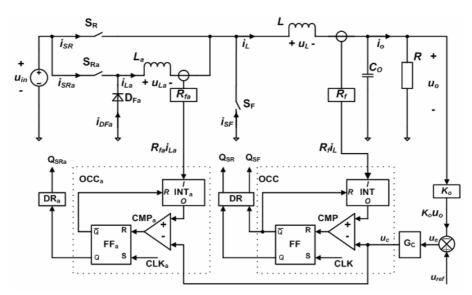

Fig. 1. The schematic of DCOCC controlled DF buck converter.

the efficiency of DF buck converter is improved.

- Unlike the average current control, there is only one voltage loop compensator and its design is very easy.

- The analog circuit to realize the controller is very simple.

In section II, the operation principle of the DCOCC controlled DF buck converter is described. In section III, the small signal models of a one cycle controller and a DF buck converter are presented, eventually, a system block diagram is established. The simulation and experimental verification are shown in section IV and section V, respectively. Finally, some conclusions are given in section VI.

In the following analysis, the capital letter represents the variable's quiescent value; the small letter represents the variable's instantaneous value, and  $\hat{x}$  represents the variable's small ac variation.

## II. THE OPERATION PRINCIPLE OF DCOCC CONTROLLED DF BUCK CONVERTER

Fig. 1 shows a schematic of the DCOCC controlled DF buck converter. There are two one cycle controllers in the schematic, a high frequency one cycle controller OCC and a low frequency one cycle controller OCCa. The sensed output voltage  $K_ou_o$  is compared with the reference voltage  $u_{\rm ref}$ . The difference between them is called the error voltage  $u_e$ , which is applied to the input of the voltage loop compensator  $G_e$ . The output of  $G_e$  is called the compensated voltage  $u_e$ , which is applied to the inverting input of the comparators COM and COMa. The sensed current  $R_i i_L$  is applied to the input of the integrator with the reset INT. The output of the INT is connected to the non-inverting input of the COM and the output of the COM is connected to the reset input of the flip-flop FF. The clock pulse CLK at the set input of the FF

determines the switching frequency of the high frequency switches  $S_R$  and  $S_F$ . The output of the FF is connected to the input of the driver DR and the output of the DR is the drive signals  $Q_{SR}$  and  $Q_{SF}$  for  $S_R$  and  $S_F$ , respectively. The inverting output of the FF is applied to reset the INT. Similarly, the drive signal  $Q_{SRa}$  for the low frequency switch  $S_{Ra}$  is derived. The frequencies  $f_H$  and  $f_L$  of the clock pulses CLK and CLKa are equal to the operation frequency of the high frequency BUCK cell and the low frequency BUCK cell, and  $f_H$  is much greater than  $f_L$ .

When the clock pulse CLK comes, the switch  $S_R$  is turned on and  $S_F$  is turned off, and the integrator INT begins to integrate the sensed current  $R_{rl_L}$ . The output of the comparator COM changes its state and triggers the flip-flop FF when the output of the INT reaches  $u_c$ . This in turn, turns on  $S_F$ , turns off  $S_R$  and resets the output of the INT to zero. The operation principle of the OCCa is the same as for the OCC described above.

The condition where the average values of  $i_{\rm L}$  and  $i_{\rm La}$  are controlled to be equal will be discussed in the following. It is assumed that the DF buck converter is working in continuous current mode (CCM), and that all of the power devices are ideal. Let the integration constants  $T_{\rm i}$  and  $T_{\rm ia}$  of the integrators INT and INTa be equal to the periods  $T_{\rm H}$  and  $T_{\rm L}$  of the clock pulses CLK and CLKa, respectively. That is:

$$T_{\rm i} = T_{\rm H} \quad T_{\rm ia} = T_{\rm L} \tag{1}$$

During the turn on of SR,  $i_L$  is:

$$i_{\rm L} = I_{\rm L} - \frac{u_{\rm in} - u_{\rm o}}{2L} dT_{\rm H} + \frac{u_{\rm in} - u_{\rm o}}{L} t \left(0 \le t \le dT_{\rm H}\right) (2)$$

where d is the duty ratio of  $S_R$ .

During the turn on of  $S_{Ra}$ ,  $i_{La}$  can be approximately expressed

| TABLE I<br>SWITCHING STATES |                 |          |

|-----------------------------|-----------------|----------|

| State                       | Active Switches |          |

|                             | $S_R$           | $S_{Ra}$ |

| a                           | ON              | ON       |

| b                           | OFF             | ON       |

| C                           | ON              | OFF      |

| d                           | OFF             | OFF      |

$$i_{La} \approx I_{La} - \frac{u_{in} - u_{o}}{2L_{a}} d_{a}T_{L} + \frac{u_{in} - u_{o}}{L_{a}} t \ (0 \le t \le d_{a}T_{L})$$

(3)

where  $d_a$  is the duty ratio of  $S_{Ra}$ .

According to [6], when the DF buck converter is in the steady state, the duty radios of  $S_R$  and  $S_{Ra}$  are equal to satisfy the voltage-second balance requirement of inductor  $L_a$ , which is assumed as d.

Referring to Fig. 1, the following can be obtained:

$$\frac{1}{T_{\rm i}} \int_{0}^{dT_{\rm H}} R_{\rm f} i_{\rm L} dt = \frac{1}{T_{\rm ia}} \int_{0}^{d_{\rm a}T_{\rm L}} R_{\rm fa} i_{\rm La} dt = u_{\rm c}$$

(4)

From (1), (2), (3), and (4), if the average values of  $i_L$  and  $i_{La}$ , denoted as  $I_L$  and  $I_{La}$ , are equal, the following equation must be satisfied:

$$R_{\rm f} = R_{\rm fa} \tag{5}$$

That is to say, if the sensor coefficients of  $i_L$  and  $i_{La}$  are equal, assumed as  $R_a$ , then the average value of  $i_L$  and  $i_{La}$  is controlled to be equal, which is assumed as  $I_a$ .

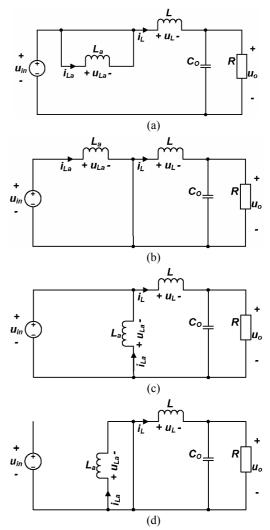

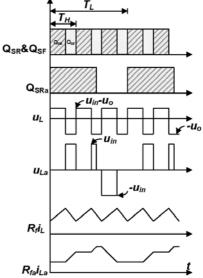

Based on the conditions described above, the operation principle of the DCOCC controlled DF buck converter is analyzed as follows. The key waveforms in one low frequency switching period are shown in Fig. 3, where  $f_{\rm H}$  is three times  $f_{\rm L}$  with the same duty cycle of 0.6. There are four switching states according to the status of the switches  $S_{\rm R}$  and  $S_{\rm Ra}$ , which are listed in Table I. State a denotes that both of the switches  $S_{\rm R}$  and  $S_{\rm Ra}$  are on and the equivalent circuit is shown in Fig. 2(a). In a similar manner, the equivalent circuits of states b, c, and d are shown in Fig. 2(b)-(d), respectively.

According to the operation principle of the DCOCC controlled DF buck converter described above, the average values of the low frequency inductor current  $i_{La}$  and the high frequency inductor current  $i_{L}$  are controlled to be equal with only one voltage loop compensator  $G_c$ . In the following, the small signal model of the DCOCC controlled DF buck converter is established to design the voltage compensator  $G_c$ .

Fig. 2. Equivalent circuit in different switching states. (a) State a. (b) State b. (c) State c. (d) State d.

Fig. 3. Voltage and current waveforms in one low frequency switching period.

## III. THE SMALL SIGNAL MODEL OF THE DCOCC CONTROLLED DF BUCK CONVERTER

Firstly, the small signal model of the one cycle controller is derived. Then this is done for the DF buck converter. Finally, the system block diagram of the DCOCC controlled DF buck converter will be established, and the transfer function for the input to output and the output impedance will be determined.

## A. The Small Signal Model of the One Cycle Controller

Assuming that the ripples of  $i_L$  and  $i_{La}$  are very small, from (1), (4), and (5), the following can be obtained:

$$R_a i_{\scriptscriptstyle \rm I} d = R_a i_{\scriptscriptstyle \rm I} {}_{\scriptscriptstyle A} d_{\scriptscriptstyle A} = u_{\scriptscriptstyle \rm C} \tag{6}$$

Perturb the variables in (6), that is:

$$\begin{split} i_{\mathrm{L}} &= I_{\mathrm{a}} + \hat{i}_{\mathrm{L}} & i_{\mathrm{La}} = I_{\mathrm{a}} + \hat{i}_{\mathrm{La}} \\ d &= D + \hat{d} & d_{\mathrm{a}} = D + \hat{d}_{\mathrm{a}} \\ u_{\mathrm{c}} &= U_{\mathrm{c}} + \hat{u}_{\mathrm{c}} \end{split} \tag{7}$$

Substituting (7) into (6), and neglecting the second order nonlinear terms, the following is obtained:

$$R_{a}I_{a}D = U_{c} \tag{8}$$

$$R_{a}I_{a}\hat{d} + R_{a}D\hat{i}_{L} = R_{a}I_{a}\hat{d}_{a} + R_{a}D\hat{i}_{La} = \hat{u}_{c}$$

(9)

From (9):

$$\hat{d} = F_{\rm m} \left( \hat{u}_{\rm c} - F_{\rm L} \hat{i}_{\rm L} \right) \tag{10}$$

$$\hat{d}_{a} = F_{m} \left( \hat{u}_{c} - F_{L} \hat{i}_{La} \right) \tag{11}$$

where:

$$F_{\rm m} = \frac{1}{R.L.} \tag{12}$$

$$F_{\rm I} = R_{\rm a}D \tag{13}$$

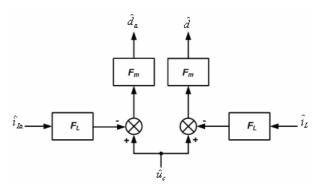

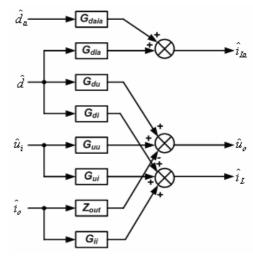

From (10) to (13), the block diagram of the one cycle controller is obtained, as shown in Fig. 4.

## B. The Small Signal Model of the DF Buck Converter

Utilizing the state-space averaging method [11], the block diagram of the DF buck converter is established, as shown in Fig. 5, where:

$$G_{\text{du}} = \frac{\hat{u}_{\text{o}}}{\hat{d}} = U_{\text{in}} \frac{1}{LCs^2 + \frac{L}{R}s + 1}$$

(14)

Fig. 4. The block diagram of the one cycle controller.

Fig. 5. The block diagram of the DF buck converter.

$$G_{\text{uu}} = \frac{\hat{u}_{\text{o}}}{\hat{u}_{\text{in}}} = D \frac{1}{LCs^2 + \frac{L}{R}s + 1}$$

(15)

$$Z_{\text{out}} = \frac{\hat{u}_{\text{o}}}{-\hat{i}_{\text{o}}} = \frac{Ls}{LCs^2 + \frac{L}{R}s + 1}$$

(16)

$$G_{\text{di}} = \frac{\hat{i}_{\text{L}}}{\hat{d}} = \frac{U_{\text{in}}}{R} \frac{RCs + 1}{LCs^2 + \frac{L}{R}s + 1}$$

(17)

$$G_{\text{ui}} = \frac{\hat{i}_{\text{L}}}{\hat{u}_{\text{in}}} = \frac{D}{R} \frac{RCs + 1}{LCs^2 + \frac{L}{R}s + 1}$$

(18)

$$G_{ii} = \frac{\hat{i}_{L}}{\hat{i}_{o}} = \frac{1}{LCs^{2} + \frac{L}{R}s + 1}$$

(19)

Fig. 6. The block diagram of the open loop DCOCC controlled DF buck converter.

$$G_{\text{dia}} = \frac{\hat{i}_{\text{La}}}{\hat{d}} = -\frac{U_{\text{in}}}{L_{\text{a}}s} \tag{20}$$

$$G_{\text{daia}} = \frac{\hat{i}_{\text{La}}}{\hat{d}_{a}} = \frac{U_{\text{in}}}{L_{a}S}$$

(21)

## C. The Small Signal Model of the DCOCC Controlled DF Buck Converter

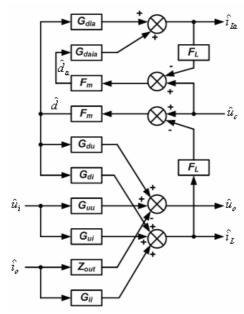

Based on the block diagram of the one cycle controller and the DF buck converter, the open-loop block diagram of the DCOCC controlled DF buck converter is obtained, as shown in Fig. 6.

Utilizing the Mason equation, the following open-loop transfer function is established. The open-loop control-to-output transfer function is:

$$G_{\text{cuo}} = \frac{\hat{u}_{\text{o}}}{\hat{u}_{\text{c}}} = \frac{F_{\text{m}}G_{\text{du}}}{1 + F_{\text{L}}F_{\text{m}}G_{\text{di}}}$$

$$= \frac{\frac{RU_{\text{in}}}{R_{\text{a}}}}{I_{\text{a}}R\left(LCs^{2} + \frac{L}{R}s + 1\right) + DU_{\text{in}}\left(RCs + 1\right)}$$

(22)

The open-loop input-to-output transfer function is:

Fig. 7. The system block diagram of the DCOCC controlled DF buck converter.

Fig. 8. The magnitude and phase curves of the loop gain T.

$$G_{\text{uuo}} = \frac{\hat{u}_{\text{o}}}{\hat{u}_{\text{in}}} = G_{\text{uu}} - \frac{F_{\text{L}} F_{\text{m}} G_{\text{ui}} G_{\text{du}}}{1 + F_{\text{L}} F_{\text{m}} G_{\text{di}}}$$

$$= \frac{DRI_{a}}{I_{\text{a}} R \left( LCs^{2} + \frac{L}{R}s + 1 \right) + DU_{\text{in}} \left( RCs + 1 \right)}$$

(23)

The open-loop output impedance is:

$$Z_{\text{outo}} = \frac{\hat{u}_{\text{o}}}{-\hat{i}_{\text{o}}} = Z_{\text{out}} + \frac{F_{\text{L}}F_{\text{m}}G_{\text{ii}}G_{\text{du}}}{1 + F_{\text{L}}F_{\text{m}}G_{\text{di}}}$$

$$= \frac{R + Ls\left[\left(LCs^{2} + \frac{L}{R}s + 1\right) + \left(RCs + 1\right)\right]}{\left(LCs^{2} + \frac{L}{R}s + 1\right)\left[\left(LCs^{2} + \frac{L}{R}s + 1\right) + \left(RCs + 1\right)\right]}$$

(24)

The transfer function from  $i_L$  to  $i_{La}$  is:

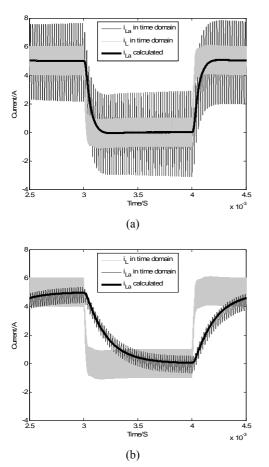

Fig. 9. The current waveforms through high frequency and low frequency inductors: (a)  $L_a$ =10 $\mu$ H. (b)  $L_a$ =50 $\mu$ H.

$$G_{\text{iiao}} = \frac{\hat{i}_{\text{La}}}{\hat{i}_{\text{L}}} = \frac{-F_{\text{L}}F_{\text{m}}G_{\text{dia}}}{1 + F_{\text{L}}F_{\text{m}}G_{\text{daia}}} = \frac{DU_{\text{in}}}{L_{\text{a}}I_{\text{a}}s + DU_{\text{in}}}$$

(25)

When the load current is changing, if  $i_{La}$  can keep up with  $i_L$  as quickly as possible, the current stress of the high frequency switches is lower, as are its switch losses. From (25), the smaller the value of  $L_a$ , the faster  $i_{La}$  keeps up with changes of  $i_L$ . However, if  $L_a$  is too small, the effect of shunting the current through the high frequency switches will be weakened. Therefore, there has to be a trade off between them.

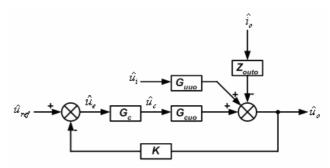

Finally, the system block diagram of the DCOCC controlled DF buck converter is established, as shown in Fig. 7. As the disturbance of the reference voltage is nearly zero, the whole system can be treated as a two-input single-output system.

The loop gain of the system is:

$$T = KG_c G_{cuo} \tag{26}$$

The close loop input to the output transfer function is:

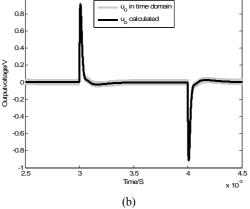

Fig. 10. The response waveforms of the output voltage: (a) Input voltage changing between 10V and 12V. (b) Load current changing between 20A and 25A.

$$G_{\text{uuc}} = \frac{\hat{u}_{\text{o}}}{\hat{u}_{\text{in}}} = \frac{G_{\text{uuo}}}{1 + T}$$

(27)

The close loop output impedance is:

$$Z_{\text{outc}} = \frac{\hat{u}_{\text{o}}}{-\hat{i}_{\text{o}}} = \frac{Z_{\text{outo}}}{1+T}$$

(28)

#### IV. SIMULATION VERIFICATION

The simulation parameters are as follows:  $U_{\rm in}$ =10V,  $U_{\rm o}$ =5V, R=0.25 $\Omega$ , L=5 $\mu$ H,  $L_{\rm a}$ =10 $\mu$ H, C=20 $\mu$ F,  $f_{\rm H}$ =250kHz,  $f_{\rm L}$ =50kHz,  $R_{\rm f}$ =0.5,  $R_{\rm fa}$ =0.5.

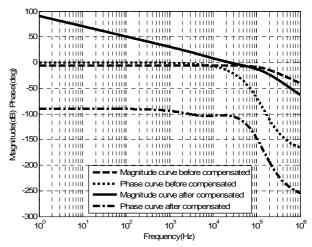

The traditional method described in [11] is used to design the voltage loop compensator  $G_c$ . After compensation, the cross frequency is 25kHz and the phase margin is  $76^{\circ}_{\circ}$ . The magnitude and the phase curves of the loop gain of the system before and after compensated are shown in Fig. 8.

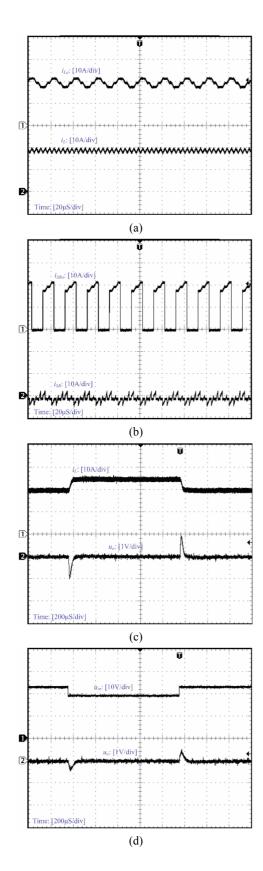

Fig. 11. Experimental waveforms: (a)  $i_L$  and  $i_{La}$ . (b)  $i_{SR}$  and  $i_{SRa}$ . (c)  $i_o$  and the response of  $u_o$ . (d) uin and the response of  $u_o$ .

Fig. 9(a) presents the simulation waveforms of  $i_{\rm L}$  and  $i_{\rm La}$  in the time domain and the calculated waveform of  $i_{\rm La}$  based on  $G_{\rm iiao}$  when the load current is changing between 20A and 25A and  $L_{\rm a}$ =10 $\mu$ H. Fig. 9(b) shows the above waveforms when  $L_{\rm a}$ =50 $\mu$ H. It can be seen that the simulation waveform of  $i_{\rm La}$  in time domain approximately coincides with the calculated waveform. It can also be seen that the smaller the low frequency inductor  $L_{\rm a}$ , the more quickly  $i_{\rm La}$  can keep up with  $i_{\rm L}$ , and the lower the current stresses of the high frequency switches  $S_{\rm R}$  and  $S_{\rm f}$ .

Fig. 10(a) shows the simulated output voltage waveforms in the time domain and the calculated output voltage waveform based on  $G_{\text{uuc}}$  when the input voltage is changing between 10V and 12V. Fig. 10(b) shows these two waveforms when the load current is changing between 20A and 25A. It can be seen that the simulated waveforms in the time domain coincide with those calculated, which verifies the correction of the theory analysis above.

#### V. EXPERIMENTAL VERIFICATION

The experimental parameters are almost the same as the simulation parameters. Fig. 11(a) shows the experimental waveforms of  $i_{\rm L}$  and  $i_{\rm La}$ . It can be seen that their average value is approximately equal. Fig. 11(b) shows the current waveforms of  $i_{\rm SR}$  and  $i_{\rm SRa}$ . Through S<sub>R</sub> and S<sub>Ra</sub>, it can be seen that the instantaneous value of  $i_{\rm SR}$  is much smaller than  $i_{\rm Sra}$ . Therefore, its switching losses are reduced. Fig. 11(c) shows the response of  $u_{\rm o}$  when  $i_{\rm o}$  is changing between 20A and 25A. Fig. 11(d) shows the response of  $u_{\rm o}$  when  $u_{\rm in}$  is changing between 10V and 12V. The experimental results are in accord with the simulation results.

#### VI. CONCLUSION

In this paper, a direct current control method based on the one cycle controller for a DF buck converter is proposed and the small signal model of it is established. Based on this model, the voltage loop compensator is designed. The simulation and experimental results have shown that:

- Adopting the DCOCC can make the average current through the high frequency and low frequency inductor equal. Therefore, the current stress and switching losses of the high frequency switches are minimized.

- The design of the voltage loop compensator is easy.

- The cross frequency and phase margin of the loop gain have no effect on the fact that the current through the low frequency inductor keeps up with the changing of the current through the high frequency inductor.

### ACKNOWLEDGMENT

Project Supported by National Natural Science Foundation of China (50907076), Scientific Research Foundation of SKL of Power Transmission Equipment & System Security and

New Technology (2007DA10512710202), The International S & T Cooperation Program of China (ISTCP) (2010DFA72250).

## REFERENCES

- [1] G. Hua and F. C. Lee, "Soft-switching techniques in pwm converters," *IEEE Trans. Power Electron.*, Vol. 42, No. 6, pp. 595-603, Dec.1995.

- [2] K. M. Smith Jr. and K. M. Smedley, "Properties and synthesis of lossless, passive soft switching converters," in Proc. 1st Int. Congr. Israel Energy, Power Motion Contr., pp. 112-119, May 1997.

- [3] K. M. Smith Jr. and K. M. Smedley, "Lossless passive soft switching methods for inverters and amplifiers," in Proc. Power Electron. Spec. Conf., pp. 1431-1439, 1997.

- [4] X. Ruan and Y. Yan, "Soft-switching techniques for pwm full bridge converters," *in Proc. Power Electron. Spec. Conf.*, pp. 18-23, 2000.

- [5] T.-F. Wu, S.-A. Liang, and Y.-K. Chen, "A structural approach to synthesizing soft switching pwm converters," *IEEE Trans. Power Electron.*, Vol. 18, No. 1, pp. 38-43, Jan. 2003.

- [6] X. Du, L. Zhou, and H.-M. Tai, "Double-frequency buck converter," *IEEE Trans. Ind. Electron.*, Vol. 56, No. 5, pp. 1690-1698, May 2009.

- [7] K. M. Smedly and S. Cuk, "One-cycle control of switching converters," *IEEE Trans. Power Electron.*, Vol. 10, No. 6, pp. 625-633, Nov.1995.

- [8] R. W. Erickson and D. Maksimovic, Fundamentals of power electronics, Second Edition, Kluwer Academic Publishers Group, 2001.

- [9] W. Tang, F. C. Lee, and R. B. Ridley, "Small-signal modeling of average current-mode control," *IEEE Trans. Power Electron.*, Vol. 8, No. 2, pp. 112-119, Nov. 1993.

- [10] F. D. Tan and R. D. Middlebrook, "A unified model for current-programmed converters," *IEEE Trans. Power Electron.*, Vol. 10, No. 4, pp. 397-408, Jul. 1995.

- [11] Y. Liu and P. C. Sen, "Large-signal modeling of hysteretic current-programmed converters," *IEEE Trans. Power Electron.*, Vol. 11, No. 3, pp. 423-430, May 1996.

**Shubo Zhi** was born in Cangzhou, China, in 1986. He received his B.S. in Electrical Engineering from the Agricultural University of Hebei, Hebei, China, in 2006. He is currently working towards his M.S. in Electrical Engineering from Chongging

University, Chongqing, China. His current research interests include LED drivers and high-efficiency bidirectional DC/DC converters.

**Weiguo Lu** was born in Zhejiang province, China, in 1977. He received his B.S., M.S., and Ph.D. in Electrical Engineering from Chongqing University, Chongqing, China, in 2000, 2003, and 2008, respectively. He is currently an Associate Professor in the

College of Electrical Engineering, Chongqing University, Chongqing, China. He is the author or coauthor of more than 20 papers in journal or conference proceedings. His current research interests include the stability analysis and control technology of switching power converters.

Quanming Luo was born in Chongqing, China, in 1976. He received his B.S., M.S., and Ph.D. in Electrical Engineering from Chongqing University, in 1999, 2002, and 2008, respectively. He was with the Emerson Network Power Co. Ltd., Shenzhen, China, as a Research and Development Engineer

from 2002 to 2005. Since 2005, he has been with the College of Electrical Engineering, Chongqing University, where he is currently an Associate Professor. He is the author or coauthor of more than 20 papers in journal or conference proceedings. His current research interests include LED driving systems, communication power systems, power harmonic suppression, and power conversion systems in electrical vehicles.

**Luowei Zhou** was born Dujiangyan, China, in 1954. He received his B.S., M.S., and Ph.D. in Electrical Engineering from Chongqing University, Chongqing, China, in 1982, 1988, and 2000, respectively. Since 1982, he has been with the College of Electrical

Engineering, Chongqing University, where he is currently a Full Professor. He was a Visiting Professor at the University of California, Irvine, between September 1998 and August 1999. He is the author or coauthor of more than 70 papers. His current research interests include the analysis and control of power electronics circuits, the realization of active power filters, power factor correction techniques, and high-frequency power conversion. Prof. Zhou is the Vice President of the China Society of Power Supply.