http://dx.doi.org/10.6113/TKPE.2012.17.1.67

# 높은 승압비를 갖는 부스트-플라이백 컨버터의 개선된 모델링 방법

서상욱<sup>1</sup>, 이귀준<sup>2</sup>, 김래영<sup>3</sup>, 현동석<sup>†</sup>

# Improved Modeling and Control of Boost-Flyback Converter With High Step-Up Voltage Ratio

Sang-Uk Seo<sup>1</sup>, Kui-Jun Lee<sup>2</sup>, Rae-Young Kim<sup>3</sup>, and Dong-Seok Hyun<sup>†</sup>

**Abstract** - This paper proposes the aggregated modeling and control of integated boost-flyback converter (IBFC) for understanding of dynamics characteristic and designing of relevant controller. The basic concept of the aggregated modeling is to substitute the boost or the flyback converter with an equivalent current source. Since each converter with equivalent current source corresponds to the basic boost and flyback converters, the overall mathematical process is significantly simplified for the modeling. Afterwards each result is combined to construct the complete model of the IBFC, and the relevant controller is designed through the achieved small-signal model. Simulation and experimental results show excellent agreement with the theoretical expectations.

Keywords: DC-DC converter, High step-up voltage ratio, Modeling and control, State-space method

#### 1. 서 론

오늘날 태양광이나 연료 전지와 같은 신재생 에너지 분야는 환경오염 및 에너지 고갈 문제를 해결할 수 있 는 미래의 에너지원으로 인식되고 있다. 이러한 에너지 원은 상대적으로 저전압(약 20~50 V)을 출력하기 때문 에, 계통에 연계하여 응용분야에 사용하기 위해서는 고 전압(약 380~400 V)으로 승압해 주어야 한다. 이를 위 한 다양한 승압형 컨버터에 대한 모델링 및 분석이 연 구되었다<sup>[1]</sup>. 많은 승압형 컨버터 토폴로지 중에서, 부스 트-플라이백 컨버터(integrated boostconverter, IBFC)는 적은 회로 소자로 고전압 증폭이 가 능한 부스트 컨버터의 장점과 변압기에 의한 시스템 절 연 및 권선비에 비례하는 전압 증폭이 가능한 플라이백 컨버터의 장점을 모두 가진 승압형 컨버터 토폴로지이 며, 많은 분야에서 응용되고 있다<sup>[2-5]</sup>. 기존의 연구에서 는 응용 분야에 따른 동작 상태 해석 및 특성 분석에

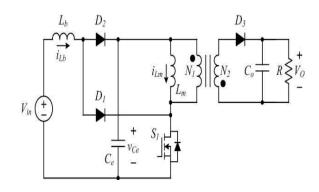

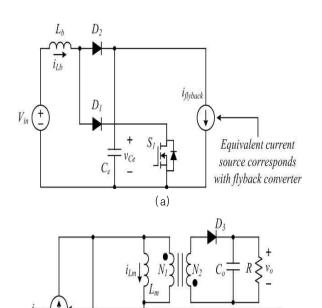

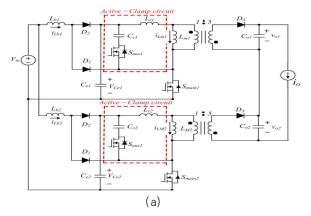

대해 제시하고 있지만, 부스트-플라이백 컨버터의 세부 적인 모델링 과정 및 제어기 설계 과정은 제시하지 않 았다. 그림 1은 일반적인 형태의 부스트-플라이백 컨버 터 구조를 보여준다. 부스트 컨버터는 불연속 도통 모드 (discontinuous conduction mode, DCM)로, 플라이백 컨 버터는 연속 도통 모드(continuous conduction mode, CCM)로 동작하도록 설계하였다 $^{[6]}$ . 기존에 제안된 모델 방법(Switch energy conservation, State-space average method)<sup>[7-9]</sup>은 단일 컨버터를 해석하기 위한 방 법이므로, 2대의 컨버터가 서로 다른 도통 모드로 동시 에 동작하는 부스트-플라이백 컨버터의 경우 이러한 모 델링 기법을 직접적으로 적용하기엔 어려움이 발생한다. 또한 회로 내 존재하는 소자들이 시스템 동작에 상호 영향을 주기 때문에, 4차 상태 공간 방정식을 유도함에 있어 수학적인 계산 과정이 매우 복잡해지는 단점이 있 다.

본 논문에서는 높은 승압 특성을 가진 부스트-플라이백 컨버터의 개선된 모델링 방법 및 부하 가변 시에도 안정적인 출력 전압을 유지하는 제어기 설계 기법을 제시한다. 위에서 언급된 문제점을 극복하기 위해 제안된모델링 방법의 개념은 부스트-플라이백 컨버터를 그림 2에 나타낸 것처럼 등가 전류 소스를 포함한 단일 부스

Paper number: TKPE-2012-17-1-10

<sup>&</sup>lt;sup>†</sup>Corresponding Author: dshyun@hanyang.ac.kr, Dept. of Electrical Eng., Hanyang University

<sup>&</sup>lt;sup>1,2,3</sup> Dept. of Electrical Eng., Hanyang University Manuscript received Sep. 6, 2011; accepted Dec. 15, 2011

트, 플라이백 컨버터로 각각 나누어 주는 것이다<sup>[10]</sup>. 나 누어진 2대의 컨버터는 다른 컨버터에 상응하는 등가 전류 소스와 2개의 상태 변수(인덕터 전류, 커패시터 전 압)를 포함한 형태로 나타나며, 기존에 단일 컨버터를 해석하는 방법으로 널리 이용되고 있는 상태-공간 평균 화 방법(State-space average method)를 적용하여 각 컨버터의 2차 상태 공간 방정식을 쉽게 유도 할 수 있 다. 유도된 2개의 상태 공간 방정식을 하나로 연립하여 부스트-플라이백 컨버터의 전체적인 4차 대 신호 상태 방정식을 유도한다<sup>[11-13]</sup>. 제안된 방법은 기존 해석에 널 리 적용된 상태-공간 평균화 방법으로 모델링 과정을 쉽게 수행할 수 있으며, 시스템 소자들의 상호 영향을 분리함으로서 상태 공간 방정식을 유도하기 위한 수학 적인 과정을 간소화 할 수 있다. 대 신호 상태 방정식에 서 동작점을 분석하였고 소 신호 방정식을 유도하여 이 를 바탕으로 부하 가변 시에도 안정적인 출력 전압을 유지하는 제어기를 설계하였다<sup>[14]</sup>. 제안된 모델링 방법 및 제어기 설계의 유효함을 증명하기 위해 시뮬레이션 및 실험 결과를 제시하여 타당성을 검증하였다.

# 2. 시스템 해석 및 모델링

#### 2.1 시스템 해석

그림 1에 나타난 부스트-플라이백 컨버터는 2대의 컨 버터가 직렬 연결된 구조로서 서로 다른 도통 모드(부스 트 컨버터 : 불연속 도통 동작 모드, 플라이백 컨버터 : 연속 도통 동작 모드)로 동시에 동작하므로, 이를 해석 하기 위해 기존에 단일 컨버터 모델링 방법에 널리 이 용된 상태 공간 평균화 방법을(State-space average method) 적용하기 어려운 단점이 있다. 또한, 회로 내 존재하는 상태 변수는 도통 모드에 따라 동작 특성이 크게 달라지고 시스템의 특성에 복잡한 영향을 주기 때 문에, 정상 상태 해석 및 시스템 모델링을 위한 4차 상 태 공간 방정식을 유도하기 위한 수학적인 계산 과정이 매우 복잡하다. 이러한 문제점을 해결하기 위해 부스트-플라이백 컨버터 회로를 그림 2에 나타낸 것처럼 등가 전류 소스를 포함한 독립적인 단일 부스트 컨버터와 플 라이백 컨버터로 분리한 후, 시스템 해석 및 모델링 과 정을 수행하였다.

2대의 단일 컨버터는 상태 공간 평균화 방법으로 이용하여 정상 상태 동작 특성을 쉽게 해석할 수 있다. 상태 공간 평균화 방법으로 각 컨버터에서 2개의 2차 상태 공간 방정식을 유도하고 등가 전류 소스 변수를 상태 변수와 입력 변수로 치환하고 하나로 연립하여 전체적인 부스트-플라이백 컨버터의 4차 대 신호 상태 공간 방정식을 유도 할 수 있다. 상태-공간 평균화 기법을 적용하기 위해서는 각 상태 변수의 시스템 세부 구간별동작 특성을 해석하여야 하는데, 이를 위해 구간별 통유률을 반드시 알아야 한다.

그림 1 일반적인 부스트-플라이백 커버터

Fig. 1 Conventional integraged boost-flyback converer

with boost converter

(b)

그림 2 등가 전류 소스를 포함한 컨버터

(a) 부스트 컨버터, (b) 플라이백 컨버터

Equivalent current

source corresponds

Fig. 2 Converter with equivalent current source

(a) boost converter, (b) flyback converter

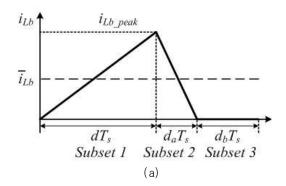

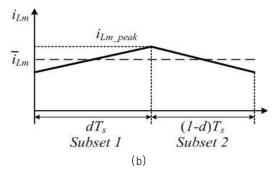

그림 3 인덕터 전류 파형 (a) 부스트 인덕터, (b) 자화 인덕터

Fig. 3 Inductor current waveforms (a) boost inductor, (b) magnetizing inductor

그림 3(b)의 플라이백 컨버터의 경우 연속 도통 모드로 동작하기 때문에 세부 구간별 통유률을 쉽게 유도할 수 있다. 하지만, 그림 3(a)에 나타낸 부스트 컨버터는 불연속 도통 모드로 동작하므로, 부스트 인덕터 전류가 상승하는 세부 구간 1, 인덕터 전류가 감소하며 저장된 에너지가 커패시터(Co)에 전달되는 세부 구간 2, 인덕터 전류가 0이 되는 세부 구간 3으로 나눠지므로, 각세부 구간별 통유률을 정확히 알 수 없다. 따라서, 부스트 인덕터 최대 전류와 평균 전류의 관계식을 이용하여부스트 인덕터 세부 구간 2, 3을 세부 구간 1의 통유율과 상태 변수로 표현 해 주어야 한다. 그림 3(a)에서 부스트 인덕터 최대 전류는 식(1)과 같이 표현된다.

$$\frac{i_{\it Lb\_peak}}{d\,T_{\it o}} = \frac{v_{\it in}}{L_{\it b}}, \; i_{\it Lb\_peak} = \frac{v_{\it in}d\,T_{\it s}}{L_{\it b}}, \; f_{\it s} = \frac{1}{T_{\it o}} \eqno(1)$$

여기서, fS는 스위칭 주파수, TS는 스위칭 주기를 나타낸다. 한 주기 동안의 부스트 인덕터 평균 전류는 식(2)와 같이 표현된다. "-"은 한 주기 동안의 평균화 수치를 나타낸다. 식(1)을 식(2)에 대입하여 그림 3(a)의 부스트 컨버터 세부 구간  $2(d_aT_s)$ ,  $3(d_bT_s)$ 의 통유률을 식(3), 식(4)와 같이 상태 변수, 평균값, 통유률로 표현할수 있다. 각 컨버터의 세부 구간 모드 해석은 다음과 같다.

$$\overline{i_{Ib}} = \frac{1}{2} (d + d_a) T_s i_{Ib\_peak} \frac{1}{T_s}

= \frac{1}{2} (d + d_a) i_{Ib\_peak}$$

(2)

$$d_a = \frac{2L_b f_s \overline{i_{Lb}}}{v_{in}d} - d = q - d \tag{3}$$

$$\begin{split} d_b &= 1 - (d + d_a) = 1 - q, \\ q &= \frac{2L_b f_s \overline{i}_{Lb}}{v_{in} d} \end{split} \tag{4}$$

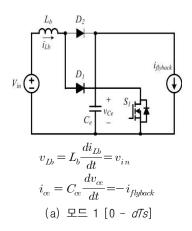

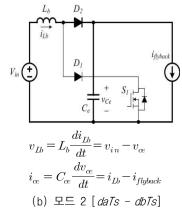

그림 4 부스트 컨버터 모드 해석 Fig. 4 Analysis of boost converter mode

$$v_{Lm} = L_m \frac{di_{Lm}}{dt} = v_{cc}$$

$$i_{co} = C_{co} \frac{dv_o}{dt} = -\frac{v_o}{R}$$

$$i_{ce} = C_{ce} \frac{dv_e}{dt} = i_{boost} - i_{Lm}$$

(a)  $\Psi = 1 [0 - dTs]$

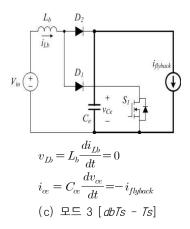

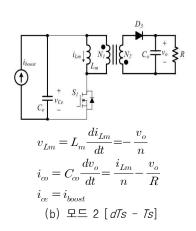

그림 5 플라이백 컨버터 모드 해석 Fig. 5 Analysis of flyback converter mode

부스트 컨버터는 부스트 인덕터  $L_b$ 와 다이오드  $D_i$ ,  $D_2$ , 커패시터  $C_e$ , 플라이백 컨버터에 상응하는 등가 전류 소스( $i_{tlyback}$ )로 구성되어 있다. 불연속 도통 구간에서 동작하므로 그림 4처럼 3개의 모드로 표현된다.

1)  $[0 - d_a T_a]$  [Fig. 4(a)]: 메인 스위치  $S_I$ 가 턴-온 되며, 다이오드  $D_z$ 는 역전압이 인가되어 오픈 된다. 부스트 인덕터  $L_b$ 는 입력 전압  $V_{in}$ 에 의해서 선형적으로 충전된다.

2)  $[d_aT_s - d_bT_s]$  [Fig. 4(b)]: 메인 스위치  $S_l$ 이  $d_aT_s$ 에서 턴-오프 되고, 다이오드  $D_2$ 가 도통된다. 인덕터를 통해 흐르는 전류  $i_L$ 가 0이 되는  $d_bT_s$  구간까지 캐패시터  $C_e$

를 충전시킨다.

3)  $[d_bT_s - T_s]$  [Fig. 4(c)]: 다이오드  $D_2$ 가 오픈 상태가되며 부스트 인덕터  $L_b$ 의 에너지는 0이 된다.

다시 메인 스위치  $S_I$ 가 턴-온 되면, 다음 스위칭 주기가 시작되는 동작을 반복하게 된다. 그림 4에 각 모드별상태 방정식을 나타내었다.

플라이백 컨버터는 자화 인덕터  $L_m$ , 다이오드  $D_3$  커 패시터  $C_e$ , 부스트 컨버터에 상응하는 등가 전류 소스  $(i_{boost})$ 로 구성되어 있다. 플라이백 컨버터는 연속 도통모드로 동작하므로 2개의 모드로 표현된다.

1)  $[0 - dT_s]$  [Fig. 5(a)]: 메인 스위치  $S_l$ 가 턴-온 되며, 다이오드  $D_s$ 는 역전압으로 인하여 오픈 된다. 커패시터  $C_e$  전압이 자화 인덕터  $L_m$ 를 선형적으로 충전시키고  $i_{Lm}$ 이 최대값까지 증가한다.

2)  $[dT_s - T_s]$  [Fig. 5(b)]: 메인 스위치  $S_r$ 이  $dT_s$ 에서 턴 -오프 되고, 다이오드  $D_s$ 가 도통된다. 따라서 변압기에 저장된 에너지가 2차측으로 전달된다. 그림 5에 각 모드 별 상태 방정식을 나타내었다.

#### 2.2 시스템 모델링

정상 상태의 한 주기 동안 부스트 컨버터와 플라이백 컨버터를 해석하였으므로, Voltage-Second-Balance(V-S-B) 와 Capacitor-Charge-Balance (C-C-B) 이론을 각 상태 변수에 적용하여 컨버터의 2 차 상태 공간 방정식을 독립적으로 유도할 수 있다.

$$\frac{d}{dt} \begin{bmatrix} i_{Ib} \\ v_{ce} \\ i_{Lm} \\ v_o \end{bmatrix} = \begin{bmatrix}

0 & \frac{-(q-d)}{L_b} & 0 & 0 \\

\frac{(q-d)}{C_e q} & 0 & \frac{-d}{C_e} & 0 \\

0 & \frac{d}{L_m} & 0 & \frac{-(1-d)}{L_m n} \\

0 & 0 & \frac{(1-d)}{C n} & \frac{-d}{C R}

\end{bmatrix} \begin{bmatrix} i_{Ib} \\ v_{ce} \\ i_{Lm} \\ v_o \end{bmatrix} + \begin{bmatrix} \frac{q}{L_b} \\ 0 \\ 0 \\ -1 \end{bmatrix} \begin{bmatrix} v_{in} \\ i_o \end{bmatrix} \tag{5}$$

$$\frac{d}{dt} \begin{bmatrix} \hat{i}_{Ib}^{\hat{i}} \\ \hat{v}_{\infty}^{\hat{i}} \\ \hat{v}_{o}^{\hat{i}} \end{bmatrix} = \begin{bmatrix} \frac{K(V_{in} - V_{ce})}{L_{b}} & (D - KI_{Ib}) & 0 & 0 \\ \frac{1}{C_{e}} & 0 & \frac{-D}{C_{e}} & 0 \\ 0 & \frac{D}{L_{m}} & 0 & \frac{-(1 - D)}{L_{m}n} \\ 0 & 0 & \frac{(1 - D)}{C_{o}n} & \frac{-1}{C_{o}R} \end{bmatrix} \begin{bmatrix} \hat{i}_{Ib}^{\hat{i}} \\ \hat{v}_{\infty}^{\hat{i}} \\ \hat{i}_{Lm}^{\hat{i}} \\ \hat{v}_{o}^{\hat{i}} \end{bmatrix} + \begin{bmatrix} \frac{KI_{Ib}}{L_{b}} & \frac{KI_{Ib}}{L_{b}D} (V_{ce} - V_{in} + \frac{DV_{ce}}{KI_{Ib}}) & 0 \\ 0 & -\frac{1}{C_{e}} (I_{Lm} + \frac{2}{K}) & 0 \\ 0 & \frac{1}{L_{m}} (V_{ce} + \frac{V_{o}}{n}) & 0 \\ 0 & -\frac{I_{Lm}}{C_{o}n} & -1 \end{bmatrix} \begin{bmatrix} \hat{v}_{in}^{\hat{i}} \\ \hat{i}_{o}^{\hat{i}} \end{bmatrix}, K = \frac{2I_{Lb}f_{s}}{DV_{in}}$$

$$(7)$$

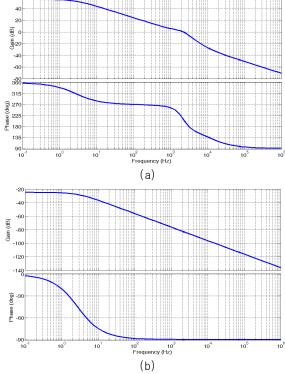

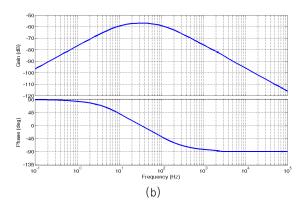

그림 6 개 루프 상태에서의 부스트-플라이백 컨버터 주파수 응답

- (a) 제어입력에 대한 출력 전압 전달함수

- (b) 출력 임피던스

Fig. 6 Frequency responses of boost-flyback converter in open loop by MATLAB

- (a) Control-to-output transfer function

- (b) Output impedance

유도된 2차 상태 공간 방정식에는 등가 전류 소스에 해당하는 변수가 포함되어 있는데 이를 시스템의 상태 변수와 입력 변수, 통유율로 치환하고 2개의 상태 공간 방정식을 연립하면 DC 동작점 해석을 위한 부스트-플라이백 컨버터의 전체적인 4차 상태 공간 방정식을 식(5)와 같이 유도할 수 있다.

식(5)의 4차 대 신호 상태 공간 방정식에서 부스트-플라이백 컨버터의 DC 동작점을 구하였으며, 부스트 인덕터 전류  $I_{Lb}$ =3.33A, 커패시터( $C_e$ ) 전압  $V_{Ce}$ =58.904V, 자화 인덕턴스 전류  $I_{Lm}$ =4.19A, 그리고 통유율 D=0.404 이다.

소 신호 AC 해석을 위한 상태 공간 방정식을 유도하기 위해 상태 변수  $i_{Lb}$ ,  $v_{Ce}$ ,  $i_{Lm}$ ,  $v_o$ 와 입력 변수  $v_{in}$ ,  $i_o$ 와, 통유율 d를 DC 동작점과 미소 변동분으로 식(6)에 나타내었다.

$$\begin{bmatrix} i_{Ib} \\ v_{ce} \\ i_{Lm} \\ v_o \end{bmatrix} = \begin{bmatrix} I_{Lb} \\ V_{ce} \\ I_{Lm} \\ V_o \end{bmatrix} + \begin{bmatrix} \widehat{i_{Ib}} \\ \widehat{v_{ce}} \\ \widehat{i_{Lm}} \\ \widehat{v}_o \end{bmatrix}, \begin{bmatrix} v_{in} \\ d \\ i_o \end{bmatrix} = \begin{bmatrix} V_{in} \\ D \\ I_o \end{bmatrix} + \begin{bmatrix} \widehat{v_{in}} \\ \widehat{d} \\ \widehat{i_o} \end{bmatrix}$$

(6)

식(6)을 대 신호 상태 공간 방정식 식(5)에 대입하여 선형화하면 소 신호 상태 공간 방정식을 식(7)와 같이 유도할 수 있다. 단, 대부분 소 신호 AC 분석의 경우 비 선형화항과 충분히 작은 2차 소 신호항은 무시하는 것으로 가정한다<sup>[14]</sup>.

소 신호 상태 공간 방정식 식(7)로부터 전압 제어기 설계를 위한 제어 입력에 대한 출력 전압 전달함수를 식(8)과 같이 유도 할 수 있으며, 전달함수의 계수는 부 록에 나타내었다.

$$G_{vd} = \frac{\hat{v_o}}{\hat{d}} = \frac{a_3 s^3 + a_2 s^2 + a_1 s + a_0}{p_4 s^4 + p_3 s^3 + p_2 s^2 + p_1 s + p_0} \tag{8}$$

그림 6(a)는 개 루프 상태에서의 제어입력에 대한 출력전압 전달함수의 이득/위상 주파수 응답을 보여준다. 저 주파수(2.8Hz)와 고 주파수(68kHz) 영역에서 각각 실수 극점이 하나씩 위치하며 2.24kHz 지점에 복소 극점(Complex pole) 한 쌍이 위치하여 공진 주파수가 형성되며 총 4개의 극점을 가진 시스템이 된다. 또한 2개의실수 영점(2.5kHz, 68kHz)과 하나의 우 평면 영점(11kHz)이 공진 주파수 영역보다 높은 주파수 영역에 위치하는 것을 확인 할 수 있다. 저 주파수 영역에서의이득은 약 55dB이다. 그림 6(b) 개 루프 상태에서의 출력 임피던스 주파수 응답이다. 저 주파수 영역에서 이득/위상 여유가 감소하므로 극점이 존재하는 것을 알 수 있다.

## 3. 제어기 설계

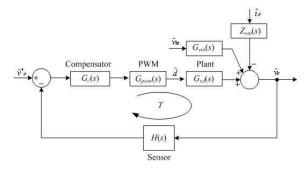

그림 7 은 부스트-플라이백 컨버터의 출력 전압 제어 블록도를 나타내며, 식(9)로 표현된다.  $G_{vel}(=\hat{v_o}/\hat{d})$ 는 제어 입력에 대한 출력 전압 전달함수,  $G_{vin}$

$$\hat{v_o} = \hat{v_o}^* \frac{1}{H} \frac{T}{1+T} + \hat{v_{in}} \frac{G_{vin}}{1+T} - \hat{i_o} \frac{Z_{out}}{1+T}$$

$$T = G_c G_{pwm} G_{vd} H$$

(9)

그림 7 부스트-플라이백 컨버터의 출력 전압 제어 블록도

Fig. 7 Block diagram of the output voltage control

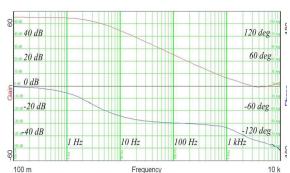

그림 8 루프이득 7의 주파수 응답

Fig. 8 Frequency response of loop gain

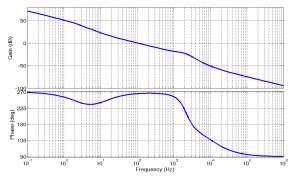

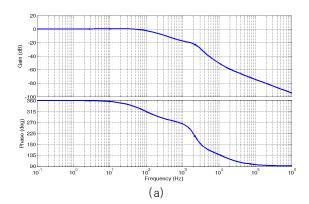

그림 9 폐 루프 상태에서의 부스트-플라이백 컨버터 주파수 응답

- (a) 기준 전압에 대한 출력 전압 전달함수

- (b) 출력 임피던스

Fig. 9 Frequency responses of boost-flyback converter in closed loop by MATLAB

- (a) Reference-to-output transfer function

- (b) Output impedance

$(=\hat{v_o}/\hat{v_{in}})$ 은 입력 전압에 대한 출력 전압의 전달함수,  $Zout(=\hat{v_o}/\hat{i_o})$ 은 출력 임피던스, Gc는 보상기, Gpwm은 PWM 이득, H는 센서 이득, T는 루프 이득을 나타낸다. 부스트-플라이백 컨버터는 저 주파수 영역에 위치한 극점의 영향으로 위상 여유가 감소하므로 이를 고려하

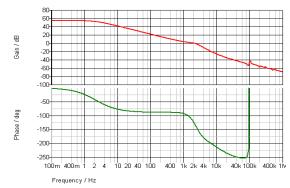

그림 10 SIMPLIS에 의한 제어 입력에 대한 출력 전압의 주파수 응답

Fig. 10 Frequency response of control-to-output transfer function by SIMPLIS

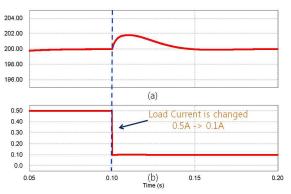

그림 11 부하 가변 시 출력 파형 (a) 출력 전압(b) 부하 전류

Fig. 11 Load variation

(a) Output voltage (b) Load current

여 제어기를 설계하여야 한다. 부하 가변 시에도 안정적인 출력 전압 추종이 가능한 피드백 제어 루프 설계를위해, 제어입력에 대한 출력 전압 전달함수를 기반으로하여 비례-적분(Proportional-Integral, PI) 보상기를 아래와 같은 과정으로 설계하였다. 1) 정상 상태의 오차를제거하기 위해서 적분에 해당하는 극점을 추가한다.(0Hz) 2) 10Hz에 영점을 추가하여 공진 주파수 앞에서의 위상 여유를 확보한다. 3) 크로스오버 주파수를 공진 주파수의 10배 정도 낮은 지점에 위치시켜 시스템의안정도를 높인다.(100Hz) 4) dc 이득을 결정한다. 그림 8은 설계된 PI 제어기를 적용한 루프이득 T의 주파수응답이다. 100Hz 의 주파수 대역폭과 85°의 위상 여유를확보함으로서 시스템이 빠른 응답 속도와 높은 안정성을 갖도록 하였다.

그림 9(a)는 폐 루프 상태에서의 기준 전압에 대한 출력 전압 전달함수의 주파수 응답이며, 그림 9(b)는 폐루프 상태에서의 출력 임피던스 이다. 저 주파수 영역에서 출력 임피던스의 크기가 음의 큰 값을 갖는 것을 확인할 수 있다.

#### 4. 시뮬레이션 결과

그림 10는 SIMPLIS 시뮬레이터를 이용하여 부스트-플라이백 컨버터의 이득/위상 여유 주파수 응답을 나타낸 것이다. 그림 6(a)에서 얻어진 제어입력에 대한 출력전압 전달함수와 비교하면 결과가 일치하는 것을 확인할 수 있으며, 이것은 제안된 모델링 방법의 유효함을 증명한다. 단, 그림 10에서 고 주파수 영역(100kHz)의갑작스런 변화는 시뮬레이션에서 스위칭 주파수를 100kHz로 선정하였기 때문이다.

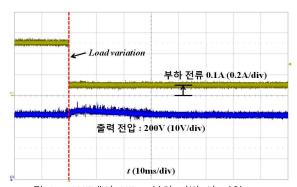

그림 11은 제어 입력에 대한 출력 전압 전달함수를 바탕으로 하여 설계된 PI제어기를 시스템에 적용한 후, 부하 가변 시에도 출력 전압(200V)을 일정하게 추종하는 PSIM 시뮬레이션 결과이다. 부스트-플라이백 컨버터는 정상 상태에서 100W의 정격 전력과 200V 출력 전압을 유지하도록 설계하였으며, 출력 전력이 100W에서 20W로 가변되어도 출력 전압은 일정하게 200V를 추종한다. 과도 상태에서 시스템의 출력 전압변동은 정상상태 출력 전압(200V)의 1% 범위이다.

#### 표 1 시스템 소자의 주요 정격

Table 1 The specification of system component

| Parameter               | Symbols | Values   |

|-------------------------|---------|----------|

| Output power            | Ро      | 100[W]   |

| Input voltage           | Vin     | 30[V]    |

| Output voltage          | Vo      | 200[V]   |

| Boost inductance        | Lb      | 15[μH]   |

| Magnetizing inductance  | Lm      | 200[µH]  |

| DC-link capacitance     | Се      | 4.4[μF]  |

| Output capacitance      | Со      | 440[μF]  |

| Output resistance       | R       | 400[Ω]   |

| Switching frequency     | fs      | 100[kHz] |

| Transformer turns ratio | n       | 5        |

그림 12 주파수 분석기(Venable model 3120)에 의한 100W IBFC의 이득/위상 주파수 응답

Fig. 12 Gain/phase plot of the 100W IBFC by FRA(Venable model 3120)

#### 5. 실험 결과

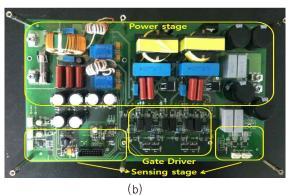

표 1에 제시된 정격으로 100W급 프로토 타입 실험 세트를 제작하여 실험을 수행하였고 제어기는 TI사의 TMS320F28335 DSP를 이용하여 구현하였다.

그림 12는 주파수 분석기(Frequency Response Analyzer: Venable model 3120)를 이용하여 얻어진 이 득/위상 주파수 응답이다. 그림 6(a)에 나타낸 제안된 모델링 방법에 의한 이론적인 주파수 응답 파형과 그림 10에 나타낸 SIMPLIS 시뮬레이션 주파수 응답 파형을 그림 12와 비교하면 시스템의 주파수 응답 특성이 일치하는 것을 확인할 수 있다. 10kHz 이상의 고 주파수 영역에서는 출력단 전해 커패시터에 존재하는 내부 등가 직렬 저항(Equivalent Series Resistor: ESR)이 시스템에 미치는 영향이 커지기 때문에 이론적인 주파수 응답 파형과 실험 결과가 일치하지 않는다.

그러나, 부스트-플라이백 컨버터는 저 주파수 영역에서 정상 동작 특성을 갖도록 설계하였으며, 전압 제어기의 대역폭도 100Hz 이므로, 고 주파수 영역에서의시스템의 특성은 고려 대상이 아니다. 따라서, 주파수 응답실험 결과는 저 주파수 영역(5kHz 이하)에서 이

그림 13 능동 소자 회로를 포함한 200W급 IBFC (a) 회로도(b) 실험 세트

Fig. 13 200W IBFC with active-clamping circuit (a) Schematic diagram (b) Prototype

그림 14 100W에서 20W로 부하 가변 시 파형 Fig. 14 Load variation from 100W to 20W

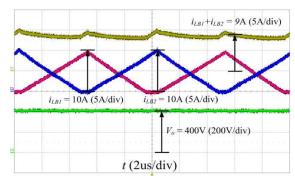

그림 15 인터리브드 운전시 부스트 인덕터 전류와 출력 전압 파형

Fig. 15 Boost inductor current and output voltage waveform under interleaved operation

론적인 예측값과 비교하였으며, 그 결과는 제안된 방법 의 유효함을 보여준다.

그림 13(a)는 능동 클램핑 회로(Active-clamping circuit)가 추가된 100W급 부스트-플라이백 컨버터 2대를 병렬 연결하여 200W급 시스템을 구성한 회로도이다. 능동 클램핑 회로는 클램핑 커패시터( $C_c$ )와 보조 스위치( $S_{aux}$ )로 구성되어 있으며,  $L_r$ 은 변압기의 누설 인덕터이다. 그림 13(b)는 실제 제작된 200W급 프로토 타입실험 세트이다.

그림 14는 100W급 부스트-플라이백 컨버터의 부하가면 시 성능 실험 결과이다. 시스템 부하를 100W에서 20W로 가변 하더라도 출력 전압을 안정적으로 유지하는 것을 확인할 수 있으며, 그림 11의 시뮬레이션 결과와 일치한다.

그림 15는 200W급 프로토 타입 시스템을 인터리브드 방식으로 운전하여 측정한 실험 파형이다. 인터리브드 방식을 적용함으로서 시스템에서 발생하는 도통 손실 (Conduction loss)를 저감하였다.

부스트 인덕터  $L_{bl}$ 과  $L_{b2}$ 의 전류 파형이  $180^{\circ}$  위상차로 불연속 도통 모드(DCM)에서 동작하며, 400V 출력 전압을 확인할 수 있다.

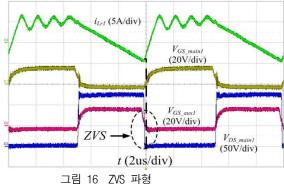

그림 16은 영전압 스위칭(Zero-voltage-switching : ZVS)이 이뤄지는 실험 파형을 나타낸다. 일반적인 부

그림 16 ZVS 파영 Fig. 16 ZVS waveforms

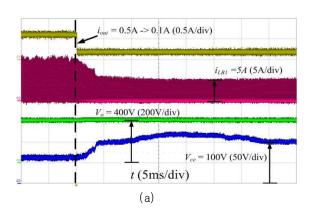

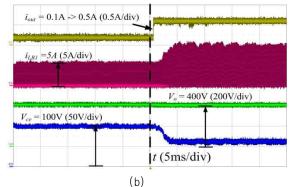

그림 17 부하 가변 실험 파형

- (a) 출력 전력을 200W에서 40W로 감소 시킨 경우

- (b) 출력 전력을 40W에서 200W로 증가 시킨 경우

Fig. 17 Load variation

- (a) Output power level change from 200W to 40W

- (b) Output power level change from 40W to 200W

스트-플라이백 컨버터의 경우, 스위칭 소자에 높은 전압 스트레스가 발생한다. 이러한 문제점을 해결하기 위해 능동 클램핑 회로를 추가하면, 전압 스트레스를 최소화하면서 영전압 스위칭이 이루어져 시스템의 안정성을 향상시킨다. 메인 스위치( $S_{main1}$ )의 드레인-소스 전압 ( $V_{DS\_main1}$ )이 영으로 감소한 후, 메인 스위치에 게이트 신호( $V_{GS\_main1}$ )가 인가되는 것을 확인할 수 있다.

그림 17(a)는 부스트-플라이백 컨버터의 부하 가변 시 실험 결과이다. 시스템이 정상 상태에서 동작하는 경우, 출력 전압은 400V, 정격 출력 전력은 200W이다. 시스템의 부하를 40W(정격 출력 전력의 20%)로 가변 하여도전압 제어기에 의해 승압된 출력 전압(400V)을 추종한다. 부하가 가변됨에 따라 커패시터  $C_e$  전압이 증가하고, 부하 전류가 감소한다. 그림 17(b)는 반대의 경우로, 20% 정격 출력에서 100% 정격 출력 전력으로 부하를가변 한 경우에도 일정하게 높은 전압 추종이 가능한것을 볼 수 있다. 따라서 제안된 모델링 방법을 기반으로 하여 설계된 제어기가 유효함을 증명한다.

# 6. 결 론

본 논문에서는 부스트-플라이백 컨버터의(Integrated boost-flyback converter, IBFC)의 동작 특성 및 정상상태 해석을 위한 개선된 모델링 방법과 부하 가변 시에도 안정적인 출력 전압을 유지하는 제어기 설계 방법을 제시하였다. 제안된 방법은 부스트-플라이백 컨버터를 등가 전류 소스를 갖는 독립적인 두 개의 컨버터로 분리하여 상태 공간 방정식을 유도하기 위한 수학적인절차를 간소화 하였고, 적합한 제어기 설계도 수행하였다. 프로토 타입으로 제작된 200W 실험 세트에서는 시스템에서 발생하는 도통 손실과 소자의 전압 스트레스를 저감하기 위해 인터리브드 방식과 영 전압 스위칭기법을 적용하였다. 수행된 시뮬레이션 및 실험 결과는이론적인 예측 결과와 일치하는 것을 확인 하였다. 따라서, 제안된 모델링 방법과 이를 바탕으로 설계된 전압제어기의 유효함을 검증하였다.

#### 부 록

Coefficient of control-to-output transfer function (6)

$$G_{\!v\!d} = \frac{\hat{v_o}}{\hat{d}} = \frac{a_3 s^3 + a_2 s^2 + a_1 s + a_0}{p_4 s^4 + p_3 s^3 + p_2 s^2 + p_1 s + p_0}$$

$p_4 = C_{ce} \cdot C_o \cdot D \cdot L_B \cdot L_M \cdot R \cdot V_{in} \cdot f_s \cdot n^2$

$p_3 = C_{ce} \cdot L_B \cdot L_M \cdot f_s \cdot n^2 \cdot (D \cdot V_{in} + 2 \cdot C_o \cdot R \cdot V_{ce} \cdot f_s - 2 \cdot C_o \cdot R \cdot V_{in} \cdot f_s)$

$p_2 = L_B \cdot V_{in} \cdot f_s \cdot (C_{ce} \cdot D \cdot R - 2 \cdot C_{ce} \cdot D^2 \cdot R + C_{ce} \cdot D^3 \cdot R - 2 \cdot C_{ce} \cdot L_M \cdot n^2 + C_o \cdot D^3 \cdot R \cdot n^2)$   $+ L_M \cdot f_s \cdot n^2 \cdot (2 \cdot C_{ce} \cdot V_{ce} \cdot L_B \cdot f_s - 2 \cdot C_o \cdot I_{LB} \cdot L_B \cdot R \cdot f_s - C_o \cdot D^2 \cdot R \cdot V_{in})$

$$\begin{split} p_1 &= 2 \cdot L_B \cdot R \cdot f_s^2 \cdot \left( C_{ce} \cdot V_{in} - 2 \cdot C_{ce} \cdot D \cdot V_{ce} + 2 \cdot C_{ce} \cdot D \cdot V_{in} + C_{ce} \cdot D^2 \cdot V_{ce} - C_{ce} \cdot D^2 \cdot V_{in} \right. \\ &\quad + C_o \cdot D^2 \cdot V_{ce} \cdot n^2 - C_o \cdot D^2 \cdot V_{in} \cdot n^2 \right) + L_B \cdot f_s \cdot \left( 2 \cdot I_{LB} \cdot L_M \cdot n^2 + D^3 \cdot V_{in} \cdot n^2 + 2 \cdot C_{ce} \cdot R \cdot V_{ce} \right) \\ &\quad - D^2 \cdot L_M \cdot V_{in} \cdot f_s \cdot n^2 \end{split}$$

$p_0 = D^2 \cdot R \cdot f_s \cdot (2 \cdot D \cdot V_{in} - V_{in} - D^2 \cdot V_{in} + 2 \cdot L_B \cdot V_{ce} \cdot f_s \cdot n^2 - 2 \cdot L_B \cdot V_{in} \cdot f_s \cdot n^2 + 2 \cdot I_{LB} \cdot L_B \cdot f_s) + 2 \cdot I_{LB} \cdot L_B \cdot R \cdot f_s^2 (1 - 2 \cdot D)$

$a_3 = C_{ce} \cdot D \cdot I_{LM} \cdot L_B \cdot L_M \cdot R \cdot V_{in} \cdot f_s \cdot n$

$a_2 = C_{ce} \cdot L_B \cdot R \cdot f_s \cdot D \cdot V_{in} \cdot (2 \cdot D \cdot V_o + D \cdot V_{ce} \cdot n - V_{ce} \cdot n)$ +  $2 \cdot I_{LM} \cdot L_B \cdot L_M \cdot R \cdot f_s^2 \cdot n \cdot (V_{ce} - V_{in})$

$a_1 = D^3 \cdot R \cdot V_{ln^2} \cdot n \cdot (1 - D) - 2 \cdot C_{ce} \cdot L_B \cdot R \cdot V_o \cdot f_s^2 \cdot (V_{ce} - V_{ln})$   $-2 \cdot C_{ce} \cdot L_B \cdot R \cdot V_{ce} \cdot f_s^2 \cdot (V_{ce} - 1) - 2 \cdot C_{ce} \cdot D \cdot L_B \cdot R \cdot f_s^2$   $\cdot (V_{ln} \cdot V_o - V_{ce}^2 \cdot n + V_{ce} \cdot V_{ln} \cdot n) + D^3 \cdot I_{LM} \cdot R \cdot V_{ln} \cdot f_s \cdot n \cdot (L_B - L_M)$   $+ 2 \cdot L_B \cdot R \cdot f_s^2 \cdot n \cdot (I_{LB} \cdot I_{LM} \cdot L_M + C_{ce} \cdot V_{ce} \cdot V_{ln})$

$a_0 = 2 \cdot I_{LB} \cdot L_B \cdot R \cdot f_s^2 \cdot (D \cdot V_o - V_o - 2 \cdot V_{ce} \cdot n + V_{in} \cdot n$   $+ 2 \cdot D \cdot V_{ce} \cdot n - D \cdot V_{in} \cdot n) + D^2 \cdot R \cdot V_{in} \cdot f_s \cdot (V_o - D \cdot V_o - 2 \cdot V_{in} \cdot n$   $+ D \cdot V_{in} \cdot n + 2 \cdot V_{ce} \cdot n - 2 \cdot D \cdot V_{ce} \cdot n) + 2 \cdot D \cdot I_{LM} \cdot L_B \cdot R \cdot f_s^2 \cdot n \cdot (V_{ce} - V_{in})$

# 참 고 문 헌

- [1] 김만고, "능동 클램프 풀브릿지 부스트 컨버터에 대한 모델링 및 분석", 전력전자학회 논문지, 제 10권 제 2호, pp.169-176, 2005. 4.

- [2] 이준영, 문건우, 김현수, 윤명중, "부스트-플라이백 결합형 ZCS Quasi-Resonant 역률개선 컨버터", 전력전자학회 논문지, 제 4권 제 1호, pp.91-98, 1999. 2.

- [3] Yim-Shu Lee and Bo-Tao Lin, "Adding active clamping and soft switching to boost-flyback single-state isolated power-factor-corrected power supplies," in IEEE Trans.on vol. 12, no. 6, 1997, pp. 1017–1027.

- [4] Liang, T.J and Tseng, K.C, "Novel high-efficiency step-up converter," IEE proceeding in Electric Power Application, vol.151, no.2, 2004, pp. 182–190

- [5] Spiazzi, G., Mattavelli, P., Gazoli, J.R., Magalhaes, R. and Frattini, G, "Improved Integrated Boost Flyback High Step-up Converter," in IEEE2010 Industrial Technology, 2010, pp.1169-1174.

- [6] R. Watsonetal., "Utilization of an active-clamp circuit to achieve soft switching in flyback converters," inProc. IEEE PESC'94 Rec., pp.909 - 916.

- [7] D. Czarkowski and M. K. Kazimierczuk, "Energy-conversion approach to modeling PWM dc-dc converters", IEEE Trans. Aerosp Electron. Syst., vol. 29, pp. 1059-1063, July 1993.

- [8] M. K. Kazimierczuk and D. Czarkowski, "Application of the principle of energy conservation modeling the PWM converters," in Proc. 2nd IEEE Conf. Control Applications, vol.1, Vancouver, Canada, Sept.13–16, 1993, pp.291–296.

- [9] S. Cuk and R. D. Middelbrook, "A general unified approach to modeling switching dc-to-dc converters in discontinuous conduction mode," in Proc. IEEE Power Electronics Specialists Conf. PESC'77, 1977, pp.36 - 57.

- [10] Rae-Young Kim and Jih-sheng Lai, "Aggregated modeling and control of a boost-buck cascade converter for maximum power point tracking of a thermoelectric generator," in IEEE 2008 Applied Power Electronics Conference, 2008, pp. 1754–1760.

- [11] D. Maximovic and S. Cuk, "A unified analysis of PWM converter in discontinuus modes," IEEE Trans. Power Electron., vol.6,pp.476 490,July1991.

- [12] J. Sun, D. M. Mitchell, M. F. Greuel, P. T. Kreain, and R. M. Bass, "Averaging models of PWM converter operating in discontinous mode," IEEETrans.PowerElectron.,vol.16,pp.482 491,July2001.

- [13] Liang, T.J and Tseng, K.C, "Analysis of integrated boost-flyback step-up converter," IEEE proceeding in Electric Power Application, 2005, pp. 217–225.

- [14] W.Erickson and D.Maksimovic, "Fundamentals of Power Electronics," second edition, Springer Science,

#### 서상욱(徐尙郁)

1983년 1월 9일생. 2010년 홍익대 전자전기 공학부 졸업. 2010년~현재 한양대 대학원 전기공학과 석사과정

#### 이귀준(李貴俊)

1979년 7월 19일생. 2005년 한양대 전자전기 컴퓨터공학부 졸업. 2005년~현재 한양대 대 학원 전기공학과 석박사통합과정.

# 김래영(金來瑛)

1974년 6월 6일생. 1997년 한양대 전기공학과 졸업. 1999년 동 대학원 전기공학과 졸업 (석사). 2009년 미국 버지니아 공대 (Virginia Tech) 대학원 전기공학과 졸업(공박). 1999년~2004년 효성 중공업 연구소 선임연구원.

2009년~2010년 미국 National Semiconductor Post Doc. Researcher. 2010년~현재 한양대 전기생체공학부 조교수. 당학회 JPE 편집위원.

## 현동석(玄東石)

1950년 4월 8일생. 1973년 한양대 전기공학과 졸업. 1978년 동 대학원 전기공학과 졸업(석사). 1986년 서울대 대학원 전기공학과 졸업(공박). 1984년~1985년 미국 토레도대학교환교수. 1988년~1989년 뮌헨공과대학 교

환교수. 2003년 IEEE, Fellow Member. 1979년~현재 한양대 전 기생체공학부 교수. 2000년 당 학회 회장 역임.