# 누화 특성 감소를 위한 MEMS 프로브 커넥터 시스템의 설계

# Design and Crosstalk Analysis of MEMS Probe Connector System

배현주·김종현·이준상·Bo Pu·이재중·나완수

Hyeonju Bae · Jonghyeon Kim · June-Sang Lee · Bo Pu · Jae Joong Lee · Wansoo Nah

요 익

본 논문에서는 프로브 커넥터 핀의 누화 특성이 -30 dB 이하를 만족시키는 핀의 피치 및 길이 파라미터에 대한 설계 기준을 제시하였다. 프로브 커넥터 핀의 누화 특성을 분석하기 위하여 격자 구조로 배열된 프로브 커넥터 핀의 인덕턴스 성분과 커패시턴스 성분을 추출하였으며, 접지 핀의 개수가 증가해도 이미 계산된 파라미터들을 이용해서 새로운 커패시턴스 및 인덕턴스 성분들을 쉽게 계산할 수 있음을 보였다. 또한, 신호(signal) 핀 주변에 위치한 접지(ground) 핀 개수를 증가시키면서 누화 특성을 향상시키는 알고리즘을 제시하였으며, 특히 접지 핀 개수의 증가가 자기장 결합(inductive coupling)에 의한 누화를 효과적으로 제거시킨다는 것을 보였다. 최종적으로는 주어진 접지 핀 개수 및 형상 하에서 -30 dB 이하의 누화 특성을 만족하는 핀의 피치 및 길이를 결정하는 영역을 도시하였으며, 이는 프로브 커넥터 시스템의 누화 특성 설계 시 유용하게 사용할 수 있을 것으로 사료된다.

#### **Abstract**

In this paper, we propose a design method that the crosstalk of probe connector pins satisfy the limitation of -30 dB. The parameters (inductance and capacitance) were extracted in the grid-structured probe connector pin system, and it is shown that the new parameters are easily calculated with increasing ground pin numbers using the previously calculated parameters. In addition, the crosstalk reduction algorithm by employing more grounds around the signal pin has been suggested, and it is confirmed that the suggested method is quite effective especially for the reduction of inductive couplings. Finally, we suggested the correlation between the pitch and the length of the pins to satisfy the crosstalk limitation of -30 dB with the given number of ground pins, which will be quite useful when design a probe connector pin system.

Key words: Coupling, Crosstalk, MEMS, Parameter Extraction, Signal Integrity

# Ⅰ. 서 론

최근 디지털 시스템은 제품의 휴대를 위해 갈수록 소형화되어 생산되고 많은 정보를 빠르게 처리하기 위해 고속 신호의 전송 및 처리가 가능한 반도체개발을 요구하고 있다. 기존 반도체 패키지(package)

기술에서 신호 전송은 와이어 본딩(wire bonding)을 이용하였으나, 고속 신호의 전송 시 기생 성분에 의한 신호 왜곡과 패키지 크기 축소의 한계가 있으며, 이를 극복하기 위해 TSV(Through-Silicon-Via) 기반 3차원 집적 회로(3D Integrated Circuit) 기술이 제안되었다. TSV 기술을 이용하면 고집적을 구현하면서도 기

<sup>「</sup>이 연구는 교육과학기술부가 주관하는 21세기 프론티어연구개발사업의 일환인 나노메카트로닉스기술개발사업단의 연구비 지원 (2011K000255)에 의해 수행되었습니다.

성균관대학교 전자전기컴퓨터공학과(Department of Electronical and Computer Engineering, Sungkyunkwan University)

<sup>·</sup>논 문 번 호 : 20111005-116

<sup>·</sup>교 신 저 자 : 나완수(e-mail : wsnah@skku.edu)

<sup>·</sup>심사일자 : 2011년 11월 14일 ·수정완료일자 : 2012년 1월 11일

존의 그 어떤 연결선보다도 짧은 전기적 연결선을 구현할 수 있으며, 기존 반도체 패키지 기술을 이용할 수 있어 기술 및 경제적 한계를 극복할 수 있다 $^{[1]}$ . 웨이퍼(wafer) 상태의 반도체를 테스트(test)하기 위하여 기존에는 피치(pitch)가 수 백  $\mu$ m인 프로브 카드(probe card)를 이용하였지만, TSV 기술을 이용한 반도체의 피치가 수 십  $\mu$ m로 줄어드는 경향으로 인해 대부분의 프로브 카드는 MEMS(Micro Electro Mechanical System) 기술을 적용하여 제작되고 있다 $^{[2]}$ .

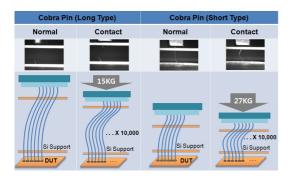

본 논문에서 분석할 프로브 커넥터(connector) 핀 을 그림 1에 나타내었다. 고집적을 구현하기 위하여 수평(horizontal)이 아닌 수직(vertical)형 커넥터 핀을 사용하였으며, 반도체 테스트 시 커넥터 핀의 길이 에 따른 컨택 포스(contact force)를 비교하였다. 길이 가 긴 커넥터 핀과 길이가 짧은 커넥터 핀이 10,000 개가 있을 때 각 핀의 컨택 포스는 15 kg과 27 kg이 며, 길이가 긴 커넥터 핀보다 짧은 커넥터 핀을 사용 할 경우 컨택 포스가 더 많이 필요하다. 이러한 기계 적 특성 때문에 커넥터 핀의 반지름과 피치는  $\mu m$ 단위임에도 불구하고, 길이는 mm 단위로 길게 설계 되어야 하며, 수 십  $\mu$ m 피치로 배열된 커넥터 핀들 간의 커플링(coupling)으로 인해 신호 전달에 제약을 받게 된다. 따라서 고속 신호 전송이 가능한 프로브 카드의 개발을 위해서는 프로브 카드를 구성하는 부 품의 신호 전달 특성을 분석하는 것이 매우 중요하 며, 여러 부품 중에서도 신호의 밀도가 가장 높은 프 로브 커넥터 핀에서의 고주파 신호 전달 특성 개선 및 커넥터 간의 노이즈(noise) 커플링 저감에 관한 연구가 필수적으로 요구된다.

그림 1. 코브라 타입의 MEMS 프로브 커넥터 핀 Fig. 1. Cobra-type MEMS probe connector pin.

본 논문에서는 프로브 커넥터 핀의 누화 특성이 -30 dB 이하를 만족하는 핀의 피치 및 길이에 대한 설계 기준을 제시하였다. 프로브 커넥터 핀의 누화 특성을 분석하기 위하여 40 μm 피치로 배열된 격 자 구조의 프로브 커넥터 핀의 인덕턴스와 커패시턴 스 성분을 추출하였으며, 접지 핀의 개수가 증가해 도 이미 계산된 파라미터 결과를 이용하여 새로운 커패시턴스 및 인덕턴스 성분들을 쉽게 계산할 수 있음을 보였다. 또한, 신호 핀 주변에 위치한 접지 핀 개수를 증가시키면서 누화 특성을 향상시키는 알 고리즘을 제시하였으며, 특히 접지 핀 개수의 증가 가 자기장 결합에 의한 누화를 효과적으로 제거시킨 다는 것을 보였다. 최종적으로는 주어진 접지 핀 개 수 및 형상 하에서 -30 dB 이하의 누화 특성을 만 족하는 핀의 피치 및 길이를 결정하는 영역을 도시 하였다.

### Ⅱ. 파라미터 추출

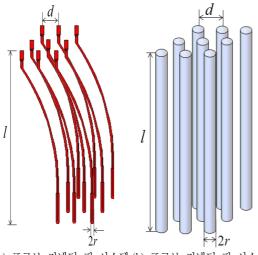

반도체 칩을 테스트하기 위하여 프로브 카드 내 커넥터 핀은 ATE(Auto Test Equipment)로부터 발생하는 테스트 신호(test signal)를 DUT(Device Under Test)까지 왜곡 없이 전달하는 역할을 한다. 프로브카드 내 수 십  $\mu$ m 피치로 배열된 프로브 커넥터 핀의 간단한 구조를 그림 2에 나타내었고, l은 커넥터 핀의 길이, d는 커넥터 핀의 피치, r은 커넥터 핀의 반지름이다. 커넥터 핀 간 커플링의 정도를 예측하기 위하여 커넥터 핀의 인덕턴스와 커패시턴스 성분을 계산하였으며, 커넥터 핀의 파라미터 추출 순서도는 그림 3에 나타내었다.

격자 구조로 배열된  $n \times n$ 개  $(n \ge 1)$  커넥터 핀의 파라미터 추출을 위해서 인덕턴스를 먼저 계산하였고, 계산식은 식 (1)과 식 (2)에 나타내었다<sup>[3]</sup>. 모든 커넥터 핀의 길이는 무한히 길다고 가정하여 각 핀의 모서리 효과(fringe field)는 고려하지 않은 이차원 해석을 하였으며, 커넥터 핀의 전류 분포는 동일하다고 가정하였다. 식 (1)과 식 (2)로부터 계산한  $n \times n$ 개 인덕턴스 행렬을 역행렬 취하여  $\mu \epsilon I$ 를 곱하면 일반화된 커패시턴스 행렬 $(C_g)$ : generalized capacitance)  $n \times n$ 개 커넥터 핀 중에서 접지 핀의 개수가  $n \times n$ 개 커넥터 핀 중에서 접지 핀의 개수가  $n \times n$ 개 커넥터 핀 중에서 접지 핀의 개수가  $n \times n$ 개 커넥터 핀 중에서 접지 핀의 개수가  $n \times n$ 개 커넥터 핀 중에서 접지 핀의 개수가  $n \times n$ 개 커넥터 핀 중에서 접지 핀의 개수가  $n \times n$ 개 커넥터 핀 중에서 접지 핀의 개수가  $n \times n$

- (a) 프로브 커넥터 핀 시스템(b) 프로브 커넥터 핀 시스

(a) Probe connector pin

템의 단순화 모델

- system (b) Simplified model of probe connector pin system

그림 2. 프로브 커넥터 핀 시스템의 구조 Fig. 2. Structure of probe connector pin system.

$\mathcal{H}(m \geq 1)$ 이면 인덕턴스와 커패시턴스 행렬의 크기는  $(n-m) \times (n-m)$ 개이다. 접지 핀의 개수에 따른  $(n-m) \times (n-m)$ 개의 커패시턴스 행렬은 식(4)를 이용하여 구할 수 있으며, 4장에서 언급하겠지만, 접지 핀의 개수가 m개보다 증가하여도 커패시턴스 행렬 계산식은 식(4)와 동일하다<sup>[6]</sup>. 식(4)로부터 계산한 결과를 역행렬 취하여 다시  $\mu\epsilon I$ 를 곱하면  $(n-m) \times (n-m)$ 개 인덕턴스 행렬을 계산할 수 있으며, 이것을 식(5)에 나타내었다.

이와 같은 방법으로 커넥터 핀의 파라미터를 추출할 수 있으며, 반지름은 13.5  $\mu$ m이고, 길이는 3 mm인 3개의 커넥터 핀이 40  $\mu$ m 피치로 배열된 구조에서 1개 접지 핀이 가운데에 위치할 때 그 외 2개신호 핀의 인덕턴스와 커패시턴스를 계산하였다. 2 개의 신호 핀 중에서 접지 핀을 기준으로 좌측과 우측에 신호 핀 1번과 2번을 배치한 파라미터 계산 결과를 표 1에 정리하였고, Ansys사의 Q3D를 이용하여 추출한 파라미터의 결과를 함께 나타내었다. 신호 핀 2개가 접지 핀을 기준으로 대칭이므로 자기인덕턴스와 커패시턴스의 값은 동일하며, 파라미터계산 결과와 시뮬레이션 결과가 잘 일치하는 것을확인할 수 있다. 또한, 그림 4에는 신호 핀이 2개이

그림 3. 파라미터 추출 순서도 Fig. 3. Flow chart of parameter extraction.

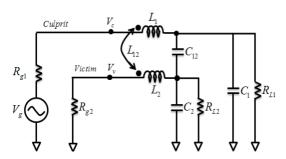

고, 접지 핀이 1개인 2+1개 도체 시스템의 집중정수 등가 회로(lumped equivalent circuit)를 나타내었다<sup>[7]</sup>. 커넥터 핀의 길이는 파장(wave length)의 1/10보다 짧다고 가정하였으므로 집중정수 등가 회로로 나타낼수 있으며, 추출한 인덕턴스와 커패시턴스 값을 등가 회로에 대입하면 자기장 및 전기장 결합 특성을 예측할 수 있다<sup>[8]</sup>.

#### Ⅲ. 자기장 및 전기장 결합 분석

앞 장에서 기술한 2+1 도체 시스템의 등가 회로에는 자기장과 전기장 결합(capacitive coupling)이 모두 포함되어 있으며, 이 회로를 바탕으로 자기장 및 전기장 결합을 분석할 수 있다. 또한, 각 결합의 분석결과를 이용하여 자기장과 전기장 결합 특성이 서로일치하는 주파수를 찾으면 각 결합의 경계가 되며,

표 1. 2+1 도체 시스템의 파라미터 추출 결과 Table 1. Extracted parameters for 2+1 conductor system.

| 파라미터                  | 계산      | 시뮬레이션   |  |

|-----------------------|---------|---------|--|

| $L_{11}[\mathrm{nH}]$ | 1.636   | 1.521   |  |

| $L_{12}[\mathrm{nH}]$ | 0.491   | 0.368   |  |

| $L_{22}[\mathrm{nH}]$ | 1.636   | 1.521   |  |

| $C_{11}[pF]$          | 0.07303 | 0.07464 |  |

| $C_{12}[pF]$          | 0.01918 | 0.02013 |  |

| $C_{22}[pF]$          | 0.07303 | 0.07464 |  |

관심 있는 주파수 대역에서 어떤 결합 특성이 우세 한지 예측할 수 있다.

자기장과 전기장 결합 특성이 일치하는 주파수를 계산하기 위해서 식 (6)번을 이용하여 그림 4에 나타 낸 등가 회로의 누화 특성을 계산하였다<sup>[9],[10]</sup>. 자기장 결합 계산 시 전기장 결합을 유도하는 커패시턴 스 성분은 무시하였고, 전기장 결합 계산 시 자기장 결합을 유도하는 인덕턴스 성분은 무시하였다.

그림 4에는 2개의 자기(self) 인덕턴스와 커패시턴 스, 1개의 상호(mutual) 인덕턴스와 커패시턴스가 존재한다. 표 1의 결과에 따라 접지 핀을 중심으로 신호 핀이 대칭으로 배열된 구조에서의 자기 인덕턴스와 커패시턴스의 값은 동일하므로  $L_{11}$  및  $L_{22}$ 는  $L_{s}$ ,  $C_{11}$  및  $C_{22}$ 는  $C_{s}$ 로 나타내고, 상호 인덕턴스와 커패시턴스  $L_{12}$  및  $C_{12}$ 는  $L_{m}$ 과  $C_{m}$ 으로 나타내었으며, 전원 저항  $R_{g1}$ 과  $R_{g2}$ , 부하저항  $R_{L1}$ 과  $R_{L2}$ 는 모두 R로 나타내었다. 이와 같은 방법으로 자기장 결합과 전기장 결합 특성이 일치하는 주파수를 식 (7)에 제시하였다.

그림 4. 2+1개 도체 시스템의 등가 회로

Fig. 4. Equivalent circuit of a 2+1 conductor system.

$$Crosstalk = 20 \text{Log} \left( \frac{V_v}{V_c} \right) \tag{6}$$

$Coupling\ boundary =$

$$-\frac{\left[R^{2}\left\{C_{m}^{2}\left(4L_{m}^{2}+5L_{s}^{2}\right)\right.\right]^{2}}{4\left[C_{m}^{2}\left(L_{s}+C_{m}\right)^{2}\right]^{2}}}{\left.-\frac{4\left(R^{4}C_{m}^{2}-L_{s}^{2}\right)^{2}\right]^{2}}{C_{m}^{2}\left(L_{m}^{2}-L_{s}^{2}\right)^{2}}}$$

$$-\frac{R^{2}\left\{C_{m}^{2}\left(4L_{m}^{2}+5L_{s}^{2}\right)\right.}{-L_{m}^{2}\left(C_{s}+C_{m}\right)^{2}\right\}}}{2C_{m}^{2}\left(L_{m}^{2}-L_{s}^{2}\right)}$$

(7)

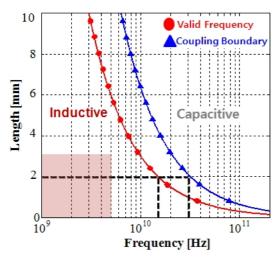

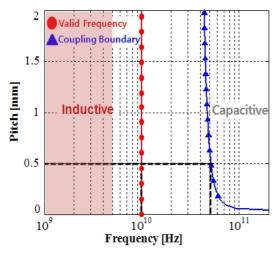

주파수 영역에서의 커넥터 핀의 길이와 피치가 증가함에 따른 전기장 및 자기장 결합의 경계를 확 인하기 위해 그림 1과 같이 반지름이 13.5  $\mu$ m인 3×3개 커넥터 핀이 배열된 구조에서 접지 핀 1개가 정 가운데에 위치할 때 그 외 8개 신호 핀의 인덕턴 스와 커패시턴스를 추출하였다. 커넥터 핀의 길이와 핀의 피치를 각각 10 mm와 2 mm까지 증가시켜 파 라미터를 추출하였으며, 커넥터 핀의 길이를 10 mm 까지 증가시킬 때 커넥터 핀의 피치는 40 μm로 일 정하고, 커넥터 핀의 피치를 2 mm까지 증가시킬 때 커넥터 핀의 길이는 3 mm로 일정하다. 8개의 신호 핀 중에서 접지 핀을 중심으로 양 옆에 위치한 신호 핀 2개의 파라미터의 결과와 4개의 저항 값 50 ohm 을 식 (7)번에 대입하여 주파수가 증가함에 따른 자 기장 및 전기장 결합의 경계를 그림 5와 그림 6에 나 타내었다. 또한, 식 (7)에 정리한 coupling boundary는 그림 4의 집중정수 등가 회로의 전기장 및 자기장 결합 특성으로부터 계산하였으므로 유효한 주파수 대역이 존재한다. 커넥터 핀의 길이가 파장(wave length)의 1/10보다 짧다고 가정하여 구한 유효 주파 수 대역을 그림 5와 그림 6에 valid frequency로 표시 하였으며, 본 논문에서 분석하려는 커넥터 핀의 길 이 3 mm와 주파수 대역 5 GHz를 진한 부분으로 표 시하였다.

그림 5에서 보는 것과 같이, 커넥터 핀의 길이 증가에 따른 전기장 및 자기장 결합의 경계는 coupling boundary를 기준으로 좌측 영역은 자기장 결합이 우세하다. 여를

그림 5. 커넥터 핀의 길이에 따른 자기장/전기장 결합의 경계

Fig. 5. The boundary of inductive/capacitive coupling according to the length of connector pin.

그림 6. 커넥터 핀의 피치에 따른 자기장/전기장 결합의 경계

Fig. 6. The boundary of inductive/capacitive coupling according to the pitch of connector pin.

들어 커넥터 핀의 길이가 2 mm일 때 30 GHz까지는 자기장 결합의 영향이 우세하며, 커넥터 핀의 길이가 2 mm일 때 유효 주파수 대역은 15 GHz까지이다. 한편, 커넥터 핀의 피치 증가에 따른 전기장 및 자기장 결합의 경계는 그림 6에서보는 것과 같이 coupling boundary를 기준으로 좌측 영역은 자기장 결합이 우세하며, 우측 영역은 전기장 결합이 우세하다.

예를 들어 커넥터 핀의 피치가 0.5 mm일 때 50 GHz 까지는 자기장 결합의 영향이 우세하며, 커넥터 핀의 피치가 0.5 mm일 때 핀의 길이는 3 mm로 일정하므로 유효 주파수 대역은 10 GHz까지이다.

따라서 일반적으로 커넥터 핀을 사용하는 주파수 대역에서는 자기장 결합의 영향이 우세한 것을 확인 할 수 있다.

#### Ⅳ. 프로브 커넥터 핀의 설계

MEMS 기술을 적용한 프로브 카드 내 커넥터 핀은 설계 시 사용할 주파수 대역에서의 누화를 고려하여 설계되어야만 한다. 이 장에서는 접지 핀의 개수에 따른 누화 특성을 분석하고, -30 dB 이하의 누화 특성을 만족하는 핀의 피치 및 길이를 결정하는 설계 방법을 정리하였다.

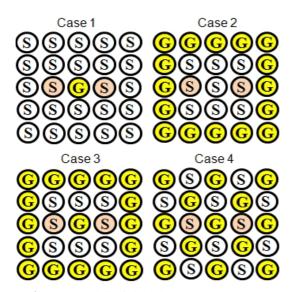

누화 특성에 영향을 미치는 접지 핀의 개수에 따 른 파라미터를 추출하기 위해 커넥터 핀의 반지름은 13.5 μm, 길이는 3 mm, 피치는 40 μm인 5×5개 커 넥터 핀의 배열 구조를 그림 7에 나타내었으며, 4가 지의 Case에서 정 가운데에 위치한 커넥터 핀의 양 옆에 위치한 신호 핀 2개의 파라미터 값을 추출하여 표 2에 정리하였다. 3장에서 설명하였듯이 추출한 파라미터의 값을 식 (6)에 대입하면 커넥터 핀의 전 기장 및 자기장 결합을 예측할 수 있다. 표 2에서 보는 것과 같이 접지 핀의 개수가 증가하거나 이상 적인 구조로 배열되면 상호 인덕턴스는 감소하지만, 상호 커패시턴스는 변화가 없다. 이것은 추출된 파 라미터를 이용하여 누화 특성을 예측하였을 때 자기 장 결합은 개선되지만, 전기장 결합은 변화가 없음 을 의미한다. 접지 핀의 개수 증가 시 상호 커패시턴 스의 값이 일정한 이유는 2장에서 언급한 식 (4)로부 터 알 수 있다. 접지 핀의 개수가 증가함에 따라 커 패시턴스 행렬의 행과 열은 소거되는데, 식 (4)의 분 모는 커패시턴스 행렬의 모든 항의 합으로 동일하 며, 식 (4)의 분자는 커패시턴스 행렬에서 소거되는 접지 핀의 각 행과 열에 해당하는 값의 합이 곱해지 므로 소거되지 않는 자기 커패시턴스와 상호 커패시 턴스의 값은 동일하다. 따라서 접지 핀의 개수가 증 가하더라도 이론적으로 상호 커패시턴스의 값은 변 하지 않는다.

그림 7. 5×5 커넥터 핀의 배열 구조 1 Fig. 7. Structures 1 of 5×5 connector pins.

표 2. 접지 핀의 배열 구조에 따른 인덕턴스와 커패 시턴스 비교

Table 2. Comparison of the inductance and capacitance according to the structures of ground pin.

| Case | $L_s[\mathrm{nH}]$ | $L_m[\mathrm{nH}]$ | $C_s[pF]$ | $C_m[pF]$ |

|------|--------------------|--------------------|-----------|-----------|

| 1    | 1.636              | 0.491              | 0.0026    | 0.0000109 |

| 2    | 1.041              | 0.127              | 0.0039    | 0.0000109 |

| 3    | 0.936              | 0.022              | 0.0065    | 0.0000109 |

| 4    | 0.857              | 0.007              | 0.0102    | 0.0000109 |

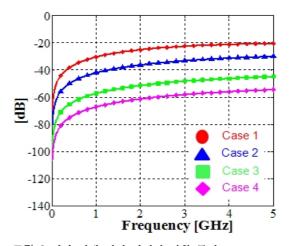

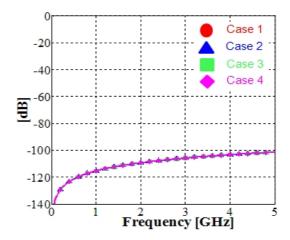

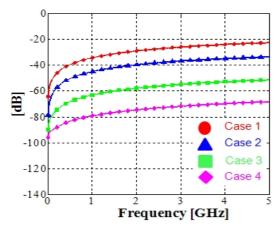

표 2에 정리한 4가지 Case의 자기장 결합 특성을 그림 8에 나타내었다. 그림 8에서 보는 것과 같이 자기장 결합은 Case 1에 비해 Case 4의 경우 약 -35 dB 개선되는 것을 확인할 수 있다. 또한, 표 2에 정리한 4가지 Case의 전기장 결합을 그림 9에 나타내었으며, 그림 10에는 4가지 Case의 자기장 결합과 전기장 결합이 모두 포함된 누화 특성을 나타내었다. 그림 9에 나타낸 4가지 Case의 전기장 결합은 접지 핀의 개수가 증가하거나 1개의 신호 핀을 접지 핀이 둘러싸고 있는 구조가 되어도 변화가 없는 반면, 그림 8과 10에서 보는 것과 같이 접지 핀의 개수에 따른 누화 특성은 자기장 결합과 전기장 결합이 모두 포함된 결과와 자기장 결합만을 나타낸 결과가 잘 일치하는 것을 알 수 있으며, 이것으로 우리가 일반적으로 사용하는 주파수 대역에서 접지 핀의 개수에

그림 8 접지 핀에 의한 자기장 결합 특성 Fig. 8. Inductive coupling according to the ground pin.

그림 9. 접지 핀에 의한 전기장 결합 특성 Fig. 9. Capacitive coupling according to the ground pin.

따른 누화 특성은 자기장 결합 특성이 우세하다는 것을 확인할 수 있다.

커넥터 핀의 설계 시 주파수가 증가함에 따른 누화 특성이 약 -30 dB 이하를 만족하면 신호 전달 측면에서 효율이 좋으며, 지금부터는 5 GHz 이내의 주파수 대역에서 -30 dB 이하의 누화 특성을 만족하는 핀의 피치 및 길이 파라미터를 결정하는 설계 방법을 제시하고자 한다.

그림 11에는 반지름은 13.5  $\mu$ m, 피치는 40  $\mu$ m, 길이는 3 mm인 커넥터 핀의 접지 핀 개수가 1개부터 3개까지 증가하는 3가지 경우의 배열 구조를 구성하였으며, 자기장 결합이 약 -30 dB 이하를 만

그림 10. 접지 핀에 의한 자기장 및 전기장 결합 특성의 3D 시뮬레이션 결과

Fig. 10. The result of 3D simulation for inductive and capacitive coupling according to the ground pin.

그림 11. 5×5 커넥터 핀의 배열 구조 2 Fig. 11. Structures 2 of 5×5 connector pins.

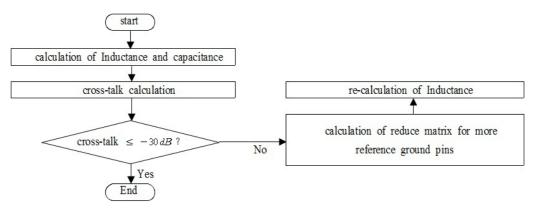

족하는 커넥터 핀의 설계 과정을 그림 12에 나타내었다. 우선 커넥터 핀의 인덕턴스와 커패시턴스를 추출하고, 3장에서 언급한 식 (6)을 이용하여 자기장 결합을 계산한다. 만약 계산한 커넥터 핀의 누화 특성이 -30 dB 이하를 만족한다면 기존에 설계했던 커넥터 핀의 파치와 길이를 그대로 사용하면 되지만 커넥터 핀의 누화 특성이 -30 dB 이상이라면 접지 핀을 추가로 더 배치해야 한다. 접지 핀을 추가로 더

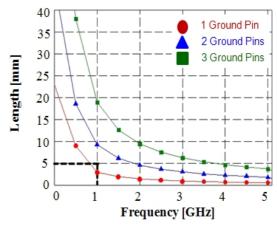

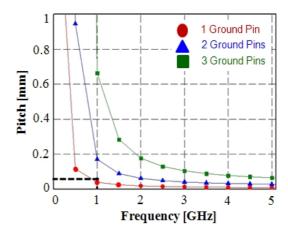

배치하면 식 (4)번을 이용하여 커패시턴스를 계산할 수 있으며, 이 결과에 따른 인덕턴스를 다시 계산하 여 자기장 결합을 예측하면 된다. 만약 이 경우에도 커넥터 핀의 누화 특성이 -30 dB 이하를 만족하지 않는다면 앞에서 소개한 방법과 같이 접지 핀을 더 추가하여 커넥터 핀의 파라미터를 추출하고, 다시 자기장 결합 특성을 예측하는 과정을 반복하면 된다. 5 GHz 이내의 주파수 대역에서 자기장 결합이 약 -30 dB 이하를 만족하는 커넥터 핀의 길이와 피치 를 계산한 결과를 그림 13과 그림 14에 나타내었다. 그림 13에서 보는 것과 같이, 설계자는 커넥터 핀의 길이를 가능한 짧게 설계해야 하며, 만약 커넥터 핀 의 길이를 더 이상 짧게 설계할 수 없는 상황이라면 신호 핀 주변에 접지 핀을 더 배치하여 커넥터 핀의 길이를 조금 더 짧게 설계할 수 있다. 예를 들어 동 작 주파수 대역이 1 GHz일 때 설계할 커넥터 핀의 길이가 5 mm라면, 그림 12에서 보는 것과 같이 자기 장 결합이 약 −30 dB 이하를 만족하기 위해서는 커 넥터 핀의 길이는 3 mm 이하가 되어야 한다. 커넥터 핀의 길이를 5 mm보다 짧게 설계할 수 없는 상황일 때 신호 핀 주변에 접지 핀을 하나 더 배치하여 모두 2개의 접지 핀을 배치하면 설계할 수 있는 커넥터 핀의 길이는 9.3 mm 이하가 되고, 이 상태에서 접지 핀의 개수를 하나 더 늘려 3개의 접지 핀을 배치하 면 설계할 수 있는 커넥터 핀의 길이는 19 mm 이하 가 되므로 커넥터 핀의 길이를 5 mm로 설계할 수 있 다. 주파수가 증가함에 따라 자기장 결합 특성이 약 -30 dB 이하를 만족하는 커넥터 핀의 피치는 그림 14에 나타내었다. 접지 핀의 개수가 3개인 경우 0.5 GHz에서 누화 특성이 -30 dB 이하를 만족하는 커 넥터 핀의 피치는 22 mm이며, 이것은 0.5 GHz에서 커넥터 핀의 피치는 누화에 영향을 미치지 않는다는 것을 의미한다. 주파수 대역이 증가할수록 커넥터 핀의 피치를 가능한 줄여야 자기장 결합이 약 -30 dB 이하를 만족할 수 있으며, 커넥터 핀의 피치를 더 이상 줄일 수 없는 상황이라면 신호 핀 주변에 접 지 핀의 개수를 추가하여 커넥터 핀의 피치를 조금 더 좁게 설계할 수 있다. 예를 들어 동작 주파수 대 역이 1 GHz일 때 설계해야 하는 커넥터 핀의 피치가 50 μm라면 그림 14에서 보는 것과 같이 자기장 결 합 특성이 약 -30 dB 이하를 만족하기 위해서는

그림 12. 자기장 결합 특성이 -30 dB 이하를 만족하는 커넥터 핀의 파라미터 추출 순서도 Fig. 12. Flow chart of parameter extraction satisfied the limitation which is -30 dB.

커넥터 핀의 피치는 40 μm 이하가 되어야 한다. 커넥터 핀의 피치를 40 μm보다 짧게 설계할 수 없는 상황일 때 신호 핀 주변에 접지 핀의 개수를 하나 더배치하여 모두 2개의 접지 핀을 배치하면 설계할 수 있는 커넥터 핀의 피치는 170 μm 이하가 되고, 이상태에서 접지 핀의 개수를 하나 더 추가하여 3개의접지 핀을 배치하면 설계할 수 있는 커넥터 핀의 피치는 660 μm 이하가 되므로 커넥터 핀의 피치를 50 μm로 설계할 수 있다. 이와 같은 방법으로 설계자는 5 GHz 이내의 주파수 대역에서 자기장 결합 특성이 약 -30 dB 이하를 만족하는 커넥터 핀의 길이와핀의 피치를 결정할 수 있으며, 신호 핀 주변에 접지 핀을 많이 배치하여 신호 전달 특성을 개선 할 수 있다.

그림 11에 나타낸 커넥터 핀의 배열 구조 중에서 접지 핀이 3개인 경우의 3D 시뮬레이션 결과를 그림 15에 나타내었다. 접지 핀의 변화에 따른 자기장 및 전기장 결합 특성과 3D 시뮬레이션 결과는 앞부분에서 이미 기술하였으므로, 그림 15에는 접지 핀이 있는 3번째 열의 5개 커넥터 핀의 표면 전류를 나타내었다. 실제 커넥터 핀의 반지름 13.5  $\mu$ m에 비하여 핀의 길이는 3 mm로 매우 길기 때문에 핀의 윗부분을 확대하였고, 좌측에 커넥터 핀의 표면 전류의 차이를 색깔로 나타낸 표를 같이 첨부하였다. 커넥터 핀에는 1 V가 인가되었으며, 3번째 열로부터  $40 \mu$ m 피치로 배열되어 있는 2번째 열과 4번째 열에는 모두 신호 핀이 위치하므로 그림 15에서 보는 것과 같이 신호 핀과 인접한 접지 핀의 전류 밀도가 상

그림 13. -30 dB 이하를 만족하는 커넥터 핀의 길이 Fig. 13. The length of the connector pin satisfied the limitation which is -30 dB.

그림 14. -30 dB 이하를 만족하는 커넥터 핀의 피치 Fig. 14. The pitch of the connector pin satisfied the limitation which is -30 dB.

그림 15. 커넥터 핀의 표면 전류 Fig. 15. Surface current of connector pins.

대적으로 높은 것을 확인할 수 있다.

## V. 결 론

본 논문에서는 프로브 커넥터 핀의 누화 특성을 분석하였고, 누화 특성이 -30 dB 이하를 만족하는 핀의 길이 및 피치 파라미터에 대한 설계 기준을 제 시하였다. 격자 구조로 배열된 커넥터 핀의 누화 특 성 분석을 위하여 핀의 인덕턴스와 커패시턴스를 계 산하였고, 시뮬레이션을 이용하여 신뢰성을 검증하 였으며, 접지 핀의 개수가 증가해도 이미 계산된 파 라미터들을 이용하여 새로운 커패시턴스 및 인덕턴 스 성분들을 쉽게 계산할 수 있음을 보였다. 그리고 커넥터 핀의 등가 회로를 바탕으로 자기장 결합과 전기장 결합 특성을 분석하여 각 결합을 구분할 수 있는 기준을 제시하였으며, 이를 통해 일반적으로 커넥터 핀을 사용하는 주파수 대역에서는 자기장 결 합의 영향이 우세하다는 것을 확인하였다. 또한, 커 넥터 핀의 누화 특성을 개선하기 위해서 신호 핀 주 변에 위치한 접지 핀 개수를 증가시키면서 누화 특 성을 향상시키는 알고리즘을 제시하였고, 접지 핀 개 수의 증가가 자기장 결합에 의한 누화를 효과적으로 제거시킨다는 것을 보였다. 이러한 분석 결과를 바 탕으로 주어진 접지 핀의 개수 및 형상 하에서 -30 dB 이하의 누화 특성을 만족하는 MEMS 프로브 커

넥터 핀의 피치 및 길이를 결정하는 영역을 도시하였다. 커넥터 핀의 커플링을 방지함으로써 반도체테스트 환경의 신뢰성 향상에 도움이 될 것으로 기대되며, 이는 프로브 커넥터 시스템의 설계 시 유용하게 사용할 수 있을 것으로 사료된다.

#### 참고문 헌

- [1] 박준서, "EMI/EMC of 3D IC(Integrated Circuit)", 한국전자파학회논문지, 22(1), pp. 42-51, 2011년 1월.

- [2] 김봉환, "멤스 프로브 카드를 위한 깊은 트렌치 안에서 S 모양의 일체형 미세 피치 외팔보 프로 브 형성 공정 개발", 전자공학회 논문지, 48(SD 1), pp. 1-6, 2011년 1월.

- [3] Clayton P. Paul, *Inductance*, A. Wiley Interscience Publication, John Wiley & Sons, pp. 205-211, 2010.

- [4] Clayton P. Paul, Analysis of Multiconductor Transmission Lines, A. Wiley - Interscience Publication, John Wiley & Sons, pp. 64-76, 1994.

- [5] Clayton P. Paul, "Solution of the transmission-line equations for three-conductor lines in homogeneous media", *IEEE*, vol. emc20, no. 1, pp. 216-222, Nov. 1978.

- [6] Clayton P. Paul, Arthur E. Feather, "Computation of the transmission line inductance and capacitance matrices from the generalized capacitance matrix", *IEEE*, vol. emc18, no. 4, pp. 175-183, Nov. 1976.

- [7] Kenneth L. Kaiser, Transmission Lines, Matching, and Crosstalk, CRC Taylor & Francis, pp. 559-562, 2006.

- [8] Howard Johnson, Martin Graham, *High-Speed Sig*nal Propagation, Prentice Hall, pp. 128-130, 2003.

- [9] Michel Mardiguian, Controlling Radiated Emissions by Design, Kluwer Academic Publishers, Boston/Dordrecht/London, pp. 136-155, 2001.

- [10] Clayton P. Paul, "On the superposition of inductive and capacitive coupling in crosstalk-prediction models", *IEEE*, vol. emc24, no. 3, pp. 335-343, Nov. 1982.

#### 배 현 주

2010년 2월: 인제대학교 전자지능 로봇공학과 (공학사) 2010년 3월~현재: 성균관대학교 정 보통신공학부 석사과정 [주 관심분야] EMI/EMC, SI, PI

#### Bo Pu

2009년 7월: Harbin Institute of Technology, China 전자공학과 (공학 사) 2009년 8월~현재: 성균관대학교 정 보통신공학부 박사과정 [주 관심분야] Signal Integrity, EMC in Package, EMC on Chip

#### 김 종 현

2007년 3월: 성균관대학교 정보통신 공학부 학사과정 [주 관심분야] Signal Integrity, Power Integrity

# 이 재 중

2010년 8월: 동국대학교 반도체과 학과(공학사) 2011년 3월~현재: 성균관대학교 정 보통신공학부 석사과정 [주 관심분야] EMC in Package, EMS

#### 이 준 상

2010년 2월: 명지대학교 전자공학 과 (공학사) 2010년 3월~현재: 성균관대학교 정 보통신공학부 석사과정 [주 관심분야] SI/PI in System Level, EMI Reduction in HEV

#### 나 완 수

1884년 2월: 서울대학교 전기공학과 (공학사) 1986년 2월: 서울대학교 전기공학과 (공학석사) 1991년 2월: 서울대학교 전기공학과(공학박사) 1991년~1993년: SSCL Guest colla-

borator

1993년~1995년: 한국전기연구원 선임연구원 1995년~현재: 성균관대학교 정보통신공학부 교수 [주 관심분야] SI, PI, EMI/EMC