Journal of Sensor Science and Technology Vol. 21, No. 1 (2012) pp. 7-12 http://dx.doi.org/10.5369/JSST.2012.21.1.7 pISSN 1225-5475/eISSN 2093-7563

# Dual Sampling-Based CMOS Active Pixel Sensor with a Novel Correlated Double Sampling Circuit

Sung-Hyun Jo, Myunghan Bae, Joontaek Jung, Pyung Choi, and Jang-Kyoo Shin+

#### **Abstract**

In this paper, we propose a 4-transistor active pixel sensor(APS) with a novel correlated double sampling(CDS) circuit for the purpose of extending dynamic range. Dual sampling techniques can overcome low-sensitivity and temporal disparity problems at low illumination. To accomplish this, two images are obtained at the same time using different sensitivities. The novel CDS circuit proposed in this paper contains MOS switches that make it possible for the capacitance of a conventional CDS circuit to function as a charge pump, so that the proposed APS exhibits an extended dynamic range as well as reduced noise. The designed circuit was fabricated by using 0.35  $\mu$ m 2-poly 4-metal standard CMOS technology and its characteristics have been evaluated.

Keywords: Dual Sampling, APS, Noise, Charge Pump

#### 1. INTRODUCTION

Complementary metal oxide semiconductor(CMOS) image sensors(CIS) have a wide range of applications from consumer applications and machine vision applications to scientific research applications[1]. Some challenging issues in CIS are noise and dynamic range(DR), which are defined as the ratio of a pixel's saturation level to its signal threshold, decided based on noise level. Noise and DR are important parameters in determining the performance of CIS. Various approaches have been proposed to reduce noise and extend DR, based on various approaches such as linear-logarithmic CIS, multiple sampling, overflow integration capacitor and dual sampling[2-15]. These approaches, however, suffer from variously noise, nonlinearity, lower sensitivity, reduced operating speed, and lower resolution. Logarithmic sensors may greatly widen the dynamic range in the high illumination region by compressing the image signal, but they suffer from noise problems in the low illumination region. In the case of linear-logarithmic sensors, linear sensors compensate for this problem. Although the problems in low illumination can be compensated for, the nonlinearity problem of logarithmic sensors still exists. Multiple sampling combines several images with different light integration times. Generally, an image that has a long light integration time shows good quality in the dark area of the incident scene but leaves the bright areas saturated. A short lightintegrated image can compensate for this deficiency. Since this technique samples the amount of photo generated electrons just before saturation, not only dynamic range but also signal-to-noise ratio(SNR) is improved. However, this approach requires a high frame rate readout for a wide dynamic range. Many researchers have tried to control the amount of accumulated charge. For this purpose, charges in highly illuminated pixels are partially transferred to a small capacitor via a switch. As this approach requires a capacitor and a switch, its pixel size is larger than standard. Dual- and multi-sampling based on analog or digital techniques has been widely researched for obtaining images with different sensitivities. However, the additional time requirements for the additional charge accumulation induces low sensitivity and time disparity among two or more of the light-integration periods, this induces image distortion. This paper suggests a new approach to dual sampling with a novel CDS circuit to overcome the low sensitivity, temporal disparity, and noise[16]. To accomplish this, two images are obtained at the same time and these obtained images have different sensitivities.

School of Electronics Engineering, Kyungpook National University <sup>+</sup>Corresponding author: jkshin@ee.knu.ac.kr (Received: Nov. 2, 2011, Accepted: Dec. 23, 2011)

Additionally, the proposed CDS circuit contains MOS switches that makes it possible for the capacitance of a conventional CDS circuit to function as a charge pump, which can reduce noise and extend dynamic range[17]. The designed circuit was fabricated by using 0.35  $\mu$ m 2-poly 4-metal(2P4M) standard CMOS technology and tested in order to evaluate the feasibility of the proposed technique.

## 2. CIRCUIT DESIGN

## 2.1 Operational principle

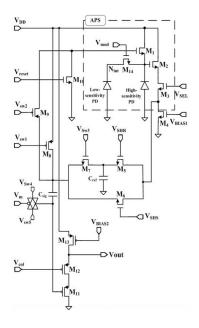

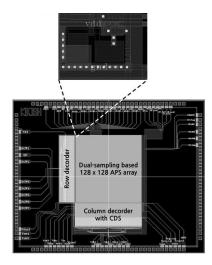

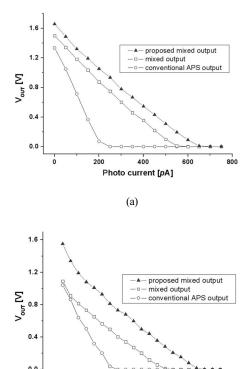

Figure 1 and 2 show a schematic diagram of the proposed 4-transistor APS with a novel CDS circuit and a timing diagram for operation, respectively. Figure 3 shows the layout of the proposed APS array. The proposed CDS circuit has two functions: to increase the reset voltage and to reduce fixed pattern noise(FPN). The sequence of operation runs as follows: First, the charge pump sharing C<sub>sig</sub> of the CDS circuit increases the gate voltage of the transistor M<sub>1</sub> from t<sub>1</sub> to t<sub>3</sub>, as shown in Fig. 2, which results in an increase of the reset voltage of Nint(the charge accumulation node). This increased reset voltage helps to extend the dynamic range of the APS, which is confirmed by the data for the proposed mixed output voltage as shown in Fig. 4. Second, the FPN is reduced by the mechanism of correlated double sampling from t2 to t6 as shown in Fig. 2[18]. The proposed 4-transistor APS sequentially performs resets of the photodiodes(both highand low-sensitivity photodiodes), accumulating signal charge and combining all the signals of both photodiodes. The reset operation is performed by turning on the transistor M<sub>1</sub> using the function of the charge pump. The energy level of the two photodiodes is set at the increased reset voltage, which extends the dynamic range, as shown in Fig. 4. During that period, the transistor M<sub>14</sub> is also turned on to reset both photodiodes.  $M_1$  and  $M_{14}$  are turned off after resetting, when photo-generated charges are simultaneously accumulated in both photodiodes. The charge accumulation rates(or quantum efficiencies) of these two photodiodes are different; therefore, the highand low-sensitivity photodiodes produce long- and shorttime exposed images of a conventional multi-sampling approach. After a certain period of charge accumulation,

transistor M<sub>14</sub> is turned on. During that time, an image combining operation is performed. This indicates an improvement of dynamic range at high illumination exhibiting the mixed output voltage seen in Fig. 4. In a state of low-illumination, both photodiodes cannot be fully charged; therefore, the APS sends the combined signal from both the photodiodes. In a state of relatively high-illumination, however, the high-sensitivity photodiode is fully charged. In that case, the APS shows lower sensitivity characteristics compared with the result obtained in a state of low-illumination. The illumination level for saturation is determined by the low-sensitivity photodiode.

Fig. 1. Proposed APS with a novel noise reduction circuit.

Fig. 2. Timing diagram of the proposed APS.

Fig. 3. Layout of the proposed APS array.

Fig. 4. Variation of the output voltage with photo current and light intensity. (a) Simulation results, (b) experimental results.

(b)

200

Light intensity [lux]

300

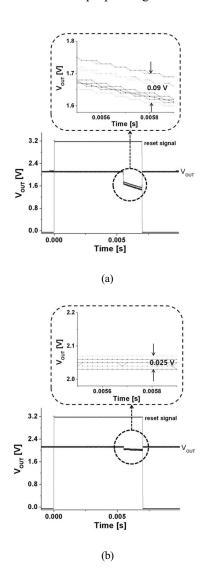

Figure 5 shows the output voltage of the APS. The noise reduction ratio of the proposed CDS circuit is obtained by measuring the variation of the APS output voltage for ten pixels when the same light is incident on the entire array of the proposed image sensor. Figures 5 (a) and (b) show the

variation of the output voltage(0.09 V) without the CDS circuit and the variation of the output voltage(0.025 V) with the CDS circuit, respectively. These result indicates that the noise is reduced by approximately 70 % with the CDS circuit.

#### 3. DISCUSSION

Compared to previously reported APS and CDS circuits, the proposed approach has several advantages. The proposed sensor performs the combination of two images by turning on the internal transistor M<sub>14</sub>; therefore, external equipment and digital signal processing are not required. All that is needed is a simple pulse signal.

Fig. 5. Output voltage of the APS. (a) Without the CDS circuit, (b) with the CDS circuit.

The two photodiodes in the proposed APS operate simultaneously unlike in other conventional multiple sampling techniques; therefore, no extra time is needed for additional charge accumulation. DR extension is adjustable by controlling parasitic capacitance and the sensitivity of both photodiodes.

In addition, charge accumulation times for both photodiodes are the same, as such, they are free from the temporal disparity problem. An expected drawback of the proposed APS is the increase of pixel size, which could be minimized by applying a stacked photodiode structure[19]. The output voltage of the APS can be decreased by using a reduced supply voltage resulting from the scaling down of the semiconductor process. The proposed CDS circuit can not only extend the dynamic range while reducing noise but also mitigates a decrease in output voltage. Due to these advantages, this technique can be applied to CMOS image sensors with a global shutter method that requires a few  $\mu$ s for the charge pump to function before noise reduction.

# 4. CONCLUSIONS

A dual sampling 4-transistor APS with a novel CDS circuit was designed and fabricated using 2-poly 4-metal standard CMOS technology. Compared to previously reported APS with CDS circuits, the proposed circuit has several advantages: no-external equipment or signal processing for combining images is required, no-additional time-requirement for additional charge accumulation is needed, it has adjustable DR extension and no temporal disparity. Experimental results agree well with simulation results. From the simulation and experimental results, we can say the proposed 4-transistor APS with a novel CDS circuit can not only extend dynamic range but also reduce noise. As such this technique can be applied to the CMOS image sensors with a global shutter method.

# **ACKNOWLEDGMENT**

This work was supported by the Basic Science Research Program through the National Research Foundation of Korea(NRF) grant funded by the Korea government (MEST) (No. 2011-0001077), the second phase of the Brain Korea21 program in 2011 and the Integrated Circuit Design Education Center(IDEC) in Korea.

#### REFERENCES

- [1] M. Bigas, E. Cabruja, J. Forest, and J. Salvi, "Review of CMOS image sensor", *Microelectronics J.*, vol. 37, p. 433, 2006.

- [2]Storm, G. G., Hurwitz, J. E. D., Renshaw, D., Findlater, K. M., Henderson, R. K., and Rurcell, M. D., "Combined linear-logarithmic CMOS image sensor", *IEEE ISSCC Dig. Tech.*, pp. 112-113, 2004.

- [3] Sugawa, S, Akanane, N., Adachi, S., Mori, K., Ishiuchi, T., and Mizobuchi, K., "A 100dB dynamic range CMOS image sensor using a lateral overflow integration capacitor", *IEEE ISSCC Dig. Tech.*, pp. 352-603, 2005.

- [4] Yamada, T., Kasuga, S., Murata, T., and Kato, Y., "A 140dB-dynamic-range MOS image sensor with in-pixel multiple-exposure synthesis", *IEEE ISSCC Dig.* Tech., pp. 50-594, 2008.

- [5] Gamal, A., "Trends in CMOS image sensor technology and design", *IEDM Technical Digest*, pp. 805-808, 2002.

- [6] Egawa, Y., Tanaka, N., Kawai, N., Seki, H., Nakao, A, Honda, H. Lida, Y., and Monoi, M., "A white-RGB CFA-patterned CMOS image sensor with wide dynamic range", *IEEE ISSCC Dig.* Tech., pp. 52-595, 2008.

- [7] Sumi, H., "Low-noise imaging system with CMOS sensor for high-quality imaging", *IEDM Technical Digest*, pp. 1-4, 2006.

- [8] Han, H., Park, H., Altice, P., Choi, W., Lim, Y., Lee, S. Kang, S., Kim, J., Yoon, K., and Hynecek, J., "Evaluation of a small negative transfer gate bias on the performance of 4T CMOS image sensor pixels", *International Image Sensor Workshop*, 2007.

- [9] Lim, Y., Lee, K., Hong, H., Kim, J., Sa, S., Lee, J. Kim, D., and J. Hynecek, "Stratified photodiode: A new concept for small size-high performance CMOS image sensor pixels", *International Image Sensor Workshop*, pp. 311-314, 2007.

- [10 Wang, C. C. and Soldini C., "Technology and device scaling considerations for CMOS image sensors", *IEDM Technical Digest*, pp. 51-54, 2001.

- [11] Wong, H. -S., "Technical and device scaling

- considerations for CMOS image sensors", *IEEE Trans. on Electron Devices*, vol. 43, no. 12, pp. 2131-2142, 1996.

- [12] Lee, S. and Yang, K., "High-dynamic-range sensor cell based on self-adaptive photosensing operation", *IEEE Trans. on Electron Devices*, vol. 53, no. 7, pp. 1733-1735, 2006.

- [13] Mori, M., Katsuno, M., Kasuga, S. Murata, T., and Yamaguchi, T., "A 1/4in 2M pixel CMOS image sensor with 1.75 transistor/pixel", *ISSCC Dig. Tech.*, pp. 110-111, 2004.

- [14] Kong, J.-S., Hyun, H.-Y., Seo, S.-H., and Shin, J.-K., "A retina-motivted CMOS vision chip based on the column parallel architechture and switch-selective resistive network", *ETRI J.*, vol. 30, no. 6, pp. 269-275, 2008.

- [15] Seo, M.-W., Seo, S.-H., Lee S., Jo, S.-H., Choi, K.-H., Kong, J.-S., and Shin, J.-K., "Dynamic range improvement of CMOS active pixel sensor by controlling the energy barrier between photo-diode

- and expansion-diode", *Extended Abstracts of SSDM*, pp. 512-513, 2009.

- [16] J. -S. Kong, S. -H. Jo, K. -H. Choi, S. -H. Seo, P. Choi, and J. -K. Shin, "Dynamic range extension of an active pixel sensor combining output signals from photodiods with different sensitivities", *SPIE*, 7536-29, 2010.

- [17] S.-H. Jo, J.-S Kong, S.-Y. Lee, K.-H. Choi, and J.-K. Shin, "Readout circuit of CMOS image sensor for dynamic range expansion and noise reduction function", proceeding of the Korean Sensor society.

- [18] Y. Degerli, F. Lavernhe, P. Magnan, and P.J. Farre., "Column readout circuit with global charge amplifier for CMOS APS imagers", *Electronics Letters 17th August*, vol. 36, no.17, 2000.

- [19] D. L. Gilblom, S. K. Yoo, and P. Ventura, "Operation and performance of a color image sensor with layered hotodiodes", *Proceeding SPIE*, vol. 5210, pp. 105-115, 2004.

Sung-Hyun Jo received BE and ME degrees in the School of Electrical Engineering and Computer Science from Kyungpook National University, Daegu, Korea in 2008 and 2011, respectively. He is now working for his PhD degree at Kyungpook National University. His current fields of interest are in CMOS image sensors and their applications.

Joontaek Jung received a BE degree in the School of Electrical Engineering and Computer Sicence from Kyungpook National University, Daegu, Korea in 2010. He is now working for his ME degree at Kyungpook National University. His current fields of interest are in CMOS image sensord and their applications.

Myunghan Bae received a BE degree in the School of Electronic Engineering and Computer Science from Kyungpook National University, Daegu, Korea in 2010. He is now working for his ME degree at Kyungpook National University. His current fields of interest are in CMOS image sensor chips and their applications.

Pyung Choi received his BS form Yonsei University, Seoul, Rep. of Korea in 1980, and his MS from Ohio State University, Columbus, Ohio in 1985, and a PhD from the Georgia Institute of Technology, Atlanta, Georgia in 1990. He is currently a full professor in the Department of Electrical Engineering at Kyungpook National University, Daegu, Korea. His Major interests are analog VLSIs, IC modeling, and CAD. Dr. Choi is a member of the IEEK and IEICE.

Jang-Kyoo Shin received his BE degree in electronic engineering from Seoul National University, Seoul, Korea in 1978 and his MS degree in electrical engineering from the Korea Advanced Institute of Science and Technology, Korea in 1980. He received a PhD degree in electrical engineering from Colorado State University, Fort Collins, USA in 1991. He is now a Professor in the School of Electronics Engineering at Kyungpook National University, Daegu, Korea. His current fields of interest are semiconductor sensors and intelligent sensor systems.