# A Subthreshold CMOS RF Front-End Design for Low-Power Band-III T-DMB/DAB Receivers

Seongdo Kim, Janghong Choi, Joohyun Lee, Bontae Koo, Cheonsoo Kim, Nakwoong Eum, Hyunkyu Yu, and Heebum Jung

This letter presents a CMOS RF front-end operating in a subthreshold region for low-power Band-III mobile TV applications. The performance and feasibility of the RF front-end are verified by integrating with a low-IF RF tuner fabricated in a 0.13-µm CMOS technology. The RF front-end achieves the measured noise figure of 4.4 dB and a wide gain control range of 68.7 dB with a maximum gain of 54.7 dB. The power consumption of the RF front-end is 13.8 mW from a 1.2 V supply.

Keywords: CMOS, subthreshold, Band-III, T-DMB, DAB, mobile TV, low-IF, tuner:

#### I. Introduction

The minimization of power consumption is of primary concern for battery-operated handheld devices. Subthreshold operation is one of the low-power design approaches available. Although the devices in a subthreshold region have drawbacks such as degraded noise and linearity performance due to lower bias current [1], advances in device technology allow subthreshold region operation to be utilized in designing for low-power very-high-frequency (VHF) applications.

In this letter, we present a subthreshold CMOS RF front-end (RFE) for low-power mobile TV receivers. The RF performance of the proposed subthreshold RFE was confirmed by integrating it with a low-IF terrestrial digital multimedia broadcasting (T-DMB) tuner and validating the tuner output.

T-DMB requires BER of  $10^{-3}$  for a Band-III Gaussian channel for RF signal level from -95 dBm to -10 dBm. Therefore, the RFE should have at least 6 dB of noise figure (NF) to meet the requirements. The proposed RFE achieves the measured NF of 4.4 dB and a wide gain control range of 68.7 dB with the maximum gain of 54.7 dB. The power consumption of the RFE is 13.8 mW from a 1.2 V supply.

### II. Proposed Subthreshold RF Front-End Design

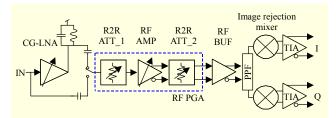

Figure 1 shows the simplified block diagram of the proposed subthreshold RFE. In this design, all RF circuits with large signal bandwidth are designed to operate in a subthreshold region or designed in a passive circuit topology for lowering the power consumption. Large transconductance for a lower current can be achieved by using a larger device in the subthreshold region [2]. The power consumption in subthreshold operation can reduce about 6.4 times less than that in saturation region [3].

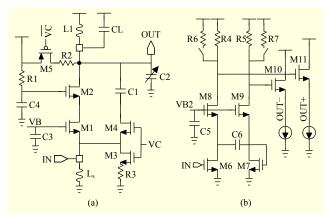

Figure 2(a) shows the gain-switched common-gate low noise amplifier (CG-LNA), which operates in the subthreshold region. The gain-switched amplifiers relax the required linearity of the following stages, resulting in power saving. The

Fig. 1. Simplified block diagram of proposed subthreshold RFE.

Manuscript received Feb. 11, 2011; revised Apr. 21, 2011; accepted May 6, 2011.

Seongdo Kim (phone: +82 42 860 5540, email: sdkim@etri.re.kr), Janghong Choi (email: cjh313@etri.re.kr), Joohyun Lee (email: juehyun@etri.re.kr), Bontae Koo (email: koobt@etri.re.kr), Cheonsoo Kim (email: cskim@etri.re.kr), Nakwoong Eum (email: nweum@etri.re.kr), Hyunkyu Yu (email: hkyu@etri.re.kr) and Heebum Jung (email: hbjung@etri.re.kr) are with the Convergence Components & Materials Research Laboratory, ETRI, Daejeon, Rep. of Korea.

http://dx.doi.org/10.4218/etrij.11.0211.0055

Fig. 2. (a) Gain-switched CG-LNA and (b) gain-switched RF amplifier.

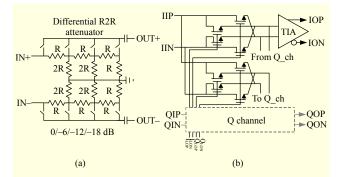

Fig. 3. (a) Differential R2R attenuator and (b) double quadrature image rejection passive mixer.

transistor M1 has a very large width of 160  $\mu$ m  $\times$  16 for large  $g_m$  with small currents, and the impact of large  $C_{gs}$  can be removed by configuring a parallel resonant circuit with the inductor L<sub>s</sub> at operating frequency. The gate bias of the LNA is set through bandgap reference (BGR) circuit and adjusted by tuning circuits. Since the drain current in the subthreshold region operation is exponentially proportional to the gate and drain voltage, the DC bias point of the device is very important. The accurate bias circuit such as BGR is required to guarantee the stable operation. The RF signals which pass through M1 and M2 in the gain-switched CG-LNA are amplified in high gain mode. The transistors M3, M4, and M5 are turned on, and M1 is turned off in low-gain mode, transferring the received RF signal to the output terminal. The output matching frequency can be tuned by the switched capacitor bank, C2. The CG-LNA achieves 1.7-dB NF and -10-dBm IIP3 at the maximum gain of 24.4 dB. The bias current is 6.6 mA.

Figure 2(b) shows the gain-switched differential RF amplifier. It operates as a part of the RF automatic gain control (AGC). The transistors M6 and M7 have both a W/L of 160 µm/0.13 µm and achieve a transconductance of 17 mS at 814 µA. The RF amplifier achieves 7.6-dB NF and -5-dBm

IIP3 with a maximum gain of 19.1 dB.

Figure 3(a) shows the differential R2R attenuator. Since the parasitics of the attenuator increase with increasing the gain control range, two R2R attenuators are designed so that the parasitics are minimized. The first and second R2R attenuators have the attenuation range of 12 dB and 18 dB, respectively. Figure 3(b) shows the image rejection mixer. The image rejection mixer is designed in a double quadrature passive circuit topology to achieve high linearity and further power saving [4]. The mixer is carefully designed to have symmetrical geometry to minimize gain and phase mismatches among the quadrature signal paths. The transimpedance amplifiers have a fixed gain of 20 dB.

#### III. Low-Power T-DMB Tuner Architecture

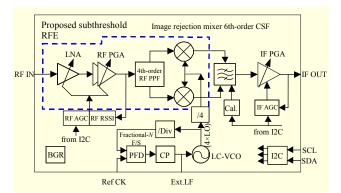

Figure 4 shows the RF tuner based on the proposed subthreshold RFE, which has a 2.048-MHz low-IF topology. The proposed RFE consists of a gain-switched CG-LNA, two R2R attenuators, a gain-switched RF amplifier, an RF buffer, an image rejection mixer, and an RF AGC with received signal strength indicator (RSSI). The 6th-order Chebyshev type-I complex bandpass filter is used to select the wanted channel and reject image signal [5]. The filter has a gain control range of 12 dB and an upper cutoff frequency of 2.816 MHz. IF programmable gain amplifier (PGA) operates as a part of the IF AGC. It has a wide gain control range of 61 dB with 1-dB control step and keeps the input level of the ADC constant to improve the SNR. For precise quadrature local oscillators (LOs) and fine frequency resolution, 4th-order sigma-delta fractional-N frequency synthesizer (FS) is adopted [6], which employees 4/16/31 dividers and tuning circuits. The on-chip LC voltage-controlled oscillator (VCO) is designed to operate over the range from 620 MHz to 1,144 MHz. Then, the divider is used to obtain the mixer LO frequency. This scheme minimizes chip area by reducing the inductance. The RF tuner is configured via an I2C interface.

Fig. 4. Architecture of RF tuner with proposed subthreshold RFE.

# **IV. Experimental Results**

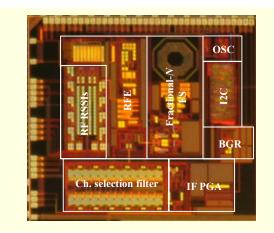

To verify RF performance and feasibility of the proposed subthreshold RFE, a T-DMB RF tuner, including the RFE, is fabricated in a 0.13- $\mu$ m CMOS technology as shown in Fig. 9. The proposed RFE with RF RSSI occupies 1.2 mm × 1.6 mm. In addition to the proposed RFE measurements, the performance for the entire tuner is also evaluated and summarized in Table 1.

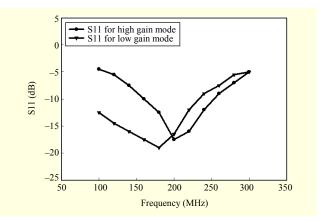

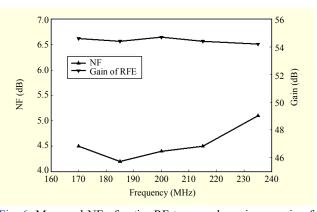

Figure 5 shows that the measured S11 of the entire RF tuner is less than -10 dB over the frequency range from 170 MHz to 236 MHz, regardless of the LNA operation mode. Figure 6 shows the measured NF for the entire RF tuner and gain for the proposed RFE as a function of frequency. Measurements show

Table 1. Measurement results summary and entire tuner performance comparison.

| Reference              | [7]                           | [8]            | [9]           | [10]          | This<br>work    |

|------------------------|-------------------------------|----------------|---------------|---------------|-----------------|

| Technology             | 0.18-μm<br>CMOS               | 65-nm<br>CMOS  | 65-nm<br>CMOS | 65-nm<br>CMOS | 0.13-nm<br>CMOS |

| Frequency              | Band-III (174 MHz to 236 MHz) |                |               |               |                 |

| NF (dB)                | 1.4**                         | 3.0            | 3.0           | 2.8           | 4.4             |

| G <sub>MAX</sub> (dB)  | (37)                          | (25*)          | (30)<br>95.5  | (-)<br>68.0   | (54.7)<br>115.3 |

| G <sub>CR</sub> (dB)   | (33)                          | (28)<br>100    | (30)<br>95.5  | (-)<br>78.0   | (68.7)<br>129   |

| IIP3 (dBm)             | (-)<br>-8.0                   | (-)<br>-4.0(3) | (-)<br>-      | (-)<br>-21*** | (-)<br>+10      |

| P <sub>1dB</sub> (dBm) | (-)<br>-                      | (-)<br>-       | (-)<br>-      | (-)<br>-      | (-)<br>+3.0     |

| P <sub>D</sub> (mW)    | (27)                          | (-)<br>102     | (-)<br>82.8   | (-)<br>35.0   | (13.8)<br>38.4  |

| $V_{DD}(V)$            | 1.8                           | 1.2/2.5        | 1.2/1.8       | 1.2/1.8       | 1.2             |

Note. ( ): RFE only, gain control range ( $G_{CR}$ ), and power dissipation ( $P_D$ ), simulated or estimated value, \*\*: DSB NF, and \*\*\*: maximum gain mode.

Fig. 5. Measured S11 of entire RF tuner as function of frequency.

a minimum NF of 4.4 dB and the maximum RFE gain of 54.7 dB. The RFE and digital signal processors are integrated on the same silicon substrate. Since the NF is measured on condition that the RFE and digital signal processor are both turned on, the measured NF is much higher than that of the simulated NF due to the noise induced from the digital domains. Since the receiver noise performance is mostly

Fig. 6. Measured NF of entire RF tuner and maximum gain of proposed RFE as function of frequency.

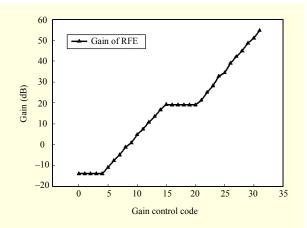

Fig. 7. Measured gain control range of proposed RFE.

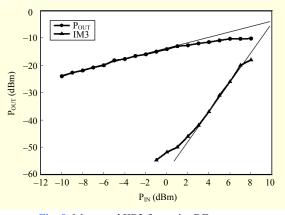

Fig. 8. Measured IIP3 for entire RF tuner.

Fig. 9. Die photograph.

determined by the RFE, the measured tuner NF can be considered as the noise performance for the proposed subthreshold RFE. Figure 7 shows the measured gain control range of the proposed RFE, which has a wide range of 68.7 dB. The entire tuner achieves a gain control range of 129.3 dB. Figure 8 shows the measured IIP3 of +10 dBm and  $P_{1dB}$  of +3 dBm of the entire RF tuner at 200 MHz under minimum gain operation. The receiver's overall power consumption is about 38.4 mW while the proposed subthreshold RFE consumes 13.8 mW from a 1.2 V supply. The implemented RF tuner, which is based on the proposed subthreshold RFE, also has been validated with a T-DMB baseband demodulator. As shown in Table 1, the proposed RFE and the tuner are superior in terms of power dissipation to previously published works, except for the tuner in [10] which consumes less power than ours. The die photograph is shown in Fig. 9.

#### V. Conclusion

In this letter, we presented a low-power RFE operating in a subtreshold region for VHF applications. The RF performance is evaluated through an RF tuner with the proposed RFE fabricated with 0.13-µm CMOS technology. The proposed subtreshold RFE achieves a minimum NF of 4.4 dB with a good impedance matching over Band-III range and a high gain control range of 68.7 dB with a maximum gain of 54.7 dB, while consuming only 13.8 mW from a 1.2 V supply. Measurement results confirm that the subtreshold operation technique can be utilized in designing RF circuits for low-power VHF applications.

## References

K. To et al., "High Frequency Noise Characteristics of RF MOSFETs in Subthreshold Region," *IEEE RFIC*, June 2003, pp. 163-166.

- [2] H. Lee et al., "A 500µW 2.4GHz CMOS Subthreshold Mixer for Ultra Low Power Applications," *IEEE RFIC*, June 2007, pp. 325-328.

- [3] B.G. Perumana et al., "A Low-Power Fully Monolithic Subthreshold CMOS Receiver With Integrated LO Generation for 2.4 GHz Wireless PAN Applications," *IEEE JSSC*, Oct. 2008, pp. 2229-2238.

- [4] M. Notten et al., "A Low-IF CMOS Double Quadrature Mixer Exhibiting 58 dB of Image Rejection for Silicon TV Tuners," *IEEE RFIC*, June 2005, pp. 171-174.

- [5] J. Crols et al., "Low-IF Topologies for High-Performance Analog Front Ends of Fully Integrated Receivers," *IEEE Trans. Circuits Syst. II*, vol. 45, Mar. 1998, pp. 269-282.

- [6] B. De Muer et al., "A CMOS Monolithic ΔΣ-Controlled Fractional-N Frequency Synthesizer for DCS-1800," *IEEE ISSC*, vol. 37, no. 7, July 2002, pp. 835-844.

- [7] I. Nam et al., "A Wideband CMOS RF Front-End Using AC-Coupled Current Mirrored Technique for Multiband Multistandard Mobile TV Tuners," *IEEE Micro. Wireless Comp. Lett*, Oct. 2007, pp. 739-741.

- [8] I. Vassiliou et al., "A 65 nm CMOS Multistandard, Multiband TV Tuner for Mobile and Multimedia Applications," *IEEE JSSC*, vol. 43, no. 7, July 2008, pp. 1522-1533.

- [9] J. Chang et al., "A Multistandard Multiband Mobile TV RF SoC in 65nm CMOS," *IEEE ISSCC*, Feb. 2010, pp. 462-463.

- [10] M. Jeong et al., "A 65nm CMOS Low-Power Small-Size Multistandard, Multiband Mobile Broadcasting Receiver SoC," *IEEE ISSCC*, Feb. 2010, pp. 460-461.