論 文 16-3-11

# 정류용 브릿지 다이오드가 없는 고효율 하프 브릿지 AC-DC 컨버터

崔祐榮<sup>†</sup>,柳主勝<sup>\*</sup>,崔堤然<sup>\*\*</sup>

A Bridgeless Half-Bridge AC-DC Converter with High-Efficiency

Woo-Young Choi, Ju-Seung Yoo, Jae-Yeon Choi

요 약

본 논문에서는 정류용 브릿지 다이오드가 없는 고효율 하프 브릿지 AC-DC 컨버터를 제안한다. 제안하는 컨버터는 비대칭 펄스 폭 변조 방식의 하프 브릿지 DC-DC 컨버터와 정류용 브릿지 다이오드가 없는 역률 개선 회로가 통합된 회로 구조를 지닌다. 제안하는 컨버터는 정류용 브릿지 다이오드를 사용하지 않고 교류 입력 전압으로부터 절연된 직류 출력 전압을 공급한다. 간단한 회로 구조와 함께 도통 손실을 줄일 수 있다. 또한 스위칭 소자들의 영전압 스위칭을 통하여 스위칭 손실을 줄일 수 있다. 두 개의 직렬 연결된 트랜스포머를 구비함으로서 프로파일을 낮추고 전력밀도를 높일 수 있다. 250~W~(48~V~)5.2~A~) 회로 설계 및 실험을 통하여 제안된 컨버터의 성능을  $90~V_{rms}$  교류 입력 전압에 대하여 입증하였다.

## **ABSTRACT**

This paper proposes a bridgeless half-bridge AC-DC converter with high-efficiency. The proposed converter integrates the bridgeless power factor correction (PFC) circuit with the asymmetrical pulse-width modulated (APWM) half-bridge DC-DC converter. It provides the isolated DC output voltage from the AC line voltage without using any full-bridge diode rectifier. Conduction losses are lowered with a simple circuit structure. Switching losses are also reduced by achieving zero-voltage switching (ZVS) of the power switches. By using series-connected two transformers, the proposed converter provides a low-profile and high power density for AC-DC converters. The performance of the proposed converter is verified from a 250 W (48 V / 5.2 A) experimental prototype circuit at 90  $V_{rms}$  line voltage.

**Key Words**: Power factor correction (PFC), Half-bridge converter, Zero-voltage switching (ZVS), Bridgeless, Full-bridge diode rectifier

## 1. 서 론

최근 전기, 전자, 통신기기의 소형화와 함께 고효율 전력 공급을 위한 스위칭 방식 전원 장치 (Switching

물 된 식· g 터는

<sup>†</sup>교신저자 : 정회원, 전북대 전자공학부 전임강사 '학생회원, 전북대 전자공학부 재학

Totale, Can Chort Ma

E-mail: wychoi@jbnu.ac.kr

접수일자: 2011. 3. 7 심사완료: 2011. 4.12 1차 심사 : 2011. 3. 28

Mode Power Supply: SMPS)의 고효율 설계 기술이 활발히 연구되고 있다. 교류 입력 전압으로부터 절연된 직류 출력 전압을 공급하는 SMPS용 AC-DC 컨버터는 입력 측 정류용 브릿지 다이오드 (Full-bridge diode rectifier)와 큰 필터 콘덴서를 이용한다. 이는 입력 전압의 왜곡 및 전도성 전자파 장애를 일으킨다. 이에 대한 대책으로 IEC등 국제기구에서는 IEC 61000-3-2 등의 규격을 제정하여 고조파 전류를 규제하고 있다<sup>[1]</sup>.

이러한 문제를 해결하기 위하여 AC-DC 컨버터는 역률 개선 (Power Factor Correction: PFC) 기능이 요 구된다. 역률 개선 방식은 크게 2단 (Two-stage) 방식 과 단일단 (Single-stage) 방식으로 나눌 수 있다. 단 일단 역률 개선 방식은 일반적으로 역률 개선 회로와 DC-DC 컨버터의 스위치와 제어기를 공유한다. 따라 서 2단 방식에 비하여 회로 제작 비용이 절감되고. 전 력 변환 효율이 높은 특징을 지닌다<sup>[2]</sup>. 단일단 역률 개 선 방식의 AC-DC 컨버터는 일반적으로 200 W급 미 만의 전원 장치에 주로 사용된다. 하지만 출력 부하가 증가되고. 스위칭 주파수가 높아짐에 따라 스위칭 손 실 (Switching Loss)이 증가되어 전력 변환 효율이 감 소된다. 따라서 스위칭 손실을 줄이기 위한 능동 스위 칭 소자들의 소프트 스위칭 (Soft-switching)이 가능한 단일단 역률 개선용 AC-DC 컨버터가 연구되어져 왔 다<sup>[3][4][10][11]</sup>. 소프트 스위칭 방식의 단일단 역률 개선용 AC-DC 컨버터는 대부분이 스위칭 손실을 줄임으로써 전력 변환 효율을 높인다. 하지만 교류 입력 전압이 낮아지고 출력 부하가 증가됨에 따라 교류 입력 측 정 류용 브릿지 다이오드는 높은 도통 손실 (Conduction Loss)을 유발한다<sup>[5]</sup>. 이에 따라 전력 변환 효율이 감소 하게 되며, 스위칭 소자들의 발열 문제가 유발된다.

본 논문에서는 정류용 브릿지 다이오드가 없는 새로 운 고효율 AC-DC 컨버터를 제안한다. 제안하는 컨버 터는 비대칭 펄스 폭 변조 (APWM: Asymmetrical Pulse-Width Modulation) 방식의 하프 브릿지 DC-DC 컨버터와 정류용 브릿지 다이오드가 없는 역률 개선 회로<sup>[6]</sup>가 통합된 회로 구조를 지닌다. 제안하는 컨버터 는 정류용 브릿지 다이오드를 사용하지 않고, 교류 입 력 전압으로부터 절연된 직류 출력 전압을 공급함으로 서, 간단한 회로 구조와 함께 도통 손실을 줄일 수 있 다. 스위칭 소자들의 영전압 스위칭 (Zero-Voltage Switching: ZVS)을 통하여 스위칭 손실을 줄일 수 있 다. 또한 컨버터의 높이를 낮추고, 전력밀도를 높이기 위하여 두 개의 직렬 연결된 트랜스포머를 이용하다. 하나의 자기 소자를 전체 전력의 절반을 다루는 자기 소자 두 개로 대처함으로써, 전체 트랜스포머의 부피 를 줄이며, 높이를 낮출 수 있다<sup>[7][8]</sup>. 또한, 주 트랜스 포머를 두 개로 나누면서 출력 인덕터의 역할까지 겸 함으로써, 하나가 출력 측으로 직접 전력을 전달하는 동안, 다른 하나는 자속 (Flux)의 형태로 에너지를 저 장함으로써 전체 자기 소자의 부피를 줄일 수 있도록 한다<sup>[9][12]</sup>. 250 W (48 V / 5.2 A) 회로 설계 및 실험을 통하여 제안된 컨버터의 성능을 90 V<sub>rms</sub> 교류 입력 전 압에 대하여 입증하도록 한다.

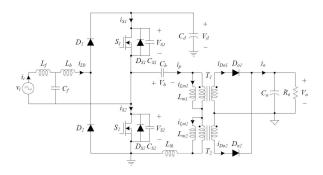

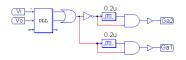

그림 1 제안하는 브릿지 정류다이오드가 없는 하프브릿지 AC-DC 컨버터

Fig. 1 Circuit diagram of the proposed bridgeless half-bridge AC-DC converter

## 2. 본 론

## 2.1 회로 구조

그림 1은 제안하는 컨버터의 회로 다이어그램을 나 타낸다. PFC 회로는  $L_b$ ,  $D_1$ ,  $D_2$ ,  $S_1$ ,  $S_2$ ,  $C_d$ 를 포함한 다.  $S_1$ 과  $S_2$ 는 MOSFET으로서, 출력 커패시터 ( $C_{SI}$ ,  $C_{S2}$ )과 Body 다이오드 ( $D_{S1}$ ,  $D_{S2}$ )를 포함한다. APWM 하프 브릿지 컨버터는  $C_d$ ,  $S_l$ ,  $S_2$ ,  $C_b$ ,  $T_l$ ,  $T_2$ ,  $D_{ol}$ ,  $D_{o2}$ ,  $C_0$ 를 포함한다.  $S_1$ ,  $S_2$ ,  $C_d$ 를 공유함으로서, 제안된 컨 버터에서는 정류용 브릿지 다이오드가 사용되지 않는 다. 인덕터  $L_b$ 는 불연속 모드 (DCM: Discontinuous Conduction Mode)로 동작한다. 따라서 스위치  $S_1$ 과  $S_2$ 의 APWM 동작을 통하여 출력 전압의 제어와 함께 PFC 기능을 수행하게 된다. 트랜스포머  $T_{i}$ 과  $T_{i}$ 는 각 각 자화 인덕턴스  $L_{ml}$ 과  $L_{m2}$ 를 지닌다. 각 트랜스포머 의 턴비 (Turns Ratio)는 1 : N<sub>2</sub>과 1 : N<sub>2</sub>이며, 누설 인덕턴스는 하나의 인덕터  $L_{lk}$ 로 나타낸다. L와 C는 교류 입력 전압에 대한 라인 필터이다. 라인 필터는 부스트 인덕터 Lb의 전류 리플 성분과 EMI (Electro-Magnetic Interfere: EMI)를 줄인다.

#### 2.2 회로 해석

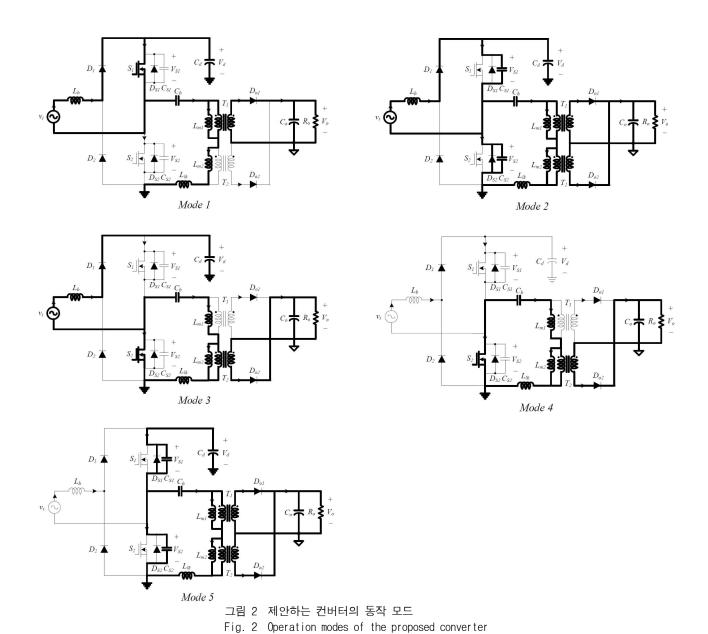

제안하는 컨버터는 교류 입력 전압 V의 극성에 따라 대칭적으로 동작한다. 교류 전압 V가 양의 주기 (Positive half-line cycle)일 때, 스위치  $S_I$ 이 제어된다. 스위치  $S_I$ 의 듀티비 (Duty Ratio)를 D라고 정의할 때, 스위치  $S_I$ 과  $S_2$ 의 도통 시간은 한 스위칭 주기  $T_S$ 에 대하여 각각  $DT_S$ 와  $(I-D)T_S$ 로 표현된다. 그림 2는 교류 전압  $V_I$ 가 양일 때,  $T_S$  동안의 제안된 컨버터의 동작 모드를 나타낸다. 제안하는 컨버터의 대칭적 동작으로 인하여 교류 입력 전압이 양의 주기인 경우에 대

하여 동작 원리를 제시한다.

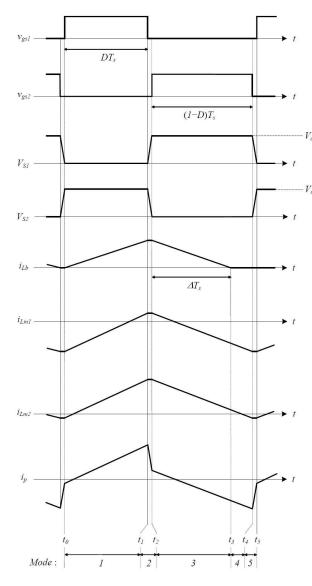

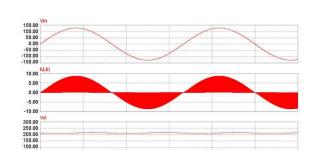

그림 3e  $T_s$  동안 제안된 컨버터의 동작 파형을 나 타낸다. 각 스위치  $S_{1}$ 과  $S_{2}$ 는  $T_{3}$  동안 비대칭 펄스 폭 변조 방식으로 동작한다. 각 스위치의 도통 시간 사이 에 일정 소거 시간 (Dead-time:  $t_d = t_1 - t_0 = t_5 - t_4$ ) 을 지님으로써, 각 스위치 양단의 출력 커패시터  $C_{SI}$ 과  $C_{S2}$ 의 충·방전을 통한 각 스위치의 영전압 스위칭 (ZVS)을 이룰 수 있다. 각 스위치의 Dead-time  $t_d$ 는 한 스위칭 주기에 비하여 매우 짧으므로,  $t_2$  -  $t_o$   $\cong$  $DT_s$ ,  $t_5 - t_2 \simeq (1-D)T_s$ 를 가정한다.  $T_s$  동안 제안된

컨버터는 다음과 같이 5가지 동작 모드를 지닌다.

$Mode\ 1\ [t_o,\ t_l]$ : 스위치  $S_l$ 의 게이팅 신호  $v_{gsl}$ 이 인가되면서,  $S_I$ 이 켜진다. 입력 전류 i는  $L_b$ ,  $D_I$ ,  $S_I$ 을 통하여 흐르게 된다. 인덕터 전류  $i_{Lb}$ 는 선형적으로 증 가하며, 입력 전압으로부터 에너지를 저장한다.  $T_1$ 은 트랜스포머로 동작하며, 일차 측의 전력을 이차 측으 로 전달한다.  $(V_d - V_b - V_o/N_I)$ 의 전압이  $L_{m2}$ 와  $L_{lk}$ 에 인가되면서,  $T_2$ 의 자화인덕턴스  $L_{m2}$ 와 누설인덕턴 스  $L_{lk}$ 는 에너지를 저장한다. 따라서 일차 측 전류  $i_{p}$ 는 다음과 같이 표현된다.

그림 3 제안하는 컨버터의 동작 파형

Fig. 3 Operation waveforms of the proposed converter

$$i_p(t) = i_p(t_o) + \frac{V_d - V_b - V_o/N_1}{L_{m2} + L_{lk}} (t - t_o)$$

(1)

$Mode\ 2\ [t_i,\ t_o]:\ S_I$ 이 소거되면서 일차 측 전류  $i_p$ 는 스위치  $S_I$ 의  $C_{SI}$ 을 충전시키며, 스위치  $S_2$ 의  $C_{SS}$ 를 방전시킨다. 이에 따라 스위치  $S_I$ 의 양단 전압  $V_{SI}$ 은 DC-link 전압  $V_d$ 로 증가하고, 스위치  $S_2$ 의 양단 전압  $V_{SS}$ 는 영으로 감소하며, 각 트랜스포머의 이차 측 양단의 전압이 바뀌기 시작한다.

$Mode\ 3\ [t_2,\ t_3]$ : 스위치  $S_2$ 의 양단 전압  $V_{S2}$ 가 영전 압이 되고, 스위치  $S_2$ 의 게이팅 신호  $V_{gS2}$ 가 인가되면

서,  $S_2$ 가 켜진다. 이때  $S_2$ 의 영전압 스위칭(ZVS)이 이루어진다. 입력 전류 i는  $L_b$ ,  $D_1$ ,  $C_d$ ,  $S_2$ ,  $D_{S2}$ 를 통하여흐르게 된다. 인덕터 전류  $i_{Lb}$ 는 선형적으로 감소하며, 인덕터에 저장된 에너지는 DC-link 커패시터  $C_d$ 로 전달된다.  $T_2$ 는 트랜스포머로 동작하며, 일차 측의 전력을 이차 측으로 전달한다.  $(V_o/N_2-V_b)$ 의 전압이  $L_{ml}$ 과  $L_{lk}$ 에 인가되면서,  $T_i$ 의 자화인덕턴스  $L_{m2}$ 와 누설인덕턴스  $L_{lk}$ 는 에너지를 저장한다. 따라서 일차 측전류  $i_b$ 는 다음과 같이 표현된다.

$$i_p(t) = i_p(t_2) + \frac{V_o/N_2 - V_b}{L_{m1} + L_{lk}} (t - t_2)$$

(2)

$Mode\ 4\ [t_3,\ t_4]$ : 인덕터  $L_b$ 의 전류  $i_{Lb}$ 가 영이 된다. 인덕터  $L_b$ 에 대하여  $T_s$  동안 voltage-second balance rule을 적용하면 다음의 관계식이 도출되며

$$|v_i|DT_s = (V_d - |v_i|)\Delta T_s \tag{3}$$

$\Delta T_s$ 를 다음과 같이 나타낼 수 있다.

$$\Delta T_s = \frac{|v_i|DT_s}{(V_d - |v_i|)} \tag{4}$$

$Mode\ 5\ [t_4,\ t_5]:\ S_2$ 가 소거되면서 일차 측 전류  $i_p$ 는 스위치  $S_1$ 의  $C_{SI}$ 을 방전시키며, 스위치  $S_2$ 의  $C_{S2}$ 를 충전시킨다. 이에 따라 스위치  $S_1$ 의 양단 전압  $V_{SI}$ 은 영으로 감소하고, 스위치  $S_2$ 의 양단 전압  $V_{S2}$ 는 DC-link 전압  $V_{G2}$ 로 증가하며, 각 트랜스포머의 이차 측 양단의 전압이 바뀌기 시작한다. 스위치  $S_1$ 의 양단 전압  $V_{SI}$ 이 영전압이 되면, 스위치  $S_1$ 의 게이팅 신호  $V_{GSI}$ 이 인가되면서,  $S_1$ 의 영전압 스위칭 (ZVS)이 이루어진다.

교류 입력 전압  $v_i$ 가 음의 주기 (Negative half-line cycle)일 때는 스위치  $S_2$ 가 제어된다. 스위치  $S_2$ 의 듀티비가 D일 때, 스위치  $S_1$ 과  $S_2$ 의 도통 시간은 각각  $(1-D)T_s$ 와  $DT_s$ 로 표현된다. 스위치  $S_2$ 가 켜질 때, 입력 전류  $i_i$ 는  $S_2$ ,  $D_3$ ,  $L_b$ 를 통하여 흐르게 된다. 스위치  $S_2$ 가 꺼질 때, 입력 전류  $i_i$ 는  $S_1$ ,  $D_{S_1}$ ,  $C_d$ ,  $D_2$ ,  $L_b$ 를 통하여 흐르게 된다.

각 트랜스포머의 자화 인덕턴스에 대하여  $T_s$  동안 voltage-second balance rule과  $t_2-t_0\cong DT_s$ ,  $t_5-t_2\cong (1-D)T_s$ 을 통하여 다음의 전압 관계식을 도출할 수 있다.

$$V_b = DV_d \tag{5}$$

$$\frac{V_o}{V_d} = \frac{D(1-D)}{D/N_1 + (1-D)/N_2} \tag{6}$$

직렬 연결된 두 트랜스포머들의 턴비가  $N = N_1 = N_2$ 일 때, 식 (6)의 전압 관계식은 다음과 같이 표현된다.

$$\frac{V_o}{V_l} = ND(1-D) \tag{7}$$

### 3. 회로 설계

#### 3.1 부스트 인덕터

제안된 컨버터의 부스트 인덕터  $L_b$ 는 불연속 모드로 동작한다. 부스트 인덕터 전류의 첨두치  $i_{Lb,peak}$ 는 입력 전압을 추종해야 한다. 따라서, 불연속 모드 동작을 위한 부스트 인덕터  $L_b$ 는 교류 입력 전압의 실효치  $V_t$ 와 최대 출력 전력  $P_{o,max}$ 에 대하여 식 (8)을 통해 구할수 있고

$$L_b < \frac{V_i^2 D T_s}{2 P_{o,\text{max}}} \tag{8}$$

$i_{Lb,peak}$ 는  $T_s$  구간에 대하여 다음과 같이 표현된다.

$$i_{Lb,peak} = \frac{V_i D T_s}{L_b} \tag{9}$$

식 (4)와 (9)로부터 부스트 인덕터 전류의 평균치  $i_{Lb,avg}$ 는 다음과 같이 표현된다.

$$i_{Lb,avg} = \frac{i_{Lb,peak}}{2} (D + \Delta) T_s$$

$$= \left(\frac{V_i D^2}{\sqrt{2} L_b f_s}\right) \left(\frac{|\sin wt|}{1 - \frac{\sqrt{2} V_i}{V_d} |\sin wt|}\right)$$

(10)

#### 3.2 DC-link 커패시터

제안된 컨버터의 DC-link 커패시터는 60 Hz 교류 입력 전압에 대하여 120 Hz 리플 전압을 지닌다. 교류 입력 전압으로부터 양의 반주기 동안 입력된 에너지  $E_i$ 와 출력된 에너지  $E_o$ 는 라인 주파수  $f_i$ 과 출력 전력  $P_o$ 에 대하여 다음과 같이 표현된다.

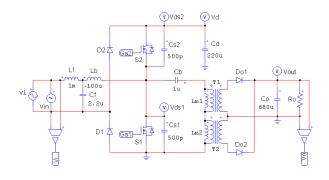

그림 4 시뮬레이션 회로도 Fig. 4 Diagram of simulation circuit

$$E_{i} = \int_{0}^{\frac{1}{2f_{l}}} |v_{i}| i_{Lb,avg} dt \tag{11}$$

$$E_o = \frac{P_o}{2f_I} \tag{12}$$

$E_i = E_o$ 를 가정하면, DC-link 커페시터의 전압  $V_o$ 는  $P_o$ ,  $L_b$ , D,  $f_o$ ,  $f_o$ 과 연관되는 식의 형태로 다음과 같이 표현된다.

$$\frac{P_o L_b f_s}{\sqrt{2} V_d D^2 f_l} = \int_0^{\frac{1}{2f_l}} \left( \frac{V_i^2 |\sin wt|^2}{1 - \sqrt{2} V_i |\sin wt|} \right) dt \quad (13)$$

## 4. 실험 결과

제안된 컨버터의 성능을 검증하기 위하여 교류 입력 전압  $V_i = 90 \text{ V}_{rms} \sim 150 \text{ V}_{rms}$ 에 대하여 250 W (48 V / 5.2 A) 회로를 설계하여 실험하였다. 일반적으로 동일한 출력 부하에 대하여 교류 입력 전압이 낮아지면, 도통 손실 및 스위칭 손실의 증가되어 AC-DC 컨버터의 전력 손실이 증가된다. 따라서 제안된 컨버터는 그성능 검증을 위하여 가장 낮은 교류 입력 전압  $V_i = 90 \text{ V}_{rms}$ , 출력 전압  $V_o = 48 \text{ V}$ , 스위칭 주파수  $f_s = 50 \text{ kHz}$ 에 대하여 설계하였다. 컨버터 동작을 위하여  $L_f = 1 \text{ mH}$ ,  $C_f = 2.2 \text{ µF}$ ,  $C_b = 1 \text{ µF}$ ,  $C_o = 680 \text{ µF}$ ,  $L_{ml} = 1 \text{ L}_{ml} = 50 \text{ µH}$ 의 회로 소자들을 이용하였다. 식 (8)과 식

298

- (a) 입력 전압 ( $V_{in}$ )과 인덕터 전류 ( $I_{Lb}$ ) 및 DC-Inik 전압 ( $V_{id}$ )

- (a) Input voltage (  $V_{in}$ ), inductor current (  $I_{Lb}$ ), and DC-link voltage (  $V_d$ )

- (b) 스위치 전압 (V<sub>ds1</sub>, V<sub>ds2</sub>)과 스위치 전류 (i<sub>S1</sub>, i<sub>S2</sub>)

- (b) Switch voltages ( $V_{ds1}$ ,  $V_{ds2}$ ) and switch currents ( $i_{S1}$ ,  $i_{S2}$ )

그림 5 시뮬레이션 결과

Fig. 5 Simulation results

(13)으로부터,  $L_b$  = 100  $\mu$ H,  $C_d$  = 220  $\mu$ F 회로 소자를 선택하였다. 스위칭 소자들은  $S_I$  =  $S_2$  = 20N60C3,  $D_I$  =  $D_2$  = SFR305PT,  $D_{o1}$  =  $D_{o2}$  = DSEK6002을 이용하였다. 출력 전압 제어를 위해 단일 칩 마이크로 컨트롤러 (Microchip, dsPIC30F3011)를 이용하여 디지털제어기를 구현하였다.

그림 4는 제안된 컨버터의 시뮬레이션 회로도를 나타낸다. 시뮬레이션은 PSIM 소프트웨어 프로그램을 이용하여 입력 전압  $v_i = 90 \text{ V}_{ms}$ 에서 정격 부하에 대한 제안된 컨버터의 동작을 검증했다. 그림 5는 제안된 컨버터의 시뮬레이션 결과를 나타낸다. 그림 5(a)는 90  $V_{ms}$  교류 입력 전압에 대하여 인덕터 전류  $(i_{Lb})$ 와 DC-link 전압  $(V_d)$ 을 나타낸다. 그림 5(b)는 각 스위치들의 전압과 스위치들의 전류를 나타낸다. 각 스위치전압이 영전압 (Zero-voltage)이 될 때, 각 스위치전 대는 영전류 (Zero-current)보다 낮음으로서, 각 스위치가 켜지는 시점에 영전압 스위칭 (ZVS)이 이루어짐을 알 수 있다.

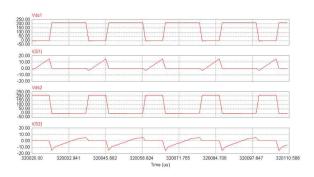

- (a) 입력 전압 (v<sub>i</sub>)과 입력 전류 (j<sub>i</sub>) 파형

- (a) Waveforms of line input voltage  $(\nu_i)$  and current  $(j_i)$

- (b) 일차 측 전류 (*i<sub>p</sub>*), DC-link 전압 (*V<sub>d</sub>*)과 출력 전압 (*V<sub>o</sub>*) 파형

- (b) Primary current (  $i_{\rho}$ ), DC-link voltage (  $V_d$ ), and output voltage (  $V_o$ )

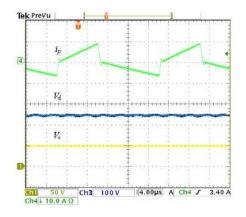

그림 6 제안하는 컨버터의 실험 파형

Fig. 6 Experimental waveform of the proposed converter

그림 6은 250 W 출력 부하에 대한 제안된 컨버터의 실험 파형을 나타낸다. 그림 6(a)는 교류 입력 전압  $(v_i)$ 과 입력 전류  $(i_i)$  파형을 나타낸다. 그림 6(b)는 일차 측 전류  $(i_p)$ , DC-link 전압  $(V_d)$ 과 출력 전압  $(V_d)$  파형을 나타낸다. 90  $V_{rms}$  교류 입력 전압과 250 W 출력 부하에 대하여 측정된 역률은 0.99로서 제안된 컨버터를 통하여 역률 개선을 이룰 수 있음을 확인할수 있다. 60 Hz의 90  $V_{rms}$  교류 입력 전압에 대하여 250 W 전력을 공급할 때, 250 V의 DC-link 전압에 대하여 8 %의 120 Hz 리플 전압을 확인할수 있다. 또한, 정류용 브릿지 다이오드를 사용하지 않고 교류 전력을 직류 전력으로 단일 변환 할수 있음을 확인할

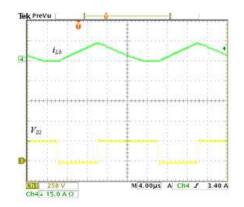

- (a) 인덕터 전류 (ilb)와 스위치 전압 (Vsi) 파형

- (a) Waveforms of line input voltage (  $V_{SI}$  ) and current (  $i_{Lb}$  )

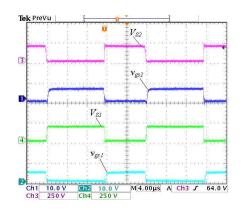

- (b) 스위치 구동 전압 ( $V_{OS1}$ ,  $V_{OS2}$ )과 스위치 전압 ( $V_{S1}$ ,  $V_{S2}$ ) 파형

- (b) Switch gating signals ( $V_{QS1}$ ,  $V_{QS2}$ ) and voltages ( $V_{S1}$ ,  $V_{S2}$ ) across the switches  $S_1$  and  $S_2$

그림 7 제안하는 컨버터의 실험 파형

Fig. 7 Experimental waveform of the proposed converter

#### 수 있다.

그림 7은 250 W 출력 부하에 대한 제안된 컨버터의 동작 방식을 보여주는 실험 결과를 나타낸다. 그림 7(a)는 인덕터 전류  $(i_{Lb})$ 와 스위치 전압  $(V_{SI})$  파형을 나타낸다. 인덕터 전류  $i_{Lb}$ 는  $T_s$ 에 대하여 불연속 모드 (DCM)로 동작함을 확인 할 수 있다. 그림 7(b)는 각스위치 구동 전압 $(V_{gSI},\ V_{gSS})$ 과 스위치 전압  $(V_{SI},\ V_{SS})$  파형을 나타낸다. 각 스위치 전압이 영전압이 된 후에 스위치 구동 전압이 인가됨으로서 각 스위치가 켜지는 시점에 영전압 스위칭 (ZVS)이 이루어짐을 실험적으로 확인할 수 있다.

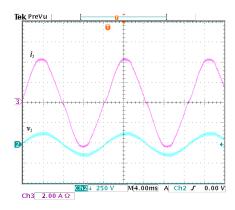

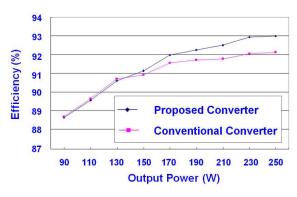

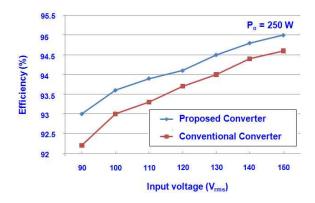

그림 8은 출력 부하의 변화에 따른 제안된 컨버터의

- (a) 출력 부하에 따른 효율 곡선

- (a) Efficiency curve for output load variations

- (b) 입력 전압에 따른 효율 곡선

- (b) Efficiency curve for line input voltage variations

그림 8 측정된 효율 곡선

Fig. 8 Measured power efficiencies

효율과 두 개의 직렬 연결된 트랜스포머를 사용하는 기존의 단일단 역률 개선용 AC-DC 컨버터<sup>[4]</sup>의 효율 을 비교한다. 기존 컨버터의 경우, 제안된 컨버터 설계 와 동일한 입력 전압 (90 V<sub>rms</sub> ~ 150 V<sub>rms</sub>) 및 동일 스 위칭 주파수(50 kHz)에 대하여 설계하였다. 기존 컨버 터의 경우 정류용 브릿지 다이오드 RBV1506을 사용 하였다. PFC용 결합 인덕터와 부스트 인덕터는 제안 된 컨버터의 제작과 동일하게 도통 손실과 스위칭 손 실이 가장 심한  $90~V_{rms}$  입력 전압에 대하여 설계 후 실험하였다. 그림 8(a)는출력 부하에 따른 효율 곡선을 나타낸다. 제안된 컨버터는 정격 부하에서 93 %의 효 율을 나타낸다. 반면 기존 컨버터는 정격 부하에서 92.2 %의 효율을 나타낸다. 제안된 컨버터는 기존 컨 버터에 비하여 0.8 %의 전력 변환 효율을 증가시킴을 확인 할 수 있다. 기존 컨버터의 경우 제안된 컨버터 에 비하여 정류용 브릿지 다이오드 사용으로 인한 도

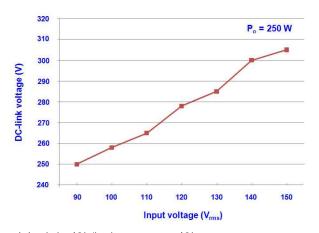

- (a) 입력 전압에 따른 DC-link 전압

- (a) DC-link voltage for line input voltage variations

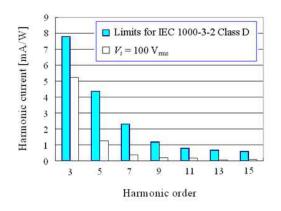

- (b) 측정된 THD 성분

- (b) Measured harmonic currents

그림 9 측정 실험 결과

Fig. 9 Measured experimental results

통 손실의 증가 및 별도의 PFC용 결합 인덕터의 사용으로 인한 자성체의 Core 손실 등이 주된 효율 감소의 원인이다. 그림 8(b)는 입력 전압에 따른 250~W~ 출력부하에 대하여 측정된 효율을 나타낸다. 도통 손실 및 스위칭 손실이 가장 큰  $90~V_{rms}$  교류 입력 전압에서 효율이 가장 크게 개선됨을 알 수 있다.

그림 9는 제안된 컨버터의 입력 전압에 따른 DC-link 전압과 교류 입력 전류의 왜곡률 (Total Harmonic Distortion: THD)을 나타낸다. 그림 9(a)는 입력 전압에 따른 DC-link 커패시터의 측정된 전압을 나타낸다. 일정한 출력 부하에 대하여 교류 입력 전압이 증가함에 따라 DC-link 전압도 상승함을 알 수 있다. 그림 9(b)는 제안된 컨버터의 THD 성분을 IEC 1000-3-2 Class D 제한 규격과 비교하여 나타낸 그림

이다. 제안된 컨버터는  $100~V_{rms}$  교류 입력 전압에 대하여 IEC 1000-3-2 Class D 제한 규격을 충분히 만족시킴을 확인할 수 있다.

## 5. 결 론

본 논문에서는 정류용 브릿지 다이오드가 없는 고효율 하프 브릿지 AC-DC 컨버터를 제안하였다. 제안된 컨버터는 정류용 브릿지 다이오드를 사용하지 않고 교류 입력 전압으로부터 절연된 직류 출력 전압을 공급함으로서, 간단한 회로 구조와 함께 도통 손실을 줄일수 있다. 또한 스위칭 소자들의 영전압 스위칭 동작을통하여 스위칭 손실을 줄일수 있다. 뿐만 아니라, 두개의 직렬 연결된 트랜스포머를 구비함으로서, 컨버터의 전력밀도를 높을 수 있다. 제안된 컨버터는 250~W (48~V~/5.2~A) 회로 설계를 통하여  $90~V_{ms}$  교류 입력 전압에 대하여 그 성능을 실험적으로 검증하였다. 제안된 컨버터를 통하여 정격 부하에 대해 93~%의 높은 효율과 0.99의 높은 역률 개선 결과를 얻었다. 따라서 제안된 컨버터를 통하여 저가격 및 고효율 AC-DC 컨버터 설계를 이룰 수 있다.

이 논문은 2010년도 정부(교육과학기술부)의 재원으로 한국연구재단의 지원을 받아 수행된 연구임(No. 2010-0029431).

#### 참 고 문 헌

- [1] A. Fernandez, J. Sebastian, M. M. Hernando, P.Villegas, and J. Garcia, "Helpful hints to select a power-factor-correction solution for low- and medium-power single-phase power supplies," IEEE Trans. on Industrial Electronics, Vol. 52, pp. 46~55, Feb. 2005.

- [2] C. Qiao, and K. M. Smedley, "A topology survey of single-stage power factor corrector with a boost type input current shaper," IEEE Trans. on Power Electronics, Vol. 16, pp. 360~368, May 2001.

- [3] T. F. Wu, J. Cj. Hung, S. Y. Tseng, and Y. M. Chen, "A single-stage fast regulator with PFC based on an asymmetrical half-bridge topology," IEEE Trans. on Industrial Electronics, Vol. 52, pp. 139~150, Feb. 2005.

- [4] W. Y. Choi, J. M. Kwon, H. L. Do, and B. H. Kwon,

- "Single-stage half-bridge converter with high power factor," IEE Proceeding on Electric Applications, Vol. 152, pp. 634~642, May 2005.

- [5] L. Huber, Y. T. Jang, and M. M. Jovanovic, "Performance evaluation of bridgeless PFC boost rectifiers," IEEE Trans. on Power Electronics, Vol. 23, pp. 1381~1390, May 2008.

- [6] W. Y. Choi, J. M. Kwon, and B. H. Kwon, "Bridgeless dual-boost rectifier with reduced diode reverse-recovery problems for power-factor correction," IET Proceeding on Power Electronics, Vol. 1, pp. 194~202, Jun. 2008.

- [7] Y. K. Lo, and J. Y. Lin, "Active-clamping ZVS flyback converter employing two transformers," IEEE Trans. on Power Electronics, Vol. 22, pp. 2416~2423, Nov. 2008.

- [8] H. K. Yoon, S. K. Han, J. S. Park, G. W. Moon, and M. J. Youn, "Zero-voltage switching two-transformer full-bridge PWM converter with lossless diode-clamp rectifier for PDP sustain power module," IEEE Trans. on Power Electronics, Vol. 21, pp. 1243~1252, Sep. 2006.

- [9] T. S. Kim, G. B. Koo, G. W. Moon, and M. J. Youn, "A single-stage power factor correction AC/DC converter based on zero voltage switching full bridge topology with two series-connected transformers," IEEE Trans. on Power Electronics, Vol. 21, pp. 89~ 97, Jan. 2006.

- [10] B. S. Kim, I. H. Lim, J. H. Lee, H. S. Ryu, and B. H. Kwon, "단일단 단일스위치 동기정류기형 플라이백 컨버터," 전력전자학회 논문지, 제11권, 제4호, pp. 361~ 370, Aug. 2006.

- [11] J. E. Yeon, J. B. Jeong, and H. J. Kim, "단일단 부스 트 입력방식의 공진형 AC/DC 컨버터," 전력전자학회 논문지, 제9권, 제1호, pp. 65~72, Feb. 2004.

- [12] G. B. Koo, T. S. Kim, G. W. Moon, and M. J. Youn, "직렬 연결된 두 개의 트랜스포머를 갖는 새로운 위상 천이 풀 브릿지 컨버터," 전력전자학회 논문지, 제7권, 제5호, pp. 443~452, Oct. 2002.

## 저 자 소 개

## 최우영(崔祐榮)

1979년 8월 30일생. 2004년 전남대 공대 전기공학과 졸업. 2009년 포항공과대 전자전기공학과 졸업(공박). 2009년 ~2010년 Virginia Tech (Post Doc.). 2010년 ~현재 전북대 전자공학부 전임강사.

유주승(柳主勝)

1986년 2월 18일생. 2004년~현재 전북 대 전자공학부 재학.

## 최제연(崔堤然)

1986년 12월 18일생. 2005년~현재 전북 대 전자공학부 재학.