## 특집: TSV를 이용한 3차원 전자접합

# 솔더 인터커넥터를 이용한 3차원 TSV 패키지의 신뢰성 연구

이 행수·김경호·좌성훈

# Reliability Study of 3D TSV Package Using Solder Interconnect

Haeng-Soo Lee, Kyoung-Ho Kim and Sung-Hoon Choa

## 1. 서 론

TSV(through silicon via)를 이용한 3차원 적층 칩 패키지 기술은 여러 개의 기판 혹은 다른 종류의 칩 들이 수직 방향으로 적층(stack)되는 형태의 패키징 기술이다. TSV 기술은 실리콘 웨이퍼를 관통하는 미세 비아(via) 홀을 형성한 후 비아 홀 내부에 전도성 물 질, 주로 구리(copper)를 충전시켜 칩 내부에 직접 전 기적 연결 통로를 확보하는 기술이다. TSV 기술을 사 용할 경우, 기존의 와이어 본딩을 이용한 적층 기술에 비해 고성능, 저전력, 고집적화 및 고기능의 효과가 발 생하기 때문에 최근 반도체 업계의 차세대 패키징 기술 로서 개발이 한창 진행 중에 있다. 특히 TSV 기술을 스마트 기기에 적용할 경우, 고질적인 문제로 지적되고 있는 배터리의 전력 소모 문제가 어느 정도 해결이 될 수 있기 때문에, 향후 스마트 폰 및 모바일 기기에 사 용되는 반도체 칩은 대부분 TSV 기술 방식의 칩 적층 기술이 사용될 것으로 예상된다<sup>1)</sup>.

그러나 아직 TSV 기술은 공정상에 여러 문제들과 패 키지 비용 저가격화를 실현하는 문제가 남아있다. 특히. 패키지 신뢰성에 대한 문제 해결이 향후 상업화에 도달 하기 위한 큰 난제로 부각되고 있다. 3차원 적층 칩은 다양한 재료로 이루어진 복잡한 구조로 되어있다. 또한 배선(interconnect)의 수가 증가하고 칩의 크기가 작 아짐에 따라서 열응력 및 기계적 피로로 인한 파괴 등 이 발생할 가능성이 많다. 특히 배선 간의 전기적 손실 을 최소화하기 위한 재료로써 구리를 사용할 경우에 발 생할 수 있는 신뢰성 문제는 간과할 수 없다. 구리는 실리콘 기판에 비하여 6~7배의 높은 열팽창계수 (coefficient of temperature expansion, CTE) 값 을 갖는다. 따라서 TSV 공정 중에 발생되는 열응력은 소자의 신뢰성에 큰 영향을 미친다<sup>2)</sup>. 또한, 비아 홀 (via hole)의 직경이 작아짐에 따라 TSV에 발생하는 응력 집중을 무시할 수 없다<sup>3)</sup>. 현재 TSV 기술에서 발 생할 수 있는 신뢰성 문제를 정리하면 다음과 같다.

- 적층 칩의 열 방출 문제

- 열기계적 응력 및 열피로 수명

- 휨 현상 (warpage)

- 공정 및 웨이퍼 thinning에 의한 잔류 응력

- 솔더(solder) 조인트의 피로 파괴

- 충격 및 기타 환경 신뢰성 문제

본 논문에서는 칩과 칩을 적층하고, 연결하기 위하여 솔더를 사용하고, 비아를 구리로 채운 TSV 구조의 패키지에 대하여 열기계적 응력, 열피로 현상, 패키지의 휨현상에 대해서 수치해석을 이용하여 신뢰성 연구를 수행하였다.

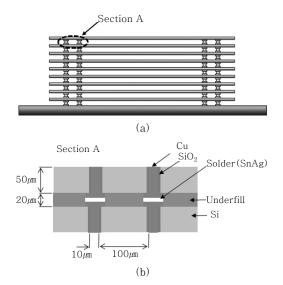

### 2. 해석 모델 및 조건

본 연구를 위하여 제안된 TSV 적층 패키지의 개략도 는 Fig. 1(a)과 같다. 폭이 30mm×30mm, 두께가 0.6mm인 실리콘 기판 위에 얇게 thinning된 8층의 실리콘 칩이 구리 TSV로 배선되어 각각 쌓여있다. 실 리콘 칩의 크기는 13.5mm x 13.5mm 이며, 두께는 50µm이다. Fig. 1(b)를 보면 TSV는 실리콘 칩 위에 구리 패드 (Cu pad), 솔더 (solder), 그리고 구리 패 드 순서로 연결된 구조 위에 구리로 채워진 비아로 이 루어져있다. 비아는 각 칩의 가장자리를 따라 배치되어 있고 실리콘 칩 사이에는 언더필(underfill) 재료가 채 워져 있다. 솔더의 재질은 Sn96.5-Ag3.5 솔더가 사용 되었으며, 언더필은 BCB (Benzocyclobutene) 재료 를 사용하였다. Fig. 1(b)에서 각 실리콘 칩의 두께는 50㎞, 언더필의 두께, 즉 적층된 실리콘 칩과 칩 사이 의 간격은 20년, 언더필 부분의 구리패드의 두께, 솔더 와 구리패드의 두께는 각각 8μm, 4μm, 8μm로 일정하게 유지시켰다. 구리 비아의 절연 막으로 쓰인 SiO2 층의

Journal of KWJS Vol.29 No.3(2011) pp301-306 DOI: 10.5781/KWJS.2011.29.3.301

Fig. 1 (a) Schematic drawing of TSV packaging (b) Detailed drawing of TSV interconnection area (Section A in Fig. 1(a))

두께는 0.5µm이다.

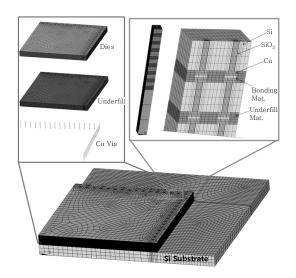

비아 홀의 크기와 비아 간의 피치 등 설계 변수들의 변화에 대한 응력 분포를 파악하기 위해 3D 유한요소해석(finite element method, FEM)을 수행하였다. 응력 집중은 구조의 파괴를 초래하므로 여기에서는 구리의 항복 응력 이상의 응력이 작용하는지 확인하였다. 상용 해석 프로그램인 ANSYS를 이용하여 8층의 실리콘 칩을 가진 3차원 TSV 모델을 구성하였으며, 전체모델 중 단위 비아 주위의 응력 분포를 살펴보기 위하여 Fig. 2와 같이 두 개의 비아를 포함하는 3층의 국부모델만을 사용하였다. 온도 조건으로서 온도를 초기온도 125℃에서 -40℃로 감소시킨다. 초기 온도인 125℃에서의 응력을 0 (free-stress)이라 하였다. 구리를 제

Fig. 2 Local model of TSV including 2 TSV holes

Table 1 Material properties of TSV structure materials used in FEM simulation

| Parts      | Material     | E<br>(GPa) | v<br>(Poisson's<br>ratio) | CTE<br>(ppm/℃) |

|------------|--------------|------------|---------------------------|----------------|

| Via        | Cu           | 120        | 0.34                      | 17             |

| Chip       | Si           | 130        | 0.28                      | 2.8            |

| Dielectric | SiO2         | 70         | 0.16                      | 0.6            |

| substrate  | Si           | 130        | 0.28                      | 2.8            |

| Underfill  | BCB          | 2.9        | 0.34                      | 52             |

| Solder     | Sn96.5-Ag3.5 | 52.7       | 0.4                       | 21.85          |

외한 나머지 재료들은 등방성 탄성재료로 가정하였고, 패키지재료의 물성치인 탄성계수(E), 프아송비, 열팽창계수는 Table 1에 제시하였다. 이 물성 값은 여러 논문에서 제시된 대표 값을 선택하였다<sup>4-6)</sup>.

패키지가 계속적인 온도의 변화에 영향을 받게 되면 각각의 부분을 구성하고 있는 재료들의 열팽창계수의 차이로 인하여 계속되는 응력 집중과 변형으로 인한 피로 파괴가 발생된다. 열에 의해 발생하는 피로로 인한 수명을 예측하기 위하여 우선, 주기적 열 사이클로 인한 열 피로 파괴가 예상되는 부위에 소성 변형률의 분포를 살펴보았다. 해석을 통해 얻어진 소성 변형률을 이용하여 Coffin-Manson 모델의 피로 수명 예측 (fatigue life prediction)식을 적용하였고 이론적인 피로 수명을 예측하였다.

## 3. 해석 결과 및 고찰

### 3.1 비아의 직경 및 피치의 영향

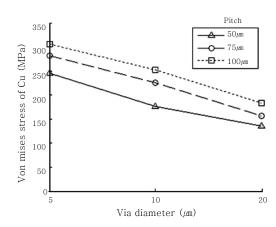

Fig. 3은 비아 크기에 따른 피치 별 구리 비아 내부의 최대 von Mises 응력을 나타낸다. 비아의 크기가 증가할수록 구리 비아 내부의 응력은 감소하게 된다.

Fig. 3 Computed von Mises stress in Cu via with different via sizes and pitch sizes

이것은 비아의 크기가 커짐에 따라 비아가 전체 패키지에서 차지하는 면적이 커지게 되므로 단위 면적 당구리 비아가 받는 응력이 감소하게 되기 때문이다. 한편비아 사이의 피치가 증가할수록 구리 비아 내의 응력또한 증가하는 것을 알 수 있다. 이것은 동일한 비아 크기에서 피치가 커짐에 따라 전체 패키지 내에서의 비아의 개수가 적어지게 되고, 결과적으로 단위 면적당 구리비아에 작용하는 응력이 커지기 때문이라고 판단된다.

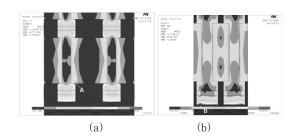

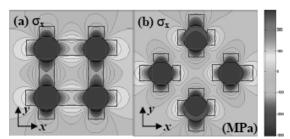

Fig. 4(a)는 비아의 직경이 10μm, 피치가 50μm일 때. 구리 비아를 중심으로 전체 패키지 단면의 von Mises 응력 분포를 보여준다. 응력은 A지점에서 최대 가 됨을 알 수 있다. A지점은 구리 패드, 언더필 재료, 실리콘이 모두 맞닿는 계면이다. 따라서 이러한 계면 부분에서 응력이 집중될 가능성이 크다. Fig. 4.(b)는 비아의 지름이 10μm, 피치가 25μm일 때의 응력 분포 를 나타낸다. 피치가 작아졌을 때, 즉 비아와 비아 사 이의 간격이 25µm로 매우 작아졌을 때에는 비아의 응 력이 다른 비아에 영향을 미쳐 비아 내부의 응력 및 주 변 실리콘 칩의 응력이 증가됨을 알 수 있었다. 따라서 비아 사이의 간격이 너무 작게 되면 비아와 비아 간의 응력 간섭이 발생되고 이로 인하여 비아 내부의 응력이 증가한다. 따라서 비아 간의 응력이 없는 상태를 추구 해야 하며 이러한 영역을 keep-away zone이라고 한 다. Lu 등<sup>7)</sup>은 다양한 TSV의 array 형태에 따라서 keep-away zone이 어떻게 변하는지에 대한 연구를 수행한 바가 있으며 Fig. 5는 keep-away zone의 한

**Fig. 4** Computed von Mises stress distribution (a) for 50μm pitch (b) for 25μm pitch

Fig. 5 Stress distribution for two different TSV arrays<sup>7)</sup>

형태를 보여주고 있다

## 3.2 열피로 수명 예측

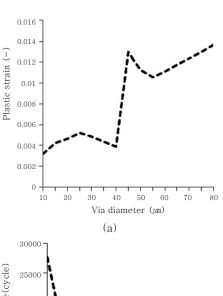

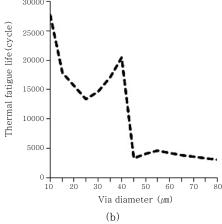

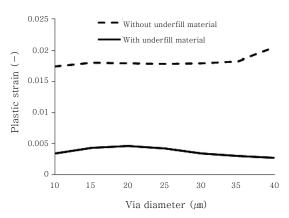

TSV 구조에서 피로 파괴가 발생이 예상되는 영역은 구리 비아, 솔더 및 구리 본딩 패드가 있다. 또한 각 영역의 접합 부분에서 피로 파괴가 발생할 수 있다. Fig. 6(a)에서 보면 피치가 200  $\mu$ m 경우 비아의 직경 이 증가됨에 따른 소성변형율의 변화를 보여주고 있다. 비아의 직경이 증가함에 따라 소성 변형율이 증가하는 경향을 보여주고 있다. 비아 직경이 40 세까가 되면 소 성 변형율은 급격히 증가한다. 소성 변형율은 비아 직 경이 50  $\mu$ m에서 최대가 되며, 그 후에는 약간 감소하 다가 다시 증가하게 된다. 이 결과는 비아 직경이 40 년 와 45 세사이의 구간에서 소성변형이 발생하였음을 의 미한다. Fig. 6(b)는 각 경우에 대한 열피로 수명을 보 여주고 있다. 비아 직경이 증가하면 열피로 수명은 감 소한다. 이러한 경향은 전술한 응력의 결과와 비교하여 보았을 때 매우 흥미로운 결과이다. Fig. 3의 결과를 보면 비아 크기가 작아질수록 von Mises 응력은 증가

Fig. 6 (a) Plastic strain of TSV structure (b)

Expected thermal fatigue life of TSV structure

한다. 따라서 비아의 직경이 작을 경우 수명이 증가하지만 안전하다고는 할 수 없다. 비아의 직경이 감소하게 되면 응력, 즉 von Mises 응력은 증가한다. 따라서비아의 직경이 작아질 경우에는 열응력을 감소시키기위한 추가적인 설계가 고려되어야 할 것으로 판단된다.

### 3.3 언더필 재료의 영향

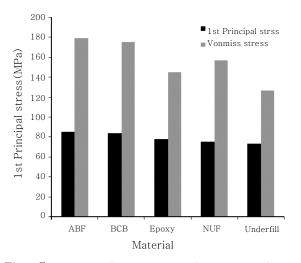

언더필 재료는 실리콘 칩 사이의 완충 역할을 해준다. 그러나 언더필 재질의 강성이 너무 높거나, 주변 재료와의 열팽창 계수의 차이가 과도할 경우 주변 재질, 특히 솔더의 변형 및 응력을 증가시키는 결과를 초대할 수 있다. 따라서 본 논문에서는 기존 논문들에서 제안되었던 여러 언더필 재료를 사용하였을 경우의 응력변화를 살펴보았다. ABF(Ajinomoto built-up film), Underfill, Epoxy, BCB, NUF(no flow underfill)의총 다섯 가지의 언더필 재료의 물성 값을 사용하여 해석하였고, 각각의 물성 값은 Table 2에 나타난 것과같다. Fig. 7은 언더필의 종류에 따른 응력 차이를 보여준다. ABF를 사용하였을 경우 구리 비아의 von

**Table 2** Material properties for different underfill materials

|           | E<br>(GPa) | v<br>(Poisson's ratio) | CTE<br>(ppm/℃) |

|-----------|------------|------------------------|----------------|

| ABF       | 3.5        | 0.27                   | 60             |

| Underfill | 3          | 0.33                   | 30             |

| Epoxy     | 6.1        | 0.35                   | 33             |

| BCB       | 2.9        | 0.34                   | 52             |

| NUF       | 5.3        | 0.35                   | 37.2           |

**Fig. 7** Computed stress for different underfill materials

Fig. 8 Maximum plastic strain with underfill material and without underfill material

Mises 응력이 최대가 되고, 그 다음으로는 BCB를 사용하였을 때가 컸다. Underfill을 사용하였을 경우가 구리 비아에서 발생하는 응력이 제일 낮았다. 물성 값을 보면 ABF의 열팽창계수가 제일 크고, 그 다음으로 BCB가 크다. 탄성계수가 제일 큰 Epoxy의 경우, 응력은 그리 크지 않다. 따라서 언더필의 경우 열팽창계수가 구리 비아의 응력에 가장 큰 영향을 미친다고 판단된다.

Fig. 8은 언더필이 있는 경우와 없는 경우의 비아 크기에 따라 최대 소성 변형률을 비교한 결과이다. 언더필이 없는 경우의 최대 소성 변형률은 언더필이 있는 경우의 최대 소성 변형률보다 7~8배 정도 더 크게 나타나 현저한 차이를 보임을 확인할 수 있었다. 이는 오랜 수명을 유지하기 위해서는 언더필이 필수적으로 사용되어야 함을 보여준다.

## 3.4 적층 공정에 따른 패키지의 휨 현상

TSV 공정 중에 발생되는 열응력은 TSV 구조의 응력 집중 및 파괴를 초래하게 되며, 또한 패키지의 휨 현상을 발생시키다. TSV 적층 기술에서 가장 중요한 이슈 중의 하나는 본딩 alignment 정밀도이다. TSV 공정에서는 얇은 칩을 본딩하는 적층 과정과 칩과 칩 사이에 언더필 재질로 채우게 되는 과정, 그 후에 annealing하는 과정을 반복적으로 수행하게 된다. 예를 들어 8층의 칩을 적층하기 위해서는 이러한 과정을 8번 반복해야 한다. 이렇게 고온과 상온의 공정 조건이 반복적으로 수행되면 실리콘 칩, 비아 홀의 구리, 언더필 재료의 CTE mismatch에 의하여 휨 현상이 발생하게 되고 이러한 휨 현상의 발생으로 인하여 적층된 칩은 out of plane 및 in-plane 변형을 초래하게 된다. 이러한 변형은 본딩 alignment에 영향을 미치며, 칩이 적층할

때 마다 mis-alignment의 양은 점점 증가하게 된다. 본딩 alignment는 비아 홀의 크기와 직접적인 관계가 있다. 즉, 비아 홀의 크기가 작아지면 본딩 alignment 에 요구되어지는 정밀도는 높아지게 된다. ITRS 로드맵에 의하면 비아의 직경은 2014년에 5  $\mu$ m 이하로 작아질 것이고, 이 경우 본딩 alignment 정밀도는 약0.6  $\mu$ m 이하가 되어야 된다고 예측하고 있다. 한편 휨현상으로 인하여 적층된 칩들이 변형하게 되면 본딩 접합부에는 전단응력이 발생하게 되고, 본딩 접합면이 파괴될 가능성이 높다. 따라서 패키지 각 공정에서의 warpage 현상을 분석하여 이를 최소화하기 위한 구체적인 방안이 필요하다.

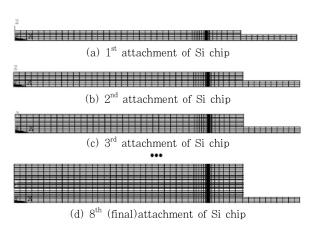

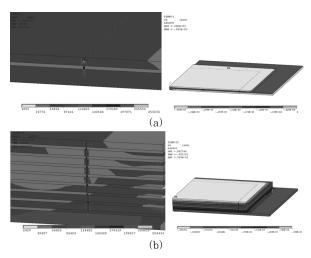

해석 모델로서 Fig. 9와 같이 8층의 적층 실리콘 3 차원 TSV 모델을 구성한다. 또한 시간대별로 층을 차 례로 추가해가며 해석을 수행하는 birth & death 기 법을 사용하여 이전 공정에서의 응력상태와 변형상태를 유지한 채 해석을 이어갈 수 있게 하였다. Fig. 10(a) 는 첫 번째 칩을 접합했을 경우의 warpage 및 von Mises 응력의 변화를 보여주고 있다. z 방향의 warpage 의 크기는 0.4 \(\mu\) 였으며, \(\text{xv}\) 방향으로의 변위, 즉 변 형은 약 3.5  $\mu$ m이다. 그리고 비아에 발생하는 최대 응 력은 763 MPa 이었다. Fig. 10(b)는 8번째의 칩을 접합했을 경우이며, 이때 최대 응력은 888 MPa, z 방 향의 warpage의 크기는 3.2 μm, xy 방향으로의 변위, 즉 변형은 약 9.6 µm이다. Table 3은 각 칩을 적층하 였을 때 발생한 warpage의 값을 나타내고 있다. 각 칩 이 적층 되면서 warpage와 xv 변형이 증가함을 알 수 있다. 결론적으로 8층의 칩을 적층한 후, 평면상의 휨 현상에 의한 최대 변형은 9.6  $\mu$ m로서 비아의 직경이 10 세 건을 감안하면 비아 직경만큼 변형이 발행하 였다. 따라서 향후 비아의 크기가 점점 줄어가고 있기

Fig. 9 Stacking process of Si chips in numerical modeling

**Fig. 10** Warpage and von Mises stress (a) after bonding 1<sup>st</sup> chip (b) after bonding 8<sup>th</sup> chip

Table 3

Warpage and xy displacement for each stacking process

| Ct                   | Displacement (um) |                 |  |

|----------------------|-------------------|-----------------|--|

| Step                 | In-plane(xy)      | Out of plane(z) |  |

| 1 <sup>st</sup> chip | 3.6               | -0.5            |  |

| 2 <sup>nd</sup> chip | 4.3               | -0.9            |  |

| 3 <sup>rd</sup> chip | 5.0               | -1.2            |  |

| 4 <sup>th</sup> chip | 5.9               | -1.6            |  |

| 5 <sup>th</sup> chip | 6.8               | -1.9            |  |

| 6 <sup>th</sup> chip | 7.8               | -2.3            |  |

| 7 <sup>th</sup> chip | 8.7               | -2.7            |  |

| 8 <sup>th</sup> chip | 9.6               | -3.0            |  |

때문에 휨 현상을 개선하기 위한 방안이 마련되어야 할 것이다

### 4. 결 론

본 연구에서는 솔더 인터커넥터를 이용한 TSV 패키지의 다양한 신뢰성에 대해서 수치해석을 통하여 신뢰성 문제를 분석하였다. TSV 구조는 공정이 복잡하고, 패키지의 재료도 다양하기 때문에 공정 중에, 또는 사용 환경에서 다양한 종류의 신뢰성이 발생할 수 있다. 따라서 수치해석이 사용된 신뢰성 예측을 통한 강건 설계의 필요성이 크다고 할 수 있다.

### 후 기

본 연구는 지식경제부, 산업기술연구회의 협동연구사업 일환인 "차세대 반도체 MCP 핵심기술 개발 사업"의

지원에 의한 것입니다. 또한 2010년도 한국연구재단의 기초연구사업(No. 2010-0004218)에 대한 지원을 받아 수행된 것입니다.

# 참 고 문 헌

- 1. Seungmin Hyun and Changwoo Lee: TSV Core Technology for 3D IC Packaging, Journal of KWS, 27-3 (2009), 4-9 (in Korea)

- Sehoon Yoo and Chang-woo Lee: Through Silicon Via Filling and Fine Pitch Joining Technology for 3D Electronic Package, Journal of KWS, 27-3 (2009), 17-22 (in Korea)

- 3. M.C. Hsieh and C. K. Yu: Thermo-mechanical Simulations For 4-Layer StackedIC Packages, EuroSimE Conf., (2008) 1-7

- 이행수

- 1966년생

- 울산과학대학 디지털 기계학부 교수

- 구조해석

- e-mail : haengsoolee@uc.ac.kr

- 김경호

- 1981년생

- 서울과학기술대학교

NID융합기술대학원 석사과정

- MEMS 및 반도체 패키징

- e-mail : nid\_kkh@seoultech.ac.kr

- 4. J. Zhang, Max O. Bloomfield, J. Lu, R. J. Gutmann, and T. S. Cale: Modeling Thermal Stresses in 3-D IC Interwafer Interconnects, IEEE Transactions on Semiconductor Manufacturing, 19-4 (2006) 437-448

- C. S. Selvanayagam, J. H. Lau, X. Zhang, S. Seah, K. Vaidyanathan and T. C. Chai: Nonlinear thermal stress/strain analyses of copper filled TSV and their flip-chip microbumps, 2008 Electronic Components and Technology Conference, (2008) 1073-1081

- L. J. Ladani: Numerical analysis of thermo- mechanical reliability of through silicon vias (TSVs) and solder interconnects in 3-dimensional integrated circuits, Microelectronic Eng., Vol. 87, (2010) 208-215

- K H. Lu, X. Zhang, S. Ryu, J. Im, R. Huang, and P. S. Ho: Thermo-Mechanical Reliability of 3-D ICs containing Through Silicon Vias, 2009 Electronic Components and Technology Conference, 630-634

- 좌성훈

- 1960년생

- •서울과학기술대학교 NID융합기술대학원 교수

- MEMS 및 반도체 패키징

- e-mail : shchoa@seoultech.ac.kr