# 데이터 페어링을 이용한 SDRAM의 전력 소모를 줄이는 DTMB 디인터리버 구조

## A DTMB Deinterleaver Structure to Reduce SDRAM Power Consumption with Data Pairing

강형주\*

Hyeong-Ju Kang\*

요 약

본 논문에서는 SDRAM의 전력 소모를 줄이는 DTMB 디인터리버의 구조를 제안한다. DTMB는 중국의 디지털 TV 표준으로써, 길이가 긴 지연버퍼들로 이루어진 디인터리버를 가지고 있다. 이 디인터리버를 구현하려면 SDRAM이 필요하다. 본 논문에서는 디인터리버에서 데이터를 페어링하여 두 개의 데이터를 한 번에 SDRAM에 읽거나 쓰는 구조를 제안한다. 제안된 구조는 SDRAM을 동작시키는 횟수를 줄임으로써 SDRAM에서 소모되는 전력을 약 35% 줄일 수 있다.

#### **Abstract**

This paper presents a DTMB deinterleaver structure to reduce SDRAM power consumption. DTMB, the Chinese digital TV standard, has a deinterleaver that consists of many long delay buffers. SDRAM is used for this deinterleaver. The proposed structure pairs data and transfer a pair with an SDRAM transfer. With the reduction of the SDRAM operation number, the proposed structure can save the SDRAM power consumption by around 35%.

Key words: DTMB, Deinterleaver, Convolutional Interleaver, SDRAM

### I. 서 론

지난 10여 년 동안 지상파 디지털 TV (Digital Terrestrial Television Broadcasting, DTTB) 산업은 급격하게 발전해왔다. 전 세계적으로 보면, Advanced Television Systems Committee (ATSC)표준을 미국이주도하고 있으며, 유럽에서는 Digital Video Broadcasting - Terrestrial (DVB-T)가 많이 채택되고 있다. 일본과 중남미에서는 Terrestrial Integrated

Services Digital Broadcasting (ISDB-T)가 선호되고 있고, 중국에서는 여러 해에 걸친 경쟁 후에 2006년에 Digital Terrestrial Multimedia Broadcast (DTMB) 표준이 발표되었다 [1].

디지털 TV 표준들은 각각의 고유한 특징들과 함께 서로 유사한 구조들도 가지고 있는데, 유사점들 중에서 대표적인 것이 인터리빙(interleaving)을 사용한다는 것이다. 인터리빙은 데이터를 송신할 때 그 순서를 뒤섞어 인접한 데이터가 서로 떨어지도록 하

<sup>\*</sup> 한국기술교육대학교 컴퓨터공학부(School of Computer Science and Engineering, Korea University of Technology and Education)

<sup>·</sup> 제1저자 (First Author) : 강형주

<sup>·</sup> 투고일자 : 2011년 3월 9일

<sup>·</sup> 심사(수정)일자 : 2011년 3월 10일 (수정일자 : 2011년 3월 30일)

<sup>·</sup> 게재일자 : 2011년 4월 30일

는 것을 말한다. 수신할 때는 다시 순서를 바꿔서 원래의 순서를 복구한다. 채널에서 발생하는 에러는 수신기에서의 순서 변환만을 겪으므로 인접한 에러, 즉burst 에러가 서로 떨어지게 되어서 random 에러로 바뀌게 된다. 길쌈 부호나 Reed-Solomon 부호와 같이burst 에러를 정정하는 능력이 제한적인 에러 정정 부호도, 인터리빙과 같이 사용하면 burst 에러의 정정능력을 향상 시킬 수 있다. 송신기에서 순서를 바꾸는 과정을 보통 인터리빙이라 부르고, 수신기에서 원래의 순서를 복원하는 과정을 보통 디인터리빙 (deinterleaving)이라고 부른다.

인터리빙은 크게 두 가지 방식이 있다. 블록 인터리빙(block interleaving)은 보내는 데이터를 블록 단위로 나누고 그 블록 내에서 순서를 바꾸는 방식이다. 다른 하나의 방식은 길쌈 인터리빙(convolutional interleaving)으로써, 인접한 데이터에 서로 다른 양의지연을 주어서 순서를 바꾸는 방식이다 [2].

앞에서 언급한 디지털 TV 표준들은 모두 길쌈 인터리빙을 채택하고 있다. DTMB의 경우에는 입력 데이터에 52가지의 지연을 주는데, 0에서 최대51\*720=36720의 지연을 주게 되어 있어서 다른 표준에 비해 더 긴 지연 버퍼가 필요하다 [3]. 이것을 플립플롭으로 만든 쉬프트 레지스터로 구현하면 그 면적이 매우 커지므로 보통 메모리를 이용하여 써큘러버퍼 방식으로 구현한다. 이 때 필요한 메모리의 크기를 구해보면, 한 개의 데이터의 크기가 2byte일 때대략 2Mbyte가 된다. 이를 Static RAM(SRAM)으로 구현하면 그 크기가 역시 매우 커지므로, 보통 Synchronous DRAM(SDRAM)으로 구현한다 [4]. 수신칩의 크기를 줄이기 위해 보통 embedded 방식이나 stacked 방식의 SDRAM를 사용한다.

SDRAM은 SRAM에 비해 많은 양의 데이터를 적은 면적에 저장할 수 있으나, 보통 third-party에서 조달하므로 그 구성을 바꾸는데 제한이 있는 단점이 있다. 이러한 구성의 제한은 SDRAM을 효율적으로 사용하는데 있어 제약이 될 수 있다. 이와 같이 SDRAM을 요하는 디인터리버가 있고 SDRAM을 사용함에 있어 고려할 점이 있음에도, SDRAM을 이용한 디인터리버에 대한 연구는 그리 많지 않다. 대부분의 기존 연구는 여러 표준의 디인터리버를 하나의

하드웨어로 구현하거나 SRAM을 효율적으로 이용하는 방법에 집중되어왔다 [5]-[7].

본 논문에서는 DTMB 디인터리버에서 SDRAM을 효율적으로 사용하는 구조를 제시한다. 디인터리버에 작은 메모리를 두어서 입력 데이터들이 짝을 지어 SDRAM에 저장될 수 있도록 한다. SDRAM에서 읽을 때도 역시 짝을 지어 읽는다. 이를 통해 SDRAM을 접근하는 횟수를 줄여서 SDRAM에서 소모되는 전력을 줄일 수 있다.

본 논문은 다음과 같이 구성되어 있다. 2장에서는 DTMB 표준과 디인터리버 구조에 대해 살펴보고, 3 장에서 새 구조를 제안할 것이다. 4장에서 실험결과 를 제시한 뒤, 5장에서 결론을 맺을 것이다.

### Ⅱ. DTMB 디인터리버

이 절에서는 DTMB 수신기의 구조를 간략히 살펴 보고 DTMB의 디인터리버에 대해 설명할 것이다.

### 2-1 DTMB 수신기

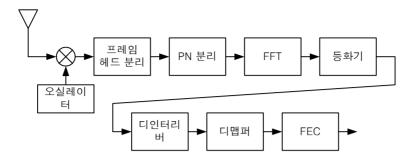

DTMB 수신기는 그림 1과 같이 구성되어 있다 [3]. 안테나를 통해 입력된 RF 신호는 오실레이터의 출력과 곱해져서 기저대역 신호로 변환된다. 기저대역 신호에서 프레임 헤드를 먼저 분리하고 다음으로 PN 시퀀스를 분리한다. DTMB는 cyclic-prefix를 사용하는 일반적인 Orthogonal Frequency Division Multiplexing (OFDM) 방식의 통신 표준들과는 다른 Time Domain Synchronized OFDM이라는 방식을 사용한다. 이 방식에서는 OFDM 심볼의 앞에 pseudorandom number(PN) 시퀀스를 두어서 심볼의 경계를 검출한다.

PN 시퀀스를 제거한 신호는 OFDM 심볼의 몸체만 남게 되며 이 OFDM 심볼에 Fast Fourier Transform(FFT)를 가하여 데이터 신호를 얻는다. 데 이터 신호는 디인터리버를 거쳐 원래의 데이터 순서 를 복원하고, 디맵퍼를 거쳐 데이터 값들을 추출한 다. 추출된 데이터 값들은 Forward Error Correction (FEC) 블록을 거치면서 에러가 수정된다.

그림 1. DTMB 수신기 구조 Fig. 1. DTMB receiver structure

### 2-2 DTMB 디인터리버

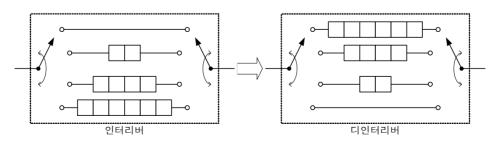

DTMB의 디인터리버는 길쌈 인터리빙 방식의 디인터리버이다. 길쌈 인터리빙은 그림 2와 같이 입력데이터에 서로 다른 지연을 주어서 데이터의 순서를바꾸는 방식이다. 수신기에서는 송신기에서의 지연값을 보상하는 만큼 데이터들에 지연을 가함으로써원래의 데이터 순서를 복원할 수 있다.

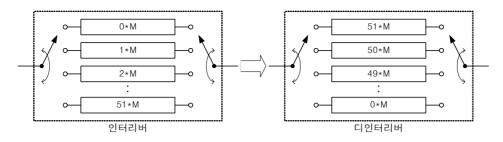

DTMB의 경우 시간 축에서 인터리빙을 깊게 하기위해 길쌈 인터리빙을 사용한다. DTMB의 인터리버와 디인터리버는 그림 3에 제시되어 있다. 그림에서 M값은 모드에 따라 240이거나 720이다. DTMB에서한 개의 OFDM 심볼은 3744개의 I/Q 샘플로 이루어지므로 [3], 한 OFDM 심볼에서 각 지연 버퍼는 72개의 데이터를 입력받고 출력한다.

DTMB의 디인터리버가 요구하는 저장 공간을 계산하면 다음과 같다. 데이터를 디매핑하기 이전이므로 입출력 데이터의 폭은 설계자가 수신기 성능을 고려하여 결정해야 한다. 일반적은 선택은 I와 Q 샘플을 각각 8비트로 해서 총 16비트이다. 지연 버퍼의 길이를 모두 더하면 51\*52/2 \* M = 1326 \* M이고 M이 720인 경우도 대처할 수 있어야 하므로, 저장 공간의크기는 1326 \* 720 \* 2byte = 1,909,440byte이다 [4].

### 2-3 DTMB 디인터리버의 구현

지연버퍼는 일반적으로 쉬프트 레지스터로 구현한다. 그러나 DTMB의 디인터리버는 쉬프트 레지스터로 구현할 경우 플립플롭이 차지하는 면적이 매우커진다. 쉬프트 레지스터의 대안은 메모리를 이용하는 써큘러 버퍼로 구현하는 것이다.

써큘러 버퍼 방식은 메모리의 일정 부분을 지연 버퍼에 할당해 주고, 지연 버퍼의 입력은 메모리에 차례로 저장하고, 지연 버퍼의 출력은 메모리에서 차 례로 읽어서 출력하는 방식을 말한다. 이 때 저장하 는 위치와 읽는 위치 사이의 간격을 일정하게 유지시 키면 지연 버퍼처럼 동작하게 된다.

저장한 데이터의 양이 많지 않을 경우에는 메모리의 위기/쓰기 동작을 빠르게 할 수 있는 SRAM을 메모리로 많이 이용한다. 그러나 DTMB 디인터리버의경우에는 SRAM으로 구현하기에도 저장 공간의 크기가 매우 크다. 따라서 일반적으로 SDRAM을 이용하여 구현한다 [4]. 이 때 SDRAM은 DTMB 수신칩의외부에 별도의 칩으로 연결할 수도 있으나, 일반적인선택은 embedded DRAM이나 stacked SDRAM이다.

그림 2. 길쌈 인터리빙 Fig. 2. Convolutional interleaving

그림 3. DTMB 인터리버와 디인터리버 Fig. 3. DTMB interleaver and deinterleaver

### Ⅲ. SDRAM의 전력 소모를 줄이는 DTMB 디인터리버 구조

이 절에서는 SDRAM을 사용할 경우 기존 DTMB 디인터리버에서 발생하는 문제점을 분석하고, SDRAM에서의 전력 소모를 줄이는 새로운 구조를 제안하다.

### 3-1 SDRAM을 이용한 구현의 문제점

일반적으로 논리회로의 합성 라이브러리를 제공하는 회사에서 SRAM 생성기도 같이 제공한다. 이 SRAM 생성기를 이용하면 다양한 구성의 SRAM을 생성할 수 있다. 이 때 바꿀 수 있는 구성으로는 SRAM의 데이터 폭, SRAM의 크기, SRAM의 내부 멀티플렉서 구조 등이 있다. 그러나 SDRAM의 경우에는 외부에서 구매하는 경우가 많으며 그 구성 역시 몇 가지 이내의 종류로 제한되는 경우가 많다.

이러한 SDRAM 구성의 제한으로 인해 SDRAM을 비효율적으로 이용하게 되기도 한다. 예를 들어, SDRAM의 데이터 폭과 디인터리버의 데이터 폭이 다르면, SDRAM을 읽거나 쓸 때 모든 데이터 라인을 이용할 수 없는 경우가 생긴다. 이러한 경우들에 의해 SDRAM을 효율적으로 이용하지 못하게 된다.

그리고 SDRAM은 하나의 데이터를 읽거나 쓰기 전에 그 데이터가 위치한 row를 활성화 시켜야 한다. DTMB 디인터리버의 경우에는 각 지연버퍼의 길이 가 대체로 길고 하나의 지연 버퍼가 여러 개의 SDRAM row에 걸쳐 있는 경우도 많다. 따라서 하나 의 지연 버퍼에 읽기와 쓰기를 한 번 할 때 거의 매번 row를 활성화 시켜야 한다. OFDM 한 심볼에 대해 계산해 보면, 3744개의 데이터가 52개의 지연 버퍼에 차례로 들어가므로, OFDM 한 심볼에 대략 3000여회 row를 활성화 시켜야 한다. SDRAM에서 row를 활성화 시키는 것은 전력을 많이 소모하는 작업 중의 하나이다.

### 3-2 SDRAM의 전력 소모를 줄이는 구조

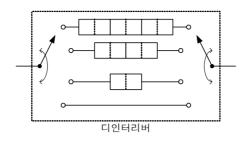

SDRAM의 전력 소모를 줄이기 위해 디인터리버를 그림 4와 같이 변환한다. 지연 버퍼의 길이가 짝수일 경우, 두 개의 데이터씩 짝을 지어서 하나의 데이터로 생각할 수 있다. 지연 버퍼에 저장할 때도 두개의 데이터를 묶어서 한 번에 저장하고, 지연 버퍼에서 읽을 때도 두 개의 데이터를 한꺼번에 읽는다. 즉, 데이터의 크기는 두 배이면서 길이는 절반인 지연 버퍼들이 된다.

이와 같이 변환을 하면 두 가지 이점이 생긴다. 첫 번째로 SDRAM의 데이터 폭이 클 경우 SDRAM을 읽거나 쓰는 횟수가 줄어든다. 예를 들어, SDRAM의 데이터 폭이 32비트이고, 디인터리버의 데이터 폭이 16비트이면, 두 개의 데이터를 동시에 읽고 쓸 수 있으므로 SDRAM을 읽고 쓰는 횟수가 절반으로 줄어드는 것이다. 디인터리버에서 사용하는 SDRAM은 주로 embedded DRAM이나 stacked SDRAM이므로 핀의 개수에 제한을 적게 받아서 데이터 폭이 32비트이상인 경우가 많다. 이러한 경우들에 본 논문에서 제안하는 구조가 유리한 것이다.

두 번째 이점으로 SDRAM의 row를 활성화시키는 횟수가 줄어든다. 버퍼 한 개의 길이가 SDRAM row

그림 4. 제안된 디인터리버 Fig. 4. Proposed deinterleaver.

의 길이보다 더 기므로 버퍼 하나에 대해 읽거나 쓸 때마다 SDRAM의 row를 한 개 씩 활성화시켜야 한다. 그러나 제안하는 구조에서는 두 개의 데이터를 묶어서 한 번만 SDRAM을 접근하므로 row를 활성화시키는 횟수도 절반으로 줄어든다.

제안하는 구조에서는 데이터를 두 개씩 묶기 위해 입력단과 출력단에서 데이터를 저장해야 한다. 입력 단에서 52개의 데이터를 저장할 공간이 필요하고 출 력단에서 52개의 데이터를 저장할 공간이 필요하다. 본 논문에서는 작은 메모리를 두어서 데이터들을 저 장했다.

### ₩. 실험 결과

본 논문에서 제안하는 구조와 기존의 구조를 표 1에서 비교하였다. 데이터의 폭은 16비트로, M은 720으로 가정하였다. '면적'열은 두 구조의 면적을 비교한 것으로써, 합성툴에서 제공하는 값을 2-input NAND equivalent gate count로 변환한 것이다. TSMC 0.25um 공정의 라이브러리로 Cadence사의 RTL Compiler를 이용하여 합성하였고, 클럭 주파수는 40MHz로 하였다. 입출력단에 있는 메모리로 인해 제안하는 구조가 기존의 구조에 비해 더 크다. 그러나두 면적 모두 수신칩 전체 면적에 비하면 무시할 수 있는 크기이다.

그 다음 열들에서는 SDRAM 동작을 분석하여, OFDM 한 심볼 당 읽고 쓰는 횟수와 row를 활성화시키는 평균 횟수를 비교하였다. SDRAM은 Micron 사의 MT48LC2M32B2로 가정하였다. Embedded DRAM이나 stacked SDRAM으로 비교하는 것이 타당하나, 이들 메모리에 대해서는 데이터가 공개되지 않고 있다. 그러나 전체적인 경향은 큰 차이가 없을 것이다. 표를 보면, SDRAM을 읽고 쓰는 횟수와 row를 활성화시키는 횟수가 모두 절반 정도로 줄어들었음을 알수 있다.

표 2에서 두 구조의 전력 소모를 비교하였다. SDRAM의 전력은 Micron 사에서 제공하는 SDRAM Power Calculator[8]를 이용하여 계산하였다. SDRAM을 읽고 쓰는 횟수와 row 활성화 횟수가 줄어듦에 따라 SDRAM에서의 전력 소모가 감소하였음을 볼 수 있다. DTMB 디인터리버의 경우 각 버퍼의 길이가길어서 SDRAM을 읽고 쓰는 횟수에 비해 row 활성화 횟수가 많다. 그러므로 활성화 전력이 전체 전력에서 큰 비중을 차지한다. 본 논문에서 제안된 구조는 활성화 전력을 절반으로 줄임으로써 전체 SDRAM 소모 전력을 35% 정도 줄일 수 있다.

표 1. 면적 비교 및 SDRAM 동작 분석 Table. 1 Area comparison and SDRAM operation analysis

|        | 면적<br>(gate count) | SDRAM 읽기 | SDRAM 쓰기 | SDRAM row 활성화 |

|--------|--------------------|----------|----------|---------------|

| 기존 구조  | 12523              | 3672     | 3672     | 3643          |

| 제안된 구조 | 17370              | 1836     | 1836     | 1822          |

|  |        | 전체 전력 | 배경 전력 | 활성화 전력 | 읽기/쓰기 전력 |

|--|--------|-------|-------|--------|----------|

|  | 기존 구조  | 134.6 | 42.4  | 89.6   | 2.6      |

|  | 제안된 구조 | 88.5  | 42.4  | 44.8   | 1.3      |

표 2. SDRAM 전력 소모 비교(mW)

Table 2. SDRAM power consumption comparison(mW)

### V. 결 론

본 논문에서는 SDRAM에서의 전력 소모를 줄이는 DTMB 디인터리버 구조를 제안하였다. DTMB 디인터리버는 여러 개의 긴 지연 버퍼로 이루어져서 SDRAM을 사용해야 한다. 제안된 구조에서는 입력단에서 데이터를 모아서 여러 개의 데이터를 한 번에 SDRAM에 읽거나 쓰게 함으로써 SDRAM에서의 전력 소모를 줄였다. 본 논문에서는 DTMB 디인터리버에 대해 제안하였지만, 여러 개의 긴 지연 버퍼로 이루어진 디인터리버에 폭 넓게 이용될 수 있을 것이다.

### 감사의 글

이 논문은 한국기술교육대학교 교육연구진흥비지 원 프로그램의 지원에 의하여 수행되었음.

### 참 고 문 헌

- [1] Z. Yang, Z. Wang, J. Wang, J. Wang, K. Peng, F. Yang, and J. Song, "Technical review for Chinese future DTTB system," *IEEE Vehicular Technology Conference Fall*, pp. 1-6, 2010.

- [2] J. L. Ramsey, "Realization of optimum interleavers," *IEEE Trans. Inform. Theory*, pp. 338-345, 1970.

- [3] M. Liu, M. Crussiere, J.-F. Helard, and O. P. Pasquero, "Analysis and performance comparison of DVB-T and DTMB systems for terrestrial digital TV," *Proc. Int. Conf. Communication Systems*, pp. 1399-1404, 2008.

- [4] Y. Zhong, H. Yang, and A. Prabhakar, "A VLSI implementation of a FEC decoding system for DTMB(GB20600-2006) standard," Proc. Int. Conf. ASIC, pp. 926-929, 2007.

- [5] M. Rim, "A VLSI architecture for convolutional deinterleavers," *Proc. Int. Conf. Consumer Electronics*, pp. 130-131, 1996.

- [6] Y.-N. Chang, "A multibank memory-based VLSI architecture of DVB symbol deinterleaver," *IEEE Trans. Very Large Scale Integration Systems*, pp. 840-843, 2010.

- [7] H. Yang, Y. Zhong, and L. Yang, "An FPGA prototype of a forward error (FEC) decoder for ATSC digital TV," *IEEE Trans. Consumer Electronics*, pp. 387-395, 1999.

- [8] Micron Technology, Inc., "SDRAM system-power calculator," http://www.micron.com/support/dram/ power calc.html

### 강 형 주 (姜亨周)

1998년 2월 : 한국과학기술원 전기 및 전자공학과(공학사)

2000년 2월 : 한국과학기술원 전자 전산학과(공학석사)

2005년 2월 : 한국과학기술원 전자 전산학과(공학박사)

2005년3월~2006년1월 (주)매그나챱반도체

2006년 2월 ~ 2009년 2월: (주)지씨티리써치 2009년 3월 ~ 현재: 한국기술교육대학교 전임강사 관심분야: VLSI 설계, 통신 모뎀 설계