# 다중 안테나 통신 시스템을 위한 저복잡도 채널 전처리 프로세서

# Low Complexity Channel Preprocessor for Multiple Antenna Communication Systems

황유선\*, 장수현\*, 한철희\*\*, 최성남\*\*, 정윤호\*

You-Sun Hwang\*, Soo-Hyun Jang\*, Chul-Hee Han\*\*, Sung-Nam Choi\*\* and Yun-Ho Jung\*

### 요 약

본 논문에서는 최대 4개의 송·수신 안테나를 지원 가능한 4x4 다중 안테나 (MIMO) 시스템에서 채널의 dimension을 축소함으로써 복잡도를 줄일 수 있는 저복잡도 채널 전처리 프로세서를 제안하고 구현한다. 제안된 채널 전처리 프로세서는 채널의 일부분을 간섭신호라 간주하고 제거하는 GIS 행렬을 구하는 데 있어서 행렬의 역행렬과 행렬간의 승산 연산을 줄이기 위해, QR 분해 기법을 이용하여 4x4 MIMO 채널 전처리 프로세서의 복잡도를 최소화한다. 또한, 로그 수체계를 이용하여 행렬간의 복소수 승산을 가산으로, QR 분해 기법의 사용으로 인해 생기는 나눗셈 연산을 감산 연산으로 대체함으로써 연산기의 단순화를 진행하고, 이를 통해 하드웨어 복잡도를 크게 감소시킨다. 제안된 채널 전처리 프로세서는 하드웨어 설계 언어 (HDL)을 이용하여 설계되었고, 0.13μm CMOS 규격 셀 라이브러리를 사용하여 합성되었다. 그 결과 기존의 2의 보수 수체계를 이용한 채널 전처리 프로세서의 설계 구조 대비 로그 수체계를 이용한 제안된 채널 전처리 프로세서의 하드웨어 복잡도가 20.2% 가량 감소됨을 확인하였다.

#### **Abstract**

In this paper, the channel preprocessor with an area-efficient architecture is proposed for the MIMO symbol detector which can support four transmit and receive antennas. The proposed channel preprocessor can shrink the channel dimension to reduce the hardware complexity of the MIMO symbol detector. Also, the proposed channel preprocessor is implemented with very low complexity by using QR decomposition (QRD) and log-number system (LNS). By applying QRD and LNS to the nulling matrix calculation block, the numbers of matrix-multiplications and matrix-divisions are decreased and thus the complexity of the proposed channel preprocessor is significantly reduced. The proposed channel preprocessor was designed in a hardware description language (HDL) and synthesized to gate-level circuits using 0.13um CMOS standard cell library. With the proposed channel preprocessor, the number of logic gates for channel preprocessor is reduced by 20.2% compared with the conventional architecture.

Key words: Channel Preprocessor, Log-Number System, MIMO, QR Decomposition

I. 서 론

최근 가정 및 기업 혹은 핫스팟 환경에서 고속의 무선 데이터 전송에 대한 수요가 늘어감에 따라 수백

\* 한국항공대학교 항공전자 및 정보통신 공학부(School of Electronics, Telecommunication and Computer Eng., Korea Aerospace University),

· 투고일자 : 2011년 2월 18일

· 게재일자 : 2011년 4월 30일

<sup>\*\*</sup> 삼성탈레스(주)(Samsung Thales, Co. Ltd)

<sup>·</sup> 제1저자 (First Author) : 황유선

<sup>·</sup> 심사(수정)일자 : 2011년 2월 18일 (수정일자 : 2011년 4월 6일)

Mbps 및 Gbps급 이상의 데이터 전송 속도를 지원할수 있는 차세대 무선 통신 시스템에 대한 관심이 고조되고 있다. 이러한 초고속 데이터 전송을 충족시킬수 있는 전송 기술로써, 다중안테나 (multiple-input multiple-output, MIMO) 시스템에 대한 연구가 활발히진행되고 있다 [1]. MIMO 기술은 송신 안테나 수에비례하여 채널의 용량을 증가시킬수 있으므로, IEEE 802.11n WLAN, IEEE 802.16e Mobile WiMAX등 최신 무선 통신 시스템에 적용되고 있다 [2-4].

MIMO 시스템은 송수신단에 여러 개의 안테나를 이용하여 동시에 서로 다른 데이터를 전송함으로써 대역폭의 증가 없이 고속의 데이터를 전송할 수 있는 공간 다중화 (spatial multiplexing, SM) 기술[3]과 송신 단에서 별도의 코딩을 거친 후 수신단에서 선형연산을 통해 다이버시티 이득을 얻고자 하는 공간 다이버시티 (spatial diversity, SD) 기술[2]로 구분된다. 전송신뢰도를 향상시키는 공간 다이버시티 기술은 수신단에서 선형 연산을 통해 maximum likelihood (ML) 심볼 검출이 간단히 이루어지는데 비해, 전송률을 향상시키는 공간 다중화 기술은 수신단에서 다중화된데이터들을 분리해야 하는 어려움이 있다 [3-4].

한편, MIMO 시스템은 하드웨어 복잡도가 크기 때 문에 무선 통신 단말의 소형화 추세를 고려했을 때, 최소의 복잡도를 갖는 하드웨어 구조 설계가 매우 중 요하다. 그러나, 최적의 성능을 보이는 ML 검출 기법 의 경우, 송신 안테나 수가 높아짐에 따라 연산 복잡 도가 지수적으로 증가하게 된다. 따라서 4x4 MIMO SM 심볼 검출기를 ML 수준 알고리듬에 의해 심볼 검출을 수행하는 경우 매우 큰 복잡도를 갖기 때문 에, 실시간 구현이 불가능하게 된다. 이에 MIMO 채 널의 특정한 부분을 간섭신호라 간주하여 제거하는 (Group Interference Suppression, GIS) 기법을 이용하 여 MIMO 채널을 nulling 함으로써, 채널의 dimension 을 축소 (4x4를 2개의 4x2채널로 분리)시켜 요구되는 연산량을 줄일 수 있는 심볼 검출 기법들이 연구되고 있다[5-6]. 이러한 심볼 검출 기법들에서 필수적으로 요구되는 블록이 MIMO 채널을 nulling 하는 채널 전 처리기 (channel preprocessor)이다. 한편, 채널 전처리 기법은 채널을 축소시켜서, 복잡도를 크게 낮추었으 나, GIS 행렬을 찾는 과정과, 채널을 nulling 하는 과 정에서, 다수의 곱셈기와 덧셈기가 필요하게 되어 여전히 실시간 구현이 어려운 문제를 갖는다. 따라서본 논문에서는 4x4 MIMO 시스템을 위한 최적의 채널 전처리기의 알고리듬과 하드웨어 구조 및 구현 결과를 제시한다.

본 논문의 구성은 다음과 같다. 먼저, II장에서는 MIMO 시스템 모델을 제시한다. III장에서는 그룹 간섭 제거에 대해 설명하고, IV장에서는 LNS를 이용한 제안된 채널 전처리기의 하드웨어 구조를 제안하고, 각블록별 구조를 설명한다. V장에서는 제안된 하드웨어 구조에 대한 구현 결과를 제시하고, 끝으로 VI 장에서 본 논문의 결론을 맺는다.

### Ⅱ. MIMO 시스템 모델

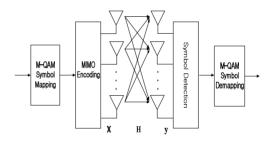

본 논문에서는 그림 1과 같이 NT개의 송신 안테나와 NR개의 수신 안테나로 구성되고, NR≥NT을 만족하는 무선 통신 채널을 고려한다. 수신 신호 벡터는 수식 (1)과 같이 표현할 수 있다.

그림 1. MIMO 시스템 모델 Fig. 1. MIMO System Model.

$$\mathbf{y} = \mathbf{H} \cdot \mathbf{X} + \mathbf{N} = \begin{bmatrix} h_1 & h_2 & \cdots & h_{N_T} \end{bmatrix} \cdot \mathbf{X} + \mathbf{N}$$

$$= \begin{bmatrix} h_{11} & h_{21} & \cdots & h_{N_T 1} \\ h_{12} & h_{22} & & h_{N_T 2} \\ \vdots & & \ddots & \vdots \\ h_{1N} & h_{2N} & \cdots & h_{N_N N} \end{bmatrix} \cdot \begin{bmatrix} x_1 \\ x_2 \\ \vdots \\ x_{N_T} \end{bmatrix} + \begin{bmatrix} n_1 \\ n_2 \\ \vdots \\ n_{N_T} \end{bmatrix}$$

$$(1)$$

여기서 xj, (j=1, 2, ···, NT)는 j번째 송신 안테나로 부터 전송되는 송신 심볼, yi, (i=1, 2, ···, NR) 는 i번째 수신 안테나에서 수신 신호를 각각 나타내며, hj,i (j=1, 2, ···, NT, i=1, 2, ···, NR) 는 j번째 송신 안테나 와 i번째 수신 안테나 사이의 페이딩 채널을 의미한다. ni, (i=1, 2, ..., NR)은 평균은 0이고  $\sigma^2$ 의 분산을가지는 additive white gaussian noise (AWGN)을 의미한다.

### Ⅲ. 제안된 채널 전처리 알고리듬

### 3-1 채널 전처리 알고리듬

MIMO 통신 시스템은 송신 안테나 수와 수신 안테 나 수가 높아짐에 따라 연산 복잡도가 지수적으로 증 가하기 때문에 실시간 구현에 어려움이 있다. 이에 MIMO 채널의 특정한 부분을 간섭신호라 간주하고, 간섭 성분을 제거하는 (Group Interference Suppression, GIS) 기법 중의 하나인 채널 전처리기를 이용하여 MIMO 채널을 nulling 함으로써, 채널의 dimension을 축소시켜 요구되는 연산량을 줄일 수 있 다. 예를 들어. 4x4 채널 행렬 H를 2개의 4x2 채널 Ha와 Hb를 사용하여 [Ha Hb]로 표현하고, Hb 성분을 제거하고자 한다면, GIS 행렬 G는 Hb의 성분을 입력 으로 하여 다음 (2)식과 같이 Hb의 역행렬 및 Hermition 변환으로 구성된다. 그리고 (3)식과 같이 GIS 행렬 G와 채널 행렬 H의 곱을 통해 Hb 성분이 nulling 되어 축소된 4x2 행렬을 구할 수 있다 [5].

$$\mathbf{G} = \left[\mathbf{I} - \overline{\mathbf{H}}_b (\overline{\mathbf{H}}_b^H \overline{\mathbf{H}}_b)^{-1} \overline{\mathbf{H}}_b^H\right]. \tag{2}$$

$$\mathbf{H}_{preprocessed} = \begin{bmatrix} \tilde{\mathbf{H}}_{a} & \mathbf{0} \end{bmatrix} = \mathbf{G} \cdot \mathbf{H}$$

(3)

여기서 G는 Hb 성분을 제거하기 위한 행렬이고, Hpreprocessed는 G 행렬과 H 행렬 간의 연산을 통해 얻어진 4x2 행렬이다. 채널 전처리기는 크게, 채널 행렬을 이용해 GIS 행렬을 찾는 과정과 GIS 행렬과 채널 행렬의 곱을 통해 nulling 연산을 하는 과정을 통해 채널을 분리할 수 있다.

## 3-2 QR 분해 (QR Decomposition, QRD)를 이용한 채널 전처리 알고리듬

수식 (2)를 통해 G 행렬을 구하기 위해서는 수 번의 행렬 곱셈과 역행렬 연산을 요구하기 때문에 복잡도가 매우 커지게 된다. 제안된 채널 전처리기는 이를 QR 분해의 특징인 QH·Q = I 를 이용하여, 수식(4)와 같이 간단히 구현된다.

$$\mathbf{G} = \left[\mathbf{I} - \mathbf{H}_{b} (\mathbf{H}_{b}^{H} \mathbf{H}_{b})^{-1} \mathbf{H}_{b}^{H}\right]$$

$$= \left[\mathbf{I} - \overline{\mathbf{Q}}_{b} \overline{\mathbf{R}}_{b} (\overline{\mathbf{R}}_{b}^{H} \overline{\mathbf{Q}}_{b}^{H} \overline{\mathbf{Q}}_{b}^{H} \overline{\mathbf{Q}}_{b}^{H} \overline{\mathbf{Q}}_{b}^{H} \overline{\mathbf{Q}}_{b}^{H}\right]$$

$$= \left[\mathbf{I} - \overline{\mathbf{Q}}_{b} \overline{\mathbf{R}}_{b} (\overline{\mathbf{R}}_{b}^{H} \mathbf{I} \overline{\mathbf{R}}_{b}^{H})^{-1} \overline{\mathbf{R}}_{b}^{H} \overline{\mathbf{Q}}_{b}^{H}\right]$$

$$= \left[\mathbf{I} - \overline{\mathbf{Q}}_{b} \overline{\mathbf{R}}_{b}^{T} (\overline{\mathbf{R}}_{b}^{H})^{-1} \overline{\mathbf{R}}_{b}^{H} \overline{\mathbf{Q}}_{b}^{H}\right]$$

$$= \left[\mathbf{I} - \overline{\mathbf{Q}}_{b} \cdot \overline{\mathbf{Q}}_{b}^{H}\right]$$

(4)

여기서, Qb과 Rb는 각각 4x2와 2x2 행렬이며, Hb를 QR분해 한 결과이다. QR 분해를 위한 알고리듬은 크게 Householder reflection (HR), givens rotation (GR), modified Gram-Schmidt (MGS) 알고리듬이 있으며, 각각의 알고리듬이 갖는 연산 복잡도와 처리 지연은 모두 다르다 [7-8]. QR분해의 처리지연 시간과 복잡도를 생각했을 때, 채널 전처리기에 적합한 QR 분해 방법은 modified Gram-Schmidt 방식이 적합하다.

## 3-3 로그 수체계 시스템을 이용한 채널 전처리 알고리듬

수식 (4)에서 볼 수 있듯이, QR 분해 방법을 사용하면 복잡도를 크게 감소시킬 수 있지만, 여전히 많은 수의 행렬 곱과 나눗셈 연산이 존재하게 된다. 제안된 채널 전처리기는 이에 로그 수 체계 시스템을 사용하여 곱과 나눗셈 연산을 가산과 감산 연산으로 변경하여 수행함으로써, 복잡도를 다시 한번 줄일 수있다 [9-10]. 로그 수체계와 2진 수체계간의 변환은 근사화 과정을 통해 연산을 할 수 있다 [11].

### Ⅳ. 제안된 채널 전처리기 하드웨어 구조

본 장에서는 4x4 MIMO 시스템에서 복잡도를 줄이기 위해 채널의 dimension을 줄이는 기능을 수행하

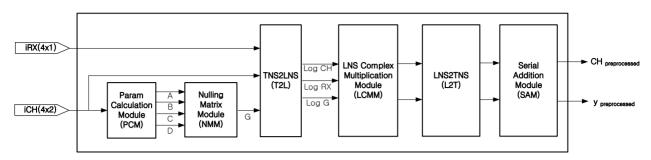

그림 2. 제안된 4x4 MIMO 채널 전처리기의 구조

Fig. 2. Block diagram of the proposed channel preprocessor for 4x4 MIMO system.

는 채널 전처리기의 하드웨어 구조를 제안한다.

4x4 채널 전처리기는 2번의 채널 전처리 과정을 통해 2개의 전처리된 4x2 채널 행렬과 4x1 수신 벡터를 구하게 되는데, 이를 모두 구현하려면, 하드웨어 복잡도가 매우 커 효율적이지 못할 뿐 아니라, 전체시스템의 하드웨어 구현에도 큰 부담이 된다. 이에 채널 입력을 스위칭하는 방법을 이용하여, 하나의 전처리 연산을 구현함으로써 하드웨어 복잡도를 줄일수 있는 하드웨어 구조를 제안한다.

그림 2는 제안된 4x4 MIMO 채널 전처리기의 하드 웨어 구조를 도시하며, 표 1은 본 논문에서 제안하는 4x4 MIMO 채널 전처리기의 알고리듬 과정을 정리한 것이다. 제안된 MIMO 채널 전처리기의 구조는 parameter calculation module (PCM), nulling matrix module (NMM), two's complement number system to logarithm number system converter (T2L), logarithm number system complex multiplication module (LCMM), logarithm number system to two's complement number system converter (L2T), serial addition module (SAM) 등의 블록으로 구성된다.

제안된 채널 전처리기는 연산량을 줄이기 위해 나 눗셈 연산이나 행렬의 곱셈 연산같이 복잡도가 높은 블럭을 로그 수체계에서 처리하고, 덧셈이나 복잡도 가 낮은 연산을 2의 보수 체계에서 처리하게 되는데, PCM, NMM, T2L, SAM이 2의 보수 수체계의 연산블 록에 해당되고, LCMM과 L2T가 로그 수체계 연산블 록에 해당된다.

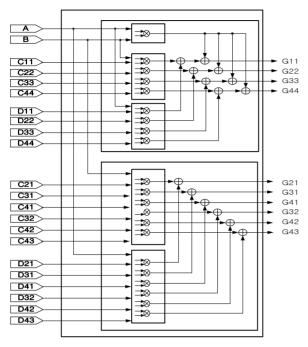

그림 3은 PCM의 블록도를 나타낸다. PCM은 입력

그림 3. PCM (Parameter Calculation Module)의 구조 Fig. 3. Block diagram of PCM (Parameter Calculation Module).

| 표 1. 제연 | 된 4x4 MIMO 채널 전처리기의 알고리듬의 단계                                    |    |

|---------|-----------------------------------------------------------------|----|

| Table 1 | Algorithmic Step for the proposed 4x4 MIMO Channel Preprocessor | ٦r |

| 단계  | 세부 블록              | 동 작                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                      |

|-----|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 1   | PCM                | $D_{11} = \ h_{11}\ ^{2}$ $D_{22} = \ h_{22}\ ^{2}$ $D_{31} = h_{31} \cdot h_{11}^{*}$ $D_{33} = \ h_{33}\ ^{2}  \vdots$ $D_{44} = \ h_{44}\ ^{2}$ $D_{43} = h_{41} \cdot h_{31}^{*}$ $B = D_{11} + D_{22} + D_{33} + A$ $A = C_{11} + C_{22} + C_{33} + C$                                                                                                                                                                | $C_1 = Bh_{14} - \mathbf{h}_3 \ \mathbf{h}_4 h_{13}$ $C_2 = Bh_{24} - \mathbf{h}_3^H \mathbf{h}_4 h_{23}$ $C_3 = Bh_{34} - \mathbf{h}_3^H \mathbf{h}_4 h_{33}$ $C_4 = Bh_{44} - \mathbf{h}_3^H \mathbf{h}_4 h_{43}$ $C_{44}$ $C_{44}$                                                                                                                                                           |                                                                                                                                      |

| 2   | NMM                | $\mathbf{G} = \begin{bmatrix} -\frac{D_{21}}{B^2} - \frac{C_{21}}{A^2} \\ -\frac{D_{31}}{B^2} - \frac{C_{31}}{A^2} \end{bmatrix}$                                                                                                                                                                                                                                                                                          | $ \frac{1}{B^2} - \frac{D_{21}^*}{B^2} - \frac{C_1 C_2^*}{A^2} - \frac{D_{31}^*}{B^2} - \frac{C_{31}^*}{A^2} \\ - 1 - \frac{D_{22}}{B^2} - \frac{C_{22}}{A^2} - \frac{D_{32}^*}{B^2} - \frac{C_{32}^*}{A^2} \\ - \frac{D_{32}}{B^2} - \frac{C_{32}}{A^2} - 1 - \frac{D_{33}}{B^2} - \frac{C_{33}}{A^2} \\ - \frac{D_{42}}{B^2} - \frac{C_{42}}{A^2} - \frac{D_{43}}{B^2} - \frac{C_{43}}{A^2} $ | $-\frac{D_{42}^{*}}{B^{2}} - \frac{C_{42}^{*}}{A^{2}} - \frac{D_{43}^{*}}{A^{2}} - \frac{C_{43}^{*}}{A^{2}}$                         |

| 3~5 | $\log_2(h_{21})$ : | $3 : T2L$ $\log_{2}(Rx0)  \log_{2}(g_{11})$ $\log_{2}(Rx1)  \log_{2}(g_{21})$ $\vdots \qquad \vdots$ $\log_{2}(Rx3)  \log_{2}(g_{44})$                                                                                                                                                                                                                                                                                     | $4 : LCMM$ $\log_{2}(g_{11}) + \log_{2}(h_{11})$ $\log_{2}(g_{21}) + \log_{2}(h_{11})$ $\vdots$ $\log_{2}(g_{44}) + \log_{2}(h_{42})$                                                                                                                                                                                                                                                           | $5 : L2T$ $2^{\log_2(g_{11}) + \log_2(h_{11})}$ $2^{\log_2(g_{21}) + \log_2(h_{11})}$ $\vdots$ $2^{\log_2(g_{44}) + \log_2(h_{42})}$ |

| 6   | SAM                | $2^{\log_{2}(g_{11}) + \log_{2}(h_{11})} + 2^{\log_{2}(g_{12}) + \log_{2}(h_{21})} + \dots + 2^{\log_{2}(g_{14}) + \log_{2}(h_{41})}$ $2^{\log_{2}(g_{21}) + \log_{2}(h_{11})} + 2^{\log_{2}(g_{22}) + \log_{2}(h_{21})} + \dots + 2^{\log_{2}(g_{24}) + \log_{2}(h_{41})}$ $\vdots$ $2^{\log_{2}(g_{41}) + \log_{2}(h_{11})} + 2^{\log_{2}(g_{42}) + \log_{2}(h_{21})} + \dots + 2^{\log_{2}(g_{44}) + \log_{2}(h_{41})}$ |                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                      |

으로 들어오는 4x2 채널 행렬 H=[h1 h2]을 이용하여 복소수 곱셈과 놈 연산, 덧셈 과정을 통하여 10개의 파라미터 C와 D를 구하고, 다시 C와 D 값을 이용하여 파라미터 A와 B를 계산한다. PCM 블록은 표 1과 같은 연산을 통해 GIS 행렬을 만들기 위한 파라미터를 계산한다. 그림 4는 NMM의 블록도를 나타낸다. NMM은 앞서 PCM에서 출력된 각각의 파라미터를 이용하여 GIS 행렬 G의 값을 연산한다.

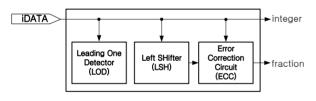

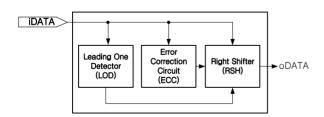

그림 5는 T2L의 블록도를 도시하였다. T2L는 입력으로 들어오는 채널행렬, 수신벡터 그리고 GIS 행렬의 항들을 2의 보수 수체계에서 로그 수체계로 바꾸는 작업을 하다. 먼저 입력 데이터의 최상위 1의 위치

를 찾아서 integer값을 결정하고, 최상위 1의 오른쪽에 위치한 비트를 소수점 왼쪽으로 shift하고, 그 소수 값에 따라 로그 변환시에 생기는 오차를 보상하여 fraction 값을 출력하게 된다. LCMM은 행렬 G와 입력 려 채널행렬의 복소수 곱셈 연산과 행렬 G와 입력 수 신벡터의 복소수 곱셈 연산과정에서 곱셈 연산을 로그 수체계의 덧셈 연산을 통해 수행한다. 그림 6은 L2T를 나타낸다. L2T는 곱셈 연산 된 채널 행렬과 수신벡터 값을 다시 2의 보수 수체계로 다시 변환시키는데, 최상위 1의 오른쪽의 비트열을 사용하여 변환시에 생기는 오차를 연산하고, 최상위 1의 위치에 따라 오른쪽으로 하위비트를 붙여서 2의 보수로 변환시

킨다. SAM에서는 2의 보수 수체계로 바뀐 값을 입력으로 하여 덧셈 연산을 통해 전처리 된 채널 행렬과수신벡터를 최종적으로 출력하게 된다.

그림 4. NMM의 구조 Fig. 4. Block diagram of NMM.

그림 5. T2L의 구조 Fig. 5. Block diagram of T2L.

그림 6. L2T의 구조 Fig. 6. Block diagram of L2T.

# V. 제안된 채널 전처리기의 설계 및 구현 결과

제안된 채널 전처리기 구조는 QR분해와 LNS를 사용하여 전처리 연산과정에서 생기는 역행렬연산, 행렬 간 곱셈과 나눗셈연산을 단순화시킴으로써 하드웨어 복잡도를 크게 감소시켰다. 4x4 MIMO 기반 심볼검출기의 제안된 하드웨어 구조는 Verilog-HDL을 이용하여 설계되었고, 0.13µm CMOS 규격 셀 라이브러리를 사용하여 합성하였다. 합성 결과, 제안된 채널전처리기는 약 622K 논리 게이트로 합성됨을 확인하였다. 제안된 채널 전처리기의 구조가 복잡도 면에서효율적이라는 것을 검증하기 위해, 표 2와 같이 채널전처리 연산을 2의 보수 수체계로 모든 블록을 설계하여 각 블록 별로 합성된 결과와 로그수체계로 설계하여 gate count를 통해 하드웨어 복잡도를 비교하였다.

표 2. 수체계에 따른 채널 전처리 연산 복잡도 비교 Table 2. Comparison results of the channel preprocessor complexity for the number system

| ,   | 채널 전처리 연산    | Gate counts |  |

|-----|--------------|-------------|--|

|     | Parameter 연산 | 169.6 K     |  |

| TNS | G 행렬 연산      | 52.9 K      |  |

|     | 전처리된 채널 행렬   |             |  |

| 기반  | 및 수신 벡터 연산   | 556.5 K     |  |

|     | 합계           | 779.1 K     |  |

|     | Parameter 연산 | 169.6 K     |  |

| 제안  | G 행렬 연산      | 52.9 K      |  |

| 된   | 전처리된 채널 행렬   | 200.4.17    |  |

| 구조  | 및 수신 벡터 연산   | 399.4 K     |  |

|     | 합계           | 621.9 K     |  |

### VI. 결 론

본 논문은 4x4 MIMO 기반 다중 안테나 시스템을 위한 효율적인 채널 전처리기 구조를 제안하고 하드웨어로 구현 및 검증하였다. 제안된 QR과 로그 수체계 방법을 통해 채널 전처리 과정에서 가장 큰 비중을 차지하는 행렬 간 곱과 나눗셈 연산을 단순화시킴으로써, 복잡도를 크게 낮추었다. 4x4 MIMO 채널 전처리기는 채널의 dimension을 축소함으로써 복잡도를 낮추는데 꼭 필요한 프로세서이므로, 제안된 채널 전처리기는 MIMO 시스템의 하드웨어 복잡도를 줄이는

데 큰 공헌을 할 수 있을 것으로 예상된다.

### 감사의 글

본 논문은 2010년 정부(교육과학기술부)의 재원으로 한국연구재단의 지원(2009-0071983)과 삼성탈레스 (주)의 재원으로 지원을 받아 수행되었고, CAD Tool은 IDEC으로부터 지원받았음.

### 참 고 문 헌

- [1] A. F. Naguib, N. Seshadri, and A. R. Calderbank, "Increasing data rate over wireless channel," *IEEE Signal Process. Mag.*, vol. 17, no. 2, pp. 744-765, Mar. 1998.

- [2] H. Sampath, S. Talwar, J. Tellado, V. Erceg, and A. Paulraj, "A fourth-generation MIMO -OFDM: broadband wireless system: Design, performance, and field trial results," *IEEE Commun. Mag.*, vol. 40, no. 9, pp. 143-149, Sept. 2002.

- [3] A.van Zelst, Tim C. W. Schenk, "Implementation of a MIMO OFDM-Based wireless LAN system," *IEEE Trans. Signal Process*, vol. 52, no. 2, pp. 483-494, Feb. 2004.

- [4] G. L. Stuber, J. R. Barry, S. W. McLaughlin, Y. Li, M. A. Ingram, and T. H. Pratt, "Broadband MIMO-OFDM wireless communications," *Proc. IEEE*, vol. 92, no. 2, pp. 271-297, Feb. 2004.

- [5] C. Huang, C. Yu, and H. Ma, "A Power-Efficient Configurable Low Complexity MIMO Detector," *IEEE Trans. Circuits Syst. I*, vol. 56, no. 2, pp. 485-496, Feb. 2009.

- [6] M.K. Abdul Aziz, P.N. Fletcher and A.R. Nix, "A Study of Performance and Complexity for IEEE 802.11n MIMO-OFDM GIS Solutions", Communications, 2004 IEEE International Conference, vol. 7, pp. 3822-3826, June. 2004.

- [7] Howard A. Anton and Robert C. Busby, "Contemporary Linear Algebra," *Wiley, Press*, 2002.

- [8] G. Strang, "Introduction to Linear Algebra,"

Wellesley-Cambridge, Press, 2003.

- [9] Y. Wang, H.M. Lam, C.Y. Tsui, R.S. Cheng, W.H. Mow, "Low complexity OFDM receiver using Log-FFT for coded OFDM system", *IEEE ISCAS*, vol 3, 445-448. 2002

- [10] Swartzlander E.E. Jr., Satish Chandra. D.V, Nagle Jr. H.T, Starks. S. A, "Sign/Logarithm Arithmetic for FFT Implementation", *IEEE*, *Trans. Comput.*, pp. 5236-534, June 1983.

- [11] 김채현, 송유수, 김종환, 신경욱, "휴대형 3D 그래 픽 가속기용 로그 수체계 기반의 누승기 설계", *대* 한전자공학회 하계학술대회 논문집, Jun. 2005

### 황 유 선 (黃裕善)

2009년 2월 : 한국항공대학교 항공전자 및 정보통신공학부 졸업. 2009년 3월~현재 : 한국항공대학교 항공전자 및 전자공학과 석사 과정 관심분야 : 무선 통신 시스템용 모뎀 프로세서의 알고리듬 및 SoC 설계

### 장 수 현 (張秀玄)

2009년 2월 : 한국항공대학교 항공전자 및 정보통신공학부 졸업. 2009년 3월~현재 : 한국항공대학교 항공전자 및 전자공학과 석사 과정 관심분야 : 무선 통신 시스템용 모뎀 프로세서의 알고리듬 및 SoC 설계

### 한 철 희 (韓哲熙)

1997년 중앙대 전자공학과 학사 졸업. 1999년 연세대 전자공학과 석사 졸업. 2007년 연세대 전기전자공학과 박사 졸업. 2006년~2007년 삼성탈레스 선임 연구원 2007년~현재 삼성탈레스 전문연구원 관심분야: 무선 통신 시스템용 모뎀 알고리듬 개발 및 구현 적응 디지털 신호처리

### 최 성 남 (崔星男)

1992년 아주대학교 전자공학과 학사 졸업. 1992년 DASHsystem 입사 . 1995년 삼성전자 입사 1997년~2001년 삼성탈레스 선임연구원 2002년~현재 삼성탈레스 전문연구원 관심분야 : 무선 통신 시스템 설계, 영상신호처리

### 정 윤 호 (丁胤豪)

1998년 2월 : 연세대학교 전자공학과졸업 2000년 8월 : 연세대학교 전기컴퓨터 공학과 졸업

2005년 8월 : 연세대학교 전기전자

공학과 졸업

2005년~2007년 : 삼성전자 통신연구소

책임연구원

2007년~2008년 : 연세대학교 전자공학과 연구교수 2008년~현재 : 한국항공대학교 항공전자 및 정보통신공학부

조교수

관심분야 : 무선 통신 시스템용 모뎀 프로세서의 알고리듬

및 SoC 설계