### 論文

# ROM 데이터 추출을 통한 결함검출 시스템

정종구\*, 지민석\*, 홍교영\*, 안동만\*, 홍승범\*

## Fault Detection System by the Extracting the ROM's Data

JongGu Jeong\*, Min Seok Jie\*, Gyo Young Hong\*, Dong-Man Ahn\*, Seung-Beom Hong\*

#### **ABSTRACT**

Generally, the digital circuit card can be tested by automatic test equipment using LASAR(Logic Automated Stimulus and Response). This paper proposes the ROM data extracting algorithm which can test the digital circuit card that consists usually ROMs. We are implemented of the proposed fault detecting program by LabWindow/CVI 8.5 and the digital automatic test instrument with NI-VXI(National Instrument – Versa Bus Modular Europe eXtentions for Instrumentation) card. We also make an interface circuit board connecting the digital test instrument and the digital circuit card. It shows the good performance of getting the data from ROMs.

**Key Words :** Fault Detection(결함 검출), ROM data(롬 데이터), LASAR, LabWindow/CVI, NI-VXI.

#### 1. 서 론

최근 디지털 제품에 임베디드 소프트웨어 또는 내장형 소프트웨어가 내장되어 소형화, 첨단화, 그리고 정밀화되어지고 있다. 또한 하드웨어의 품질보증을 중시하기보다 소프트웨어의 비중이 점차적으로 증가되고 있고, 하드웨어보다 소프트웨어의 오류로 인한 신뢰성 문제에 평가 비중이 확대되고 있다. 더불어 하드웨어의 결함은별도의 결함을 검출하는 오류분석시스템을 장착하여 결함 검출 시스템이 간소화되고 있다[1-2].

1990년대에 도입된 디지털 장비의 경우, 회로 카드에 대한 결함 검출은 실제 환경을 구현한 상 태의 목업(Mock-up)을 이용하여 회로 카드를 정 비하던 수동방식에서 스티뮬러스(Stimulus)와 측 정 기능을 토대로 만든 자동 시험장비로 정비하고 있는 자동방식 추세로 발전하였다. 이런 자동시험장비는 국외에서 도입된 경우 장비와 동시에 정비 및 점검을 위해 자동시험장비를 도입하는 것이 관례이다. 하지만 자동시험장비의 구성품에 대한 제작사 생산 중단과 유지보수의 기간이 만료로 인한 시험장비 기술지원의 중단으로 운용유지보수의 어려움을 겪고 있는 현실이다.

새롭게 도입된 자동시험장비의 경우, 하드웨어와 소프트웨어가 서로 상이하여 이전 디지털 장비들에 적용하기 어렵다. 기존의 시험장비의 경우, 노후화, 기술 지원 중단 및 해당 장비의 운용소스 코드 미공개로 인해 해당 장비의 업그레이드 시 어려움이 증가되고 있다. 이미 도입된 장비의 수명 연장이나 성능개량 시 필요한 소자의단종에 따른 회로 카드 개조가 어렵고 대체 소자에 따른 회로 카드의 변경이 발생하게 되어 기존의 자동시험장비의 시험프로그램 적용이 불가능하다. 그래서 특정시험장비에 의존한 자동시험장비보다 보편화된 자동시험장비개발에 많은 연구가 진행되고 있다.

미국의 경우 도입 후 20~30년 이상 된 자동

연락저자, E-mail : sbhong@hanseo.ac.kr 충남 태안군 남면 신온리 한서대학교 태안비행장

<sup>2011</sup>년 11월 22일 접수 ~ 2011년 12월 8일 심사완료 \* 한서대학교 항공전자공학과

시험장비가 증가되어 해당 장비구성품의 하드웨어 단종과 소프트웨어의 노후화로 인해 운용유지에 따른 문제점이 대두되어 기존의 시험프로그램도 이용 가능하도록 자동시험장비에 대한 표준화작업이 진행되고 있다. 또한 자동화검사체계를 구성하고 있는 장비에 대해 상용통합형 계측기개발 및 적용으로 소형화와 표준화의 추세이며, 자동화검사체계에서 사용하는 하드웨어 및 소프트웨어는 점차 상용 툴을 적용하고 있다[1].

특히 미국에서 도입된 장비 중 ROM 디지털 회로 카드의 경우, 회사의 중요한 데이터가 포함되었거나 알고리즘 등이 포함되어 있어 ROM의데이터를 복사하지 못하도록 락(Lock)를 설치하거나 상용화된 ROM를 사용하지 않는 경우 다른 ROM으로 대체하지 못하도록 한다. 따라서ROM 디지털 회로카드의 경우 결함이 발생하거나 ROM 칩 잘못되었는지를 파악하기 어려운 문제점이 있다.

대표적인 자동시험장비로 Teradyne사의 LASAR (Logic Automated Stimulus and Response) [3-5] 오류 검출 프로그램을 사용하고 있다. LASAR 프로그램은 넷 리스트(net list)를 이용, 주 입력 (primary inputs) 부분에 패턴을 인가하면서 시 뮬레이션을 통해 결함 사전을 만들어 결함 검출 율를 높이는 방법으로 만들어진다. 하지만, LASAR 방식은 해당 회로카드에 대한 소자들의 라이브러리가 있어야 한다는 점과 결함검출(fault detect)을 위한 패턴 생성에 대한 많은 노력이 필 요한 단점이 있다. 이런 문제점으로 인해 본 논 문에서는 회로소자들의 라이브러리나 각 회로소 자를 연결한 넷 리스트 없이 ROM 특성을 이용 하여 결함을 파악하는 방식을 제안한다. ROM 디지털 회로 카드에 직접 전원을 공급하여 ROM 데이터를 어드레스 별로 데이터를 입력한 후 자 동 시험 장비(NI-VXI channel card)를 통하여 알 려지지 않은 ROM 데이터가 동작 후의 결과 데 이터를 양품 데이터와 비교하므로 ROM의 결함 여부를 판별하는 방식이다.

본 논문은 기존의 오류 검출 기법과 본 논문에서 제안한 오류 검출 기법을 설명하며 실험을 수행하여 성능을 검사하여 결론을 도출하였다.

#### 2. 기존 오류 검출 기법

## 2.1 결함 모델

회로 카드에 대한 결함을 검출하고자 할 때에

결함을 고찰하는 방법이 중요한 문제가 된다. 예를 들어, 회로카드의 노후화로 인해 부품의 연결이 단락되거나 부식되었을 경우와 같이 육안으로 식별이 가능한 결함에 대해서는 쉽게 결함에 대한 해결이 가능하다. 그러나 내부 선로의 단선이나 단락또는 부품 불량을 육안으로 식별하는 것은 불가능하여 기능적인 시험으로만 결함을 판정할 때에는 회로 카드 점검에 많은 어려움이 예상된다.

이를 해결하기 위해 논리 레벨에서의 결함 모델을 사용하는 것이 실제 회로나 소자내 많은 물리적 결함을 포괄하여 고찰 할 수 있으며 결함테스트도 간단해진다. 이렇게 하여 공통적으로모형화된 결함이 고착 결함 모델(Stuck-at fault model)이다.

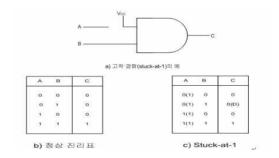

고착 결함 모델은 결함을 판별하는 결함 모델로써 널리 사용되고 있다. Fig. 1에서 보듯이 실제 회로의 물리적 결함이 결과적으로 회로의 논리 레벨에서 신호선이 영구적으로 논리값 0(Stuck-at-0)이나 1(Stuck-at-1)을 갖도록 하여 고장을 검출하는 모델이다. 따라서 게이트의 논리값이 A 입력부분의 논리값 stuck-at-0 이나 Stuck-at-1으로 인해 출력이 변화되지 않는 결함을 가져온다[6-7].

고착 결함 모델이 널리 쓰이는 이유는 UUT(unit under test)의 결함 분석 문제가 실제 회로의 물리적 문제가 아니라 논리적 문제가 됨으로써 서로 다른 많은 물리적 결함들이 하나의 고착 결함으로 설명이 가능하기 때문이다.

Fig. 1 고착 결함 모델

## 2.2 LASAR 오류 검출

LASAR는 전자 그리고 통신 분야 등에서 FPGA/ASIC 그리고 디지털 소자 등의 자동 오류 검출 장비와 소프트웨어를 개발한 Teradyne 사의 오류 검출 프로그램이다. LASAR는 복잡한 디지털 회로에 대하여 고품질의 기능적인 시험 프로그램을 만들기 위해 설계된 LASAR 6.6버전의 프로그램은 Sun 워크스테이션을 이용하여 회

로카드를 수리한다[3-5].

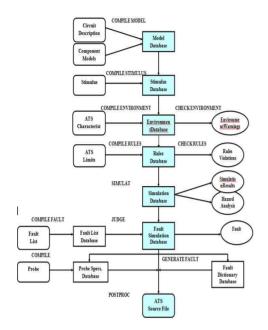

LASAR의 오류 검출 방법은 두 가지 형식의 전단 데이터인 결함 사전 데이터와 지시 프로브 데이터(Guided Probe data)를 생성하여 결함 고착모델을 검출한다. 시뮬레이션 생성 절차는 Fig. 2와 같은 방법에 기반을 두어 만들어진다.

Fig. 2 시험 프로그램 생성 절차

LASAR의 결함 고착 모델을 검출하기 위한 생성 절차를 살펴보면 다음과 같다. 첫째 단계는모델 데이터베이스(Model Database)를 생성하는단계로 회로 설명(Circuit Descriptor)와 부품 모델(Component Models)를 정의한다. 디지털 회로카드의 사용 소자에 대한 모델 정의와 입/출력및 내부 연결 상태를 텍스트 파일에 정의하여 모델을 구현한다. 이 과정을 통해 시뮬레이션 프로그램은 회로카드에 대한 연결 상태 및 소자에 대한 특성(타이밍 정보와 전압 레벨)에 대한 기본적인 정보를 인식한다.

둘째 단계는 모델에 대한 컴파일(Compile)스 티뮬러스 단계이다. 디지털 회로 카드의 특성에 맞게 논리 레벨을 이용하여 패턴을 인가한다.

세 번째 단계는 컴파일 환경 설정 단계로 ATS(Automatic Test program Set) 자동 시험 장비와의 실제 경로 매칭을 하는 단계이다.

네 번째 단계는 오류 검출을 위한 패턴 룰 (Rule) 입력과 결함 검출 판단을 위한 시뮬레이션하는 단계이다. 이 단계에서 해당 입력 패턴을

IC 개별 소자의 내부까지 결함을 추출하는 게이트 레벨(Gate Level)이나 IC 개별 소자 단위의 프리미티브 레벨(Primitive Level)에 맞게 결함 사전을 생성한다. 각 입력 패턴에 따라 생성된 결함 사전을 바탕으로 고착 결함을 검출하는 단계로서 패턴 인가 및 결함 검출 판단(Judge)하는 단계를 반복하여 게이트 레벨에서 결함 검출율이 95%이상 되도록 한다. 결함 사전의 경우, 다양한 패턴을 발생시켜 결함을 가상으로 검출된 데이터로 구성된다.

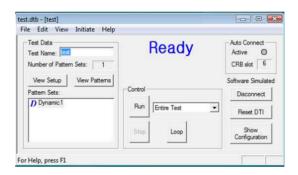

다섯 번째 단계로 결함 목록에 따른 결함 부위를 프로브(Probe)하기 위한 데이터를 생성하는 단계로 회로카드의 불량부분을 자동 지시할 있도록 지시 프로프 데이터를 생성한다. 마지막 단계로 자동 시험장비에서 사용 가능한 프로그램을 만드는 과정이다. 이 과정을 통해 생성된 프로그램은 실제적으로 Fig. 3의 디지털 시험장비 패널을 이용하여 자동 시험 장비에서 디지털 회로 카드에 대한 기능 점검이 가능하게 된다.

Fig. 3 디지털 시험장비 패널

하지만, LASAR의 경우 디지털 회로카드 조립체의 고착 결함 탐지를 위해 회로카드를 구성하고 있는 각각의 부품들에 대한 라이브러리가 존재해야 한다. 또한 고착 결함 모델을 기반으로고장 유무를 판단하는 95%이상의 게이트 레벨결함 탐지율을 높이기 위해 패턴 형성에 많은 시간과 노련을 들여야 하는 단점이 있다.

#### 3. ROM 오류 검출 시스템

## 3.1 시스템 개요

본 논문에서는 ROM에 저장된 데이터는 손상 하지 않고, 외부 인터페이스 보드를 통해 ROM 회로카드에 입력 패턴 데이터를 인가한다. ROM 회로카드가 동작한 후 ROM으로부터 얻은 출력 데이터를 양품 데이터와 검사하므로 ROM의 오 류나 회로카드의 오류를 검사하게 된다.

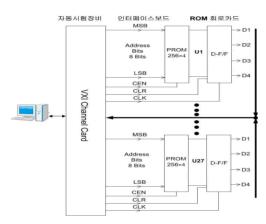

Fig. 4와 같이 전체 오류검출 시스템은 자동시험 장비(NI-VXI<sup>1</sup>) channel card)에서 시험 ROM회로카드에 클럭(CLK)과 테스트 패턴 데이터를 인가하여 회로카드 출력 데이터를 자동시험장비로 불러 들여 결함유무를 검사하는 방법이다.

따라서 ROM 디지털 회로와 자동시험장비를 연결하기 위한 인터페이스 보드를 제작하였다. 인 터페이스 보드의 형태는 각 비트별 데이터를 입력 포트와 각 ROM 데이터를 동작하기 위한 클릭과 클리어(CLR) 신호를 통하여 RPOM를 검사하여 16진 데이터 파일(Hex Data File) 형태로 자동 시 험 장비로 값을 전달하도록 구성하였다.

최종 결함 유무의 판정은 입력패턴에 따른 양품 데이터와 출력 결과 핵사 데이터 파일을 비교하여 회로카드 전체 또는 일부 ROM에 대해 결합 유무를 판단하여 결합 여부를 판정한다.

Fig. 4 시스템 구성도

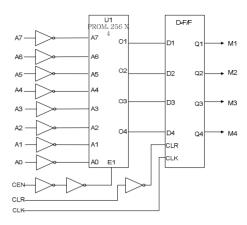

#### 3.2 인터페이스 보드

Fig. 5는 ROM 디지털 회로 카드를 구성하는 각 ROM 연결 형태이다. 따라서 자동시험장비에서 채널카드를 사용하는 자동시험장비와 회로카드와의 인터페이스를 위한 각 입출력 포트를 Fig. 5와 동일하게 인터페이스 보드(interface board)를 제작하였다. 이는 자동시험장비의 채널과 회로카드와의 인터페이스를 위해 1:1 매칭을이루고 있다. 회로카드의 출력에 풀업 저항이나

풀다운 저항은 자동시험장비의 채널카드에서 제 공 가능하므로 고려하지 않았다.

Fig. 5 ROM 디지털 회로 카드

ROM 디지털 회로카드에 스티뮬러스를 제공하 거나 출력되는 데이터를 자동시험장비에서 측정 가능하도록 회로카드의 입력과 출력 부분에 대한 라인을 모두 고려하여 Fig. 6과 같이 제작하였다.

Fig. 6 인터페이스 보드 회로도

회로카드와 시험 장비의 채널 사이에 1:1 매칭으로 연결하여 자동 시험 장비의 메모리로 전달하게 된다. 각 ROM 회로 카드의 상이한 PROM 형태의 데이터를 인터페이스 보드를 통하여 자동시험 장비로 연결하게 된다.

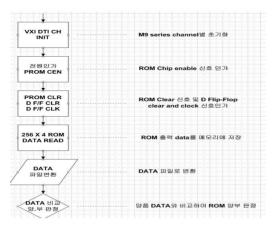

## 3.3 오류 검출용 알고리즘

시험 프로그램 코드는 C언어 기반의 Lab Windows CVI 8.5와 VXI Library를 이용하여 작성하였으며 프로그램에 대한 알고리즘은 Fig. 7과 같은 순서로 구성하였다.

<sup>1)</sup> NI-VXI : National Instrument사에서 개발된 Versa Bus Modular Europe eXtentions for Instrumentation로 모듈형 자동 계측 장비임.

Fig. 7 오류 검출 프로그램 알고리즘

LabWindows CVI 8.5 프로그램에서 테러다인 사의 자동 시험 장비(VXI 채널 카드)를 컨트롤하는 VXI 라이브러리(Library) 함수를 이용하여 ROM 데이터 검증 프로그램을 작성하였다. 시험 프로그램은 ROM에 내장된 데이터만을 추출하므로 기능시험을 위한 패턴 생성은 불필요하지만 ROM 자체적으로 동작하게 하는 최소한의 패턴 만에 대해서 VXI Library 함수를 이용하여 인가한다.

시험 프로그램 알고리즘은 다음과 같은 단계로 수행한다. 첫 번째 단계로 자동 시험 장비를 초기화 하는 단계로 각 VXI 채널을 초기화한다.

두 번째 단계로 ROM 칩에 동작 신호를 인가한다. 또한, PROM과 플립플롭이 동작 가능하도록 ROM의 Chip Enable과 D F/F Clear 신호 및 D F/F Clock 패턴을 인가한 상태이다.

셋 번째 단계로 ROM 메모리의 256번지까지 어드레스만 변경하여 인가되는 주소 값에 따라 출력되는 4비트 출력값이 자동 시험 장비의 VXI 채널의 RAM에 저장 된다.

네 번째 단계로 자동 시험 장비의 RAM에 저장된 데이터를 반복문을 사용하여 어드레스별 데이터를 읽어 들여 C프로그램의 메모리상에 저장시킨다.

마지막 단계로 이 데이터를 다시 2진 텍스트 파일로 만들어 양품의 ROM 데이터와 비교 데이 터 무결성을 검증하여 불량을 검출하는 방식이다.

양품의 ROM인 경우 양품의 ROM 패턴과 동일한 형태의 결과가 출력되지만, 오류가 존재할 경우 출력 값이 0xFF 값으로 출력하게 되어 정확히 어떤 ROM에서 오류가 발생했는지를 판정할 수 있다.

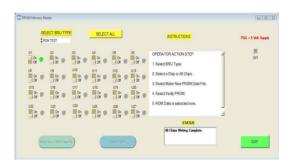

### 4. 실험 및 검토

자동 시험 장비는 NI-VXI Channel 카드가 장 착된 자동시험장비와 채널 카드, 시험 대상 ROM 회로카드와의 인터페이스를 위해 제작한 연결 인터페이스 보드, 그리고 제어용 PC를 이 용하여 실험하였다.

시험 방법은 인터페이스 보드에 점검하고자하는 ROM 디지털 회로카드를 장착한다. ROM 디지털 회로카드는 모두 27개의 ROM 칩들로 구성되어있다. 여기서 각 ROM은 U1 ~ U27로 명명한다.

시험하고자 하는 ROM 버튼을 선택하여 실행 시키면 선택된 기능 즉 전체적 또는 개별적인 ROM에 대해 점검을 시험 프로그램 알고리즘에 따라 수행한다.

Fig. 8 ROM 데이터 추출 패널

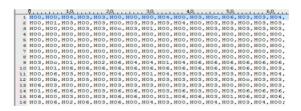

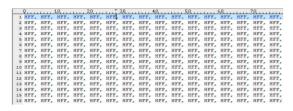

ROM 데이터 추출 프로그램을 이용하여 U1 ROM을 선택하여 시험을 실시하였다. Fig. 9는 U1 ROM의 양품 데이터이며, Fig. 10은 시험결과 불량 ROM 데이터를 추출한 결과이다. 선택된 ROM이 불량일 때는 최종적으로 데이터 추출패널에 LED버튼이 적색으로 지시되며 추출된 데이터는 텍스트 파일로 컴퓨터에 저장된다.

Fig. 9 양품 ROM 데이터

Fig. 10 불량 ROM 데이터

#### 5. 결 론

ROM 데이터를 검출하기 위한 프로그램은 LabWindows CVI 8.5내의 NI-VXI Channel 카드를 컨트롤 하는 VXI Library 함수들을 이용하여 구현하였다. ROM과 플립플롭으로 구성되어 있는 회로 카드를 사용하므로 LASAR로 인한 라이브러리가 불필요하다는 점과 결함 검출을 위한 패턴 인가에 대한 많은 노력이 필요한 점을 개선하였다. 본 논문에서 개발한 프로그램은 ROM의 기능적인 측면보다는 ROM에 있는 데이터만을 추출하여 데이터 무결성을 판단하여 회로카드의 양부를 판정하게 된다.

IC 소자들 중에 미공개된 ROM 데이터로 인하여 해당 소자에 대해 국내에서 사용하기 불편한 점이 있었으나 제안한 오류 검출 시스템을 통해 개발한 프로그램은 ROM 데이터 무결성을 검증 할 수도 있다. 그리고 ROM 데이터를 추출할수 있어 ROM 데이터 미공개로 인한 불편사항을 추가적으로 해소하였다. 향후에 회로카드내의 ROM 데이터를 WRITE하는 기능도 추가 개발할계획이며, 회로가 유사한 카드들에 대해서도 시험이 가능하도록 기능을 추가할 계획이다.

## 후 기

본 논문은 LIG 넥스원(주) 대학 협력 연구 지원사업(Y11-014) 실용형 민수무인항공기 운용체계 및 정보전송시스템 연구으로 수행된 연구되었습니다. 이에 감사드립니다.

## 참고문헌

- [1] 주간기술동향, "임베디드 S/W 산업 육성 정책 방향", 정보통신부 소프트웨어진홍과, 2003

- [2] http://news.mk.co.kr/newsRead.php? year=2011&no=672256

- [3] http://www.teradyne.com/atd/news/press Room/pressReleases/2000/05221997.html

- [4] Teradyne. Inc., M9-Series Digital Test Instrument Manual, 2007.

- [5] Teradyne, Inc., LASAR 6.60 Reference Manual, 1997.

- [6] 김지혜, "순차회로를 위한 효율적인 혼합 고 장 진단 알고리즘", 연세대학교 공학석사논문, 2003.

- [7] 정원창, "회로 분할 기법을 이용한 ATPG의 가속화", 연세대학교 공학석사논문, 1998.