# **Linearity-Distortion Analysis of GME-TRC MOSFET** for High Performance and Wireless Applications

Priyanka Malik\*, R.S. Gupta\*\*, Rishu Chaujar\*\*\*, and Mridula Gupta\*

Abstract—In this present paper, a comprehensive drain current model incorporating the effects of channel length modulation has been presented for multi-layered gate material engineered trapezoidal recessed channel (MLGME-TRC) MOSFET and the expression for linearity performance metrics, i.e. higher order transconductance coefficients:  $g_{m1}$ ,  $g_{m2}$ ,  $g_{m3}$ , and figure-of-merit (FOM) metrics;  $V_{IP2}$ ,  $V_{IP3}$ , IIP3 and 1-dB compression point, has been obtained. It is shown that, the incorporation of multi-layered architecture on gate material engineered trapezoidal recessed channel (GME-TRC) MOSFET leads to improved linearity performance in comparison to its conventional counterparts trapezoidal recessed channel (TRC) and rectangular recessed channel (RRC) MOSFETs, proving its efficiency for low-noise applications and future ULSI production. The impact of various structural parameters such as variation of work function, substrate doping and source/drain junction depth (X<sub>i</sub>) or negative junction depth (NJD) have been examined for GME-TRC MOSFET and compared its effectiveness with MLGME-TRC MOSFET. The results obtained from proposed model are verified with simulated and experimental results. A good agreement between the results is obtained, thus validating the model.

E-mail: mridula@south.du.ac.in

Index Terms—Corner effect, linearity, MLGME, RF, TRC MOSFET

#### I. INTRODUCTION

Recent explosion in the demand for mobile telecommunication, computing and multimedia applications has resulted in much interest in system on chip (SOC) applications based on all CMOS technologies due to their inherent low cost and high density. In sub-100 nm regime MOSFETs are the strong contenders for analogue RF applications in lucrative wireless communications market. Linearity assessment [1-3] is an important parameter in all RF systems which need to be tailored in order to ensure that the inter-modulation and high-order harmonics are minimal at the output. Although there are system level techniques to improve linearity, they all require complex circuitry [4]. A transistor-level linearization is more appropriate for power amplifiers in the portable systems, which requires an analysis of linearity behaviour at device level as a function of important design parameters.

The present work concentrates on the extensive study for various recessed channel structures, i.e. RRC, TRC, GME-TRC and MLGME-TRC MOSFETs, for different dielectric configurations to optimize the linearity performance by developing a model and validating it with experimental and simulation results. The Recessed channel (RC) MOSFET [5-7] structures are considered as potential candidates to suppress and overcome short channel effects (SCEs), punch-through and DIBL effects even at gate lengths down to the sub-100 nm regime because negative junctions can be fabricated without any increase in the series resistance and hence, for use in

Manuscript received May 5, 2011; revised Jul. 22, 2011.

<sup>\*</sup> Electronic Sciences, Delhi University, New Delhi, Delhi, India

<sup>\*\*</sup> Electronics & Communication Engineering, Maharaja Agrasen Institute of Technology, New Delhi, Delhi, India

<sup>\*\*\*</sup> Applied Physics, Delhi Technological University, New Delhi, Delhi, India

CMOS ULSI circuits. This is because the recessed channel MOSFETs carries concave device structure in which two potential barriers are formed at the corners due to high density of electric field lines, resulting in improvement of SCEs in terms of reduced punchthrough and drain induced barrier lowering (DIBL) effect. However, these barriers act as hurdle in the path of carriers, because carriers now require more energy to surmount the barriers, which limits its carrier transport efficiency and hence, current driving capabilities of the device. In case of trapezoidal recessed channel (TRC) MOSFET, the height of corner barriers is comparatively low as compared to rectangular recessed channel (RRC) MOSFET, which results in improved device speed and also SCEs suppression [7]. The amalgamation of GME architecture on TRC MOSFET further adds on the enhancement in carrier transport efficiency and reduction in SCEs, owing to the step in potential profile due to the gate electrodes of different metal work functions, i.e.  $\Phi_{M1}$  for metal M1 and  $\Phi_{M2}$  for metal M2; thus resulting in screening of channel region, under gate material M1, from drain potential variations [7]. This screening ensures the diminution in DIBL, enhanced carrier transport; reduced hot carrier effect and increased drain current and thus, shows the improved linearity performance as compared to conventional TRC and RRC MOSFETs.

Moreover, for deeply scaled MOS structures, the gate oxide thickness becomes one of the important scaling parameter. Leakage current and tunneling effects will become more prominent as thickness is scaled below 2 nm. The high-k films are anticipated to be a viable alternative [8]. However, these films results in high fringing electric field from gate into the source/drain regions thereby degrading the short channel performance [9-12] of the device. This limitation of high-k/SiO<sub>2</sub> system [13-14] can be overcome by using gate stack architecture consisting of a thin passivating layer of SiO<sub>2</sub> between bulk and high-k dielectric has been given extensive consideration. Thus, due to the negligible gate oxide leakages and increased carrier transport efficiency, MLGME-TRC MOSFET integrates the potential benefits of GME-TRC MOSFET in terms of high linearity and low distortion behaviour in comparison with conventional MOSFETs in terms of figure-of-merit (FOM) metrics: V<sub>IP2</sub>, V<sub>IP3</sub>, IIP3, 1-dB compression point and higher order transconductance coefficients: g<sub>m1</sub>, g<sub>m2</sub>, g<sub>m3</sub>, proving its efficiency for low-noise applications and future ULSI production. Further, to gain an insight into the effectiveness of the proposed design, the characteristics are investigated for different workfunction difference,  $X_j$ , dielectric constant ( $\epsilon_{ox2}$ ), and substrate doping ( $N_A$ ) in order to study the overall device performance. The results obtained from proposed model are also verified with simulated and experimental results. A good agreement between the results is obtained, thus validating the model.

## II. FABRICATION FEASIBILITY OF GME-TRC MOSFET

The MLGME-TRC MOSFET can be fabricated conveniently by using present fabrication technologies and lithographic resolutions. The fabrication of TRC structure is feasible by implementing the fabrication process used by Xiao-Hua et al [16] and Seo et al [17] for grooved gate MOSFET. Further, for GME architecture, many fabrication schemes has been suggested such as inter diffusion process [18, 19] and tilt angle evaporation (TAE) [20, 21] which makes the fabrication possible even in sub-100 nm regime. Moreover, for the viability of advanced multi-layered gate engineered structures, several techniques [22, 23] were reported in the past, using the stack of a thin SiO<sub>2</sub> and a thick high-k layer. Thus, with these presented fabrication feasibilities of individual grooved-gate MOSFET, multi-layered and GME architecture, the device fabrication probability of integrated MLGME-TRC MOSFET is enhanced and hence, with advanced lithographic considerations and techniques, its fabrication is possible, so new structure is proposed with its validation.

#### III. STRUCTURE DESCRIPTION

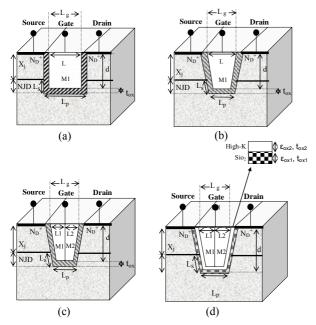

A schematic cross-sectional view of different recessed channel structures, i.e. MLGME-TRC, GME-TRC, TRC and RRC MOSFETs are shown in Figs. 1(a-d).

The effective channel length  $L_{eff}$  corresponds here to the metallurgical channel length, taken along the gate oxide, i.e.  $L_{eff}$ =(2 $L_s$ ) +  $L_p$  where,  $L_p$  is the planar part and  $L_s$  is the angular part of the channel. The substrate doping,  $N_A$ , is taken as 1 × 10<sup>17</sup> cm<sup>-3</sup> and source/drain region doping,  $N_D^+$ , is 1 × 10<sup>20</sup> cm<sup>-3</sup> and gate length,  $L_g$ , is

**Fig.1.** (a), (b), (c) and (d), respectively, shows the schematic structure of RRC, TRC, GME-TRC and MLGME-TRC MOSFETs, where channel length  $L_g$  = $L_1$  +  $L_2$ =68 nm, with work function difference  $\Phi_{MI}$ =4.7 V and  $\Phi_{M2}$ =4.10 V for MLGME-TRC and GME-TRC MOSFET and gate consists of multi-layered-gate dielectrics having a thickness  $t_{ox1}$ =2 nm and  $t_{ox2}$ =2 nm of the lower and the upper gate dielectrics with the corresponding permittivites,  $\epsilon_{ox1}$ =3.9 and  $\epsilon_{ox2}$ =20, respectively and for GME-TRC, TRC and RRC MOSFETs  $t_{ox}$ =4 nm and  $\epsilon_{ox}$ = $\epsilon_{ox1}$ =3.9. For TRC and RRC MOSFET, channel length  $L_g$ =L=68 nm and work function  $\Phi_{MI}$ =4.7 V having Source/Drain junction depth ( $X_j$ )=10 nm, groove depth d=20 nm, permittivity  $\epsilon_{ox1}$ =3.9,  $N_A$ =1 × 10<sup>17</sup> cm<sup>-3</sup>,  $N_D$ =1 × 10<sup>20</sup> cm<sup>-3</sup>. Effective channel length is,  $L_{eff}$ =(2 $L_s$ ) +  $L_p$ , where,  $L_p$ =28 nm and  $L_s$ =14 nm for MLGME-TRC, GME-TRC, TRC MOSFETs and  $L_p$ =68 nm and  $L_s$ =10 nm for RRC MOSFET, unless stated otherwise.

taken as 68 nm for all the devices for fair comparison. The work functions of gate metals M1 and M2 are chosen as 4.77 eV and 4.1 eV, respectively. The study is carried out using ATLAS and DEVEDIT device simulators in order to verify the results of proposed model and a good agreement between their results is obtained. All the device parameters of considered device structures are equivalent, unless otherwise stated.

#### IV. MODEL FORMULATION

#### 1. Linearity-Distortion Analysis

Low distortion is one of the biggest concerns for current and next-generation wireless communication systems. In order to study the linearity performance, analysis has been carried out in terms of higher order transconductance coefficients and device FOMs:  $V_{IP2}$  and  $V_{IP3}$  [24], third-order input intercept point (IIP3) [25] and 1-dB compression point, which has been obtained using drain current ( $I_{ds}$ - $V_{gs}$ ) characteristics with channel length modulation (CLM) effect from sub-threshold to saturation region [26], and is defined as:

$$I_{ds} = \frac{W.\mu_{s}.C_{oxc}}{(L_{eff}-I_{d}).\left(1 + \frac{\delta_{o}.\mu_{s}.V_{dsx}}{(L_{eff}-I_{d}).V_{sat}}\right)}.(V_{gsx}-V_{th}-0.5.\alpha.V_{dsx}).V_{dsx}$$

(1)

where, W is the device width,  $\mu_s$  is the inversion layer mobility of carriers,  $\delta_o$  is the fitting parameter,  $\alpha$  is the Bulk body term,  $\nu_{sat}$  is the carrier saturation velocity,  $V_{gs}$  and  $V_{ds}$  are the gate to source voltage and drain to source voltage, respectively and  $C_{oxc}$  is the gate oxide capacitance, which can be defined as:  $C_{oxc} = \frac{\epsilon_o \epsilon_{ox}}{r_o \ln(1 + EOT/r_o)}, \text{ where } \epsilon_o \text{ and } \epsilon_{ox} \text{ are the dielectric}$  permittivity of air and SiO<sub>2</sub>, respectively,  $r_o$  is the radius of the convex groove [27] and EOT is the effective oxide thickness, i.e.,  $\frac{EOT=t_{ox1}+\frac{\epsilon_{ox1}}{\epsilon_{ox2}}t_{ox2}}{\epsilon_{ox2}}, \text{ where, } \epsilon_{ox1} \text{ and } \epsilon_{ox2} \text{ are}$  the Dielectric permittivity of lower and upper gate and  $t_{ox1}$  and  $t_{ox2}$  are the thickness of the lower and upper dielectric, respectively.

Also,  $L_{eff}$  is the effective channel length and;  $V_{dsx}$  is the effective drain-source voltage and  $V_{gsx}$  gives the smooth transition from strong to weak inversion, which is given as:

$$\begin{aligned} &V_{dsx} \!=\! V_{dsat} \!\cdot\! \left[ 1 \!-\! \frac{ln \! \left[ 1 \!+\! exp \! \left[ A \!\cdot\! \left( 1 \!-\! \frac{V_{ds}}{V_{dsat}} \right) \right] \right]}{ln \! \left( 1 \!+\! exp \! \left( A \!\cdot\! \right) \right)} \right] \quad and \\ &V_{gsx} \!=\! 2 .\eta .V_t .ln \! \left[ 1 \!+\! exp \! \left[ \frac{V_{gs} \!-\! V_{th}}{2 .\eta .V_t} \right] \right] \!+\! V_{th} \end{aligned}$$

where,  $V_{dsat}$  is drain saturation voltage,  $\eta$  is the capacitive coupling factor between gate and silicon surface,  $V_t = \frac{k.T}{q}$ , where, k and T are the Boltzmann constant and temperature in Kelvin, respectively and A is constant, whose value is taken as 8.

The effective channel length is decreased by  $l_d$ , due CLM effect, i.e.  $l_d = l.\ln\left(1 + \frac{V_{dsx} - V_{dsat}}{V_{nn}}\right)$  where,  $B = (V_{gsx} - V_{th} - 0.5.\alpha. V_{dsx}).V_{dsx}$  $l = \sqrt{\frac{\varepsilon_{si}}{\varepsilon}} \cdot t_{ox} \cdot X_{j}$ , where,  $\varepsilon_{si}$  is the dielectric permittivity of Silicon and  $X_i$  is the Source/Drain junction depth and  $V_{pp}$ [26] is treated as fitting parameter and its value can be calculated as:  $V_{pp} = \frac{l.\epsilon_c}{\delta^{1/2}}$ , where  $\epsilon_c = 2.\frac{v_{sat}}{U_{sat}}$

The, threshold voltage, Vth, for GME-TRC MOSFET [27] is defined as:

$$V_{th} = 2\phi_{F} + \frac{1}{M} \frac{(r_{o} + EOT)y_{d}}{(y_{d} - r_{o} - EOT)} \frac{qN_{A}}{\varepsilon_{s}} - 2exp\left(\frac{-\theta_{01}}{2\lambda}\right) \sqrt{\delta_{11}\delta_{12}}$$

(2)

The depletion layer thickness  $y_d$ , is approximately given by  $y_d = \sqrt{\frac{2\varepsilon_{Si}}{qN_A}} 1.5\phi_F$  where,  $\phi_F$  is the Fermi potential and q is the electronic charge.

Further, assuming the concave corner to be part of a cylinder, having corner radius of the convex groove is r<sub>0</sub>, and the corner angle under region M1 is  $\theta_{o1}$ .

Also,  $\lambda$ , M,  $\delta_{11}$  and  $\delta_{12}$  are the variables whose values have been calculated in [27].

Moreover, Non-linearity in a device is manifested by the presence of high-order 'harmonics' at the output signal. To model the non-linearity, a MOSFET modulated with an AC gate voltage, Vgs, producing a drain current, Ids, can be viewed as a time variant nonlinear system

$$1_{ds} = I_o + g_{m1} \cdot V_{gs} + g_{m2} \cdot V_{gs}^2 + g_{m3} \cdot V_{gs}^3 + \dots$$

(3)

where, I<sub>0</sub> is the current at DC operation point and Taylor expansion coefficients are  $g_{mn} = \frac{1}{n!} \frac{\partial^n I_{ds}}{\partial V^n} \Big|_{V_{ds} = const}$  which can be represented as:

#### A. First Order Transconductance

$$g_{ml} = \frac{\partial I_{ds}}{\partial V_{gs}} \Big|_{V_{ds} = const} = \begin{cases} -\frac{A'B}{C} \cdot \left( -\frac{dI_d}{dV_{gs}} \cdot v_{sat} + \delta_o \cdot \mu_s \cdot \frac{dV_{dsx}}{dV_{gs}} \right) + \\ A' \left( \frac{dV_{gsx}}{dV_{gs}} - \frac{0.5 \alpha dV_{dsx}}{dV_{gs}} \right) \cdot V_{dsx} \\ + A' \cdot (V_{gs} - V_{th} - 0.5 \cdot \alpha \cdot V_{dsx}) \cdot \frac{dV_{dsx}}{dV_{gs}} \end{cases}$$

where,

$$A' = \frac{\mu_s . C_{oxc} . W. \nu_{sat}}{\left(\left(L_{eff} - l_d\right) . \nu_{sat} + \delta_o . \mu_s . V_{dsx}\right)}$$

,

$$B = (V_{gsx} - V_{th} - 0.5 . \alpha . V_{dsx}) . V_{dsx}$$

$$C = \left(\left(L_{eff} - l_d\right) . \nu_{sat} + \delta_o . \mu_s . V_{dsx}\right) \text{ and } E = 1 + exp \left[\frac{V_{gs} - V_{th}}{2 . \eta . V_t}\right]$$

#### B. Second Order Transconductance

$$g_{m2} = \frac{\partial^{2}I_{ds}}{\partial V_{gs}^{2}} \Big|_{V_{ds} = const} = \begin{bmatrix} \frac{2 A'B}{c} \cdot \left( \frac{dI_{d}}{dV_{gs}} \cdot V_{sat} + \delta_{o} \cdot \mu_{s} \cdot \frac{dV_{dsx}}{dV_{gs}} \right)^{2} - \frac{2A'B}{c} \cdot \left( \frac{dV_{gsx}}{dV_{gs}} - \frac{0.5\alpha dV_{dsx}}{dV_{gs}} \right) - \frac{2A'B}{c} \cdot \left( -\frac{dI_{d}}{dV_{gs}} \cdot V_{sat} + \delta_{o} \cdot \mu_{s} \cdot \frac{dV_{dsx}}{dV_{gs}} \right) - \frac{2A'}{c} \cdot \left( -\frac{dI_{d}}{dV_{gs}} \cdot V_{sat} + \delta_{o} \cdot \mu_{s} \cdot \frac{dV_{dsx}}{dV_{gs}} \right) - \frac{2A'B}{c} \cdot \left( -\frac{d^{2}I_{d}}{dV_{gs}^{2}} \cdot V_{sat} + \delta_{o} \cdot \mu_{s} \cdot \frac{d^{2}V_{dsx}}{dV_{gs}} \right) + \frac{A'B}{c} \cdot \left( -\frac{d^{2}I_{d}}{dV_{gs}^{2}} \cdot V_{sat} + \delta_{o} \cdot \mu_{s} \cdot \frac{d^{2}V_{dsx}}{dV_{gs}^{2}} \right) + \frac{A'B}{c} \cdot \left( \frac{d^{2}V_{gsx}}{dV_{gs}^{2}} - 0.5\alpha \cdot \frac{d^{2}V_{dsx}}{dV_{gs}^{2}} \right) \cdot V_{dsx} + \frac{2A'}{c} \cdot \left( \frac{dV_{gsx}}{dV_{gs}} - \frac{0.5\alpha dV_{dsx}}{dV_{gs}} \right) \cdot \frac{dV_{dsx}}{dV_{gs}} + \frac{A'}{c} \cdot (V_{gsx} - V_{th} - 0.5 \cdot \alpha \cdot V_{dsx}) \cdot \frac{d^{2}V_{dsx}}{dV_{gs}^{2}}$$

where,

$$V_{dsat} = \frac{V_{gsx} \cdot V_{th}}{\alpha}$$

,  $\frac{dV_{dsat}}{dV_{gs}} = \frac{E \cdot l}{\alpha \cdot E}$  and

$$\frac{dl_d}{dV_{gs}} = \frac{l}{V_{pp}} \cdot \frac{\left(\frac{dV_{dsx}}{dV_{gs}} - \frac{dV_{dsat}}{dV_{gs}}\right)}{\left(1 + \frac{V_{dsx} \cdot V_{dsat}}{V}\right)}$$

(5)

$$\frac{dV_{dsx}}{dV_{gs}} = \frac{dV_{dsat}}{dV_{gs}} \cdot \begin{bmatrix} -\ln\left[1 + \exp\left[A \cdot \left(1 - \frac{V_{ds}}{V_{dsat}}\right)\right]\right] - \\ -\ln\left(1 + \exp(A)\right) \\ \exp\left[A \cdot \left(1 - \frac{V_{ds}}{V_{dsat}}\right)\right] \\ \frac{A \cdot V_{ds}}{V_{dsat}} \cdot \frac{\exp\left[A \cdot \left(1 - \frac{V_{ds}}{V_{dsat}}\right)\right] - \ln\left(1 + \exp(A)\right)}{1 + \exp\left[A \cdot \left(1 - \frac{V_{ds}}{V_{dsat}}\right)\right] \cdot \ln\left(1 + \exp(A)\right)} \end{bmatrix}$$

(6)

Also,

$$\frac{d^2l_d}{dV_{gs}^2}$$

and  $\frac{d^2V_{dsx}}{dV_{gs}^2}$  can be obtained by

differentiating Eqs. (5-6) w.r.t. V<sub>gs</sub>.

Similarly, by differentiating again Eq. (4) w.r.t. V<sub>gs</sub> we obtained  $g_{m3}$ , i.e.

$$\begin{split} g_{m3} = & \frac{\partial^{3} I_{ds}}{\partial V_{gs}^{3}} \Big|_{V_{ds} = const} = NQ. \\ & \frac{dN}{dV_{gs}} - \frac{2A'}{QC} \frac{dV_{dsx}}{dV_{gs}} - \frac{2QA'}{QC} \frac{d^{2}V_{dsx}}{dV_{gs}} - \frac{2QA'}{C} \frac{d^{2}V_{dsx}}{dV_{gs}^{2}} - \frac{2QA'}{C} \\ & \frac{dN}{dV_{gs}} - \frac{2QA'}{QC} \frac{d^{2}V_{dsx}}{dV_{gs}^{2}} - \frac{2QA'}{C} \frac{d^{2}V_{dsx}}{dV_{gs}^{2}} - \frac{2QA'}{C} \\ & \frac{dQ}{dV_{gs}} + \frac{2A'}{C} \frac{dV_{dsx}}{dV_{gs}^{2}} - \frac{2QA'}{C} \frac{dV_{dsx}}{dV_{gs}} - \frac{2QA'}{QC} \\ & \frac{dQ}{dV_{gs}} + \frac{2A'}{C} \frac{dV_{dsx}}{dV_{gs}} - \frac{2A'B}{C} \frac{dV_{dsx}}{dV_{gs}} - \frac{2A'B}{C} \frac{dV_{dsx}}{dV_{gs}} - \frac{2A'}{C} \frac{dV_{dsx}}{dV_{gs}} - \frac{A'}{C} \frac{dV_{dsx}}{dV_{gs}} - \frac{A'$$

$$where, \ N = \left(-\frac{dI_{\it d}}{dV_{gs}}.\nu_{sat} + \delta_{o}.\mu_{s}.\frac{dV_{dsx}}{dV_{gs}}\right), \quad Q = \left(\frac{dV_{gsx}}{dV_{gs}} - 0.5\alpha.\frac{dV_{dsx}}{dV_{gs}}\right)$$

Further, the linearity FOMs can be obtained by using above equations as:

$$V_{IP2} = 4 \cdot \left(\frac{g_{m1}}{g_{m2}}\right)$$

and  $V_{IP3} = \sqrt{24 \cdot \frac{g_{m1}}{g_{m3}}}$  [28] IIP3= $\frac{2}{3} \cdot \left(\frac{g_{m1}}{g_{m3} \cdot Rs}\right)$  and [29] 1-dB compression point =  $0.22 \sqrt{\frac{g_{m1}}{g_{m3}}}$

where, Rs=50  $\Omega$  for most RF applications.

For improved linearity performance and low distortion operations, these FOMs should be as high as possible. Where,  $V_{IP2}$  represents the extrapolated input voltage at which first and second-order harmonic voltages are equal;  $V_{IP3}$  represents the extrapolated input voltage at which first and third-order harmonic voltages are equal; and IIP3 represents the extrapolated input power at which first and third-order harmonic powers are equal.

#### V. RESULTS AND DISCUSSION

### 1. Electron Temperature Assessment for Different Recessed Channel Structure

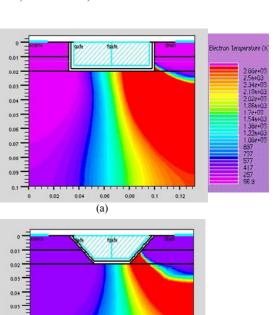

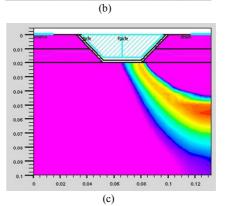

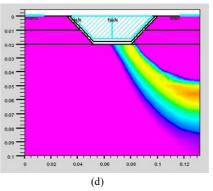

Fig. 2 shows the impact of electron temperature for various recessed structures along the channel position. In

**Fig. 2.** (a), (b), (c) and (d), respectively, show the variation of electron temperature along the channel position for RRC, TRC, GME-TRC and MLGME-TRC MOSFETs.

scaled devices, electric field peak near the drain end causes carrier heating that results in the hot electron effect thereby degrading the hot carrier reliability of the device. From Fig. 2(a) and (b), it can be seen that the TRC MOSFET results in improved hot carrier reliability as compared to RRC MOSFET by possessing lower electron temperature at the drain end. This is because in RRC MOSFET the corners are comparatively sharper as compared to TRC MOSFET which results in high peak electric field at the corners, leading to high carrier heating near the drain end, resulting in degradation of hot carrier immunity in RRC MOSFET. In GME-TRC MOSFET high electric field originates in between the channel and reduces at the drain end, because of the work function difference between the two metal gates. This result in screening of channel regime from potential variations at the drain, leading to reduced carrier heating, thereby enhances the hot carrier reliability in terms of reduced electron temperature at the drain, as shown in Fig. 2(c). The incorporation of multi-layered high-κ dielectric system facilitates physically thicker gates, thereby permitting the scaling of gate oxide thickness and thus, increasing gate control over the channel. Also, it is seen from Fig. 2(d) that, MLGME-TRC MOSFET exhibits lowest electron temperature near the drain as compared to its conventional counterparts, owing to the use of high-κ upper dielectric, resulting in improved screening across the channel from drain potential variation, tending to reduced electric field at the drain end which in turn reduces the gate leakage current and hence, also provides the hot carrier immunity in the device.

#### 2. Linearity Performance Evaluation

#### A. Higher Order Transconductance Parameterization

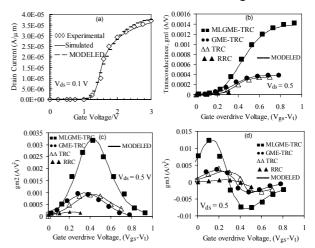

Fig. 3(a) shows the drain current characteristics for grooved gate MOSFET [30], having  $L_g$ =140 nm. It is reflected from the figure that there is a good agreement between experimental, simulation and proposed model. Figs. 3(b-d) shows the higher order transconductance parameters, i.e.  $g_{m1}$ ,  $g_{m2}$ , and  $g_{m3}$  with respect to gate overdrive voltage ( $V_{gs}$ - $V_t$ ), for MLGME-TRC, GME-TRC, TRC and RRC MOSFETs having threshold voltage, i.e.  $V_t$ , equals to 0.191 V, 0.217 V, 0.30 V and 0.49 V, respectively.

Fig. 3(b) indicates that, MLGME-TRC MOSFET shows the higher performance as compared to RRC and

GME-TRC MOSFET. This is due to the gate material

**Fig. 3.** (a) Experimental, Simulation and modeled result comparison of  $I_{ds}$ - $V_{gs}$  characteristics of grooved gate MOSFET, having  $L_g$ =140 nm.(b), (c) and (d) shows the variation of  $g_{m1}$ ,  $g_{m2}$  and  $g_{m3}$  respectively.

engineering architecture and multi-layered high- $\kappa$  dielectric system, which provides the significantly enhanced screening effect and facilitates the physically thicker gates, thereby permitting the scaling of gate oxide thickness, resulting in increasing the gate control over the channel and hence, the transconductance parameters. The zero-crossover point of  $g_{m3}$  determines the DC bias point for optimum device operation.

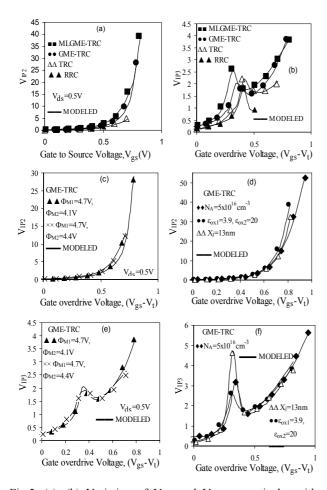

Thus, the non-linear behaviour of g<sub>m3</sub> can be minimized by setting DC bias close to g<sub>m3</sub> zero-crossover point. Since g<sub>m3</sub> has approximately a balanced magnitude around the zero-crossover point as is clear from Fig. 3(d), the harmonic distortion it generates can be cancelled for a small signal [19]. Fig. 3(d) clearly indicates that, as we move from RRC structure to more prominent device structures, i.e. TRC, GME-TRC and then to MLGME-TRC, it results in shifting of bias point towards the lower V<sub>gs</sub>, as a consequence of improvement in gate control, and hence causing reduction in harmonic distortion and non-linear behaviour. Moreover, to gain the effectiveness of the proposed design, impact of various technology parameter variations has been considered for higher transconductance parameters with respect to gate overdrive voltage, having threshold voltage 0.217 for  $\Phi_{M1}$ =4.7 V,  $\Phi_{M2}$ =4.1 V, 0.288 for  $\Phi_{M1}$ =4.7 V,  $\Phi_{M2}$ =4.4 V, 0.06 V for,  $N_A=1\times10^{17}$  cm<sup>-3</sup>, 0.19 V for,  $\varepsilon_{ox1}=3.9$  and  $\varepsilon_{ox2}$ =20 and 0.18 V for X<sub>i</sub>=13 nm, as shown in Figs. 4(a-f). It is seen from Figs. 4(a), (c) and (e) that, the increase in

work function difference of two gate metals, i.e.  $\Phi_{M1}$  and

**Fig. 4.** (a), (c) and (e) Variation of  $g_{m1}$ ,  $g_{m2}$  and  $g_{m3}$ , respectively, with gate overdrive voltage  $(V_{gs}-V_t)$  for workfunction difference variation of GME-TRC MOSFET. (b), (d) and (f) Variation of  $g_{m1}$ ,  $g_{m2}$  and  $g_{m3}$ , respectively, with gate overdrive voltage  $(V_{gs}-V_t)$  of GME-TRC MOSFET for different structural parameters.

$\Phi_{M2}$ , results in enhancement of potential step at the metal gate interface, leading to the improvement in screening effect due to metal gate M2.

Thus, increasing workfunction difference can further suppress the harmonic distortion and non linear behaviour in terms of shifting of DC bias point of  $g_{m3}$  towards the lower  $V_{gs}$ , as shown in Fig. 4(e).

Results also indicate that, higher order transconductance parameters can be improved further by using lightly doped substrate, due to carrier mobility enhancement, which in turn implies better carrier transport efficiency and reduced non linear behaviour in terms of shifting of DC bias point of  $g_{m3}$  towards the lower  $V_{gs}$ , as shown in Fig. 4(f). It is seen from the figure that, the increase of dielectric constant  $\varepsilon_{ox2}$ , also improves the linearity behaviour due to reduced gate oxide leakages and hot carrier effects (HCEs), leading to suppress harmonic distortion and non-linear behaviour exhibited by  $g_{m3}$ . Moreover, as  $X_i$  increases, i.e. NJD

decreases, the bias point moves towards the lower  $V_{gs}$ , this is mainly attributed because of the decrease in height of the barriers formed at the corners with the decrease in NJD, resulting in increased carrier mobility due to improved gate control over the channel thereby, enhancing the linear characteristics, as illustrated by Fig. 4(b), (d) and (f). Close proximity of modeled and simulated results proves the validity of the proposed model.

#### B. $V_{IP2}$ and $V_{IP3}$ Linearity FOMs

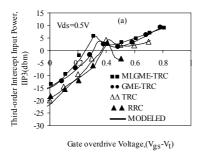

V<sub>IP2</sub> and V<sub>IP3</sub>, represents the extrapolated gate-voltage amplitudes at which the second and third order harmonics, respectively, becomes equal to the fundamental tone in the device drain current (I<sub>ds</sub>). These are the suitable FOMs, which can properly determine the distortion characteristics from DC parameters; to achieve high linearity and low distortion operations, these should be as high as possible. It is seen from Fig. 5(a) and (b) that V<sub>IP2</sub> and peak point or singularity in V<sub>IP3</sub> increases significantly in MLGME-TRC MOSFET and occurs at the lower gate bias, implies that lower gate voltage is needed to preserve the linearity, as compared to conventional GME-TRC, TRC and RRC MOSFETs. This is due to the reduced harmonic distrotion, owing to the improvement in gate leakages, carrier transport efficiency and hence the device gain. The peak of V<sub>IP3</sub> mainly signifies the second order interaction effect and depicts the cancellation of the third-order non-linearity by device internal feedback around a second order nonlinearity. This peak is highest in MLGME-TRC MOSFET, as shown in Fig. 5(b), thus, it is more linear than its conventional counterparts. Moreover, in order to improve the RF performance of the device, the structural design parameter needs to be tailored; hence influence of various technology variations have also been studied.

Figs. 5(c-f), respectively, shows the  $V_{IP2}$  and  $V_{IP3}$  profile for different structural parameter variations. It is seen that, as the metal gate work function difference for GME-TRC MOSFET is increased, substrate doping is decreased and  $X_j$  is increased, i.e. NJD is decreased,  $V_{IP2}$  and the peak in  $V_{IP3}$  significantly increases and singularity in  $V_{IP3}$  shifts more towards the lower gate bias, owing to improved gate control and drive current due to the increased screening of metal gate M1, improved mobility and enhanced carrier effeciency

Fig.5. (a), (b) Variation of  $V_{IP2}$  and  $V_{IP3}$ , respectively, with overdrive voltage  $(V_{gs}-V_t)$  for MLGME-TRC, GME-TRC, TRC and RRC MOSFETs. (c), (e) Variation of  $V_{IP2}$  and  $V_{IP3}$ , respectively, with gate overdrive voltage  $(V_{gs}-V_t)$  for workfunction difference variation of GME-TRC MOSFET. (d), (f) Variation of  $V_{IP2}$  and  $V_{IP3}$ , respectively, with gate overdrive voltage  $(V_{gs}-V_t)$  of GME-TRC MOSFET for different structural parameters

across the channel, respectively. It is also indicated from the Fig. 5(d) and (f) that, linearity-distortion performance is improved with the increase in dielectric constant, i.e.  $\epsilon_{ox2}$ , of MLGME-TRC MOSFET due to enhanced gate control over inversion charge density leading to improvement in  $g_{m1}$  and hence,  $V_{IP2}$  and  $V_{IP3}$ .

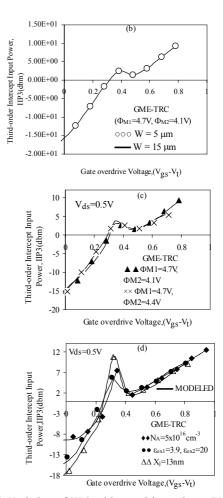

Fig.6. (a) Variation of IIP3 with overdrive voltage  $(V_{gs}-V_t)$  for MLGME-TRC, GME-TRC, TRC and RRC MOSFETs, (b) Variation of IIP3 with overdrive voltage  $(V_{gs}-V_t)$  for workfunction difference variation of GME-TRC MOSFET, (c) Variation of IIP3 with overdrive voltage  $(V_{gs}-V_t)$  of GME-TRC MOSFET for device width W=1  $\mu$ m and 15  $\mu$ m, (d) Variation of IIP3 with overdrive voltage  $(V_{gs}-V_t)$  of GME-TRC MOSFET for different structural parameters.

#### C. IIP3 and 1-dB compression point

IIP3 and 1-dB compression point are yet another important FOMs that evaluates the linearity performance. Further, the third-order nonlinearity term,  $g_{m3}$ , is mainly caused the trouble in RF applications, since it leads to inter-modulation, i.e. distortion of the fundamental amplitude via signals in the adjacent bands. In signal power, IIP3, where this spurious term is equal to the fundamental one is called the third-order intermodulation intercept point. Fig. 6(a) represents the variation of IIP3 with gate overdrive voltage for various recessed channel structures. There is a considerable enhacement in IIP3 for MLGME-TRC MOSFET in comparison to conventional GME-TRC, TRC and RRC

MOSFETs. This is attributed to the step potential profile and improved gate controlability exhibited by GME and multilayered architecture. Thus, this significantly increases the carrier transport efficiency and gate control over the channel, thereby enhancing the gain (i.e. transconductance, g<sub>m1</sub>). Further, in order to preserve linearity, the device should be biased in pre-kink position. Fig. 6(a) clearly shows the shifting of kink position towards higher gate bias for conventional MOSFETs in comparison to MLGME-TRC MOSFET which implicates that conventional MOSFETs need larger currents to preserve linearity. Moreover, it is seen from Fig. 6(b) and (c) that the variation of IIP3 for device width  $W = 5 \mu m$  and W = 15um is same as that for W=1 um. This is due to the fact that, the transconductance mainly depends on the carrier following across the channel and the width of the device hardly affects its performance. Due to this reason authors have taken the constant device width (W), i.e. 1 µm, through out its consideration.

Further, the input power value, in dB, at which the gain of the low noise amplifier (LNA) drops by 1 dB, is referred to as the 1 dB gain compression point or the P1dB. This parameter is important for an amplifier circuit as it gives an idea about the maximum input power that the circuit can handle by providing a fixed amount of gain. Once the input power exceeds the P1dB of the amplifier, the gain starts decreasing. Thus, it is desirable that a LNA should have as high a P1dB value as feasible without significant tradeoff in the other parameters.

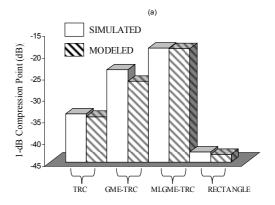

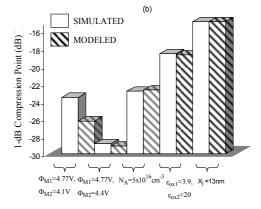

Fig. 7(a) clearly demonstrates that MLGME-TRC MOSFET exhibits a higher 1-dB compression point in contrast to conventional MOSFETs due to reduced signal distortion, and transconductance. Further, the effect of variation of device width (W) on P1dB is negligible and gives the same value, i.e. -26 for W=1  $\mu m$ , 5  $\mu m$  and 15  $\mu m$ . This is because P1 dB is depends on transconductance and its derivative which is related to the carrier transport efficiency across the channel and the device width hardly has any impact on the channel formed.

Moreover, tuning of the GME-TRC MOSFET design in terms of increased workfunction difference, increased  $X_j$ , i.e. decreased NJD, dielectric constant,  $\varepsilon_{ox2}$ , and reduced substrate doping further improves IIP3 and 1-dB compression point and hence, enhances the linearity performance of the proposed design, as shown in Figs. 6(c, d) and Fig. 7(b).

Fig.7. (a) 1-dB compression point (dB) at gate bias,  $V_{gs}$ =0.5 V for MLGME-TRC, GME-TRC, TRC and RRC MOSFETs, (b) 1-dB compression point (dB) at gate bias,  $V_{gs}$ =0.5 V for different structural parameter variations of GME-TRC MOSFET.

Hence, MLGME-TRC MOSFET exhibits superior linearity performance and high device efficiency as compared to conventional MOSFETs in terms of transconductance coefficients  $g_{m1}$ ,  $g_{m2}$  and  $g_{m3}$ ; and linearity metrics evaluation parameters:  $V_{IP2}$ ,  $V_{IP3}$  and IIP3. Results, thus, imply that the RF harmonic distortion and linearity improves tremendously in scaled MOS devices. Although the amplifier's IIP3 and IMD3 are more complex in a single MOSFET, the optimization of the MOSFETs characteristics is a requisite to achieve the best LNA performance.

#### VI. CONCLUSIONS

The present work concentrates on the extensive study for various recessed channel structures, i.e. RRC, TRC, GME-TRC and MLGME-TRC MOSFETs, for different dielectric configurations to optimize the linearity performance by developing a model and validating it with experimental and simulated results. The key

factors affecting the device performance and the physics behind it are also scrutinized. Results reveal that MLGME-TRC design is superior to its conventional counterpart in all aspects, proving its consistently enhanced linearity performance in terms of improved higher order transconductance coefficients:  $g_{m1}$ ,  $g_{m2}$ ,  $g_{m3}$  and intermodulation distortion performance in terms of FOMs:  $V_{IP2}$ ,  $V_{IP3}$ , IIP3 and 1-dB compression point. Hence, MLGME-TRC MOSFET design presents its effectiveness in the high-scale integration, design and modeling of power amplifiers and RFIC design.

#### REFERENCES

- [1] T.Y.Yum, L.Chiu, C.H.Chan and Q.Xue, "High-Efficiency Linear RF Amplifier-A Unified Circuit Approach to Achieving Compactness and Low Distortion," *IEEE Trans. Microw. Theory Tech.*, Vol.54, pp.3255-3266, 2006.

- [2] C.Yu, J.S.Yuan and H.Yang, "MOSFET Linearity Performance Degradation Subject to Drain and Gate Voltage Stress," *IEEE Trans. Device Mater. Rel.*, Vol.4, pp.681-689, 2004.

- [3] S.Y.Lee, Y.S.Lee and Y.H.Jeong, "A Novel Phase Measurement Technique for IM3 Components in RF Power Amplifiers," *IEEE Trans. Microw. Theory Tech.*, Vol.54, pp.451-457, 2006.

- [4] B.Razavi, RF Microelectronics, Prentice-Hall; Chapter-2, 1998.

- [5] P. Malik, R. Chaujar, M. Gupta, R.S. Gupta, "Linearity Performance Assessment of Nanoscale Gate Material Engineered Trapezoidal Recessed Channel (GME-TRC) MOSFET for RFIC design and Wireless application," *Nanotech conference* and Expo 2010, Anaheim, CA, United state of America, pp.705-708, June, 2010.

- [6] P. Malik, S.P. Kumar, R. Chaujar, M. Gupta, R.S. Gupta, "GATE MATERIAL ENGINEERED-TRAPEZIODAL RECESSED CHANNEL MOSFET FOR HIGH-PERFORMANCE ANALOG AND RF APPLICATIONS," *Microwave and optical technology letter,* Vol.52, pp.694-698, 2010.

- [7] H. Ren, Y. Hao, "The influence of geometric structure on the hot-carrier-effect immunity for deep-sub-micron grooved gate PMOSFET," Solid-State Electronic, Vol.46, pp.665-673, 2002.

- [8] International Technology Roadmap for Semiconductors (ITRS). 2004 edition.

- [9] H.S. Momose, M. Ono, T. Yoshitomi, T. Ohguro, S. Nakamura, M. Saito, H. Iwai, "1.5 nm direct-tunneling gate oxide Si MOSFET's," *IEEE Trans. Electron.Dev.* Vol.43, pp.1233-1242, 1996.

- [10] G.D.Wilk, R.M.Wallace, J.M.Anthony, "High-K gate dielectrics: current status and materials properties considerations," *J.Appl.Phys.*, Vol.89, pp. 5243-5275, 2001.

- [11] B.-Y.Tsui, L.-F.Chin, "A Comprehensive Study on the FIBL of Nanoscale MOSFETs," *IEEE Trans. Electron.Dev.* Vol.51, pp.1733-1736, 2004.

- [12] G. C.-F. Yeap, S. Krishnan, M.-R. Lin, "Fringing-induced barrier lowering (FIBL) in sub-100 nm MOSFETs with high-K gate dielectrics," *Electron. Lett.* Vol.34, pp.1150-1152, 1998.

- [13] C. Hobbs, L. Fonseca, V. Dhandapani, S. Samavedam, B. Taylor, J. Grant, L. Dip, D. Triyoso, R. Hegde, D. Gilmer, R. Garcia, D. Roan, L. Lovejoy, R. Rai, L. Hebert, H. Tseng, B. White, P. Tobin, "Fermi level pinning at the PolySi/Metal Oxide interface," *Symp.VLSI Tech.Dig*, pp.9-10, 2003.

- [14] R.M. Wallace, G.Wilk, "Alternative Gate Dielectrics for Microelectronics," MRS Bull. Vol.27, pp.192-197, 2002.

- [15] V. Mistra, G.Lucovsky, G.Parsons, "Issues in high-k gate stack interfaces," MRS Bull. Vol.27, pp.212-216, 2002.

- [16] M. Xiao-Hua, H. Yue, S. Bao-Gang, G. Hai-Xia, R. Hong-Xia, Z. Jin-Cheng, Z. Jin-Feng, Z. Xiao-Ju, Z. Wei-Dong, "Fabrication and characterization of groove-gate MOSFETs based on a self-aligned CMOS process," *Chin. Phy. Soc*, Vol.15, pp.195-198, 2006.

- [17] J.Y. Seo, K.J. Lee, Y.S. Kim, S.Y. Lee, S.J. Hwang, C.K. Yoon, "Reliability for recessed channel structure n-MOSFET," *Microelectron. Reliab.*, Vol.45, pp.1317-1320, 2005.

- [18] I. Polishchuk, P. Ranade, T.J. King and C. Hu, "Dual work function metal gate CMOS technology using metal interdiffusion," *IEEE Electron Device Lett.*, Vol.22, pp.444-446, 2001.

- [19] J. Lee, Y.S. Suh, H. Lazar, R. Jha, J. Gurganus, Y. Lin and V. Misra, "Compatibility of dual metal gate electrodes with high-k dielectrics for CMOS,"

- IEDM Tech. Dig., pp.323-326, 2003.

- [20] S. Luan, H. X. Liu and R. X. Jia, "Performance investigations of novel dual-material gate (DMG) MOSFET with dielectric pockets (DP)," *Science in China Series E: Technological Sciences*, Vol.52, pp. 2400-2405, 2009.

- [21] W. Long, H. Ou, J.M. Kuo, et al, "Dual material gate (DMG) field effect transistor," *IEEE Trans Electron Devices*, Vol.46, pp.865-870, 1999.

- [22] S.J. Lee, C.H. Choi, A. Kamath, R. Clark and D.L. Kwong, "Characterization and reliability of dual high-k gate dielectric stack (poly-Si–HfO<sub>2</sub>–SiO<sub>2</sub>) prepared by in situ RTCVD process for system-on-chip applications," *IEEE Electron Device Lett.*, Vol. 24, pp.105-107, 2003.

- [23] T. Kauerauf, B. Govoreanu, R. Degraeve, G. Groeseneken and H. Maes, "Scaling CMOS: finding the gate stack with the lowest leakage current Solid-State Electron," Vol.49, pp.695-701, 2005.

- [24] P.H. Woerlee, M.J. Knitel, R. Van Langevelde, D.B.M. Klaassen, L.F. Tiemeijer, A.J. Scholten, A.T.A. Zegers-van Duijnhoven, "RF-CMOS performance trends," *IEEE Trans. Electron Dev.* Vol.48, pp. 1776-1782, 2001.

- [25] S. Kaya, W. Ma, "Optimization of RF linearity in DG-MOSFETs," *IEEE Electron Device Lett.* Vol.25, pp. 308-310, 2004.

- [26] N.D. Arora, R. Rios, C-L Huang and K. Raol, "PCIM: A Physically Short-Channel IGFET Model for Circuit Simulation," *IEEE Trans. Electron Devices*, Vol.41, pp.988-997, 1994.

- [27] P. Malik, R. Chaujar, M. Gupta, R.S. Gupta, "Physics based Threshold Voltage Analysis of Gate Material Engineered Trapezoidal Recessed Channel (GME-TRC) Nanoscale MOSFET and its multilayered gate architecture," *INTERNATIONAL JOURNAL OF MICROWAVE AND OPTICAL TECHNOLOGY*, Vol.5, pp.361-368, 2010.

- [28] P. H.Woerlee, M. J. Knitel, R.V. Langevelde, D. B. M. Klaassen, L. F. Tiemeijer, A. J. Scholten, and A. T. A. Zegers-van Duijnhoven, "RF-CMOS Performance Trends," *IEEE TRANSACTIONS ON ELECTRON DEVICES*, Vol.48, pp.1776-1782, 2001.

- [29] S. Kaya, and W. Ma, "Optimization of RF Linearity in DG-MOSFETs," *IEEE ELECTRON DEVICE LETTERS*, Vol.25, pp.308-310, 2004.

[30] M. Xiao-Hua, H. Yue, S. Bao-Gang, G. Hai-Xia, R. Hong-Xia, Z. Jin-Cheng, Z. Jin-Feng, Z. Xiao-Ju, and Z. Wei-Dong, "Fabrication and characterization of groove-gate MOSFETs based on a self-aligned CMOS process," *Chin. Phys. Soc.*, Vol.15, pp.195-198, 2006.

**Priyanka Malik** was born in New Delhi, India, in 1985. She received her BSc. (H) and MSc. in Physics from University of Delhi, India, in 2005 and 2007, respectively. She is presently pursuing her PhD. in

Electronics from University of Delhi. Her research involves Analytical Modeling and Simulation of Recessed Channel MOSFETs in sub–100 nm regime for RF and microwave applications. She also worked as a Senior Research Fellow in DST sponsored project, "Modeling, Simulation and Characterization of Modified Different Gate Geometric Double Gate High electron Mobility Transistor for High Power and High frequency applications with two separate common Gate control". She has authored or co-authored more than 12 papers in various international and national journals and conferences.

**R. S. Gupta** (SM'81) received the B.Sc. and M.Sc. degrees from Agra University, Agra, India, in 1963 and 1966, respectively, and the Ph.D. degree in electronic engineering from the Institute of Technology, Banaras

Hindu University, Varanasi, India, in 1970.

In 1971, he was with Ramjas College, University of Delhi, Delhi, India. In 1987, he was with the Department of Electronic Science, University of Delhi South Campus, New Delhi, India, as a Reader and later as a Professor from 1997 to 2008, where he is currently an Emeritus Scientist and with the Semiconductor Devices Research Laboratory. He heads several major research projects sponsored by the Ministry of Defence, the Department of Science and Technology, the Council of Science, and the

Industrial Research and University Grants Commission. In 1988, he was a Visitor with the University of Sheffield, Sheffield, U.K., under the ALIS Link exchange program and also visited several U.S. and Spanish universities in 1995 and 1999, respectively. He also visited the Czech Republic in August 2003; Korea in November 2003; Rensselaer Polytechnic Institute, Troy, NY, in August 2004; and China in December 2005. In Dec 19, 2007 he visited Rome, Italy and in 2009 he visited North Texas University and Southeast Missouri State University USA. He has authored or coauthored over 497 papers in international and national journals and various conference proceedings. He contributed the chapter entitled "MOSFET Modeling" in the Encyclopedia on RF and Microwave Engineering (Wiley, 2005). He has supervised 36 Ph.D. students. In addition to that he has also supervised/supervising 11 PhD students. His current interests and activities include modeling of SOI submicrometer MOSFETs and LDD MOSFETs, modeling and design of HEMTs, hot-carrier effects in MOSFETs, and modeling of GaAs MESFETs for high-performance microwave and millimeter-wave circuits and quantumeffect devices.

Prof. Gupta was an Executive Member of the IEEE Electron Devices Society/Microwave Theory and Techniques Society Chapter of the IEEE India Council. Prof Gupta is the Chairman of IEEE EDS Delhi Chapter. His name also appeared in the Golden List of the IEEE TRANSACTIONS ON ELECTRON DEVICES in December 1998, 2002, and 2004. He is a Fellow of the Institution of Electronics and Telecommunication Engineers (India), a Life Member of the Indian Chapter of the International Centre for Theoretical Physics, and a Life Member of the Semiconductor Society of India and chairman of society for microelectronics and VLSI. He was the Secretary of ISRAMT'93 and the 1996 Asia-Pacific Microwave Conference (APMC'96), and the Chairman of the Technical Programme Committee of APMC'96. He edited the proceedings of both of these international conferences. He was the Chairman of APMC'2004 held in New Delhi in December 2004. He has been listed in Who's Who in the World. Prof Gupta is chairman of 12<sup>TH</sup> ISMOT 2009 to be held in Dec 2009 in India.

**Rishu Chaujar** (M'09) was born in New Delhi, India, in 1982. She received her B.Sc.(H), M.Sc. and Ph.D degrees in Electronics from the University of Delhi, India, in 2003, 2005, 2009 respectively. She is

presently working as an Assistant Professor in Department of Applied Physics, Delhi Technological University (Formerly Delhi College of Engineering), New Delhi, India. She has worked as an Assistant Professor in Department of Physics and Electronics, Deen Dayal Upadhyaya College, University of Delhi from July 2009 to May 2010. She has worked as an Assistant Professor in Department of Electronics, Acharya Narendra Dev College, University of Delhi from August 2008 to April 2009. She worked as a Design Engineer in Saora Informatics India Pvt. Ltd., New Delhi from July-2005 to October-2005.

Her doctoral research involves modeling, design and simulation of Sub-100nm gate engineered Grooved Gate/Concave MOSFET for RFIC design and wireless applications, modeling and simulation of Insulated Shallow Extension (ISE) MOSFET for RF and microwave applications; and HEMT structures modeling for high performance microwave circuits. Her other areas of interests and activities cover VHDL implementation, FPGA realization and Board-Level experimentation of digital-based modern communication system designs. She has authored or co-authored more than 89 papers in various international and national journals and conferences. She has been awarded the "Best Student Paper" award in Indian Microelectronics Society 2007 (IMS-2007) Conference held in August 2007, Chandigarh, India. She has received a full fellowship in the IWPSD-2007 Conference, held in Mumbai, India.

Dr. Chaujar is an executive member of the IEEE-Electron Devices Society- Delhi Chapter, a Life member of the Semiconductor Society of India, Member of International Association of Engineers, Hongkong and Member of IEEE Communication Society. She is a reviewer of Journal Of Electronics and Electrical Engineering Research, Physica-E: Low-Dimensional Systems and Nanostructures, IETE Technical Review, International Journal of Physical Sciences (IJPS), International Journal of Numerical Modeling: Electronic Networks, Devices and Fields and Reviewer of

International Conference - Asia Pacific Microwave Conference (APMC)-2008, Hong Kong. Her name also appeared in the Marquis Who's Who in the World and Who's Who in America, 2010. She has also visited Japan in August 2005; USA in December 2007, August 2008 and June 2010; and Hongkong in December 2008.

**Mridula Gupta** (SM'09) received the B.Sc. degree in physics, the M.Sc. degree in electronics, the M.Tech. degree in microwave electronics, and the Ph.D. degree in optoelectronics from the University of Delhi, Delhi,

India, in 1984, 1986, 1988, and 1998, respectively. Since 1989, she has been with the Department of Electronic Science, University of Delhi South Campus, New Delhi, India, where she was previously a Lecturer and is currently an Associate Professor and with the Semiconductor Devices Research Laboratory. She has authored or coauthored approximately 235 publications in international and national journals and conference proceedings. She has supervised 12 Ph.D. students. She contributed the chapter entitled "MOSFET Modeling" in the *Encyclopedia on RF and Microwave Engineering* (Wiley, 2005). Her current research interests include modeling and simulation of MOSFETs, MESFETs, and HEMTs for microwave-frequency applications.

Dr. Gupta is a Fellow of the Institution of Electronics and Telecommunication Engineers (India) and a Life Member of the Semiconductor Society of India. She was the Secretary of the 2004 Asia–Pacific Microwave Conference, and was General Secretary of 12<sup>th</sup> ISMOT 2009 which were held in New Delhi, India.