# 부 스큐 지연 방식과 피드포워드 방식을 사용한 링 발진기의 대신호 해석

논 문 59-7-25

# A Large-Signal Analysis of a Ring Oscillator with Feed-Forward and Negative Skewed Delay

이 정 광\*・이 순 재\*\*・정 항 근<sup>†</sup> (Jeong-Kwang Lee·Soon-Jai Yi·Hang-Geun Jeong)

**Abstract** - This paper presents a large signal analysis of ring-type oscillators with feed forward and negative skewed delay scheme. The analysis yields the frequency increase factor due to two schemes. The large signal analysis is needed, because small signal model is limited to the initial stage of oscillation[1]. For verification of the frequency increase factor, simulation were done under the same conditions for the two different types of ring oscillators, i.e., with and without feed forward and negative skewed delay scheme. Simulation results are in good agreement with predictions based on analysis.

Key Words: Negative Skewed Delay, Ring oscillator, Feed Forward, NSD

#### 1. 서 론

최근 RF(Radio Frequency)를 사용하는 기기들이 급증하여 고속으로 동작하는 회로들이 중요시되고 필요성이 증대되고 있다. 특히 PLL은 무선통신을 포함한 많은 응용에 이용되고 있어 다양한 연구가 진행되고 있다. 그 중 VCO(Voltage Controlled Oscillator)는 PLL의 성능을 결정하는 중요한 블록이며 LC VCO와 ring VCO로 나뉜다. LC VCO는 높은 위상잡음 특성을 요구하는 PLL에 사용되지만 인덕터를 양질로 제작하기 어렵고, 넓은 면적을 차지하는 문제점이 있다 [2-3]. Ring VCO는 구조가 간단하고, 제작 시 LC VCO 보다적은 면적으로 제작할 수 있으며 다중위상 클록 발생과 넓은 주파수 가변 범위를 갖는다[3-4]. 그러나 ring VCO는 동작속도에 제한이 있으며, 이러한 문제를 극복하기 위하여 NSD(Negative Skewed Delay) 회로와 피드포워드 방식의회로가 제안되었다[5-6].

NSD 구조는 지연단의 PMOS 입력에 3단 앞단의 출력을 연결하여 지연단의 지연시간의 2배만큼 먼저 풀업시킴으로써 상승천이 시간을 줄여 VCO의 발진주파수를 높이는 방식이다. NSD 구조를 이용한 VCO는 소신호 모델을 사용하여 분석 되었다[7].

그러나 소신호 모델은 VCO의 발진 초기에만 적용 가능하다는 문제점을 가지고 있다. 피드포워드 방식은 풀다운 회로에도 NSD를 적용하여 발진주파수를 높이는 방식이다.

\* 준 회 원 : 전북대학 전자정보공학부 석사

\*\* 정 회 원 : 전북대학 전자정보공학부 박사과정

† 교신저자, 정회원 : 전북대학 전자공학부 교수

E-mail : hgjeong@jbnu.ac.kr 접수일자 : 2009년 12월 15일 최종완료 : 2010년 6월 25일 본 논문에서는 기존 NSD 구조에 피드포워드 방식의 메카니즘을 접목시켜 상승천이, 하강천이 시간을 모두 줄여 발진주파수를 최대한 상승시킬 수 있는 FFNSD(Feed Forward and Negative Skew Delay) 지연단을 제안하였다. 이 지연단을 사용하여 7단으로 구성된 ring VCO를 설계하였고 기존의 ring VCO와 발진주파수를 비교하였다. 또한 대신호모델을 통해 NSD 및 FFNSD 방식을 사용한 VCO의 발진주파수를 해석하였고 발진주파수의 증가량도 분석해 제안한회로의 효율성을 보였다.

### 2. 대신호 분석

## 2.1 기존 지연방식

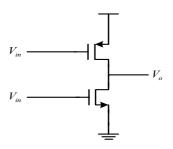

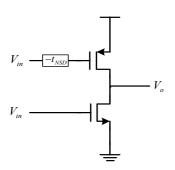

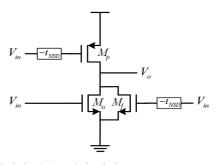

그림 1은 CMOS 인버터를 지연단으로 사용하는 기존 발 진기의 지연단 개념도이다.  $M_p$ 에 입력되는 신호와  $M_n$ 에 입력되는 신호는 같은 입력신호이다.

그림 1 기존 지연단을 갖는 단일단 개념도 Fig. 1 Concept of conventional delay cell

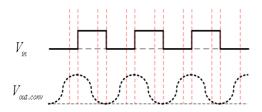

그림 2는 기존의 지연단을 갖는 회로에 입력으로 구형파를 인가한 경우의 출력파형을 나타내고 있으며, 출력 캐패시턴스 영향으로 출력파형은 입력신호와 위상차가 발생하게 된다.

그림 2 기존 지연소자의 출력 파형

Fig. 2 Output waveform of conventional delay cell

#### 2.1.1 하강천이

그림 3은 기존의 지연단에 상승입력이 가해질 경우의 하 강천이 파형을 나타내고 있다. t=0이 되어 입력신호가 인 가되면 그림 3과 같은 출력파형을 나타낸다.  $M_{\rm n}$ 은 포화영역에서 동작하며, 이때의 출력 노드 전압은 (1)같이 표현된다 [9]-[11].

그림 3 일반적 지연소자의 하강천이 출력 파형

Fig. 3 Output waveform of conventional delay cell during high-to-low transition

$$C_{L} \frac{dV_{o}(t)}{dt} = -I_{DSAT} = -\frac{1}{2} k_{n} (V_{DD} - V_{th})^{2}$$

(1)

채널 길이 변조 효과는 무시하였고, 초기 조건 $V_o(t=0)$  =  $V_{DD}$ 을 적용하면 (2)가 나온다.

$$V_{o}(t) = V_{DD} - \frac{1}{2C_{L}} k_{n} (V_{DD} - V_{th})^{2} \cdot t$$

(2)

$V_o(t) \leq V_{DD} - V_{th}$ 가 되면  $M_n$ 는 트라이오드영역에서 동작하는데 이때를  $t=t_1$ 라고 하면 (3)처럼 표현된다.

$$t_1 = \frac{C_L V_{th}}{\frac{1}{2} k_n (V_{DD} - V_{th})^2} \tag{3}$$

이번에는  $t>t_1$  이라 할 때, 출력 노드 전압은 다음과 같이 표현가능하다.

$$C_{L} \frac{dV_{o}(t)}{dt} = -k_{n} \left\{ V_{DD} - V_{th} - \frac{1}{2} V_{o}(t) \right\} \cdot V_{o}(t)$$

(4)

dt항과  $dV_o(t)$ 항을 분리시키고  $V_o(t)$ 에 대하여 정리하면 (5) 를 얻을 수 있다.

$$V_{o}(t) = (V_{DD} - V_{th}) \cdot \frac{2}{1 + e^{\frac{t - t_{1}}{R_{n}C_{L}}}}$$

(5)

$t_{pHL}$ 은  $V_o(t) = \frac{1}{2} \, V_{DD}$  되는 시간으로 정의된다.

$$\frac{t_{pHL} - t_1}{R_n C_L} = \ln \left| \frac{2(V_{DD} - V_{th})}{V_o(t)} - 1 \right|$$

(6)

$$t_{pHL} = t_1 + R_n C_L \cdot \ln \left| 3 - \frac{4 V_{th}}{V_{DD}} \right|$$

(7)

$t_1$ 에 관한 식을 대입하면  $t_{pHL}$ 을 구할 수 있다.

$$t_{pHL} = R_n C_L \cdot \left( \frac{2 \frac{V_{th}}{V_{DD}}}{1 - \frac{V_{th}}{V_{DD}}} + \ln \left( 3 - \frac{4 V_{th}}{V_{DD}} \right) \right)$$

(8)

#### 2.1.2 상승천이

그림 4는 하강입력신호가 입력될 때의 출력파형을 나타내고 있다.  $V_i(t)$ 가  $V_{DD}$ 에 있다가 t=0인 시점에 GND로 변한후 계속해서 GND에서 머무르는 경우 출력전압은 원래 GND에 있다가 t>0인 시간 영역에서 시간에 변화함에 따라 점차 증가하여  $V_{DD}$ 로 수렴한다.

그림 4 일반적 지연소자의 상승천이 출력 파형

Fig. 4 Output waveform of conventional delay cell during low-to-high transition

$V_0(t)=V_{thp}$ 가 되는 시작을  $t=t_1$ 이라고 하면  $t\leq t_1$  일 때의 출력노드 전압은 다음과 같이 표현 가능하다.

$$C_L \frac{dV_o(t)}{dt} = I_{DSAT} = \frac{1}{2} k_p (V_{DD} - V_{th})^2$$

(9)

추후 계산은 하강천이 계산과정과 같이 계산을 하면  $t_1$  시간 (11)과  $t_{vLH}$ 를 구할 수 있다.

$$t_1 = \frac{C_L V_{th}}{\frac{1}{2} k_p (V_{DD} - V_{th})^2} \tag{10}$$

$$t_{pLH} = t_1 + R_p C_L \cdot \ln \left| 3 - \frac{4 V_{th}}{V_{DD}} \right| \tag{11}$$

$$t_{pLH} = R_{p}C_{L} \cdot \left( \frac{2\frac{V_{th}}{V_{DD}}}{1 - \frac{V_{th}}{V_{DD}}} + \ln\left(3 - \frac{4V_{th}}{V_{DD}}\right) \right)$$

(12)

#### 2.2 NSD(Negative Skewed Delay) 방식

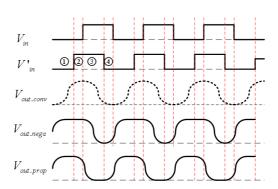

그림 5는 NSD 지연 방식의 개념도이며, 인버터를 지연단 으로 사용하는 구조와 차이점은  $M_p$ 에 개념적인 NSD 입력이 들어가고 있다. 따라서  $M_p$ 로 들어가는 신호가  $M_n$ 로 들어 가는 신호보다 시간상으로  $t_{NSD}$  만큼 앞서 있는 신호이다.

그림 5 NSD 지연방식의 개념도 Fig. 5 Concept of NSD cell

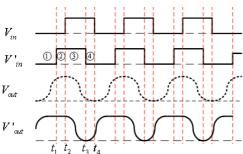

그림 6은 기존 지연단과 NSD 지연방식을 이용하는 지연단 의 동작 메카니즘 차이를 보여 주고 있다. 인버터 지연소자 는  $M_p$ 와  $M_n$ 의 on, off 되는 시간이 같지만 NSD 소자는  $M_{p}$ 와  $M_{n}$ 의 on, off 시간이 같지 않고  $M_{p}$ 의 입력이  $M_{n}$ 의 입력 시간보다  $t_{NSD}$  만큼 먼저 on, off 되는 구조이다.

그림 6 기존 지연소자와 NSD 소자의 출력 파형 Fig. 6 Output waveforms of conventional and NSD cell

NSD 소자는  $M_p$ 의 입력신호가 먼저 입력되어 그림 6의 ④, ①구간이 일반적인 지연소자와 다르게 된다.  $M_n$ 에 신호가 입력될 때  $M_n$ 에 2단 앞의 신호가 입력되는 구조로서  $t_{NSD}$ 는  $2t_P(t_P$  = 한단의 지연 시간)값을 가진다.

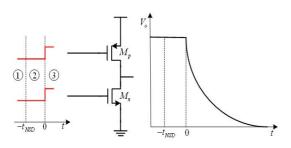

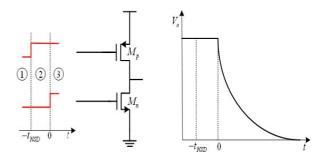

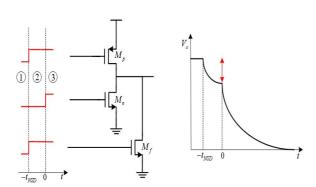

#### 2.2.1 하강천이

그림 6의 ③구간은 입력신호로 up 신호가 입력되는 구간 이다. 그리고 ③, ④ 구간을 따로 표시한 것이 그림 7이다. NSD 회로의 발진주파수 향상 메카니즘은 상승천이 시간을 NSD를 사용하지 않은 회로에 비하여 상대적으로 줄이는 방 법이다. 반면 NSD 회로의 하강천이 특징은 NSD 방식을 사 용하지 않는 회로와 동일한 동작특성을 갖는다.

그림 7 NSD 지연소자의 하강천이 파형

Fig. 7 Output waveform of NSD cell during high-to-low transition

그림 7을 보면 NSD 구조로 인하여  $M_p$ 에 상승입력이  $t=-t_{\mathit{NSD}}$ 에 입력되고 t=0일 때  $M_n$ 에 상승입력 신호가 인가된다. ①구간일 때  $V_o = V_{DD}$  값을 갖으며  $M_n$ 의 입력신 호 보다  $t_{NSD}$  만큼 먼저  $M_{n}$ 에 입력신호가 가해지지만 ② 구간에서  $M_p$ 가 off 되어도  $V_o$ 은 플로팅되어 기존전압  $V_{DD}$ 을 유지한다. 그리고 t=0에  $M_n$ 에 입력신호가 인가되면 출 력전압이 하강천이를 한다. 따라서 하강천이 구간에서는 NSD 구조를 사용하여도 특별한 개선사항이 없으며 기존회 로와 동일한 특성을 갖는다. 앞서 정의한  $V_o(t)$ ,  $t_1$ ,  $t_{pHL}$ 을 다시 적용시킬 수 있다.  $t \le t_1$ 인 경우의 출력전압은 (13)과

$$V_{o}(t) = V_{DD} - \frac{1}{2C_{r}} k_{n} (V_{DD} - V_{th})^{2} \cdot t \tag{13} \label{eq:13}$$

$t_1 < t$ 인 경우의 출력전압은 (14)처럼 표현된다.

$$V_o(t) = (V_{DD} - V_{th}) \cdot \frac{2}{1 + e^{R_n C_L}}$$

(14)

$M_n$ 이 트라이오드영역에서 동작하기 시작 시점인  $t_1$ 는 (15)로 정의할 수 있다.

$$t_1 = \frac{C_L V_{th}}{\frac{1}{2} k_n (V_{DD} - V_{th})^2}$$

(15)

$V_o(t) = \frac{1}{2} V_{DD}$ 로 정의되는  $t_{pHL}$ 은 (16)으로 표현가능하다.

$$t_{pHL} = R_n C_L \cdot \left( \frac{2 \frac{V_{th}}{V_{DD}}}{1 - \frac{V_{th}}{V_{DD}}} + \ln \left( 3 - \frac{4 V_{th}}{V_{DD}} \right) \right)$$

(16)

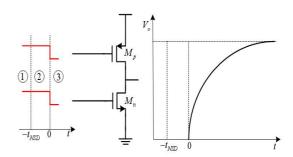

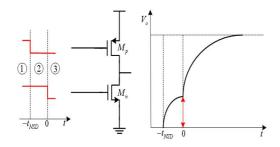

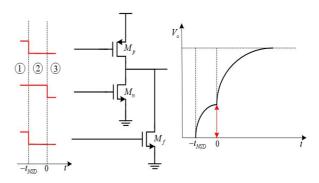

#### 2.2.2 상승천이

그림 6의 ④구간은 입력신호로 하강 신호가 입력되는 구 간이다. 그리고 ④, ①구간의 출력파형을 나타낸 것이 그림 8이다. NSD 방식은 이 구간의 시간을 단축시킴으로써 발진 주파수를 향상시키는 메카니즘이다.

그림 8 NSD 지연소자의 상승천이 파형

Fig. 8 Output waveform of NSD cell during low-to-high transition

②번 구간에서는  $t=-t_{NSD}$  일 때  $M_p$ 에 하강신호가 입력 되면  $M_n$ 가 on이 되어 기존회로와 상이한 동작특성을 갖게 된다.  $-t_{NSD} \leq t \leq 0$  구간동안 on이 되어진  $M_{p}$ 에 의하여 출력노드에 일정전압을 선행 충전시킴으로서 t=0가 되어  $M_n$ 에 입력신호가 인가될 때 출력전압은 일정전압이 충전된 시점에서 시작하게 되어 출력전압이  $V_{DD}$ 에 도달하는 시간이 단축되는 구조를 갖고 있다. 2번 구간에서는  $M_p$ 는 포화,  $M_n$ 는 트라이오드 영역에서 동작하므로 (17)로 표현할 수 있다

$$C_L \frac{dV_o(t)}{dt} = \frac{1}{2} k_p (V_{DD} - V_{th})^2 - k_n \left( (V_{DD} - V_{th}) V_o(t) - \frac{1}{2} V_o(t)^2 \right)$$

(17)

dt항과  $d\,V_o(t)$ 항을 분리하고  $V_o(t)$ 에 관하여 표현하면 (18)과 같이 ②번 구간의 출력전압 함수를 구할 수 있다.

$$V_{o.LH1}(t) = k_n \left(V_{DD} - V_{th}\right) + \frac{\frac{1}{R_{np}} \cdot \left(1 + e^{\frac{(t - t_1)}{R_{np}C_L}}\right)}{k \cdot \left(1 - e^{\frac{(t - t_1)}{R_{np}C_L}}\right)}$$

(18) 그림 10 제안한 지연소자의 출력파형

③번 구간의 출력전압은 기존의 회로와 같은 천이 특성을 갖는다. ③번구간의 출력전압을 다시 표현하면 (19)처럼 나 타낼 수 있다.

$$V_{o.LH2}(t) = V_{DD} - (V_{DD} - V_{o.LH1}(t_{NSD})) \frac{2}{1 + e^{\frac{t}{R_{tp}C_L}}}$$

(19)

$(16) \qquad \frac{V_{o,LH1}(t_{NSD})}{\frac{1}{2}V_{DD}-V_{o,LH1}(t_{NSD})} 만큼 충전되어 있기 때문에 <math>t_{pLH}$ 는  $\frac{1}{2}V_{DD}-V_{o,LH1}(t_{NSD})$ 만큼 충전되는 시간으로 정의할 수 있다.

$$t_{pLH} = R_{p}C_{L} \cdot \ln \left( 3 - \frac{4V_{o.LH1}(t_{NSD})}{V_{DD}} \right) \tag{20}$$

#### 2.3 FFNSD(Feed Forward Negative Skewed Delay) 방식

그림 9는 제안한 지연소자의 개념도이다. CMOS 인버터에 NSD 지연구조를 갖도록  $M_n$ 에  $M_n$ 로 입력되는 신호보다 두 단 앞선 신호를 인가하고, 추가적으로 피드포워드 구조를 갖도록 기존  $M_n$ 에 병렬로  $M_f$ 를 추가하였고 입력으로는  $M_f$ 와 같이 두 단 앞선 신호를 인가하여 주는 구조이다.

그림 9 제안한 지연소자의 개념도

Fig. 9 Concept of proposed delay cell

그림 10은 기존회로의 출력파형, NSD 지연소자를 갖는 회로 의 출력파형 그리고 제안한 지연소자를 갖는 회로의 출력파 형을 나타내고 있다. 출력파형을 보면 알 수 있는 바와 같이

Fig. 10 Output waveforms of proposed delay cell

지연소자를 갖는 회로와 달리 상승천이, 하강천이 두 구간 모두 시간이 기존 회로보다 줄어든 것을 알 수 있다. 이는 상승천이 구간에서는 NSD 지연방식이 적용되어 상승시간이 줄어들며, 하강천이 구간에서는 피드포워드 방식이 적용되어 하강시간을 감소시켜 발진주파수를 향상시키는 메카니즘이다.

#### 2.3.1 하강천이

하강천이 구간은 ④, ①구간이며 이 구간을 자세히 다시 표현한 것이 그림 11이다. 이 구간에서 지배적인 역할을 하는 것은 피드포워드 방식이다. ④구간 초기값인  $V_o = V_{DD}$ 이었던 출력전압을 t = 0이 되기 전  $-t_{NSD} \leq t < 0$  동안  $M_f$ 에 의하여 출력전압이 선행 방전되어 하강천이 시간이단축되는 방식이다. 이때 선행 방전되는 양은  $M_n$ 과  $M_f$ 의 크기 비율에 따라 달라진다.  $t = -t_{NSD}$  이전 시간에는 모든 MOSFET에 하강 신호가 입력되므로 출력전압은  $V_{DD}$ 값을 갖는다.  $-t_{NSD} < t$ 이 되면  $M_p$ ,  $M_f$ 에 up 신호가 입력되어  $M_p$ 는 off 되고 반면  $M_f$ 는 on 되어 선행 방전을 시작한다. t = 0가 되어  $M_n$ 에 up 신호가 입력되면  $M_n$ 이 on되어 방전을 하는데, 방전 시작점이  $V_{DD}$ 가 아닌  $V_{DD} - V_{o.HL1} \times (t_{NSD})$  값을 가지므로 하강천이 시간이줄어들게 된다.

**그림 11** NSD 지연소자의 하강천이 파형

Fig. 11 Output waveform of NSD cell during high-to-low transition

$-t_{NSD} \leq t \leq 0$  구간에서는  $M_p$ 와  $M_f$ 에  $t_{NSD}$  만큼 일찍 입력이 가해지므로  $-t_{NSD} \leq t \leq 0$  구간의 출력전압은  $C_L \frac{dV_o(t)}{dt}$   $= k_p \bigg\{ (V_{DD} - V_{th}) \, V_o(t) - \frac{1}{2} \, V_o(t)^2 \bigg\} - \frac{1}{2} k_{nf} (V_{DD} - V_{th})^2 \, \mathrm{Z} \quad \mathrm{E} \, \mathrm{Te} \,$

$$V_{o.HL1}(t) = V_{DD} - k_p (V_{DD} - V_{th}) + \frac{\frac{1}{R_{np}} \cdot \left(1 + e^{\frac{(t - t_1)}{R_{np}C_L}}\right)}{k_n \cdot \left(1 - e^{\frac{(t - t_1)}{R_{np}C_L}}\right)}$$

$$\frac{1}{R_{fp}} = \sqrt{k_p^2 (V_{DD} - V_{th})^2 - k_p k_{nf} (V_{DD} - V_{th})^2}$$

(21)

$0 \le t$ 인 구간에서는 기존 회로와 같은 천이특성을 갖는다.

$$V_{o.HL2}(t) = (V_{DD} - V_{o.HL1}(t_{NSD})) \frac{2}{1 + e^{\frac{t}{R_D C_L}}}$$

(22)

이를 바탕으로  $t_{pHL}$ 을 구하여 보면 다음과 같다.

$$t_{pHL} = R_{\!fp} C_{\!L} \, \bullet \, \ln \biggl( 3 - \frac{4 \, V_{o.HL1} (t_{NSD})}{V_{DD}} \biggr) \eqno(23)$$

#### 2.3.2 상승천이

상승천이 구간은 그림 10의 ②, ③구간이며 이 구간은  $M_f$ 의 입력이  $M_p$ 와 같기 때문에 추가적으로 출력전압에 영향을 주지 않는다. 따라서 이 구간은 NSD 지연 소자의 상승천이 구간과 같은 특성을 갖는다.

그림 12 NSD 지연소자의 상승천이 파형

Fig. 12 Output waveform of NSD cell during low-to-high transition

②번 구간에서는  $t=-t_{NSD}$  일 때  $M_p$ 에 하강 신호가 입력되면  $M_p$ 가 on 되어 기존회로와 상이한 동작특성을 갖게된다.  $-t_{NSD} \le t \le 0$  구간동안 on이 되어진  $M_p$ 에 의하여출력노드에 일정전압을 충전시킴으로서 t=0일 때  $M_n$ 에 입력신호가 인가되고 출력전압은 일정전압이 충전된 시점에서시작하게 되어 출력전압이  $V_{DD}$ 에 도달하는 시간이 단축되는 구조를 갖고 있다. ②번 구간에서는  $M_p$ 는 포화  $M_n$ 는 트라이오드영역에서 동작하므로 (24)처럼 표현 할 수 있다.

$$C_L \frac{dV_o(t)}{dt} = \frac{1}{2} k_p (V_{DD} - V_{th})^2 - k_n \left( (V_{DD} - V_{th}) V_o(t) - \frac{1}{2} V_o(t)^2 \right)$$

(24)

dt항과  $dV_o(t)$ 항을 분리하고  $V_o(t)$ 에 관하여 표현하면 (25)처럼 ②번 구간의 출력전압 함수를 구할 수 있다.

$$V_{o.LH1}(t) = k_n \left( V_{DD} - V_{th} \right) + \frac{\frac{1}{R_{np}} \cdot \left( 1 + e^{\frac{(t - t_1)}{R_{np}C_L}} \right)}{k_n \cdot \left( 1 - e^{\frac{(t - t_1)}{R_{np}C_L}} \right)}$$

(25)

③번 구간은 기존의 회로와 같은 천이 특성을 가지며 ③번 구간의 출력전압 함수는 (26)과 같다.

$$V_{o.LH2}(t) = V_{DD} - (V_{DD} - V_{o.LH1}(t_{NSD})) - \frac{2}{1 + e^{\frac{t}{R_{\eta}C_L}}}$$

(26)

$V_{o1}(t_{NSD})$ 만큼 출력전압이 선행 충전되어 있기 때문에  $t_{pLH}$ 는  $rac{1}{2}\,V_{DD}-V_{o.LH1}(t_{NSD})$ 만큼 충전되는 시간으로 정의할 수 있다.

$$t_{pLH} = R_{np} C_L \cdot \ln \left( 3 - \frac{4 V_{o.LH1} (t_{NSD})}{V_{DD}} \right)$$

(27)

#### 2.4 발진주파수

대신호 해석을 통하여 얻은 상승, 하강천이 특성을 이용하여 발진주파수를 구하면 기존회로와 NSD 지연소자를 사용한 회로, 본 논문에서 제안한 회로의 경우에 대해서 각각 발진주파수를 비교해 볼 수 있다. 먼저 기존 회로의 발진주파수는 상승천이와 하강천이 구간의 전파지연을 이용하여 개략적으로 계산해 볼 수 있다.

$$f_{osc.conv} = \frac{1}{NC_{L} \cdot \left(R_{n} \cdot \left(\frac{\frac{2V_{th}}{V_{DD}}}{1 - \frac{V_{th}}{V_{DD}}} + \ln\left|3 - \frac{4V_{th}}{V_{DD}}\right|\right) + R_{p} \cdot \left(\frac{\frac{2V_{th}}{V_{DD}}}{1 - \frac{V_{th}}{V_{DD}}} + \ln\left|3 - \frac{4V_{th}}{V_{DD}}\right|\right)\right)}$$

(28)

NSD 지연소자를 이용한 발진주파수는 동일한 절차를 통하여 NSD 지연소자를 사용한 회로의 발진주파수를 얻을 수 있다.

$$f_{osc.NSD} = \frac{1}{NC_{L} \cdot \left( \frac{2V_{th}}{R_{n}} \cdot \left( \frac{\frac{2V_{th}}{V_{DD}}}{1 - \frac{V_{th}}{V_{DD}}} + \ln \left| 3 - \frac{4V_{th}}{V_{DD}} \right| \right) + R_{np} \cdot \ln \left| 3 - \frac{4V_{o.LH1}(t_{NSD})}{V_{DD}} \right| \right)}$$

$$(29)$$

(28)과 (29)를 비교해보면 분모의 (b)값이 줄어든 것을 알수 있다. 그리고 (29)는  $t_{NSD}$ 에 의하여 값이 변화하는 것을알수 있다. 이것은 출력 노드에 선행 충전되는 양이  $t_{NSD}$ 에 따라 달라지기 때문이다. NSD 지연 방식과 피드포워드 방식을 접목시킨 제안된 회로의 발진주파수는 같은 방식으로구할수 있다.

$$f_{osc.proposed} = \frac{1}{NC_{L} \cdot \left(R_{fp} \cdot \ln \left| 3 - \frac{4V_{o.HL1}(t_{NSD})}{V_{DD}} \right| + R_{np} \cdot \ln \left| 3 - \frac{4V_{o.LH1}(t_{NSD})}{V_{DD}} \right| \right)}{(a)}$$

$$(30)$$

(30)을 살펴보면 NSD 지연소자는 상승천이 구간에서 시간적 이득을 보기 때문에 분모의 (a)가 변화한 반면 제안한 회로는 상승, 하강천이 모두 시간적 이득을 보기 때문에 분모의 (a), (b) 모두 변화한 것을 알 수 있다.  $\frac{V_{th}}{V_{DD}}$ = 0.3이라고 할경우 각각의 발진주파수는 (31)과 같다.

$$f_{osc.conv} \approx 0.34 \cdot \frac{1}{NRC}$$

,  $f_{osc.NSD} \approx 0.45 \cdot \frac{1}{NRC}$ ,

$$f_{osc.pro} \approx 0.67 \cdot \frac{1}{NRC}$$

(31)

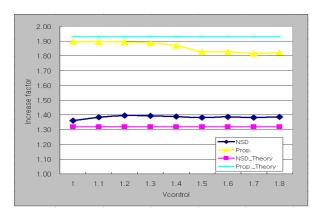

이는 NSD 지연소자를 사용할 시에 기존 발진주파수보다 1.32배 향상된 발진주파수를 기대할 수 있으며, NSD 지연 방식과 피드포워드 방식을 접목시킨 방법을 사용할 시에는 기존 발진주파수보다 1.93배 향상된 발진주파수를 기대할 수 있다.

#### 3. 시뮬레이션

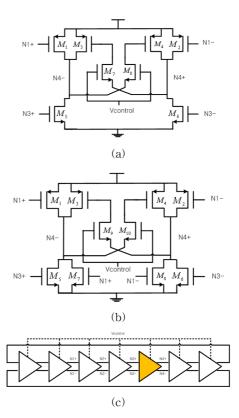

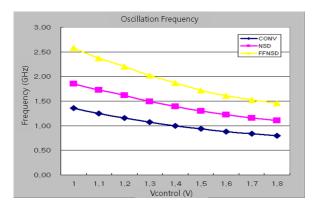

본 논문에서는 그림 13(a)와 같이 NSD를 갖는 기존 회로에 FFNSD 구조를 적용하여 그림 13(b)의 지연단을 제안하였다. 제안된 지연단을 사용한 VCO와 NSD를 활용한 VCO, 기존의인버터 방식을 사용한 VCO를 설계하여 그림 13(c)처럼 7단으로 구성하였고 VCO 각각의 발진주파수를 시뮬레이션 하였다. 앞절에서 분석한 결과와 마찬가지로 FFNSD를 사용한지연단의 VCO가 동일한 제어전압에서 상승 및 하강 천이시간을 단축시켜 VCO의 발진주파수를 높였다. 그림 14는 7단으로 설계된 각각의 VCO가 제어전압의 변화에 따른 발진주파수를 보여준다. 설계된 ring VCO는 표준 0.18µm CMOS공정을 사용하여 시뮬레이션 하였다.

그림 13 지연단 회로 (a) NSD, (b) FFNSD, (c) 7단 ring VCO Fig. 13 Delay cell circuit (a) NSD, (b) FFNSD, (c) 7-stage ring VCO

그림 14 제어전압에 따른 발진주파수

Fig. 14 The simulated oscillation frequency vs. the control voltages

그림 15는 제안한 지연방식을 사용하는 발진기와 NSD 지연 방식을 사용한 발진기의 발진주파수 증가량을 보여주고 있다. 그림 14의 내용을 토대로 발진주파수 증가량을 나타내었으며, 이 값은 절대적인 값이 아니다. 앞서 제시한 대신호 분석을 통한 발진주파수 함수를 보면 알 수 있듯이 발진주파수 함수는  $M_p$ 의 폭과  $t_{NSD}$ 를 알면 발진주파수를 예측할 수 있으며, 반대로 원하는 발진주파수를 만들기 위하여  $M_p$ 의 폭과  $t_{NSD}$ 를 구할 수 있다.

그림 15 제어전압에 따른 발진주파수 증가량

Fig. 15 The simulated frequency increase factor vs. the control voltages

#### 4. 결 론

본 논문에서는 FFNSD 구조를 가지는 지연단을 제안하였으며 이 지연단을 활용하여 7단 ring VCO를 설계하였다. 제안된 지연단은 대신호 모델을 사용하여 분석하였으며 발진주과수 증가량은 NSD 방식이 약 1.32배, FFNSD 방식은 1.93배이다. 시뮬레이션을 이용한 발진주과수 증가량은 각각 1.37배, 1.86배이었다. 대신호 분석을 통한 발진주과수 증가량이 시뮬레이션을 통한 발진주과수 증가량 값과 10% 오차범위 안에 있다.

#### 감사의 글

본 연구는 IDEC CAD tool과 BK(Brain Korea)21의 지원으로 수행되었습니다.

#### 참 고 문 헌

- [1] B. Razavi, Design of Analog CMOS Integrated Circuits, pp. 484–495, McGraw-Hill, 2001.

- [2] De Muer, Borremans, Steyaert, and Li Puma, "A 2-GHz low-phase-noise integrated LC-VCO set with flicker-noise up conversion minimization" IEEE J. Solid-State Circuits, vol. 35 no. 7, Jul. 2000.

- [3] A. Hajimiri and T. H. Lee, "A general theory of phase noise in electrical oscillators," IEEE J. Solid-State Circuits, vol. 33, pp. 179-194, Feb. 1998.

- [4] Yalcin Alper Eken and John P. Uyemura, "A 5.9-GHz voltage-controlled ring oscillator in 0.18-µm CMOS" IEEE J. Solid-State Circuits, vol. 39 no. 1, Jan. 2004.

- [5] Seog-Jun Lee, Beomsup Kim, and Kwyro Lee, "A Novel High-Speed Ring Oscillator for Multiphase Clock Generation Using Negative Skewed delay Scheme" IEEE J. Solid-State Circuits, Vol. 32. NO. 2. Feb. 1997.

- [6] F. H. Gebara, J. D. Schaub, a. J. Drake, K.J. Nowka, R. B. Brown, "4.0Ghz 0.18um CMOS PLL based on an interpolative oscillator", Symp. on VLSI Circuits 2005, pp. 100–103, Jun. 2005.

- [7] 김성하, 김삼동, 황인석, "향상된 부 스큐 고속 VCO를 이용한 초고주파 PLL," 대한전자공학회 SC편, vol. 42, pp. 315-327, Jun. 2005.

- [8] Ge Yan, Chen Zhongjian, and Jl Lijiu, "Design of CMOS high speed self-regulating VCO using negative skewed delay scheme," Proc. of ICSICT, pp. 1333-1336, Feb. 2004.

- [9] Sung-Mo Kang, Yusuf Leblebici, CMOS Digital Integrated Circuits, pp. 196–233, McGraw-Hill, 1999.

- [10] Jan M. Rabaey, Anantha Chandrakasan, Borivoje Nikolic, Digital Integrated Circuits, pp. 179–234, Prentice Hall, 1995.

- [11] Tim Grotjohn, Bernd Hoefflinger, "A parametric short-channel MOS transistor model for subthreshold and strong inversion current" IEEE J. Solid-state Circuits, vol. 31 no. 2, Jun. 1984.

# 저 자 소 개

# 이 정 광 (李 廷 光)

2008년 전북대학교 전자정보공학부 졸업. 2010년 전북대학교 전자정보공학부 석사 졸업

<주관심분야: PLL, Ring-VCO>

# 이 순 재 (李 洵 在)

2007년 전북대학교 전자공학과 석사 졸업.

2007년~ 전북대학교 전자정보공학부 박 사과정

<주관심분야: PLL, Sigma-Delta ADC>

# 정 항 근 (丁 恒 根)

1979년 한국과학기술원 전기전자공학 석 사 졸업.

1989년 플로리다대학교 전기공학 박사졸업.

1979년~1982년 한국 전자통신연구소 재직 1991년~현재 전북대학교 전자공학부 교수.

<주관심분야: 주파수 합성기, Low-voltage Low-power analog circuit, High speed data Interface circuit>