[논 문] 한국재료학회지 Kor. J. Mater. Res. Vol. 20, No. 5 (2010)

# 실리콘 기판위에서의 Cr-Doped SrZrO3 박막의 저항변화 특성

양민규\*,\*\* · 고태국\*\* · 박재완\*\*\* · 이전국\*<sup>†</sup>

\*한국과학기술연구원 광전자재료센타, \*\*연세대학교 전자전기공학과

\*\*\*위스콘신 메디슨대학교 재료공학과

# Resistive Switching Properties of Cr-Doped SrZrO<sub>3</sub> Thin Film on Si Substrate

Min Kyu Yang\*,\*\*, Tae Kuk Ko\*\*, Jae-Wan Park\*\*\* and Jeon-Kook Lee\*

\*Optoelectronic Materials Center, Korea Institute of Science and Technology, Seoul 136-791, Korea

\*\*Department of Electrical and Electronic Engineering, Yonsei Univ., Seoul 120-749, Korea

\*\*\*Department of Materials Science and Enginnering, University of Wisconsin-Madison, Madison, WI 53705, USA

(2010년 4월 22일 접수 : 2010년 5월 7일 최종수정 : 2010년 5월 7일 채택)

Abstract One of the weak points of the Cr-doped SZO is that until now, it has only been fabricated on perovskite substrates, whereas NiO-ReRAM devices have already been deposited on Si substrates. The fabrication of RAM devices on Si substrates is important for commercialization because conventional electronics are based mainly on silicon materials. Cr-doped ReRAM will find a wide range of applications in embedded systems or conventional memory device manufacturing processes if it can be fabricated on Si substrates. For application of the commercial memory device, Cr-doped SrZrO<sub>3</sub> perovskite thin films were deposited on a SrRuO<sub>3</sub> bottom electrode/Si(100)substrate using pulsed laser deposition. XRD peaks corresponding to the (112), (004) and (132) planes of both the SZO and SRO were observed with the highest intensity along the (112) direction. The positions of the SZO grains matched those of the SRO grains. A well-controlled interface between the SrZrO<sub>3</sub>:Cr perovskite and the SrRuO<sub>3</sub> bottom electrode were fabricated, so that good resistive switching behavior was observed with an on/off ratio higher than 10<sup>2</sup>. A pulse test showed the switching behavior of the Pt/SrZrO<sub>3</sub>:Cr/SrRuO<sub>3</sub> device under a pulse of 10 kHz for 10<sup>4</sup> cycles. The resistive switching memory devices made of the Cr-doped SrZrO<sub>3</sub> thin films deposited on Si substrates are expected to be more compatible with conventional Si-based electronics.

Key words <u>resistive switching</u>, SrZrO<sub>3</sub>, non-volatility.

#### 1. 서 론

현대 정보 통신사회는 문자, 음성 및 영상 등을 복합적으로 이용한 쌍방향 통신을 교환하기 위하여 더 많은 정보를 더욱 빠르게 처리 할 수 있는 능력을 가진 반도체 소자를 요구하고 있다. 또한 이러한 방대한 양의 정보를 저장하고 다시 사용하기 위한 저장장치의 생산능력은 경이로울 정도로 발전해 왔고 이에 따른 제품의 소형화 및 초고집적화가 이루어짐에 따라 박막 제조 공정기술과 박막 재료의 특성평가에 대한 연구 또한 활발히이루어지고 있다. 그러나 현재의 저장장치 중에서 휘발성메모리의 성장은 그 한계에 다다랐다는 분석과 이를 대체할 차세대 메모리의 개발에 박차를 가하고 있다. 이

적화가 가능한 비휘발성 메모리 소자 개발의 필요성이 그 어느 때보다도 커지고 있는 것 또한 의심의 여지가 없다. 이러한 배경은 기존의 DRAM 공정은 1-Transistor/ 1Capacitor (1T1R) 구조의 단위cell을 이루고 있는데, 소자 의 크기가 작아짐에 따라, capacitor공정의 난이도가 점 점 더 올라가게 되어, 높은 수율을 가지는 DRAM cell 의 제작이 매우 어렵게 되는데 있으며 기존 DRAM을 대 체할 수 있는 메모리의 필요성이 크게 요구되고 있다. 현 재 개발되고 있는 차세대 메모리는 DRAM의 고집적성과 낮은 소비 전력, frash 메모리의 비휘발성, SRAM (static random access memory) 의 고속 동작을 모두 구현하기 위한 시도가 이루어지고 있다. 최근 ITRS roadmap에 따 르면, 차세대 메모리로 유력하게 대두되고 있는 소자는 PRAM (phase change RAM), NFGM (nano floating gate memory), ReRAM (resitance RAM), PoRAM (polymer RAM), MRAM (magnetic RAM), 분자전자 소자 등이

러한 경제/산업적인 고용량 정보 저장에 필요한 초고집

<sup>†</sup>Corresponding author

E-Mail: jkleemc@kist.re.kr (J. -K. Lee)

있다. 그 중에서도 ReRAM (Resistance Random access memory)은 구조가 간단하고 on/off ratio 와 전력소비량 에서 기존의 메모리에 비해 많은 장점이 있다고 보고되 어 국내외로 많은 연구가 보고되고 있다. 적용가능 재료 로는 Cr-doped SrTiO<sub>3</sub>, 1) Cr-doped SrZrO<sub>3</sub> (SZO), 2) Pr<sub>0.7</sub>-Ca<sub>0.3</sub>MnO<sub>3</sub> (PCMO),<sup>3)</sup> PbZr<sub>0.52</sub>Ti<sub>0.48</sub>O<sub>3</sub> (PZT),<sup>4,5)</sup> NiO,<sup>6)</sup> La<sub>0.7</sub>-Ca<sub>0.3</sub>MnO<sub>3</sub> (LCMO), <sup>7)</sup>등이 연구되고 있다. 그 중 ReRAM 의 주요 연구분야는 바이너리계(NiO)와 PCMO perovskite 가 대두 되고 있다. 이 두 물질을 ReRAM 디바이스에 적용한다면 몇 가지 단점이 발생한다. NiO or PCMO device의 경우 on/off resistance 가 작거나 너무 큰 전압 에서 구동되어 많은 전력소비를 가져온다. 덧붙여 NiO 와 같은 바이너리계는 compliance current limit 을 요구 한다. 이것 또한 디바이스 회로구성면에서 단점으로 작용 한다. 또한, 아직까지 그 스위칭 메카니즘이 불분명하여 많은 연구자들에 의해 그 이론이 연구되고 있다. 최근 가 장 가능성이 있는 메카니즘은 oxygen ions의 migration 으로 발표되고 있다.<sup>8-11)</sup> 본 연구에서 우리는 이런 것을 해 결할 수 있는 Cr-doped SZO를 선택하였다. 즉 compliance current limit가 필요하지 않으며 on/off ratio와 스위칭 Reset 전류가 탁월해 ReRAM device 적용시 큰 장점이 되리라 사료된다. 그러나 Cr-doped SZO는 아직까지 같 은 계열의 perovskite 기판을 사용하여 그 특성을 구현 하고 있으며 반면 NiO-ReRAM 디바이스는 일찍이 Si기 반위에 적용해 성공하였다. Si 기판에 RAM의 제작은 상 용화를 위해 매우 중요한 사항 중에 하나이다. 12) 만약 Si 위에 증착하여 ReRAM 특성을 구현한다면 임베디드 시 스템이나 산업용 메모리제작에 좀 더 쉽게 적용되리라 사 료된다. 그러므로 본 연구에서는 Si 위에 Cr-doped SZO 을 증착하는 방법과 그에 따른 저항특성을 관찰하였다. 마지막으로 좀 더 상용화 가능성을 확인하기 위해 pulse 테스트를 통하여 이를 증명하였다.

## 2. 실험 방법

본 연구에서는 Si 위에서의 ReRAM 특성을 알아보기 위하여 Pt/SrZrO<sub>3</sub>/SrRuO<sub>3</sub>/Si 구조박막을 제작하였다. 중착하기 위해서 KrF 펄스 레이저 시스템을 이용하였으며 타겟은 각각 3N의 Cr (0.2 at%) doped SZO (insulator)와 SRO (bottom electrode)를 PRAXAIR사(USA)에서 주문 제작하여 사용하였다. 우수한 표면 조직을 위하여 기판의 전처리는 다음과 같이 실행하였다. 우선 - 아세톤 - 메탄올 - 에탄올에서 각각 10 분씩 초음파세척기를 통하여 유기 세척을 하였다. 세척이 끝난 기판은 시편 준비실을 통하여 중착챔버로 장입되었다. 중착 가스는 O<sub>2</sub>를 사용하였다. 1×10<sup>-6</sup>torr 이하의 base pressure로 유지한 후

O<sub>2</sub> 가스를 유입하였으며, 유량은 MFC로 조절하였다. 증 착 압력은 Baratron guage와 throttle valve controller 를 사용하여 조절하였으며 증착하는 동안 uniform한 박막을 형성하기 위해 stepping moter 을 이용하여 Target holder 을 회전시켰다. 먼저 기판위에 하부 메탈로 금속 산화 물 SRO 박막을 증착하였다. SRO가 하부전극의 역할을 하 려면 전도성이 중요하다. 그 조건을 만족하기 위한 실험 조건은 KrF excimer laser (Lambda phisik-compex-102) 펄스 레이저 시스템을 이용하여 radiation energy density 2 J/cm<sup>2</sup> 와 5 Hz 의 retention time 으로 증착하였다. 증 착 압력과 온도는 각각 250 mTorr 과 600℃로 증착하 였으며 그 때 200 nm의 두께의 비저항 428 μΩ·cm 의 전 도성 하부전극을 얻을 수 있었다. SRO/Si substrate 위에 ReRAM 특성을 가지는 Cr-doped SZO 박막을 증착하기 위해산소 분압 250 mTorr에서 실험을 수행하였으며 insitu annealing 을 통한 미세구조와 결정성에 따른 ReRAM 특성을 분석하였다. 마지막으로 상부 전극으로는 Pt를 사 용하였으며 150~300 μm² dia 의 size의 pad를 증착하기 위해 메탈 마스크를 사용하였고 증착 방법으로는 전형 적인 DC sputtering 방법을 사용하였다. 증착 후 결정성 관찰하기 위하여 분말 X-선 회절 분석(XRD, Model D8 ADVANCE / BRUKER) 을 행하였다. 이때 XRD 분석 은 Cu Kα선으로 2θ가 20°~50° 사이에서 측정하였으며, 정확한 격자 상수 계산을 위하여 표준 시료로 Si 분말 을 균일하게 혼합한 후 측정하였으며, 격자 상수를 최소 자승법(least square method) 을 이용하여 계산하였다. 두 께와 미세구조를 관찰하기 위해 environment scanning electron microscope (ESEM)을 사용하였다. 또 박막의 grain 구조 및 결정립을 관찰하기 위해 TEM을 사용하 였다. ReRAM 특성은 metal-insulator-metal (MIM) capacitor 구조로 박막 제작 후 측정하였다. 박막의 resistive switching 특성은 Keithley 4200 parameter analyzer 을 이용하였으며 이때의 recording은 voltage control mode 을 사용하였다. 마지막으로 상용화를 위해 pulse-induced resistive switching을 수행하였다.

#### 3 결과 및 고찰

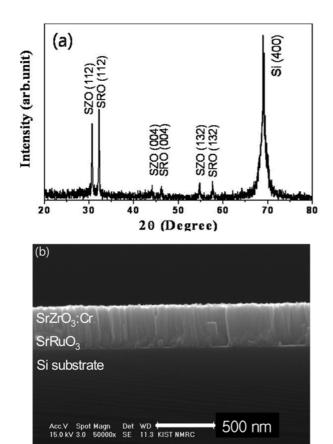

ReRAM 의 상용화를 위해 Si 기판위에의 SZO:Cr 박막의 재료적 분석과 전기적 특성을 실험을 하였다. Fig. 1(a)은 증착온도 650°C에서 Si 기판위에서 SZO:Cr 박막구조의 결정성을 관찰하기 위해 XRD 분석을 하였다. 분석결과 Cr:SZO 박막은 polycrystalline 으로 성장하였으며주 peak은 (112) 방향으로 성장함을 알 수 있었으며 (004), (132) plane peaks 도 관찰되었다. 이는 Si 위에 SRO의결정 방향과 일치함을 알 수 있었으며 SRO와 Cr:SZO

**Fig. 1.** (a) XRD pattern of the Cr-doped SZO/SRO/Si (100) structure deposited at 650°C, (b) SEM image.

가 같은 결정성을 가지는 것을 보아 Cr:SZO 박막의 결정성은 하부 SRO의 결정성에 의존한다고 사료된다. Fig. 1(b)은 Si(100) 기판위에서 성장한 SZO:Cr/SRO 박막의

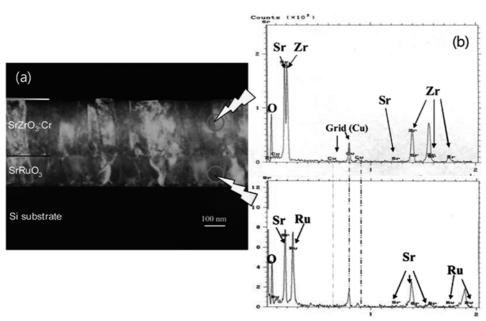

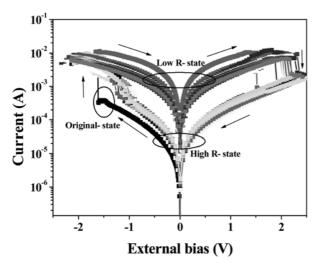

단면을 scanning electron microscopy (SEM) image로 관 찰한 것이다. 박막의 결정상은 SRO. SZO:Cr 박막 모두 columnar로 성장했다. 하지만 SEM 으로는 SRO와 SZO: Cr를 분리 할 수 없었으며 특히 Si 위에 native oxide의 두 께 및 생성여부를 관찰 할 수 없었다. 그래서 더 정밀 하게 분석하기 위하여 TEM (Transmission Electron Microscope)과 EDS (Energy Dispersive X-ray Spectroscopy) 을 통하여 관찰하였다. Fig. 2에 그 결과를 나타내었다. TEM 분석결과 SRO와 Cr:SZO의 증착 두께는 각각 200 nm, 300 nm 로 각각 관찰되었으며 Si substrate와 SRO 박막사이에 수 나노의 native oxide를 관찰할 수 있었고, 하부전극인 SRO layer의 조성으로는 Sr, Ru, O가 관찰 되어 SRO가 Si 위에 잘 성장되었음을 관찰하였다. 또한 EDS 분석결과 SRO 위에 SZO:C layer의 조성은 Sr, Zr, O 가 관찰되었으며 이는 SRO위에 SZO:Cr layer가 잘 성장되었음을 뜻하며 SRO layer와 일치하면서 columnar 구조를 가지면서 성장했다.<sup>11)</sup> Fig. 3에는 Si(100) 기 판위에서의 SZO:Cr 박막의 I-V 특성을 나타내었다. Resistive switching voltage는 재현성 있게 대략 ±2 V에서 나타났으며 reset current 가 0.01A로 나타났으며 on/off current ratio는 초기에는  $10^2$ 에서 많은 sweep을 거치면 서 10배 정도로 줄고 있음을 관찰 할 수 있었다. 하지만 이결과는 SRO/Si 위에 성장시킨 Cr:SZO가 비휘발성 메 모리로 응용할 수 있음을 나타낸다. I-V 특성에서 저항 상태는 Original state, (high resistance state) HRS, (low resistance state) LRS 3가지 상태로 나타났으며 Original state가 가장 큰 저항 상태를 나타내었다. 또 HRS는 voltage sweep 동안 결코 Original state 의 저항상태로 돌아가지

Fig. 2. (a) TEM image of the Cr-doped SZO/SRO/Si (100) structure deposited at 650°C and (b) EDS analysis.

**Fig. 3.** I-V characteristics of a SrZrO<sub>3</sub> film doped with 0.2% Cr grown on a SrRuO<sub>3</sub>/Si(100).

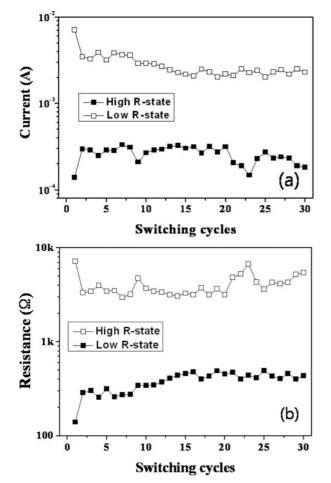

**Fig. 4.** Electrical properties of a Cr-deped  $SrZrO_3$  on  $SrRuO_3/Si(100)$  substrate (a) On/Off of current and (b) On/Off of resistance.

않았다. 이런 결과로 보아 forming 상태를 거쳐 박막내 부에 저항을 저하시키는 어떤 metallic한 성분이 생성되 었고 그 결과 original state로는 결코 돌아가지 못한다.

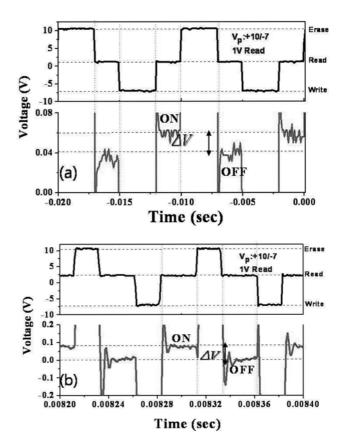

**Fig. 5.** Pulse switching behavior of Cr-doped SrZrO<sub>3</sub> thin film on SrRuO<sub>3</sub>/Si (100) substrate (a) 100 Hz and (b) 10 kHz.

또한 STO 기판 위에서의 결과와 다르게 같은 산소 분 압 250 mTorr 조건에서 낮은 switching voltage를 얻을 수 있었다. 이런 결과로 보아 SZO:Cr 박막의 결정성도 conduction path의 방향과 연관 되었을 것이라 생각된다. 다시 말해 polycrystalline일 때 conduction path가 더 많 이 생성되고 이는 switching voltage를 낮추는 중요한 요 소라 생각된다. Fig. 4에는 SZO:Cr 박막의 switching 횟 수에 따른 current 와 resistance 의 변화를 I-V 로 측정 한 결과를 나타낸 그래프이다. 두 가지의 변화 모두 재 현성 있게 switching 상태가 나타났으며 거의 규칙적인 on/off current ratio 와 resistance 변화를 관찰할 수 있 었으며 특히 처음 forming 상태가 가장 큰 변화를 보였 다. 또한 switching 횟수가 증가함에 따라 on/off current ratio 와 저항차가 줄고 있음이 관찰 되었다. 이는 앞으 로 더 개선되어야 하는 점 중에 하나로 판단된다. Fig. 5 에서는 pulse signal 을 통한 Si 기판위에서의 SZO:Cr 박막의 특성이다. 특히 Si 기판위에서의 pulse signal 측 정은 SZO:Cr 박막의 상용화에 매우 중요한 요소이다. Pulse signal 측정을 위해 switching 전압을 +10 V, -7 V 즉, -쪽은 write +쪽은 erase 로 분리했으며, +1 V에서 read 할 수 있게 측정했다. input 과 output signal 은 300 K

에서 측정했다. pulse를 인가한 후 on 과 off state를 전압의 변화상태 즉  $\Delta V$ 로 나타냈으며, Fig 5(a)의 전압 변화량은 on state 일 때 0.056~V이고 off 상태일 때 0.037~V로 측정되었다. Frequency는 100~Hz에서  $60~min~ 동안 <math>5\times 10^4$ 의 switching cycles를 보였다. Fig 5(b)~10~kHz의 전압 변화량은 on state에서 0.07~V off state에서 0.001~V로 변화되었다.

#### 4. 결 론

상용화를 위해 Si(100) 기판에 Cr-doped SrZrO<sub>3</sub> 박막 증착을 시도하여 10<sup>4</sup> 이상의 스위칭 횟수, 10 kHz이상의 속도, 10<sup>2</sup> 이상의 on/off current ratio와 같은 좋은 전기적 특성을 얻었다. 또한 상용화 적용을 위한 Pulse signal 특성 결과 전압변화량과 10<sup>4</sup> 이상의 스위칭 횟수, 10 kHz 이상의 스위칭 속도와 같은 우수한 전기적 특성을 얻었다. 이는 Cr-doped SrZrO<sub>3</sub> 박막이 비휘발성 메모리로써의 역할을 충분히 할 수 있는 가능성을 가지고 있음을 증명한다.

### 감사의 글

This research was supported by "The National Research Program for the 0.1 Terabit Non Volatile Memory Development" Sponsored by Korea Ministry of Commerce, Industry and Energy.

#### 참 고 문 헌

- 1. Y. Watanabe, J. G. Bednorz, A. Bietsch, Ch. Gerber, D. Widmer, A. Beck and S. J. Wind, Appl. Phys. Lett., 78, 3738 (2000).

- 2. A. Beck, J. G. Bednorz, Ch. Gerber, C. Rossel and D. Widmer, Appl. Phys. Lett., 77, 139 (2000).

- 3. S. Q. Liu, N. J. Wu and A. Ignativ, Appl. Phys. Lett., **76**, 2749 (2000).

- 4. J. Rodriguez Contreras, H. Kohlstedt, U. Poppe, R. Waser, C. Buchal and N. A. Pertsev, Appl. Phys. Lett., **83**, 4595 (2003).

- 5. W. S. Hong, N. C. Park and C. S. Oh, Kor. J. Mater. Res., **19**(6), 337 (2009).

- S. Seo, M. J. Lee, D. H. Seo, E. J. Jeoung, D. -S. Suh, Y. S. Joung, I. K. Yoo, I. R. Hwang, S. H. Kim, I. S. Byun, J. -S. Kim, J. S. Choi and B. H. Park, Appl. Phys. Lett., 85, 5655 (2004).

- M. Hasan, R. Dong, H. J. Choi, D. S. Lee, D.-J. Seong, M. B. Pyun and H. Hwang, Appl. Phys. Lett., 92, 202102 (2008).

- R. Dong, W. F. Xiang, D. S. Lee, S. J. Oh, D. J. Seong, S. H. Heo, H. J. Choi, M. J. Kwon, M. Chang, M. Jo, M. Hasan and H. Hwang, Appl. Phys. Lett., 90, 182118 (2007).

- N. Xu, L. Liu, X. Sun, X. Liu, D. Han, Y. Wang, R. Han,

J. Kang and B. Yu, Appl. Phys. Lett., 92, 232112 (2008).

- M. Fujimoto, H. Koyama, M. Konagai, Y. Hosoi, K. Ishihara, S. Ohnishi and N. Awaya, Appl. Phys. Lett., 89, 223509 (2006).

- 11. M. Izuha, K. Abe, M. Koike and N. Fukushima, Solid State Ionics., **108**, 99-104 (1998).

- 12. S. H. Choi and K. S. Lee, Kor. J. Mater. Res., **19**(12), 637 (2009).