## **Rigorous Design of 22-nm Node 4-Terminal SOI FinFETs for Reliable Low Standby Power Operation** with Semi-empirical Parameters

Seongjae Cho\*, Shinichi O'uchi\*\*, Kazuhiko Endo\*\*, Sang Wan Kim\*\*\*, Younghwan Son\*\*\*, In Man Kang\*\*\*\*, Meishoku Masahara\*\*, James S. Harris, Jr.\*, and Byung-Gook Park\*

Abstract—In this work, reliable methodology for device design is presented. Based on this method, the underlap length has been optimized for minimizing the gateinduced drain leakage (GIDL) in a 22-nm node 4terminal (4-T) silicon-on-insulator (SOI) fin-shaped field effect transistor (FinFET) by TCAD simulation. In order to examine the effects of underlap length on GIDL more realistically, doping profile of the source and drain (S/D) junctions, carrier lifetimes, and the parameters for a band-to-band tunneling (BTBT) model have been experimentally extracted from the devices of 90-nm channel length as well as pnjunction test element groups (TEGs). It was confirmed that the underlap length should be near 15 nm to suppress GIDL effectively for reliable low standby power (LSTP) operation.

*Index Terms*—Device design, gate-induced drain leakage (GIDL), fin-shaped field-effect transistor (FinFET), TCAD simulation, carrier lifetime, bandto-band tunneling (BTBT), underlap length

#### I. INTRODUCTION

Recently, managing the standby power is considered as one of the most critical reliability issues in CMOS technologies including SRAM and high-density mobile electronic appliance. One of the major leakage current sources in ultra-small metal-oxide-semiconductor fieldeffect transistors (MOSFETs) is the gate-induced drain leakage (GIDL) current mainly caused by band-to-band tunneling (BTBT) near the drain end [1]. The devices on silicon-on-insulator (SOI) are known to have low intrajunction leakage and punch-through leakage [2, 3]. In a device structure view, fin-shaped FET (FinFET) have merits of better controllability on threshold voltage  $(V_{th})$ and higher drivability of on-current [4, 5]. In this work, a rigorous design of 22-nm node 4-terminal (4-T) SOI FinFET aiming low standby power (LSTP) operation is carried out for suppressing GIDL by controlling the gate underlap length by TCAD simulation [6]. We used the parameters extracted from the fabricated devices of 90nm technology node and junction-engineered pn-diode. This semi-empirical approach makes the design of the ultra-small CMOS devices more realistic and reliable.

## II. DEVICE STRUCTURE AND DESIGN STRATEGY

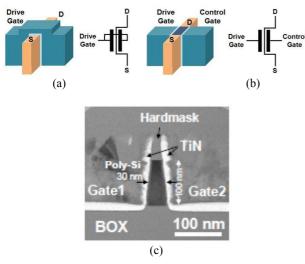

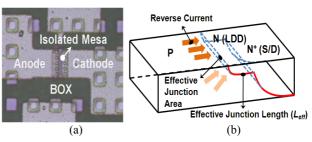

The schematic views with circuit symbols for 3-T and 4-T SOI FinFETs and a cross-sectional image by scanning electron microscope (SEM) are shown in Fig. 1(a), (b) and (c).

Manuscript received Nov. 4, 2010; revised Dec. 8, 2010.

<sup>\*</sup> S. Cho, J. S. Harris, Jr., and B.-G. Park are with the Electrical Engineering Department, Stanford University, CA 94305 USA B.-G. Park is on leave from the School of Electrical Engineering and Computer Science, Seoul National University, Seoul 151-742, Republic of Korea \*\* S. O'uchi, K. Endo, and M. Masahara are with the Silicon Nanoscale Device Group, Nanoelectronics Research Institute, National Institute of Advanced Industrial Science and Technology (AIST), Ibaraki 305-8568, Japan \*\*\* S. W. Kim and Y. Son are with the School of Electrical Engineering and Computer Science, and Inter-university Semiconductor Research Center (ISRC), Seoul National University, Seoul 151-742, Republic of Korea

<sup>\*\*\*\*</sup> I. M. Kang is with the School of Electronics Engineering, Kyungpook National University, Daegu 702-201, Republic of Korea E-mail : bgpark@snu.ac.kr

**Fig. 1.** Schematic views with circuit symbols for (a) 3-T and (b) 4-T SOI FinFETs, (c) Cross-sectional SEM image of the fabricated 4-T SOI FinFET following the 90-nm technology node [7].

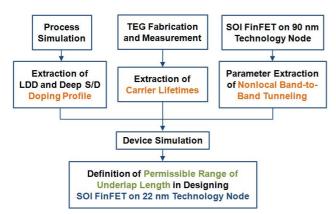

Fig. 2 demonstrates the flow chart for the design of SOI FinFET on 22-nm technology node. As shown in the figure, three different initial approaches were made simultaneously toward the design purpose in order to collect the crucial ingredients that will be embedded in the device design by TCAD simulation.

**Fig. 2.** Flow chart for the design of LSTP 4-T SOI FinFET on 22-nm node.

## III. MEASUREMENT AND COMPACT MODELING

#### 1. Doping Profile Extraction from Process Simulation

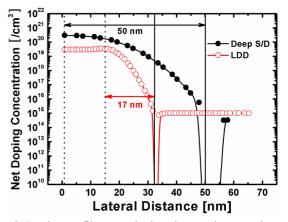

In order to identify the doping profile near the drain end of the fabricated device, process simulations were performed by fully following the process steps taken in

the fabrication [7]. As<sup>+</sup> ions of  $5 \times 10^{13}$  /cm<sup>2</sup> dose were implanted at 5 keV with 60° tilt for the source/drain (S/D) extensions. After the formation of sidewall spacer made of plasma oxide, P<sup>+</sup> ions of  $1 \times 10^{15}$  /cm<sup>2</sup> dose were implanted at 10 keV with 7° tilt for deep S/D implantation. The activation was performed by spike rapid thermal annealing (RTA) for 4 sec at 830 °C. In the fabrication, low thermal budget was pursued in the RTA process to minimize the unwanted movements of boron atoms in consideration of the applications for static random access memory (SRAM) architectures where ptype MOSFET should be implemented simultaneously [7-10]. Fig. 3 shows that the distances from the  $n^+$  doping peaks of the extensions and deep S/D regions to the metallurgical junctions are 17 nm and 50 nm, respectively, by the process simulations. In this figure, the nominal distances are only meaningful since two curves reflect the results from two times of independent ion implantations on different Si wafers so that the relative locations are meaningless. Thus, these doping gradients of the LDD and S/D regions will be used in the design works regardless of the thicknesses of sidewall spacers, i.e, the underlap lengths.

**Fig. 3.** Doping profiles near the junctions at the extension and deep S/D ends. The dotted lines and solid lines indicate  $n^+$  peak doping locations and the metallurgical junctions, respectively.

# 2. Extraction of Carrier Lifetimes from Calibration Devices

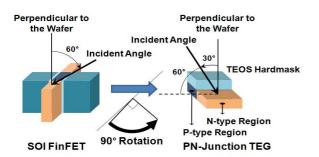

For extracting more accurate carrier lifetimes, a test element group (TEG) containing pn-junctions of various dimensions was fabricated on the 6" SOI wafer following the actual process conditions for S/D junctions. A 6" ptype (100) SOI wafer with body doping concentration of

$5 \times 10^{15}$  /cm<sup>3</sup> was prepared. The thickness of SOI is 1000 Å, which is the height of silicon fin, and the active region is isolated in a mesa structure by dry etch. A TEOS dummy pattern of 1000 Å thickness is constructed for distinguishing p- and n-type regions and the S/D extension is implanted by the previous condition,  $As^+ 5 \times$  $10^{13}$  /cm<sup>2</sup> dose at 5 keV with a changed tilting angle of 30°. In other words, the polysilicon gate and gate oxide in an SOI FinFET were simply replaced by TEOS hard mask in a pn-junction. The incident angle is switched from  $60^{\circ}$  to  $30^{\circ}$  to obtain the same doping profile in a pn-junction where the current flows along the wafer surface. The simple rotational conversion is demonstrated in Fig. 4. Sidewall spacers are formed by consecutive deposition and anisotropic dry etch of Si<sub>3</sub>N<sub>4</sub> after the S/D extensions are formed. Likewise, S/D ion implantation is performed at a converted tilt of 83°. All the doses and acceleration energy conditions are same with those

adopted in the fabrication of 4-T SOI FinFET. By this condition, extremely shallow S/D junctions on the Si fin sides are formed. After an activation by spike RTA, interlayer dielectric (ILD) is deposited and contact holes are made, which are followed by metallization and alloy at 450 °C for 30 min in an  $N_2/H_2$  ambient.

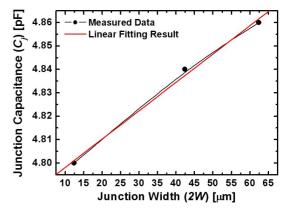

Fig. 5(a) and (b) show the fabricated pn-junction and the definition of the effective junction length  $(L_{eff})$ , respectively. The junction width was varied from 0.6 µm to 41.2 µm in the masks. On the other hand,  $L_{eff}$  is kept invariable since all the devices were fabricated by the same implantation and RTA conditions. Fig. 6 shows the junction capacitances measured by Agilent 4284A. The junction capacitances were measured from the capacitors with long junction widths and two capacitors are connected in parallel so that  $C_j$  is mainly composed of the surface component. Thus, the *x*-axis in Fig. 6 indicates

**Fig. 4.** Rotational conversion relation between tilt angles in ion implantations for the S/D regions of SOI FinFET and pn-junction.

**Fig. 5.** Junction-engineered pn-diode in the TEG. (a) Microscopic view on top, (b) Schematic view of the mesa-structured pn-diode and effective junction area.

**Fig. 6.** Junction capacitance  $(C_j)$  as a function of junction width (2W).

the doubled junction width. Based on the slope of the fitting line,  $1.21 \times 10^{-11}$  F/cm, built-in potential values, and the depletion width at a reverse bias of 0.5 V,  $L_{eff}$  was extracted to be  $6.4 \times 10^{-4}$  cm. The carrier and generation lifetimes were calculated by following equations [11].

$$J_{R} = I_{R} / A_{eff} = I_{R} / WL_{eff} = q \sqrt{\frac{D_{n}}{\tau_{n}}} \frac{n_{i}^{2}}{N_{A}} + \frac{qn_{i}W_{dep}}{\tau_{g}} \quad (1)$$

$$\tau_{g} = \tau_{p} e^{(E_{T} - E_{i})/kT} + \tau_{n} e^{-(E_{T} - E_{i})/kT} \quad (2)$$

The effective junction area to calculate the reverse current density  $(J_R)$  is the multiplication of the junction width as a design variable and the extracted junction length. Since there are two unknowns in Eq. (1),  $\tau_n$  and  $\tau_g$ ,  $J_R$ 's under two reverse bias conditions at a fixed junction width were considered to set up two equations. Assuming the trap level is near the midgap  $(E_T \sim E_i)$  as the usual CMOS processes,  $\tau_g$  is simply expressed as the sum of  $\tau_p$ and  $\tau_n$  from Eq. (2). The effective junction area in Eq. (1) is the multiplication of junction width as the design variable and the extracted effective junction length. The reverse currents were measured at reverse voltages of - 0.2 V and -0.35 V by Agilent 4156C. Assuming  $E_T \sim E_i$ , the carrier lifetimes are calculated as  $\tau_n = 5.430 \times 10^{-5}$  s and  $\tau_p = 5.752 \times 10^{-6}$  s, which are reasonable values in the devices fabricated by conventional CMOS processes [12].

#### 3. Modeling of Band-to-Band Tunneling

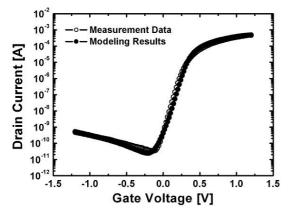

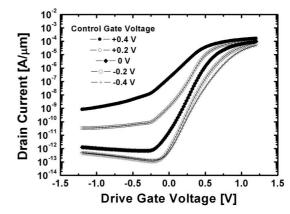

Fig. 7 shows the transfer characteristics curve from the measurement of a fabricated 4-T SOI FinFET under 3-T operation and its modeling results in which the newly extracted carrier lifetimes are reflected. Although there are a number of BTBT models [13-15], nonlocal BTBT calculations were carried out in consideration of quantum effects, which shows a very good agreement with the measured data as confirmed in the figure. For more elaborate fitting, the contact resistance and the electron mobility parameters were recursively figured out and equipped in the TCAD simulation. The channel length was 90 nm and the drive drain voltage  $(V_{DD})$  was 1.0 V. Since GIDL is independent of device channel length [16, 17], the determined coefficients from the modeling results could be persistently utilized in designing the SOI FinFET device with 20-nm channel length.

**Fig. 7.**  $I_{D}$ - $V_{GS}$  curves from measurement data and modeling result.

### IV. DESIGN OF LOW STANDBY POWER (LSTP) SOI FINFET

Based on the parameters extracted from the measurement and the compact modeling in the previous sections, a design of SOI FinFET device on 22-nm technology node for LSTP operation has been performed. The design variable was underlap length which substantially affects the GIDL in the off-state of device. The underlap length can be easily modulated by the bottom width of the sidewall spacer [18-20]. For more reliable design, a number of realistic models were included in the simulation works: field and concentration-mobility models, Shockley-Read-Hall (SRH) recombination model, bandgap narrowing model, quantum model, gate current model, nonlocal BTBT model, and nonlocal trapassisted tunneling (TAT) model [21-27].

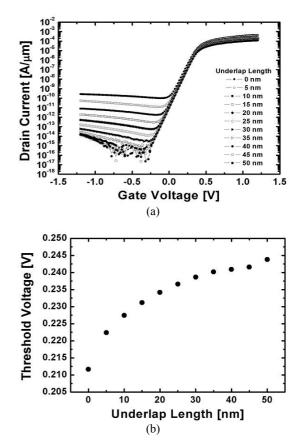

Fig. 8(a) shows the simulation results of  $I_D$ - $V_{GDrv}$ ( $V_{GDrv}$ : drive gate voltage) curves of an SOI FinFET with a channel length of 20 nm. The drive and control gates (Fig. 1) are connected in common to investigate the transfer characteristics for the basic 3-T operation. The thicknesses of silicon fin and gate oxide were 10 nm and 1.4 nm, respectively. The underlap length was varied from 0 to 50 nm by 5 nm spacing. Fig. 8(b) depicts the  $V_{th}$  as a function of underlap length. They were extracted by a constant current method ( $V_{th} = V_{GDrv}$  @( $I_D = 1$  $\mu A/\mu m$ )). It was confirmed that the  $V_{th}$  values are in a

**Fig. 8.** Effects of the underlap lengths. (a)  $I_D$ - $V_{GS}$  curves for the SOI FinFET devices, (b) corresponding threshold voltages ( $V_{GS}$  at a constant current of  $I_D = 10^{-7}$  A/µm) with variation on the underlap lengths.

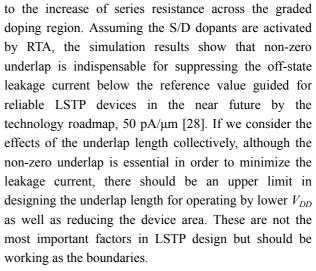

permissible range to meet the requirements on multiplegate (MG) MOSFETs designated by the most recent technology roadmap [28]. In Fig. 8(a) and (b),  $V_{DD}$  was set to be 1.0 V in accordance with the near-term predictions for the LSTP technology by roadmap. Fig. 9(a) shows on-state ( $I_{on}$ ) and off-state ( $I_{off}$ ) currents with variation on underlap length. Both  $I_{on}$  and  $I_{off}$  decrease monotonically as the underlap elongates. Especially,  $I_{off}$ rolls off more prominently than  $I_{on}$  by controlling the underlap length.  $I_{off}$  is effectively suppressed below 20 pA/µm and saturated with an underlap longer than 10 nm.

Fig. 9(b) demonstrates the current ratio  $(I_{on} / I_{off})$  as a function of underlap length. The current ratio increases drastically from non-underlap condition to underlap length of 15 nm due to the sharp decline in  $I_{off}$  up to this length. However, the ratio begins to roll off above the underlap length of 15 nm, where it is determined dominantly by continuous decrease of  $I_{on}$ . The drive current  $(I_D @(V_{GS} = V_{DD} = 1.0 \text{ V}))$  is monotonically degraded with a large slope as the underlap elongates due

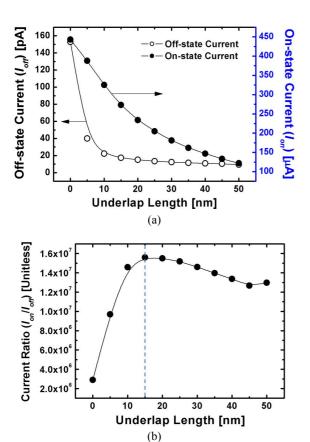

Fig. 10(a) and (b) demonstrates an analytical method of extracting GIDL. In this method, GIDL current is defined as the difference in drain current induced by

**Fig. 9.** Current characteristics as a function of underlap length. (a)  $I_{on}$  and  $I_{off}$  ( $I_{off} = I_D @((V_{G,Drv}, V_D) = (0 \text{ V}, 1 \text{ V})))$ , (b) On/off-current ratio ( $I_{on}/I_{off}$ ). A local maximum is observed at an underlap length of 15 nm.

**Fig. 10.** Quantitative extraction of GIDL component. (a) Definition of GIDL by TCAD simulations: the drain current difference by switching on and off the set of all the GIDL-related models, (b) Extracting  $V_G$  location.

switching the full set of GIDL-related models at a specific gate voltage as shown in Fig. 10(a). The code names of GIDL-related models activated in the TCAD simulation were srh (Shockley-Read-Hall model), bbt.std (standard BTBT model), trap.tunnel (TAT model), bbt.nonlocal (nonlocal BTBT model), bbt.nlderivs (a BTBT model considering the derivatives of the tunneling current with respect to the values of the band edges), bbt. forward (a BTBT model for more accurate calculation in forward tunneling current), bbt.reverse (same purpose for in reverse one), and tat.nonlocal (a TAT model enabling the nonlocal tunneling model in the calculation of the field effect enhancement factors). There is no feasible way to extract GIDL from the measured  $I_D$ - $V_G$  curve in reality. However, in simulation works, GIDL can be quantitatively evaluated by switching on and off the set of GIDL-related models. In a previous research, only BTBT model was switched but it is more realistic to deal with all the related models simultaneously [29-31]. In Fig. 10(a), GIDL is defined as the current difference generated by switching the model set. Fig. 10(b) shows the positioning  $V_G$  value for GIDL extraction.

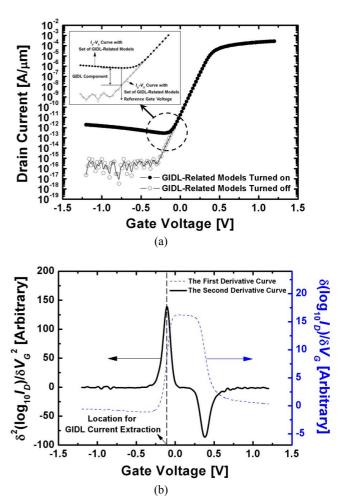

The switching operations were performed at a gate voltage where the second derivative of  $I_D$ - $V_G$  curve has a local maximum. It can trace the point where the curvature most rapidly changes. At this point, drastic enhancement in GIDL begins to occur [31]. In a physical sense, this is more reliable than the conventional method [29]. Since it is almost impossible to extract GIDL solely from other current components by measurement from an already fabricated device, establishing a reliable method of quantitative extraction of GIDL based on device simulation will be useful. Fig. 11 depicts the extracted

Fig. 11. GIDL current as a function of underlap length. The tentative reference line indicates GIDL of 1  $pA/\mu m$ .

**Fig. 12.**  $I_D$ - $V_{G,Drv}$  curves for 4-T operations with  $V_{G,Ctr}$  control  $(V_{DD} = 1.0 \text{ V})$ .

GIDL components as a function of underlap length. If a permissible GIDL current is presumed to be 1 pA/ $\mu$ m, the underlap length should be longer than 10 nm. Thus, for the sake of stable  $V_{th}$  window, maximum  $I_{on}/I_{off}$  ratio, and effective repression of  $I_{off}$  in terms of GIDL, the underlap should be at least 15 nm but limited for efficiency in operation and area. Fig. 12 shows  $I_D$ - $V_{GDrv}$  curves at different control gate voltages ( $V_{GCtr}$ ). The designed channel length and underlap were 20 nm and 15 nm, respectively, as optimized. The results confirm the 4-T operation and threshold  $V_{GDrv}$  is adjustable by  $V_{GCtr}$ . In order to suppress  $I_{off}$  below a reference value by roadmap, 50 pA/ $\mu$ m, while keeping the subthreshold slope steep for the LSTP logic application, nonpositive  $V_{GCtr}$  biasing is desirable.

#### V. CONCLUSIONS

In this work, a rigorous design of 4-T SOI FinFET device on 22-nm technology node for LSTP operation has been performed. For higher reliability, parameters were extracted and calculated semi-empirically from the fabricated 90-nm SOI FinFET and TEGs. The doping profiles obtained by the process simulations abiding by actual fabrication conditions, majority and minority carrier lifetimes, and recursive fitting, the accuracy of device design was made highly reliable. Based on these results, a 22-nm node 4-T SOI FinFET has been designed focusing on the underlap length for LSTP application by TCAD simulations. In order to achieve reliable LSTP operation with marginal performance and area-effectiveness, the underlap should be precisely controlled

around 15 nm in a process architecture using the RTA system.

#### **ACKNOWLEDGMENTS**

This work was supported by National Research Foundation of Korea (NRF) (previously, KOSEF) and Japan International Science and Technology Exchange Center (JISTEC).

#### REFERENCES

- J. Chen, T. Y. Chan, I. C. Chen, P. K. Ko, C. Hu, "Subbreakdown drain leakage current in MOSFET," *IEEE Electron Device Lett.*, Vol.8, No.11, pp.515-517, Nov. 1987.

- [2] S. Veeraraghaven, J. G. Fossum, "Short-channel effects in SOI MOSFETs," *IEEE Trans. Electron Devices*, Vol.36, No.3, pp.522-528, Mar. 1989.

- [3] Y. Omura, H. Konishi, and K. Yoshimoto, "Impact of fin aspect ratio on short-channel control and drivability of multiple-gate SOI MOFET's," *J. Semicond. Technol. Sci.*, Vol.8, No.4, pp.302-310, Dec. 2008.

- [4] D.-S. Woo, J.-H. Lee, W. Y. Choi, B.-Y. Choi, Y.-J. Choi, J. D. Lee, and B.-G. Park, "Electrical characteristics of FinFET with vertically nonuniform source/drain doping profile," *IEEE Trans. Nanotechnol.*, Vol.1, No.4, pp.233-237, Dec. 2002.

- [5] D.-S. Woo, B. Y. Choi, W. Y. Choi, M. W. Lee, J. D. Lee, and B.-G. Park, "30 nm self-aligned FinFET with large source/drain fan-out structure," *Electron. Lett.*, Vol.39, No.15, pp.1154-1155, Jul. 2003.

- [6] ATHENA/ATLAS User's Manual, Silvaco International, Nov/Dec. 2008.

- [7] K. Endo, S. O'uchi, Y. Ishikawa, Y. Liu, T. Matsukawa, K. Sakamoto, J. Tsukada, K. Ishii, H. Yamauchi, E. Suzuki, and M. Masahara, "Enhancing SRAM cell performance by using independent double-gate FinFET," in *IEDM Tech. Dig.*, 2008, pp.857-860.

- [8] T.-S. Park, H. J. Cho, J. D. Choe, S. Y. Han, D. Park, K. Kim, E. Yoon, and J.-H. Lee, "Characteristics of the full CMOS SRAM cell

using body-tied TG MOSFETs (Bulk FinFETs)," *IEEE Trans. Electron Devices*, Vol.53, No.3, pp. 481-487, Mar. 2006.

- [9] H. Yamauchi, "A scaling trend of variation-tolerant SRAM circuit design in deeper nanometer era," J. Semicond. Technol. Sci., Vol.9, No.1, pp.37-50, Mar. 2009.

- [10] K. Endo, S. O'uchi, Y. Ishikawa, Y. Liu, T. Matsukawa, K. Sakamoto, M. Masahara, J. Tsukada, K. Ishii, H. Yamauchi, and E. Suzuki, "Independent-double-gate FinFET SRAM for leakage current reduction," *IEEE Electron Device Lett.*, Vol.30, No.7, pp.757-759, Jul. 2009.

- [11] S. M. Sze and K. K. Ng, *Physics of Semiconductor Devices*, 3rd ed., Wiley-Interscience, New York, USA, 2007, pp.96-98.

- [12] R. F. Pierret, Semiconductor Device Fundamentals, Addison Wesley, Massachusetts, USA, 1996, p. 116.

- [13] E. O. Kane, "Theory of tunneling," J. Appl. Phys., Vol.32, No.1, pp.83-91, Jan. 1961.

- [14] G. A. M. Hurkx, D. B. M. Klaassen, and M. P. G. Knuvers, "A new recombination model for device simulation including tunneling," *IEEE Trans. Electron Devices*, Vol.39, No.2, pp.331-338, Feb. 1992.

- [15] A. Schenk, "Rigorous theory and simplified model of the band-to-band tunneling in silicon," *Solid State Electron.*, Vol.36, No.1, pp.19-34, Jan. 1993.

- [16] J.-H. Chen, S.-C. Wong, and Y.-H. Wang, "An analytical three-terminal band-to-band tunneling model on GIDL in MOSFET," *IEEE Trans. Electron Devices*, Vol.48, No.7, pp.1400-1405, Jul. 2001.

- [17] T. Y. Chan, J. Chen, P. K. Ko, and C. Hu, "The impact of gate-drain leakage current on MOSFET Scaling," in *IEDM Tech. Dig.*, 1987, pp.718-721.

- [18] S. K. Sung, Y. J. Choi, J. D. Lee, and B.-G. Park, "Fabrication of ultra-thin line using sidewall structure and the application for nMOSFET," *The 6th Korean Conf. Semicond.*, pp.617-618, Feb. 1999.

- [19] Y.-K. Choi, T.-J. King, and C. Hu, "A spacer patterning technology for nanoscale CMOS," *IEEE Trans. Electron Devices*, Vol.49, No.3, pp.436-441, Mar. 2002.

- [20] B.-G. Park, D. H. Kim, K. R. Kim, K.-W. Song, and J. D. Lee, "Single-electron transistors fabricated

with sidewall spacer patterning," *Superlattices Microstruct.*, Vol.34, No.3-6, pp.231-239, Sep.-Dec. 2003.

- [21] D. M. Caughey and R. E. Thomas, "Carrier mobilities in silicon empirically related to doping and field." *Proc. IEEE*, Vol.55, No.12, pp.2192-2193, Dec. 1967.

- [22] S. Selberherr, "Process and device modeling for VLSI", *Microelectron. Reliab.*, Vol.24, No.2, pp. 225-257, Mar.-Apr. 1984.

- [23] W. Shockley and W. T. Read, "Statistics of the recombination of holes and electrons", *Phys. Rev.* Vol.87, No.5, pp.835-842, Sep. 1952.

- [24] R. N. Hall, "Electron hole recombination in germanium", *Phys. Rev.* Vol.87, No.2, p.387, Jul. 1952.

- [25] J. W. Slotboom and H. C. De Graaf, "Measurements of bandgap narrowing in silicon bipolar transistors", *Solid State Electron.*, Vol.19, No.10, pp.857-862, Oct. 1976.

- [26] G. A. M. Hurkx, D. B. M. Klaassen, M. P. G. Knuvers, and F. G. O'Hara, "A new recombination model describing heavy-doping effects and low temperature behaviour", in *IEDM Tech. Dig.*, 1989, pp.307-310.

- [27] Y. Apanovich, P. Blakey, R. Cottle, E. Lyumkis, B. Polsky, A. Shur, and A. Tcherniaev, "Numerical simulation of submicrometer devices including coupled nonlocal transport and nonisothermal effects," *IEEE Trans. Electron Devices*, Vol.42, No.2, pp.890-898, May 1995.

- [28] Process Integration, Devices, and Structures (PIDS), International Technology Roadmap for Semiconductors (ITRS), 2009 edition, p.9.

- [29] K. Tanaka, K. Takeuchi, M. Hane, "Practical FinFET design considering GIDL for LSTP (low standby power) devices," in *IEDM Tech. Dig.*, 2005, pp.1001-1004.

- [30] F. Gilibert, D. Rideau, A. Dray, F. Agut, M. Minondo, A. Juge, P. Masson, and R. Bouchakour, "Characterization and modeling of gate-induceddrain-leakage," *IEICE Trans. Electron.*, Vol.E88-C, No.5, pp.829-837, May 2005.

[31] S. Cho, J. H. Lee, S. O'uchi, K. Endo, M. Masahara, and B.-G. Park, "Design of SOI FinFET on 32 nm technology node for low standby power (LSTP) operation considering gate-induced drain leakage (GIDL)," *Solid-State Electron.*, Vol.54, No.10, pp.1060-1065, Oct. 2010.

Seongjae Cho received the B.S. and Ph.D. degrees in electrical engineering from School of Electrical Engineering and Computer Science (EECS), Seoul National University (SNU), Seoul, Korea, in 2004 and 2010,

respectively.

He worked as a student internship member at the Department of System IC of Hynix Semiconductor 2003. He also worked as a process engineer in 2004 and a teaching assistant for semiconductor process education from 2005 to 2007 at the Inter-university Semiconductor Research Center (ISRC) in SNU. He also worked with the National Institute of Advanced Industrial Science and Technology (AIST) in Tsukuba, Japan, with the support by Korea Science and Engineering Foundation (KOSEF) in 2009. From March 2010 to September 2010, he worked as a postdoctoral researcher at EECS, SNU, and since October 2010, he has been working in the same position at Electrical Engineering, Stanford University, California. He authored or co-authored more than 120 papers published in journals and presented in conferences.

He is a member of IEEE Electron Devices Society, KPS (The Korean Physical Society), IEICE (The Institute of Electronics, Information and Communication Engineers), and a Life Member of IEEK (The Institute of Electronics Engineers of Korea). He received Distinguished Research Achievement Awards from EECS, SNU, in 2009 and 2010. His research interests include design, fabrication, and characterization of nanoscale CMOS, emerging nonvolatile memory, and optoelectronic devices.

Shinichi O'uchi received the B.E. degree in electrical engineering from Tokyo University of Science, Tokyo, Japan, in 1997 and the M.S. and Ph.D. degrees in information and communication engineering from the University of Tokyo, in 1999 and 2002, respectively.

In 2002, he was with the Research and Development Center, Toshiba Corporation, Tokyo. Since 2005, he has been a researcher with the Nanoelectronics Research Institute, National Institute of Advanced Industrial Science and Technology, Ibaraki, Japan. He had been engaged in researches for single-electron memories, dedicated processors for a quantum-computing simulation, and CMOS-integrated DNA chips. His research interest is currently in the digital and analog integrated circuits utilizing the double-gate MOSFETs.

Dr. O'uchi is a member of the IEEE Solid State Circuit Society.

Kazuhiko Endo received the B.S., M.S., and Ph.D. degrees in electrical engineering from Waseda University, Tokyo, Japan, in 1991, 1993, and 1999, respectively.

From 1993 to 2003, he was with the

Systems Laboratories, Silicon Research NEC Corporation, Otsu, Japan, where he worked on the research and development of multilevel interconnection of ultralarge-scale integration (ULSI), high-k gate stack technologies. From August 1999 to August 2000, he was a visiting scholar in the Center for Integrated Systems, Stanford University, Stanford, CA, where we worked on the thermal effects in the Cu interconnects. He is currently a researcher with the Nanoelectronics Research Institute, National Institute of Advanced Industrial Science and Technology, Tsukuba, Japan. His research interests include nanometer-scale manufacturing for high-performance and low-power ULSI. He also works on exploratory high-performance interconnects. Additionally, his research extends to aggressively scaled double-gate transistors in advanced very large scale integration technologies.

Dr. Endo was the recipient of a Best Paper Award at the 2003 Advanced Metallization Conference and at the 1998 Meeting of Japan Society of Applied Physics. He is a member of the Japan Society of Applied Physics.

Sang Wan Kim received the B.S. and M.S. degrees in 2006 and 2008 from Seoul National University, Seoul, Korea, where he is currently working toward the Ph.D. degree in electrical engineering.

He has worked as a research and education assistant at Inter-university Semiconductor Research Center (ISRC) in Seoul National University since 2008. His current research interests include device modeling, measurement, characterization, and fabrication of 1T DRAM, CNT, TFET, and nanoscale CMOS devices. He is a student member of IEEK.

Younghwan Son received the B.S. and M.S degrees in electrical engineering from Chungnam National University, Daejeon, Korea, in 2004 and 2007, respectively. He is working toward the Ph.D. degree in

electrical engineering and computer science at Seoul National University, Seoul, Korea.

From February 2005 to December 2006, he had worked in the school of computational sciences at Korea Institute for Advanced Study (KIAS), Seoul, Korea. His research interests include the device random noise analysis and modeling of flash memory cells and reliability issues of nanoscale CMOS devices.

In Man Kang received B.S. degree in electronic and electrical engineering from Kyungbook National University, Daegu, Korea, in 2001, and the Ph.D degree in electrical engineering from Seoul National University, Seoul,

Korea, in 2007. From 2007 to 2010, he was with Samsung Electronics, as a Senior Engineer. In 2010, he joined the School of Electronics Engineering, Kyungpook National University, Daegu, as a full-time lecturer. His current research interests include CMOS RF modeling, silicon nanowire devices, tunneling transistor, nano CMOS.

Meishoku Masahara received the B.S., M.S., and Ph.D. degrees in electrical engineering from the School of Science and Engineering, Waseda University, Tokyo, Japan, in 1990, 1992, and 1995, respectively.

From 1994 to 1996, he was a research associate with Waseda University where he worked on the development of single-ion microprobe system for MOS device diagnosis. From 1996 to 1998, he was a researcher with CREST, Japan Science and Technology Corporation, and was with the Research Center for Nanodevices and Systems, Hiroshima University, Hiroshima, Japan, where he worked on research and development of smallgeometry MOSFET with ultrathin gate oxide. From 1998 to 2000, he was a visiting lecturer in the Kagami Memorial Laboratory for Materials Science and Technology, Waseda University, where he worked on the development of a novel Si nanoprocess. From July 2005 to June 2006, he was a Visiting Researcher at IMEC. He is currently a Senior Researcher with the Nanoelectronics Research Institute, National Institute of Advanced Industrial Science and Technology, Tsukuba, Japan, where he is working on the research and development of multigate MOSFETs. He has published over 100 research papers in archival journals and refereed international conferences on these subjects.

Dr. Masahara serves on the Technical Program Committee of the Symposium on VLSI Technology and on the International Microprocesses and Nanotechnology Conference. He is a member of the IEEE Electron Devices Society, the Institute of Electrical Engineering of Japan, and the Japan Society of Applied Physics.

James S. Harris, Jr. received the B.S., M.S., and Ph.D. degrees in electrical engineering from Stanford University, Stanford, CA, in 1964, 1965, and 1969, respectively.

In 1969, he joined Rockwell International Science Center, Thousand

Oaks, CA, where he was one of the key contributors to ion implantation, molecular beam epitaxy, and heterojunction devices, leading to their preeminent position in GaAs technology. In 1980, he became the Director of the Optoelectronics Research Department. In 1982, he joined the Solid State Electronics Laboratory, Stanford University, as a Professor of Electrical Engineering, where he was the Director of the Solid State Electronics Laboratory (1984-98), the Director of the Joint Services Electronics Program (1985-99), and is currently the James and Ellenor Chasebrough Professor of Electrical Engineering, Applied Physics, and Materials Science in the Center for Integrated Systems. His research interests include physics and application of ultra-small structures and novel materials to new highspeed and spin-based electronic, and optoelectronic devices and systems. He is the author or coauthor of more than 650 publications. He holds 14 issued U.S. patents.

Dr. Harris is a Fellow of the American Physical Society. He was the recipient of the 2000 IEEE Morris N. Liebmann Memorial Award, the 2000 International Compound Semiconductor Conference Walker Medal, the IEEE Third Millennium Medal, and the Alexander von Humboldt Senior Research Prize in 1998 for his contributions to GaAs devices and technology.

**Byung-Gook Park** received his B.S. and M.S. degrees in electronic engineering from Seoul National University (SNU) in 1982 and 1984, respectively, and his Ph.D. degree in electrical engineering from Stanford

University in 1990. From 1990 to 1993, he worked at the AT&T Bell Laboratories, where he contributed to the development of 0.1 micron CMOS and its characterization. From 1993 to 1994, he was with Texas Instruments, developing 0.25 micron CMOS. In 1994, he joined SNU as an assistant professor in the School of Electrical Engineering (SoEE), where he is currently a professor. In 2002, he worked at Stanford University as a visiting professor, on his sabbatical leave from SNU. He has been leading the Inter-university Semiconductor Research Center (ISRC) at SNU as the director from June 2008.

His current research interests include the design and fabrication of nanoscale CMOS, flash memories, silicon quantum devices and organic thin film transistors. He has authored and co-authored over 580 research papers in

journals and conferences, and currently holds 34 Korean and 7 U.S. patents. He has served as a committee member on several international conferences, including Microprocesses and Nanotechnology, IEEE International Electron Devices Meeting, International Conference on Solid State Devices and Materials, and IEEE Silicon Nanoelectronics Workshop (technical program chair in 2005, general chair in 2007).

He is currently serving as an executive director of Institute of Electronics Engineers of Korea (IEEK) and the board member of IEEE Seoul Section. He received "Best Teacher" Award from SoEE in 1997, Doyeon Award for Creative Research from ISRC in 2003, Haedong Paper Award from IEEK in 2005, and Educational Award from College of Engineering, SNU, in 2006. Also, he received Haedong Academic Research Award from IEEK in 2008.