# Metal Insulator Gate Geometric HEMT: Novel Attributes and Design Consideration for High Speed Analog Applications

Ritesh Gupta\*, Ravneet Kaur\*\*, Sandeep Kr Aggarwal\*\*\*, Mridula Gupta\*, and R. S. Gupta\*

Abstract—Improvement in breakdown voltage  $(BV_{ds})$  a nd speed of the device are the key issues among the researchers for enhancing the performance of HEMT. Increased speed of the device aspires for shortened gate length  $(L_g)$ , but due to lithographic limitation, sh ortening  $L_g$  below sub-micrometer requires the inclusi on of various metal-insulator geometries like T-gate o nto the conventional architecture. It has been observe d that the speed of the device can be enhanced by m inimizing the effect of upper gate electrode on device characteristics, whereas increase in the  $BV_{ds}$  of the d evice can be achieved by considering the finite effect of the upper gate electrode. Further, improvement in  $BV_{ds}$  can be obtained by applying field plates, especia lly at the drain side. The important parameters affect ing  $BV_{ds}$  and cut-off frequency  $(f_T)$  of the device are t he length, thickness, position and shape of metal-insul ator geometry. In this context, intensive simulation w ork with analytical analysis has been carried out to s tudy the effect of variation in length, thickness and p osition of the insulator under the gate for various me tal-insulator gate geometries like T-gate, Γ-gate, Step-g ate etc., to anticipate superior device performance in conventional HEMT structure.

Index Terms—InAlAs/InGaAs HEMT, metal-insulator

\*\*\* HRMITM, GGSIP University, Hamidpur, Delhi-110036 E-mail: rsgu@bol.net.in geometries, breakdown voltage, cut-off frequency and maximum frequency of oscillations

# I. Introduction

High electron mobility transistors (HEMTs) consisting of InAlAs/InGaAs heterostructure, lattice matched to InP show promising characteristics due to its large conduction band discontinuity [1] and a large Γ-L valley separation [2]. However, some analog applications of HEMTs are still limited by the reduced breakdown voltage of these devices, which limits their power applications. In general, this problem is related to the properties of InAlAs/InGaAs material systems, in particular due to enhanced impact ionization effects in the narrow bandgap (0.73 eV) of In<sub>0.53</sub>Ga<sub>0.47</sub>As or tunneling due to low Schottky barrier height (0.66 eV) of In<sub>0.52</sub>Al<sub>0.48</sub>As [3-10]. Thus, ever since its development, significant efforts have been made to improve the speed and breakdown voltage of the device.

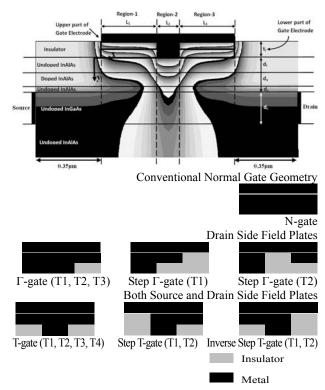

The speed of the device can be improved by shortening the gate length  $(L_g)$ , but shortening the  $L_g$  below sub-micrometer range requires various complex lithographic techniques [11-22]. This state-of-art performance requires careful attention to the technological details of gate formation, layer design, and MBE growth by multilevel resist process using e-beam lithography forming various metal insulator geometries like T-gate,  $\Gamma$ -gate etc. These geometries are usually fabricated in such a way that the device performance is mainly affected by the lower part of the T-gate geometry as shown in Fig. 1 with negligible effect of upper part for enhanced performance.

High breakdown voltage  $(BV_{ds})$  is amongst the

Manuscript received Nov. 15, 2009; revised Jan. 10, 2010.

<sup>\*</sup> Semiconductor Device Research Laboratory

Department of Electronic Science, University of Delhi South Campus, New Delhi – 110 021, India

<sup>\*\*</sup> Acharya Narendra Dev College, University of Delhi Department of Electronics, Govindpuri, Kalkaji, New Delhi-110019, India

**Fig. 1.** Cross-sectional view of different Metal-Insulator Geometric Pulsed doped High Electron Mobility Transistor acting field plates of different shapes on drain side and on both source and drain side.

primary requirements for achieving higher device reliability and the essence of achieving this in HEMT is to have an increasing depletion width at the surface of the channel from the drain to the Schottky gate. This increase in depletion depth can be accounted in terms of additional charges trapped at the surface of the channel, resulting in a lower electric field peak at the drain-side-edge of the gate and hence, higher  $BV_{ds}$ . By considering the finite effect of upper gate electrode as shown in Fig.1 on the device characteristics as in Field Plates (FP) between gate-drain spacing ( $\Gamma$ -gate) (which is usually ignored in T-gate geometries with passivation layer), increase in  $BV_{ds}$  [23-30] can be seen owing to increase in depletion depth as a combined effect of both the upper gate electrode and the lower gate in T-gate geometry.

Inclusion of FP modulates the electric field profile in such a way that three peaks are obtained in various  $\Gamma$ -gate instead of two peaks as in normal gate device due to the effect of different region of gate in  $\Gamma$ -gate geometry as shown in Fig. 1 with lower electric field peak in the region near the drain end. But this additional depletion region formed at the surface of the channel due to trapped charges leads to increase in gate-drain

capacitance and channel resistance thereby reducing the gain/cut-off frequency  $(f_T)$  of the device. Thus, to have desired characteristics without the emergence of these anomalies, the effect of upper part of the gate should be negligible [23-30], thereby showing a trade-off between the emergence of gate-drain capacitance and channel resistance and the increased breakdown voltage. Device optimization is thus required to tailor the field profile to improve the  $BV_{ds}$  and  $f_T$  of the device.

The important parameters affecting  $BV_{ds}$  and  $f_T$  of the device are the length, thickness, position and shape of metal-insulator geometry under the gate forming various metal-insulator gate geometries like T-gate,  $\Gamma$ -gate, Stepgate etc., with same lithographic length. All these parameter variations have been analyzed by performing analytical analysis supported by simulation work [31]. Generalized analytical models for HEMT [30, 32-34] have been used to obtain the analytical results for various metal-insulator geometries by considering different values of insulator thickness and permittivity in various regions of the device under consideration. Taking into account, the present lithographic scenario and controlled thermal reflow treatment [11] on multiresist process for fabrication, a gate geometry has been considered, which upon playing with the insulator thickness and dielectric constant of the material forming the gate-dielectric system can give an account of various metal-insulator geometries in which the effect of FP can be made possible either on source side (SFP), or drain side (DFP) or on both source and drain end (BFP). Since, the electric field suppression at the drain end is the prime requirement for increased  $BV_{ds}$ , the electric field suppression using SFP is not desirable and hence only those geometries having DFP and BFP have been given extensive consideration in this work. Analytical analysis have been performed for DFP and BFP devices and characteristics like drain current  $(I_d)$ , transconductance  $(g_m)$ , total trans-capacitance  $(C_T)$ ,  $f_T$  and maximum frequency of oscillations  $(f_{max})$  have been obtained to predict enhanced speed and reliability of the device in metal-insulator geometric HEMT in comparison to conventional HEMT structure.

# II. THEORETICAL CONSIDERATIONS

The basic HEMT structure used in the analysis as

shown in Fig. 1 consists of undoped InGaAs layer to form the 2DEG channel; an InAlAs undoped spacer-layer of thickness  $d_s$ ; a Si-doped InAlAs layer of thickness  $d_a$  to provide 2DEG sheet charge density; and an undoped InAlAs Schottky enhancement layer of thickness  $d_i$ . The gate geometry is such that the whole structure is divided into three regions -1, 2 and 3 respectively having different insulator (with permittivity  $\varepsilon_{lz}$ ) thicknesses ( $t_{lz}$ ) between gate and the semiconductor, where z = 1, 2 and 3 corresponding to region 1, 2 and 3 respectively. The comprehensive effect of the variation in the length, thickness and position of the insulator between the upper part of the gate electrode and the semiconductor giving rise to various innovative structures, have been studied and are shown in Fig. 1.

Generalized analytical model for HEMT [30, 32-34] has been used to obtain the analytical results. The expression of drain current in different region for different metal-insulator gate geometric HEMT is given by

$$I_{ds}|_{z} = \frac{Wq\mu_{o}}{C_{z}B_{z}^{2}} \frac{\left(f\left[y(V_{1z})\right] - f\left[y(V_{0z})\right]\right)}{\left(L_{z} + \frac{\mu_{o}\left(V_{1z} - V_{oz}\right)}{V_{sat}}\right)}$$

(1)

Where  $f(y) = A_z^2 y + \frac{y^2}{2} + \frac{4A_z y^{3/2}}{3}$  and  $y(V_z) = (\beta_z k_2)^2 + 4\beta_z (1 + \beta_z k_3) (V_{gs} - V_{off}|_z - k_1 - V_z - I_{ds} R_s)$  in which  $A_z = -\beta_z k_2$ ,  $B_z = 2(1 + \beta_z k_3)$ ,

$$C_{z} = -4\beta_{z} \left(1 + \beta_{z} k_{3}\right), \quad \beta_{z} = \frac{\varepsilon_{o} \cdot \varepsilon_{S}}{q \left(d_{T} + \frac{\varepsilon_{S} \cdot I_{Iz}}{\varepsilon_{Iz}}\right)} \quad \text{and} \quad V_{off} \Big|_{z} \text{ is the}$$

threshold voltage and  $d_T$  (=  $d_s + d_a + d_i$ ). The threshold voltage for planar doped/delta doped structure for different gate regions can be expressed as

$$V_{off}\Big|_{z} = \phi_{b} - \Delta E_{c} - \frac{q.N_{d}.d_{a}^{2}}{2.\varepsilon_{o}.\varepsilon_{s}} \left(1 + \frac{2.d_{i}}{d_{a}}\right) - \frac{q.N_{d}.t_{lz}.d_{a}}{\varepsilon_{o}.\varepsilon_{lz}}$$

(2)

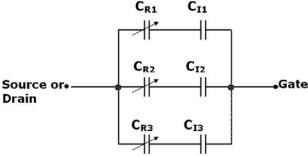

The gate to source capacitance and gate to drain capacitance obtained from the model can be represented as series and parallel combination of insulator capacitance ( $C_{II}$ ,  $C_{I2}$  and  $C_{I3}$ ) and depletion capacitances ( $C_{RI}$ ,  $C_{R2}$  and  $C_{R3}$ ) in various regions as shown in Fig. 2 to obtain the resultant capacitance for various metalinsulator geometries under consideration. Using the

**Fig. 2.** The circuit representation of gate capacitance of different Metal-Insulator Geometric Pulsed doped High Electron Mobility Transistor.

drain current model evaluated in the above section, gatesource capacitance and gate-drain capacitance is calculated in various regions and is given by [30, 32-34]

$$\begin{split} C_{gg}\Big|_{z} &= \frac{-q^{2}W^{2}\mu_{o}}{I_{di}}\frac{\partial I_{ds}}{\partial V_{gg}}\Big|_{V_{gg}} \Big(f_{1}\big[y(V_{z})\big] - f_{1}\big[y(V_{z-1})\big]\Big) - C.f_{2}\big[y(V_{z})\big] dy_{g}(V_{z}) + C.f_{2}\big[y(V_{z-1})\big] dy_{g}(V_{z-1}) \Big] dy_{g}(V_{z-1}) \Big] \\ C_{gd}\Big|_{z} &= \frac{-q^{2}W^{2}\mu_{o}}{I_{di}}\frac{\partial I_{ds}}{\partial V_{gd}}\Big|_{V_{gg}} \Big(f_{1}\big[y(V_{z})\big] - f_{1}\big[y(V_{z-1})\big]\Big) - C.f_{2}\big[y(V_{z})\big] dy(dV_{z}) + C.f_{2}\big[y(V_{z-1})\big] dy(dV_{z-1}) \\ \Big(3\Big) \end{split}$$

where

$$dy_g(V) = 1 - \frac{\partial V}{\partial V_{gs}}\Big|_{V_{gs}} - R_s \frac{\partial I_{ds}}{\partial V_{gs}}\Big|_{V_{gs}}$$

,

$dy(dV) = -dV - g_m R_s$  and

$$f_1(y) = \frac{1}{C_z B_z^4} \left( A_z^4 y + \frac{8A_z^3 y^{3/2}}{3} + 3A_z^2 y^2 + \frac{8A_z y^{5/2}}{5} + \frac{y^3}{3} \right)$$

$$f_2(y) = \frac{qW n_s|_z}{C} \left( \frac{qW n_s|_z \mu_o}{I_{ds}} - \frac{1}{E_c} \right)$$

# III. DEVICE REALIZATION AND CHARACTERIZATION

Various proposed structures have been created by dividing the region between the gate and the high band gap semiconductor (InAlAs) into six different regions, rectangular in shape of dimensions  $L_g/3 \times t_I$  where  $L_g$  is the gate length of the normal gate device and  $t_I$  is the thickness of the insulator. These regions are considered to be either metallic or insulating in nature to obtain the desired metal-insulator geometries as shown in Fig. 1. The results obtained for  $g_m$ ,  $C_T$ ,  $f_T$ ,  $f_{max}$  and  $f_{max}/f_T$  obtained at maximum value of  $g_m$  are tabulated in Table-1 & 2. The conventional gate (N-gate) device is

considered to be of 300 nm gate length and other shorter gate length devices used for improving speed are treated as combination of different metal-insulator geometries with passivation layer of SiO<sub>2</sub> for improving various reliability concerns of the device. Furthermore, to minimize the effect of parasitic resistance, analytical and simulation analysis have been performed by considering the source and drain electrode to be vertical in geometry. Various models included in simulation are the CONMOB, FLDMOB and QUANTUM model. The simulated (symbols) [31] and analytical results (solid lines) are compared with each other in this effort and are found to be in good agreement thereby proving the validity of the proposed analytical model.

#### 1. Drain side Field Plates (DFP)

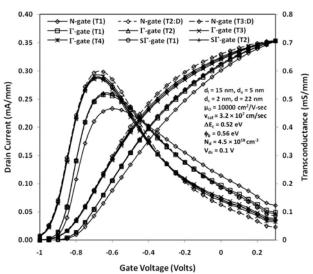

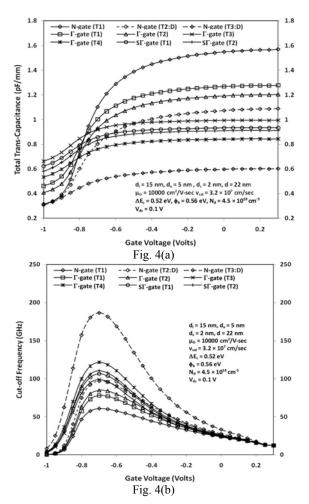

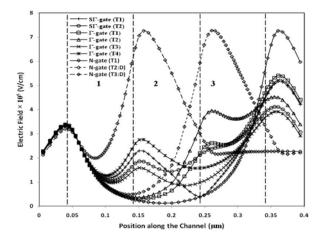

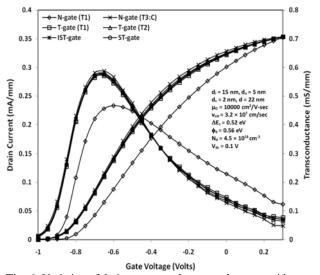

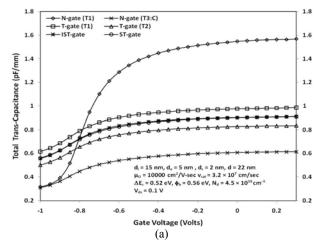

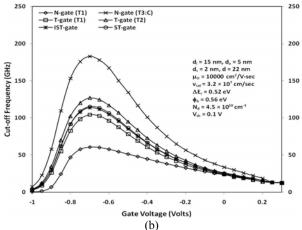

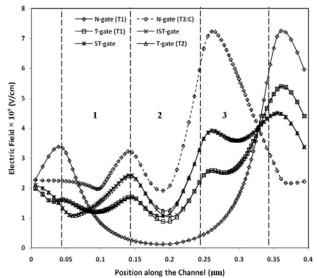

Analysis of FP on drain side for different lengths, thicknesses and shapes of metal-insulator gate geometries have been performed by considering nine different gate geometries listed in Table-1, having lithographic length of 300 nm but leading to FP of length 100 nm and 200 nm. The variation of  $g_m \& I_d$ ,  $f_T$  and  $C_T$  with gate voltage ( $V_{gs}$ ) are shown in Fig. 3, 4(a) and 4(b) respectively for 200 nm and 300 nm gate length devices for the nine different metal-insulator geometric HEMT devices as shown in Fig. 1. Fig. 5 shows the electric field (EF) profile of all these devices at sufficient gate and drain bias ( $V_{gs} = -3.0 \ V \& V_{ds} = 5.0$ ) thereby enabling all

**Fig. 3.** Variation of drain current and transconductance with gate voltage for various metal-insulator geometric structures acting as field plate on drain side. (Solid) analytical (symbol) simulated [31].

**Fig. 4.** (a) Variation of total Trans-capacitance with gate voltage for various metal-insulators geometric structures acting as field plate on drain side. (Solid) analytical (symbol) simulated [31]. (b) Variation of total cut-off frequency with gate voltage for various metal-insulators geometric structures acting as field plate on drain side. (Solid) analytical (symbol) simulated [31].

**Fig. 5.** Variation of Electric field with the position along the channel for various metal-insulators geometric structures acting as field plate on drain side. (Solid) analytical (symbol) simulated [31].

the three regions comprising the channel to reach their threshold values and also causes the EF at the drain end to be larger in magnitude as compared to that obtained at the source end. The results obtained for  $g_m$ ,  $C_T$ ,  $f_T$ ,  $f_{max}$ and  $f_{max}/f_T$  ratio at  $V_{ds} = 0.1 \ V$  and  $V_{gs}$  corresponding to maximum value of  $g_m$  have been tabulated in Table 1(a). The results obtained from the table demonstrate that  $g_m$ increases from N-gate (T1) to  $\Gamma$ -gate (T1) followed by relative increment in  $\Gamma$ -gate (T2), N-gate (T2: D),  $\Gamma$ -gate (T3), S $\Gamma$ -gate (T1), S $\Gamma$ -gate (T2),  $\Gamma$ -gate (T4) and Ngate (T3: D). This shows that introduction of insulator between the N-gate device leads to increase in  $g_m$ , and maximum value of  $g_m$  is seen when the effect of upper part of gate electrode is negligible. Further, it is seen that the increase in length of insulator underneath the upper part of gate electrode  $(L_{fp})$  has larger effect than the increase of insulator thickness  $(t_I)$ . S $\Gamma$ -gate geometry having higher  $t_l$  towards drain side has larger value of  $g_m$ in comparison to what is obtained when having higher value of  $t_I$  in the middle.  $\Gamma$ -gate geometry as compared to step gate profile shows larger enhancement in  $g_m$ .

The enhancement in  $g_m$  in different devices are due to reduction in channel resistance, which can be explained

by considering various regions as various devices connected in series. The device having insulator in between gate and semiconductor have a larger threshold voltage  $(V_{th})$  than the device having gate electrode in immediate contact with the semiconductor. The combination of these devices leads to different  $V_{th}$  in different regions; however it's the lowest value that accounts the  $V_{th}$  of the overall structure. As a result, the device having insulator in between, keep on gaining the carrier concentration with the variation of  $V_{gs}$ , until the other device switches from OFF to ON state. When the device having gate electrode in immediate contact with the semiconductor, switched from OFF to ON state, these carriers start flowing right away under the influence of drain voltage, thus resulting in a sharp increase in  $I_{ds}$  from its normal value thereby increasing the slope of the  $I_{ds}$ - $V_{gs}$  characteristics and hence  $g_m$  of the device. Increasing  $t_I$  enhances the carrier concentration in the channel or even maximizes it if the effect of upper gate electrode is negligible, thus raising the  $g_m$  further. Increasing  $L_{fp}$  increases the peak value of  $g_m$ . The variation in characteristics of  $S\Gamma$ -gate with variation of position of insulator with larger thickness is due to the

**Table 1(a).** Device Characteristics for Drain Side Field Plates

| Device               | $L_g$ | $t_{II}/t_{I2}/t_{I3}$ | $V_g$   | g <sub>m</sub> | $C_T$   | $f_T$ | $f_{max}$ | $f_{max}/f_T$ |

|----------------------|-------|------------------------|---------|----------------|---------|-------|-----------|---------------|

|                      | (nm)  | (nm)                   | (Volts) | (S/mm)         | (pF/mm) | (GHz) | (GHz)     |               |

| N-gate(T1)           | 300   | 0/0/0                  | -0.60   | 0.47           | 1.29    | 57.7  | 105.5     | 1.83          |

| $\Gamma$ -gate(T1)   | 200   | 0/0/10                 | -0.65   | 0.51           | 1.07    | 76.9  | 168.5     | 2.19          |

| $\Gamma$ -gate(T2:D) | 200   | 0/0/20                 | -0.65   | 0.52           | 0.99    | 83.7  | 182.2     | 2.18          |

| N-gate $(T2)$        | 200   | $0/0/\infty$           | -0.65   | 0.52           | 0.86    | 95.6  | 198.8     | 2.08          |

| Γ-gate(T3:D)         | 100   | 0/10/10                | -0.70   | 0.57           | 0.92    | 98.9  | 205.2     | 2.08          |

| SΓ-gate(T1)          | 100   | 0/20/10                | -0.70   | 0.57           | 0.86    | 106.5 | 225.2     | 2.12          |

| SΓ-gate(T2)          | 100   | 0/10/20                | -0.70   | 0.58           | 0.83    | 110.4 | 236.0     | 2.14          |

| Γ-gate(T4)           | 100   | 0/20/20                | -0.70   | 0.58           | 0.76    | 121.6 | 267.4     | 2.20          |

| N-gate(T3)           | 100   | $0/\infty/\infty$      | -0.65   | 0.60           | 0.52    | 181.4 | 362.0     | 2.00          |

Table 1(b). Electric field peaks for Drain Side Field Plates

| Device       | $L_g$ $(nm)$ | $t_{II}/t_{I2}/t_{I3}$ (nm) | $V_{th1}/V_{th2}/V_{th3}$<br>(-ve)(Volts) | $E_{p1}$ (KV/cm) | $E_{p2}$ (KV/cm) | $E_{p3}$ (KV/cm) | $E_{p4}$ (KV/cm) |

|--------------|--------------|-----------------------------|-------------------------------------------|------------------|------------------|------------------|------------------|

| N-gate(T1)   | 300          | 0/0/0                       | 0.83/0.83/0.83                            | 339              | -                | -                | 702              |

| Γ-gate(T1)   | 200          | 0/0/10                      | 0.83/0.83/2.03                            | 338              | -                | 261              | 541              |

| Γ-gate(T2:D) | 200          | 0/0/20                      | 0.83/0.83/3.23                            | 338              | -                | 395              | 453              |

| N-gate(T2)   | 200          | 0/0/∞                       | 0.83/0.83/                                | 338              | -                | 727              | -                |

| Γ-gate(T3:D) | 100          | 0/10/10                     | 0.83/2.03/2.03                            | 334              | 159              | -                | 522              |

| SΓ-gate(T1)  | 100          | 0/20/10                     | 0.83/3.23/2.03                            | 332              | 229              | -                | 515              |

| SΓ-gate(T2)  | 100          | 0/10/20                     | 0.83/2.03/2.03                            | 313              | 186              | 241              | 411              |

| Γ-gate(T4)   | 100          | 0/20/20                     | 0.83/3.23/3.23                            | 331              | 276              | -                | 391              |

| N-gate(T3)   | 100          | $0/\infty/\infty$           | 0.83/ /                                   | 319              | 725              | -                | -                |

increase of depletion width  $V_{ds}$  underneath the FP.

There are three distinct peaks seen in  $g_m$  variation with  $V_{gs}$  for the concerned devices of  $L_g = 300 \text{ nm}$ , 200 nm and 100 nm respectively. However, the variation of  $t_I$  has negligible effect on  $g_m$ , but it could lead to reduction in  $C_T$  as shown in Fig. 4(a), thereby increasing  $f_T$  of the device. The results obtained from Fig. 4(a & b), tabulated in Table 1(a) show that  $C_T$  decreases in N-gate (T1) followed by  $\Gamma$ -gate (T1),  $\Gamma$ -gate (T2), N-gate (T2: D),  $\Gamma$ -gate (T3),  $S\Gamma$ -gate (T1),  $S\Gamma$ -gate (T2),  $\Gamma$ -gate (T4) and N-gate (T3: D) and same is the order for the increase in  $f_T$  and  $f_{max}$  for different devices under consideration. The variation in  $C_T$  can be explained from the circuit shown in Fig. 2. For normal gate structures there is nothing between the upper gate electrode and the semiconductor, as a result, there is only a parallel combination of depletion capacitances in the device. But for the other devices, there is a region having an insulator between the upper gate electrode and the semiconductor. This lowers the effect of  $V_{gg}$  on depletion of carriers thus decreasing the depletion capacitance  $(C_R)$ in that region. The series combination of  $C_R$  with insulator capacitance  $(C_l)$  results in the further lowering of the gate capacitance in that region. The parallel combination of this gate capacitance with other regions lowers the overall capacitance  $(C_T)$  of the device. Increasing  $L_{fp}$  leads to enhancement in  $C_R$  in two regions in place of one that further reduces the  $C_T$  of the device. Increase in  $t_I$  decreases the  $C_R$  as well as  $C_I$  thus reduces the  $C_T$  of the device. The variation in characteristics of  $S\Gamma$ -gate with variation in position of insulator layer is due to the increase of depletion width as an effect of  $V_{ds}$ underneath the FP. It is found from the analysis that with the increase in  $V_{ds}$  and  $t_{I}$ , the enhancement in the device saturates due to saturation in insulator capacitance ( $C_I \propto$  $1/t_I$ ). With increase in  $V_{ds}$ , the device performance saturation is achieved at smaller values of  $t_I$  due to lower  $C_T$  value obtained at higher  $V_{ds}$ . Results also show that device with  $L_g = 100 \ nm$  and  $L_{fp} = 200 \ nm$  has larger impact of FP in reducing the  $C_T$  than the devices with  $L_g$  $= 200 \ nm \ and \ L_{fp} = 100 \ nm.$

From Table 1(a), it is quite clear that although N-gate has maximum enhancement in  $f_T$  and  $f_{max}$  in comparison to metal-insulator geometries but these geometries have higher enhancement in  $f_{max}/f_T$  ratio desired for analog applications. Furthermore, to improve the reliability

issue, the effect of upper gate electrode should be finite as can be seen from Fig. 5. Fig. 5 shows four different peaks in the electric field profile in the channel viz.  $E_{p1}$  (source side of gate edge),  $E_{p2}$  (100 nm from  $E_{p1}$ ),  $E_{p3}$  (100 nm from  $E_{p2}$ ) and  $E_{p4}$  (100 nm from  $E_{p3}$ ). The value of electric field obtained at these peaks is tabulated in Table 1(b). Results obtained from the table shows that  $E_{p4}$  has the maximum value in the channel at  $V_{gs} = -3.0 \ V$  and  $V_{ds} = 5.0 \ V$  and the value of  $E_{p4}$  decreases in N-gate (T1)/ N-gate (T2: D)/ N-gate (T3: D) followed by  $\Gamma$ -gate (T1),  $\Gamma$ -gate (T3),  $\Gamma$ -gate (T1),  $\Gamma$ -gate (T2),  $\Gamma$ -gate (T2) and  $\Gamma$ -gate (T4). This suggests that increase in  $t_1$  decreases the peak at the gate edge near drain side but raises the peak in the middle, whereas, increase in  $L_{fp}$  suppresses both these peaks.

The formation of peaks in the electric field profile and variation in these peaks can be explained by dividing the whole channel into various regions as shown in Fig. 1. For N-gate (T1) device, in all the three regions, metal is in direct contact with semiconductor and have almost same  $V_{th}$ . So there are only abrupt variations in the channel at the edges of gate electrode leading to formation of two peaks  $E_{p1}$  and  $E_{p4}$ . For  $\Gamma$ -gate (T1) device, region- 1 & 2 have metal is in direct contact with semiconductor, whereas, the region-3 have insulator in between metal and semiconductor. So, region- 1 & 2 have same  $V_{th}$ , almost equivalent to the  $V_{th}$  of the overall device, whereas, the region-2 have higher  $V_{th}$  leading to higher value of minimum channel potential  $[V_c \text{ (min)}]$ and lower value of electric field in that region. Furthermore, equilibrium between these regions has been established and due to variation in  $V_{th}$  in these regions, minimum channel potential in first two regions has also been raised thereby minimizing electric field at the gate edge of source end. Moreover, the abrupt variation between region- 2 & 3 leads to formation of peak  $E_{p2}$  in the channel. For  $\Gamma$ -gate (T2) device,  $t_I$  have been increased resulting in higher  $V_{th}$  in that region compared to Γ-gate (T1) device leading to gradual variation at the gate edge on drain side thereby reducing the value of  $E_{p4}$ . However, due to greater abruptness between the region- 2 & 3, this effect also leads to increase in value of  $E_{p3}$ . But the  $E_{p3}$  is still lesser than the  $E_{p4}$  so increase in insulator thickness enhances the performance of  $\Gamma$ -gate HEMT device. It is found from the analysis that the value of  $E_{p4}$  and  $E_{p3}$  are strongly

dependent on the  $V_{ds}$  and  $t_I$ . The effect of increase in  $t_I$ increases the  $E_{p3}$  and decreases the  $E_{p4}$  whereas the effect of increase in  $V_{ds}$  increases the  $E_{p4}$  and decreases the  $E_{p3}$ . So the device design required for higher  $BV_{ds}$  should have higher value of  $E_{p4}$  in comparison to  $E_{p3}$ . However, at lower  $V_{ds}$  a situation may arise where  $E_{p3}$  can become greater than  $E_{p4}$  and in that case S $\Gamma$ -gate can be used to further optimize the device. In some cases while optimizing, both  $E_{p3}$  and  $E_{p4}$  are found to be lesser than  $E_{pl}$  thereby raising the requirement for source side electric field profile optimization. Increasing the  $t_I$  can even eliminate the  $E_{p4}$  completely and can even raises the  $E_{P3}$  to  $E_{p4}$  in N-gate (T2) device. Under such circumstances, maximum value of  $f_T$  is obtained from Ngate (T2) device. In  $\Gamma$ -gate (T3) device, metal is in direct contact with semiconductor in region-1, whereas, region-2 & 3 have insulator between metal and semiconductor, thus raising the potential in region- 2 & 3 thereby lowering the value of  $E_{p4}$  as compared to what is obtained in N-gate (T1) device. This is attributed to the larger length of region having higher  $V_{th}$  in comparison to region having lower  $V_{th}$ . The equilibrium has to be established between these regions which reduces both the value of  $E_{p4}$  and  $E_{p2}$  in comparison with the values obtained for Γ-gate (T1) device. Similarly, the effect of increase in  $t_I$  and  $L_{fp}$  can be seen in  $\Gamma$ -gate (T4) device.

In S $\Gamma$ -gate (T1) device, metal is in direct contact with semiconductor in region-1 and in region-2 & 3 there is an insulator in between metal and the semiconductor, and  $t_l$  in region- 2 is of double the thickness in region- 3. As there is larger abruptness between region- 1 & 2, so,  $E_{p2}$  is larger than that for  $\Gamma$ -gate (T3). The abruptness between the regions B & C can also lead to peak in electric field profile  $(E_{p3})$ , but at particular  $V_{gs}$ ,  $V_{ds}$  and  $t_I$ this peak can even vanish in this device. This abruptness in region- 2 and 3 also reduces the value of  $E_{p4}$  in comparison to  $\Gamma$ -gate (T3). Although  $E_{p4}$  in this case is larger in comparison to  $\Gamma$ -gate (T4), but  $E_{p2}$  has reduced much more in comparison to  $\Gamma$ -gate (T4) that make this geometry useful at lower drain voltage when the value of middle peaks become greater than the peak at drain end. This happens due to the use of higher value of  $t_I$  in the design for higher  $BV_{ds}$ . S $\Gamma$ -gate (T2) device have increase in  $t_I$  from source to drain reducing abruptness at the edge of region- 1 & 2 and 2 & 3, thus reducing both

the peaks  $E_{p2}$  and  $E_{p3}$ .

# 2. Both Drain and Source Side Field Plates (BFP)

Analysis of FP on both drain and source side for length, thickness and shape of metal-insulator gate geometries have been performed by considering six different gate geometries listed in Table 2, having lithographic length of 300 nm but leading to FP of length 100 nm on both source and drain side. The variation of  $g_m$  and  $I_d$ ,  $f_T$  and  $C_T$  with  $V_{gs}$  are shown in Fig. 6, 7(a) and 7(b) respectively for  $L_g=100$  nm and 300 nm devices for these six different metal-insulator geometric HEMT devices. Fig. 8 shows the electric field profile of all these devices at  $V_{gs} = -3.0 \text{ V}$  and  $V_{ds} = 5.0 \text{ V}$ . The results obtained for  $g_m$ ,  $C_T$ ,  $f_T$ ,  $f_{max}$  and  $f_{max}/f_T$  ratio at  $V_{ds} = 0.1 \text{ V}$ and  $V_{gs}$  corresponding to maximum value of  $g_m$  have been tabulated in Table 2(a). The results obtained from the table demonstrate that  $g_m$  increases in N-gate (T1) followed by increase in T-gate (T1), IST-gate, ST-gate, Tgate (T2) and N-gate (T3: C). However,  $C_T$  decreases in N-gate (T1) followed by decrease in T-gate (T1), ISTgate, ST-gate, T-gate (T2) and N-gate (T3: C) and same is the order of increase in  $f_T$  and  $f_{max}$ . Comparing the results in Table 1(a) & 2(a), it is found that BFP offers larger enhancements in device characteristics in comparison to DFP due to decrease in depletion width at the source end even in the absence of  $V_{ds}$ . Furthermore,

**Fig. 6.** Variation of drain current and transconductance with gate voltage for various metal-insulator geometric structures acting as field plate on both drain and source side. (Solid) analytical (symbol) simulated [31].

**Fig. 7.** (a) Variation of total Trans-capacitance with gate voltage for various metal-insulators geometric structures acting as field plate on both drain and source side. (Solid) analytical (symbol) simulated [31]. (b) Variation of total cut-off frequency with gate voltage for various metal-insulators geometric structures acting as field plate on both drain and source side. (Solid) analytical (symbol) simulated [31].

from Fig. 8 it is clear that BFP suppress the field at both drain and source end, whereas, DFP suppress the field only at the drain end. Results tabulated in Table 2(b) also shows that as there is lesser field at the source end so the inclusion of insulator layer of even small thickness i.e.,  $10 \text{ nm } t_I$ , suppresses the source side field  $(E_{pI})$  completely. Comparing the results for IST-gate and ST-gate geometry from Table-2(a), it is found that increase of the  $t_I$  at drain end is more beneficial than increase of the  $t_I$  at source end in suppressing the electric field and this fact is reemphasized by Fig. 8 and Table-2(b). Increase of  $t_I$  uniformly on both source and drain side

**Fig. 8.** Variation of Electric field with the position along the channel for various metal-insulators geometric structures acting as field plate on both drain and source side. (Solid) analytical (symbol) simulated [31].

Table 2(a). Device Characteristics for both Drain and Source Side Field Plates

| Device       | $L_g \ (nm)$ | $t_{II}/t_{I2}/t_{I3}$ (nm) | $V_{gs}$ (Volts) | 8 <sub>m</sub><br>(S/mm) | $C_T$ $(pF/mm)$ | $f_T$ $(GH_Z)$ | f <sub>max</sub><br>(GHz) | f <sub>max</sub> /f <sub>T</sub> |

|--------------|--------------|-----------------------------|------------------|--------------------------|-----------------|----------------|---------------------------|----------------------------------|

| N-gate(T1)   | 300          | 0/0/0                       | -0.60            | 0.47                     | 1.29            | 57.7           | 105.5                     | 1.83                             |

| T-gate(T1)   | 100          | 10/0/10                     | -0.65            | 0.57                     | 0.89            | 102.7          | 226.2                     | 2.20                             |

| IST-gate     | 100          | 20/0/10                     | -0.65            | 0.57                     | 0.81            | 111.6          | 240.1                     | 2.15                             |

| ST-gate      | 100          | 10/0/20                     | -0.65            | 0.58                     | 0.81            | 113.5          | 240.2                     | 2.12                             |

| T-gate(T2)   | 100          | 20/0/20                     | -0.65            | 0.58                     | 0.74            | 124.5          | 271.0                     | 2.18                             |

| N-gate(T3:C) | 100          | $\infty/0/\infty$           | -0.65            | 0.59                     | 0.52            | 178.1          | 356.8                     | 2.00                             |

**Table 2(b).** Electric field peaks for both Drain and Source Side Field Plates

| Device              | $L_g$ | $t_{II}/t_{I2}/t_{I3}$ | $V_{th1}/V_{th2}/V_{th3}$ | $E_{pl}$ | $E_{p2}$ | $E_{p3}$ | $E_{p4}$         |

|---------------------|-------|------------------------|---------------------------|----------|----------|----------|------------------|

|                     | (nm)  | (nm)                   | (-ve)(Volts)              | (KV/cm)  | (KV/cm)  | (KV/cm)  | ( <i>KV/cm</i> ) |

| N-gate(T1)          | 300   | 0/0/0                  | 0.83/0.83/0.83            | 339      | -        | -        | 721              |

| T-gate(T1)          | 100   | 10/0/10                | 2.03/0.83/2.03            | -        | 171      | 259      | 539              |

| IST-gate            | 100   | 20/0/10                | 3.23/0.83/2.03            | -        | 243      | 258      | 539              |

| ST-gate             | 100   | 10/0/20                | 2.03/0.83/3.23            | -        | 169      | 393      | 451              |

| T-gate(T2)          | 100   | 20/0/20                | 3.23/0.83/3.23            | -        | 241      | 392      | 451              |

| <i>N-gate(T3:C)</i> | 100   | $\infty/0/\infty$      | /3.23/                    | -        | 322      | 724      | -                |

has larger effect in increasing both  $g_m$  and  $f_T$  than device with different  $t_I$  on both source and drain side. In that case also, by considering the finite effect of upper gate electrode on both source and drain side, the  $f_{max}/f_T$  ratio enhances and  $f_T$  and  $f_{max}$  decreases.

# IV. CONCLUSIONS

Intensive simulation work with analytical analysis has been carried out to study the effect of variations in length, thickness and position of the insulator under the gate for various metal-insulator gate geometries like T-gate, Γgate, Step-gate etc., to anticipate superior device performance in conventional HEMT structure with same lithographic length. Analysis has been performed for DFP and for BFP. Analytical results are compared with simulated results and are found to be in good agreement with each other, thus proving the validity of the analytical model. Variation of  $t_I$  has negligible effect on  $g_m$ , but it could lead to reduction on  $C_T$ , thereby increasing the  $f_T$  of the device.  $C_T$  decreases in N-gate (T1) followed by reduction of  $C_T$  in  $\Gamma$ -gate (T1),  $\Gamma$ -gate (T2), N-gate (T2: D), Γ-gate (T3), T-gate (T1), SΓ-gate (T1), SΓ-gate (T2), IST-gate, ST-gate, Γ-gate (T4), Tgate (T2), N-gate (T3: C) and N-gate (T3: D) and same is the order of increase in  $f_T$  and  $f_{max}$ . Increase in  $t_I$ decreases the peak at the gate edge near drain side but raises the peak in the middle and can be even suppressed Step-gate geometries. BFP offers larger enhancements in device characteristics in comparison to DFP. Furthermore, BFP suppress the field at both drain and source end, whereas, DFP suppress the field only at the drain end. However  $f_T$  and  $f_{max}$  decreases by considering the finite effect of upper gate electrode on both source and drain side but it enhances the  $f_{max}/f_T$  ratio which is desired for analog applications.

# **ACKNOWLEDGMENTS**

The authors acknowledge the Department of Science and Technology (D.S.T) and Council of Scientific and Industrial Research (CSIR), Government of India for providing the necessary financial support for this work.

# REFERENCES

- [1] D. F. Weslch, G. W. Wicks, and L. F. Eastman, "Calculation of the conduction band discontinuity for InAlAs/InGaAs heterojunction," *J. Appl. Phys.*, Vol. 55, p.3176 1984.

- [2] K. Y. Chen, A. Y. Cho, S. G. Christman, T. P. Pearsall and J. E. Rowe "Measurement of the Γ-L separation in InGaAs by ultraviolet photoemission," *Appl. Phys. Lett.*, Vol.40, p. 423 1980.

- [3] Sandeep R. Bahl and Jesus A. del Alamo, "Physics of Breakdown in InAlAs/n<sup>+</sup> InGaAs Heterostructure Field –Effect Transistors," *IEEE Trans. Electron Devices*, Vol.41, No.12, December 1994 2268-2275.

- [4] Sandeep R. Bahl, Jesus A. del Alamo, Jurgen Dickmann and Steffen Schildberg, "Off State Breakdown in InAlAs/InGaAs MODFET's," *IEEE Trans. Electron Device*, Vol.42, No.1, January 1995 15-22.

- [5] Aldo Di Carlo, Lorenzo Rossi, Paolo Lugli, Gunther Zandler, Gaudenzio Meneghesso, Mike Jackson and Enrico Zanoni, "Monte Carlo Study of the Dynamic Breakdown Effects in HEMT's," *IEEE Electron Device Letters*, Vol.21, No.4 April 2000, 149-151.

- [6] Mark H. Somerville, Chris S. Putnam and Jesus A. del Alamo, "Determining dominant breakdown mechanisms in InP HEMTs," *IEEE Electron Device letters*, Vol.22, No.12, December 2001 565-567.

- [7] M. Borgarino, R. Menozzi, D. Dieci, L. Cattani and F. Fantini, "Reliability physics of compound semiconductor transistors for microwave applications," *Microelectronics Reliability* Vol.41, 2001, 21-30.

- [8] Gaudenzio Meneghesso and Enrico Zanoni, "Failure modes and mechanisms of InP-based and metamorphic high electron mobility transistors," *Microelectronic reliability*, Vol.42, 2002, 685-708.

- [9] Ammar Sleiman, Aldo Di Carlo, Paolo Lugli, G. Meneghesso, E. Zanoni and J. L. Thobel, "Channel Thickness dependence of Breakdown Dynamic in InP-based lattice-Matched HEMTs," *IEEE Trans. Electron Device*, Vol.50, No.10, October 2003 2009-2014.

- [10] K. Higuchi, H. Matsumoto, T. Mishima and T. Nakamura, "High Breakdown voltage InAlAs/InGaAs High Electron Mobility Transistors on GaAs with Wide Recess Structure," *Jpn. J. Appl. Phys.* Vol. 38, 1999, pp.1178-1181.

- [11] Y. C. Lien et al, "Low-Noise Metamorphic HEMTs with Reflowed 0.1-μm T-Gate," *IEEE Electron Device Letters*, Vol.25, No.6, p.348 June 2004.

- [12] K. Elgaid, H. McLelland, M. Holland, D. A. J. Moran, C. R. Stanley, and I. G. Thayne, "50-nm T-Gate Metamorphic GaAs HEMTs With f<sub>T</sub> of 440 GHz and Noise Figure of 0.7 dB at 26 GHz," *IEEE Electron Device Letters*, Vol.26, No.11, p.784 November 2005.

- [13] Ming-Jyh Hwu, Hsien-Chin Chiu, Shih-Cheng Yang, and Yi-Jen Chan, "A Novel Double-Recessed 0.2-\_m T-Gate Process for Heterostructure InGaP—InGaAs Doped-Channel FET Fabrication," *IEEE Electron Device Letters*, Vol.24, No.6, p.381 June 2003

- [14] D.S. Wen, C.C-H. Hsu, Y. Taur, D.S. Zicherman, M.R. Wordeman, and T.H. Ning, "A Self-Aligned Inverse-T Gate Fully Overlapped LDD Device for Sub-Half Micron CMOS," *IEDM Tech. Dig.*, p. 766-769, 1989.

- [15] Y. C. Chou, et al, "Reliability Investigation of 0.07μm InGaAs–InAlAs–InP HEMT MMICs With Pseudomorphic In<sub>0.75</sub>Ga<sub>0.25</sub>As Channel," *IEEE Electron Device Letters*, Vol. 24, No.6, p.378 June 2003.

- [16] G. H. Jessen, et al, "High Performance 0.14 μm Gate-Length AlGaN/GaN Power HEMTs on SiC," *IEEE Electron Device Letters*, Vol.24, No.11, p. 677 November 2003.

- [17] S. J. Koester, R. Hammond, and J. O. Chu, "Extremely High Transconductance Ge/Si<sub>0.4</sub>Ge<sub>0.6</sub> p-MODFET's Grown by UHV-CVD," *IEEE Electron Device Letters*, Vol.21, No.3, p.110 March 2000.

- [18] D. Geiger et al, "InGaP/InGaAs HFET with High Current Density and High Cut-Off Frequencies," *IEEE Electron Device Letters*, Vol.16, No.6, p.259 June 1995.

- [19] W.-S. Lour, *Member, IEEE*, W. L. Chang, Y. M. Shih, and W. C. Liu, "New Self-Aligned T-Gate InGaP/GaAs Field-Effect Transistors Grown by LP-MOCVD," *IEEE Electron Device Letters*, Vol. 20, No.6, p. 304 June 1999.

- [20] T. Enoki, H. Yokoyama, Y. Umeda and T. Otsuji, "Ultrahigh-Speed Integrated Circuits Using InP Based HEMTs," *Jpn. J. Appl. Phys.*, Vol.37, pp. 1359-1364 1998.

- [21] K. L. Tan et al, "140 GHz 0.1µm Gate-length pseudomorphic InAlAs/InGaAs/InP HEMT," *IEEE IEDM Tech. Digest*, 1991 p. 239.

- [22] A. Lepore, M. Levy, H. Lee, and E. Kohn, "Fabrication and Performance of 0.1-pm Gate-Length AlGaAs/GaAs HEMT's with Unity Current Gain Cutoff Frequency in Excess of 110 GHz," *IEEE Trans Electron Device*, Vol.35, No.12, p. 2441 December 1988.

- [23] Shreepad Karmalkar, Michael S. Shur, Grigory Simin, and M. Asif Khan, "Field-Plate Engineering for HFETs," *IEEE Trans Electron Devices*, Vol.52, 2005, Pp. 2534-2540.

- [24] N.-Q. Zhang, S. Keller, G. Parish, S. Heikman, S. P. DenBaars, and U. K. Mishra, "High Breakdown GaN HEMT with Overlapping Gate Structure," *IEEE Electron Device Lett.*, Vol.21, No.9, September 2000, pp.421-423.

- [25] Shreepad Karmalkar, Jianyu Deng, Michael S. Shur, and Remis Gaska "RESURF AlGaN/GaN HEMT for High Voltage Power Switching," *IEEE Electron Device Lett.*, Vol.22, No.8, August 2001, pp.373 -375.

- [26] Shreepad Karmalkar and Umesh K. Mishra, "Enhancement of Breakdown Voltage in AlGaN/GaN High Electron Mobility Transistors Using a Field Plate," *IEEE Trans Electron Devices*, Vol.48, No.8, August 2001, pp. 1515-1521.

- [27] Y. Ando, Y. Okamoto, H. Miyamoto, T. Nakayama, T. Inoue, and M. Kuzuhara, "10-W/mm AlGaN—GaN HFET With a Field Modulating Plate," *IEEE Electron Device Lett.*, Vol.24, No.5, May 2003, pp. 289-291.

- [28] Shreepad Karmalkar and N. Soudabi, "A Closed-Form Model of the Drain-Voltage Dependence of the OFF-State Channel Electric Field in a HEMT With a Field Plate," *IEEE Trans Electron Devices*, Vol.53, No.10, October 2006, pp. 2430-2437.

- [29] Huili Xing, Y. Dora, A. Chini, S. Heikman, S. Keller, and U. K. Mishra, "High Breakdown Voltage AlGaN–GaN HEMTs Achieved by Multiple Field Plates," *IEEE Electron Device Lett.*, Vol.25, No.4, April 2004, pp. 161-163.

- [30] Ritesh Gupta, Sandeep kr Aggarwal, M. Gupta and R. S. Gupta, "Short Channel Analytical Model for High Electron Mobility Transistor to obtain Higher Cut-Off Frequency maintaining the Reliability of the Device," *Journal of Semiconductor Technology and Science (JSTS)* Vol. 7, no.2, pp. 120-131 June 2007.

- [31] *ATLAS Device Simulator*, Silvaco Int., Santa Clara, CA, Spring-2003.

- [32] Ritesh Gupta, Sandeep kr Aggarwal, M. Gupta and R. S. Gupta, "Analytical Model for Metal insulator Semiconductor High Electron Mobility Transistor (MISHEMT) for its high frequency and high power applications," *Journal of Semiconductor Technology and Science (JSTS)*, Vol.6, No.3, pp.189-198 September 2006.

- [33] Ritesh Gupta, A. Kranti, S. Haldar, M. Gupta and R. S. Gupta, "An Analytical parasitic resistance dependent  $I_d$ - $V_d$  model for Planar doped InAlAs/InGaAs/InP HEMT using Non-linear Charge control Analysis," *Microelectronic Engineering*, Vol.60, pp. 323-337 2002.

- [34] Ritesh Gupta, Servin Rathi, Ravneet Kaur, Mridula Gupta, R.S. Gupta, "T-gate geometric (solution for submicrometer gate length) HEMT: Physical analysis, modeling and implementation as parasitic elements and its usage as dual gate for variable gain amplifiers", Superlattice and Microstructures Vol.45, pp.105-116, 2009.

Ritesh Gupta was born in Delhi, India, on July 20, 1976. He received the B.Sc. and M.Sc. degrees in physics and the Ph.D. degree in microelectronics from the University of Delhi, Delhi, in 1997, 1999, and

2003, respectively.

He joined the Semiconductor Devices Research Laboratory, Department of Electronic Science, University of Delhi South Campus, New Delhi, India, in 1999 as a Junior Research Fellow, where he is currently a Research Associate on a Department of Science and Technology (DST)-sponsored project. His research interests include modeling and simulation of Si/SiC/InP MESFET/ MOSFET/HEMT devices for high-frequency applications. He has published 30 technical papers in various journals and conferences.

Ravneet Kaur was born in Delhi, India, on December 13, 1981. She received the B.Sc.(H), M.Sc. and Ph. D degrees in Electronics from the University of Delhi, New Delhi, in 2002, 2004 and 2008, respectively.

She has been appointed as Assistant Professor in Department of Electronics, Acharya Narendra Dev College, University of Delhi in 2009. Her area of interest includes analytical analysis, characterization and simulation of short channel effects in sub-100nm MOSFET for high performance. The work involves the physics based analytical modeling of MOS devices and simulating their intrinsic and terminal characteristics using numerical simulation software. Her present research areas focus on the development of efficient 2D algorithms and optimization techniques for advanced sub-100nm MOS devices. Consideration has also been given to exploration of new architectures of Silicon on Insulator and Silicon On Nothing MOSFETs for enhanced performance and their applications in various different fields. Recently, she has started with modeling and simulations of HEMTs for high performance microwave circuits. She has authored or co-authored more than 66 papers in various international and national journals and conference proceedings.

Dr. Kaur has been a reviewer for IEEE TRANSACTIONS ON ELECTRON DEVICES and for International Conference -Asia Pacific Microwave Conference (APMC)-2008 held from 16-19, December 2008 in Hong Kong Convention and Exhibition Center, China. Her name has been listed in 2010 edition of Who's Who in the World.

Sandeep Kr Aggarwal was born in Delhi, India, on 1st December, 1976. He received the B.Sc and M.Sc. degrees in Physics and Electronics from Jamia Millia Islamia, Delhi, India, in 1999 and 2001, respectively and his PhD degree in microelectronics

from department of Electronics Science, University of Delhi, India in 2008. He joined the semiconductor device research Laboratory, Department of Electronic Science, Univer-sity of Delhi, south campus in 2001 currently he is working as Assistant Professor in HMR institute of Technology & Management, GGSIP University .His research interest includes modeling and simulation of

SiC/InP MESFET/MOSFET/HEMT /ESD devices for High frequency and high temperature applications. He has published 11 technical papers in international/national journals and conferences.

**Mridula Gupta** (SM'09) received the B.Sc. degree in physics, the M.Sc. degree in electronics, the M.Tech. degree in microwave electronics, and the Ph.D. degree in optoelectronics from the University of Delhi, Delhi,

India, in 1984, 1986, 1988, and 1998, respectively.

Since 1989, she has been with the Department of Electronic Science, University of Delhi South Campus, New Delhi, India, where she was previously a Lecturer and is currently an Associate Professor and with the Semiconductor Devices Research Laboratory. She has authored or coauthored approximately 229 publications in international and national journals and conference proceedings. She has supervised 14 Ph.D. students. She contributed the chapter entitled "MOSFET Modeling" in the *Encyclopedia on RF and Microwave Engineering* (Wiley, 2005). Her current research interests include modeling and simulation of MOSFETs, MESFETs, and HEMTs for microwave-frequency applications.

Dr. Gupta is a Fellow of the Institution of Electronics and Telecommunication Engineers (India) and a Life Member of the Semiconductor Society of India. She was the Secretary of the 2004 Asia–Pacific Microwave Conference, New Delhi, held in December 2004. Dr. Gupta is General Secretary of 12<sup>th</sup> ISMOT 2009 to be held in Dec 2009 in India.

**R. S. Gupta** (SM'81) received the B.Sc. and M.Sc. degrees from Agra University, Agra, India, in 1963 and 1966, respectively, and the Ph.D. degree in electronic engineering from the Institute of Technology,

Banaras Hindu University, Varanasi, India, in 1970.

In 1971, he was with Ramjas College, University of Delhi, Delhi, India. In 1987, he was with the Department of Electronic Science, University of Delhi South Campus, New Delhi, India, as a Reader and later as a Professor from 1997 to 2008, where he is currently an Emeritus Scientist and with the Semiconductor Devices Research

Laboratory. He heads several major research projects sponsored by the Ministry of Defence, the Department of Science and Technology, the Council of Science, and the Industrial Research and University Grants Commission. In 1988, he was a Visitor with the University of Sheffield, Sheffield, U.K., under the ALIS Link exchange program and also visited several U.S. and Spanish universities in 1995 and 1999, respectively. He also visited the Czech Republic in August 2003; Korea in November 2003; Rensselaer Polytechnic Institute, Troy, NY, in August 2004; and China in December 2005. In Dec 19, 2007 he visited Rome, Italy and in 2009 he visited North Texas University and Southeast Missouri State University USA. He has authored or coauthored over 489 papers in various international and national journals and conference proceedings. He contributed the chapter entitled "MOSFET Modeling" in the Encyclopedia on RF and Microwave Engineering (Wiley, 2005). He has supervised 36 Ph.D. students. In addition to that he has also supervised/supervising 11 PhD students. His current interests and activities include modeling of SOI submicrometer MOSFETs and LDD MOSFETs, modeling and design of HEMTs, hot-carrier effects in MOSFETs, and modeling of GaAs MESFETs for high-performance microwave and millimeter-wave circuits and quantumeffect devices.

Prof. Gupta was an Executive Member of the IEEE Electron Devices Society/Microwave Theory and Techniques Society Chapter of the IEEE India Council. Prof Gupta is the Chairman of IEEE EDS Delhi Chapter. His name also appeared in the Golden List of the IEEE TRANSACTIONS ON ELECTRON DEVICES in December 1998, 2002, and 2004. He is a Fellow of the Institution of Electronics and Telecommunication Engineers (India), a Life Member of the Indian Chapter of the International Centre for Theoretical Physics, and a Life Member of the Semiconductor Society of India and chairman of society for microelectronics and VLSI. He was the Secretary of ISRAMT'93 and the 1996 Asia-Pacific Microwave Conference (APMC'96), and the Chairman of the Technical Programme Committee of APMC'96. He edited the proceedings of both of these international conferences. He was the Chairman of APMC'2004 held in New Delhi in December 2004. He has been listed in Who's Who in the World. Prof Gupta is chairman of 12<sup>TH</sup> ISMOT 2009 to be held in Dec 2009 in India.