# 5-Gb/s 연속시간 적응형 등화기 설계 A 5-Gb/s Continuous-Time Adaptive Equalizer

김 태 호\*, 김 상 호\*, 강 진 구\*\*

Tae-Ho Kim\*, Sang-Ho Kim\*, Jin-Ku Kang\*\*

#### Abstract

In this paper, a 5Gb/s receiver with an adaptive equalizer for serial link interfaces is proposed. For effective gain control, a least-mean-square (LMS) algorithm was implemented with two internal signals of slicers instead of output node of an equalizing filter. The scheme does not affect on a bandwidth of the equalizing filter. It also can be implemented without passive filter and it saves chip area and power consumption since two internal signals of slicers have a similar DC magnitude. The proposed adaptive equalizer can compensate up to 25dB and operate in various environments, which are 15m shield-twisted pair (STP) cable for DisplayPort and FR-4 traces for backplane. This work is implemented in 0.18-\mu m 1-poly 4-metal CMOS technology and occupies 200x300\mu^2. Measurement results show only 6mW small power consumption and 2Gbps operating range with fabricated chip. The equalizer is expected to satisfy up to 5Gbps operating range if stable varactor(RF) is supported by foundry process.

### 요 약

본 논문에서는 5Gb/s의 직렬 링크 인터페이스에 적용 가능한 적응형 수신기를 제안한다. 효율적인 이득 제어를 위해 등화필터의 출력단 대신 슬라이서의 내부 신호를 적용한 LMS(Least Mean Square) 알고리즘을 구현하였다. 제안된 방식은 등화기의 대역폭에 영향을 미치지 않는다. 또한 비슷한 DC 크기의 신호를 가지는 슬라이서(slicer)의 내부 신호를 이용하였기 때문에 수동소자를 이용한 필터를 제거함으로써 칩 면적 및 전력소모를 줄일 수 있다. 제안된 적응형 등화기는 25dB까지 보상이 가능하며 디스플레이포트를 위한 15-m STP 케이블과 FR-4 전송선로에 적용 가능하다. 제안된 회로는 0.18 $\mu$ m 1-폴리 4-메탈 CMOS 공정 기술이 적용하여 구현하였으며 200 $\kappa$ 300 $\mu$ m²의 칩 면적을 차지한다. 제작된 칩의 측정 결과 1.8 $\kappa$ 3 공급전원에서 6 $\kappa$ 4의 매우 적은 전력소모를 나타내고 2Gbps 동작을 확인하였다. 안정된 RF용 버랙터(Varactor)를 사용하는 공정을 적용할 경우 5Gbps 동작범위를 만족할 것으로 예상된다.

Key words: Adaptive equalizer, Feed-Forward equalizer, DisplayPort, CDR, LMS algorithm

## I . 서론

\* 인하대학교 전자공학부

(School of Electronics Engineering, Inha University)

- ★ 교신저자 (Corresponding author)

- ※ 감사의 글 (Acknowledgment)

This work was sponsored by ETRI System Semiconductor Industry Promotion Center, Human Resource Development Project for SoC Convergence.

接受日:2010年 3月 8日, 修正完了日: 2010年 3月 24日

반도체 공정 기술과 집적회로 기술의 발달은 XAUI, OC-192 표준과 같은 고속의 데이터 전송 시스템 구현을 가능하게 하지만, 고품질, 대용량의 데이터 전송을 위한 데이터 전송속도에 대한 요구는 꾸준히 높아지고 있다. 전기적인 신호를 전송하기 위한 전송선로의 대역폭은 전송선로의 환경(온도, 습도, 열화) 및 전송선로의 표피효과 및 유전율 손실에 의해 제한되며 이는 고속의 데이터 전송을 어렵게 한다. 이러한 제한된 대역폭을 증가시킬 수 있는 회로적인 구현방법으로 등화기법이 적용된다. 수신기의 전단에 적용된 등화기는 손실 주파수를 보상하고 심볼 간 간섭(Inter-Symbol Interference) 성분을 제거함으로써

수신기의 비트 오율(Bit-Error-Rate)을 감소시킨다. 등화기의 구조로 결정 피드백 등화기 (Decision-Feedback Equalization)와 피드포워드 등화기 (Feed -Forward Equalization) 등화기법이 주로 사용된다. DFE 기법은 수신단의 노이즈를 증폭하지 않는 장점에 비해 성능을 향상시키기 위해 많은 탭을 적용해야하고, 수신 후 제한된 시간 내에 동작해야 하는 단점으로 인해 고속의 회로 구현에 적용하기 어렵다[1]. FFE 기법은 보상하고자 하는 보상 이득만큼 고주과노이즈 성분이 증폭되어 신호 대 잡음비(Signal-to-Noise Ratio)가 낮아지지만, NRZ(Non-Return to Zero)와 같은 큰 전기적인 신호를 전송하는 데 미치는 영향은 적고, 구성이 간단하며 저전력 구현 및 큰보상 이득의 구현이 용이하다[2].

전송선로의 손실량 변화에 대해 보상크기를 최적화하여 보상할 수 있도록 LMS [3]-[6], 전이 시간 검출 (Transition-Time detection) [7], 지터 감소 알고리즘 등 다양한 알고리즘이 병행되어 적용된다[8]-[11]. 그러나 정확한 LMS 알고리즘을 구현하기 위해 수동소자를 이용한 필터의 사용은 회로의 면적을 증가시킨다[3],[4],[6].

본 논문에서는 5Gb/s 대역의 데이터 전송을 위한적응형 등화기의 구조를 제안한다. 제안된 등화기는 커패시턴스 디제너레이션 (Capacitive-degeneration)기법이 적용된 등화 필터를 3단 종속으로 연결하여높은 보상 이득을 구현한다. 전송선로에 최적화된 보상이득을 결정하기 위해 수동소자를 피하고, LMS 알고리즘과 필터의 출력단과 분리함으로써 이득 범위가제한되는 간섭현상을 최소화한 적응형 루프 구조를 제안한다.

## Ⅱ. 회로 설계

## 1. 제안한 수신기의 전체 구조

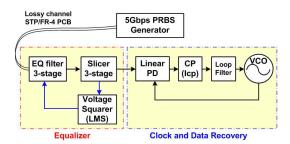

제한된 대역폭 특성을 갖는 전송선로에 의해 왜곡된 데이터 신호로부터 ISI 성분을 제거하고 이를 수신기에서 정확히 복원할 수 있는지 검증하기 위한 제안된 수신기의 전체적인 구조를 그림 1에 나타낸다.

제안된 수신기의 등화기 부분은 대역폭 제한으로 인해 왜곡된 입력 데이터의 손실을 보상해 주는 등화 필터와 등화기의 출력 크기를 일정 직류 레벨로 증폭 하기 위한 슬라이서, 등화기의 보상 크기를 적응형으 로 제어하기 위한 전압 스퀘어로 구성된다. 이후 등 화기를 통과한 신호로부터 데이터 및 클럭의 복원이

Fig. 1. Block diagram of the proposed receiver.

그림 1. 제안된 수신기의 구조

정상적으로 이루어지는지 검증하기 위한 클릭 및 데이터 복원 회로를 추가로 구성하여 성능을 검증한다. 다음의 2절에는 등화기가 적용된 전송선로의 모델링결과와 등화기 및 클릭 및 데이터 복원회로의 구성에대해 3절과 4절에 각각 기술한다.

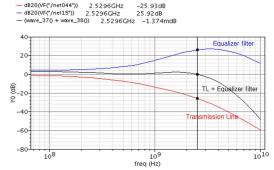

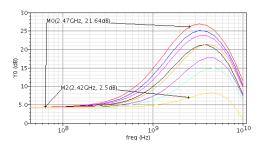

### 2. 전송 선로 모델링

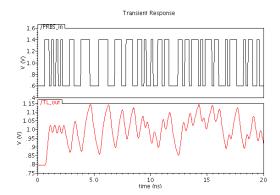

전송선로에 발생되는 표피효과 및 유전율 손실은 동작주파수가 높아질수록 손실의 양도 증가되어 대역폭을 제한한다. 그림 2에 STP 케이블을 이용한 주파수 응답특성 및 등화기 적용후의 AC 응답특성 곡선을 나타내고, 시간에 따른 파형 결과를 그림 3에 나타내었다. 데이터를 전송할 수 있는 대역폭은 3000mb로 현저히 감소되지만 등화기를 적용하여 대역폭을확장시킴으로써 5Gb/s에서 데이터의 왜곡 없이 수신이 가능하게 한다.

AC Response

Fig. 2. AC response of the 15-m STP cable with pi-model

그림 2. pi-model을 이용한 15-m STP 케이블의 AC 특성 곡선

Fig. 3. Transient analysis of the 15-m STP cable 그림 3. STP 케이블의 시간에 따른 파형 분석

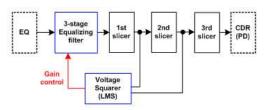

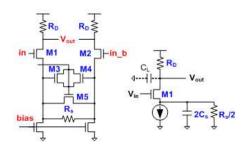

(a) Block diagram of the equalizer

(b) Equalizing filter unit cell & equivalent

(c) Voltage Squarer and Slicer unit cell

Fig. 4. Block diagram of the proposed equalizer structure and unit circuit

그림 4. 제안한 등화기의 구조 및 단위 회로

#### 3. 적응형 등화기

기존의 제안된 구조들은 정확한 보상 이득을 결정하기 위해 직류(DC) 성분과 고주파(High-Frequency) 성분으로 분리하여 적응형 알고리즘에 적용한다. 저역 및 고역 대역 필터를 이용한 기존의 방법은 정확한 보상 이득의 제어를 가능하게 하지만, 수동소자로 구성된 대역필터의 사용은 추가적인 칩의 면적 및 전력 소비를 필요로 한다[3],[4],[6].

제안하는 등화기의 전체적인 구조를 그림 4에 나타 낸다. 커패시티브-디제너레이션 (Capacitive-degenera -tion) 기법이 적용된 고주파 필터를 이용해 감쇠된 고주파 성분의 손실량 만큼 보상하고 등화 필터를 통 과한 데이터의 모서리를 슬라이서를 통해 수직으로 만들어 냄으로서 이상적인 데이터 출력을 만들어 낸 다. 전압 스퀘어러(voltage-Squarer) 회로를 이용해 구현된 LMS 알고리즘은 손실량 변화에 대해 적응하 여 보상 이득이 최적화되도록 제어한다.

제안된 등화 필터는 큰 이득손실을 보상하기 위해 3단 종속 연결 구조로 구성되었고, 등화필터의 단위 블록내의 MOSFET 버랙터(Varactor) M<sub>3</sub>, M<sub>4</sub>와 능동 저항(MOSFET resistor) M<sub>5</sub>에 인가되는 이득 조절 값에 의해 영점과 극점을 동시에 제어함으로써 저주파 및 고주파의 이득 크기가 최적화되어 보상된다.

LMS 알고리즘을 통해 연속적인 값으로 되먹임 (feedback) 되는 보상 제어 신호는 등화필터의 영점과 극점을 제어함으로써 이득 보상의 크기를 가변시킬수 있으나 출력 노드의 기생 커패시턴스(2nd pole) 성분에 의해 전체적인 동작 대역폭은 제한된다. 적응형으로 동작하기 위해 LMS 알고리즘을 등화 필터의 출력단에 연결할 경우 등화 필터내 출력노드의 커패시턴스 성분이 증가되어 등화기의 대역폭을 더욱 제한된다. 등화필터의 전달함수와 영점, 극점은 다음의식 (1), (2) 에 나타낸다.

$$H_{EF(S)} = \frac{g_m R_D (1 + s \, C_s R_s)}{(1 + s \, C_L R_D) (1 + g_m R_s + s \, C_s R_s)} \tag{1}$$

$$DC \ gain = \frac{g_m R_L}{1 + g_m R_d}$$

$$zero = -\frac{1}{C_d R_d}$$

$$pole_1 = -\frac{1 + g_m R_d}{C_d R_L}$$

$$pole_2 = -\frac{1}{C_L R_L}$$

$$(2)$$

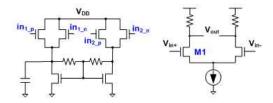

Fig. 5. AC response curves of the equalizer filter gain compensation with varying control signal 그림 5. 제어신호 변화에 따른 등화필터의 이득 변화

그림 5에 보상 제어신호의 크기에 따른 등화 필터 의 보상 이득 곡선을 나타낸다.

LMS 알고리즘을 등화 필터의 특성으로부터 독립적으로 적용하기 위해 LMS 알고리즘 (voltage Squarer)에 필요한 두 입력 데이터를 3단 종속 연결된 슬라이서의 첫 번째 슬라이서의 출력 노드에서 취함으로써 등화필터의 출력노드 커패시턴스를 최소화하였다. 또한 동일한 CML 형태로 구성된 슬라이서를 통과한 두 신호의 DC level은 동일하기 때문에 별도의 수동소자를 이용한 필터 없이 두 데이터의 직접적인 비교를 가능하게 한다. 식 (3), (4)에 의해 보상 이득의 제어신호의 크기는 제어된다[12].

$$\begin{split} I_{D1} &= \mu_p C_{ox} \frac{W}{L} (V_{in1p} - V_s - V_{thp})^2 \\ I_{D2} &= \mu_p C_{ox} \frac{W}{L} (V_{in1n} - V_s - V_{thp})^2 \\ I_{D3} &= \mu_p C_{ox} \frac{W}{L} (V_{in2p} - V_s - V_{thp})^2 \\ I_{D4} &= \mu_p C_{ox} \frac{W}{L} (V_{in2n} - V_s - V_{thp})^2 \end{split}$$

$$\begin{split} I_{out} &= (I_{D1} + I_{D2}) - (I_{D3} + I_{D4}) \\ &= 2 \big\{ (V_{in1p} - V_{in1n})^2 - (V_{in2p} - V_{in2n})^2 \big\} \end{split} \tag{4}$$

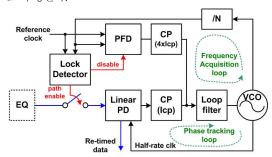

## 4. 클록 및 데이터 복원 회로

등화된 데이터로부터 클릭 및 데이터 정보가 정확하게 추출되는지 검증하기 위한 이중 루프의 클릭 및 데이터 복원 회로(Dual loop Clock and Data Recovery)를 그림 6에 나타낸다.

동작 주파수에 대한 전압제어 발진기의 제어전압을 설정하기 위한 주파수 획득 루프와 입력된 데이터로 부터 클록의 위상을 고정시키기 위한 위상 추적 루프로 구성된다.

Fig. 6. The block diagram of the dual loop CDR 그림 6. 이중 루프 클록 및 데이터 복원회로의 구성도

입력 데이터로부터 위상 검출기가 정상적으로 위상 추적이 가능하도록 전압 제어 발진기의 동작 주파수범위를 설정하기 위해 외부 기준 클록을 이용한 위상고정 루프 회로(Phase-Locked Loop)를 이용하여 공통으로 적용된 루프 필터에 초기 동작 주파수의 전압값을 설정한다.

외부 클록과 내부의 전압 제어 발진기로부터 분주된 주파수가 동일해 지면 주파수 고정 검출기 (Frequency Lock Detector)를 통해 주파수 획득 (Frequency-Acquisition) 루프로부터 위상 추적 (Phase-Tracking mode) 루프로 전환된다.

위상 추적 루프로 전환되면서 등화된 출력테이터도 위상 검출기의 입력으로 동시에 인가된다. 지터 특성이 우수한 하프-레이트 선형 위상 검출기(Half-Rate linear Phase Detector)를 적용하였고, 4단의 차동 지연 셀로 구성된 전압제어 발진기로부터 필요한 클록을 발생시킨다. 고속의 동작을 위해 내부의 모든 로직들은 전류모드 로직(Current Mode Logic) 형태로구현되었다.

## Ⅲ 모의실험 및 측정 결과

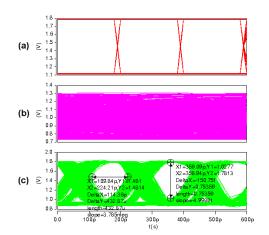

등화기 모의실험을 위해 15-m STP 케이블 (pi-model) 및 FR-4 트레이스(w-element model)를 모델링하여 적용하였다. 레이아웃 진행 후 기생성분을 추출한 정보를 적용한 포스트 모의실험(Post simulation)에 대한 결과를 그림 7에 나타내었다. 전송선로에 의해 데이터의 눈(Eye)은 완전히 닫힌 왜곡된 값이 인가되었지만, 등화기를 통해 출력된 눈(Eye)은 0.78UI로 CDR이 안정적으로 데이터 및 클록을 복원할 수 있는 수준의 값을 유지할 수 있었다.

Fig. 7. Eye-diagrams of PRBS data through STP cable @5Gb/s after LPE (Layout Parasitic Extraction) process

(a) PRBS input (b) ISI data (c) equalized data 그림 7. STP 케이블을 통과한 5-Gb/s PRBS 데이터 및 등화필터를 통과한 데이터의 아이 다이어그램 (a) PRBS 입력 (b) ISI 데이터 (c) 등화된 데이터

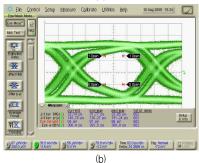

Fig. 8. measurement eye-diagram of the equalizer

(a) ISI input data through lossy channel(40-in FR-4)

(b) Output data of the equalizer

그림 8. 측정된 등화기의 아이 다이어그램

(a) 전송선로을 통과한 ISI 입력데이터(40-in FR-4)

(b) 등화기의 출력 데이터

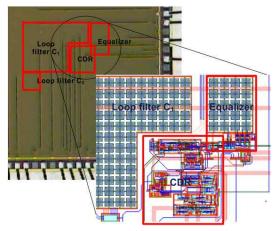

Fig. 9. Chip photo and Layout of the proposed Receiver 그림 9. 제안한 수신기의 칩 사진 및 레이아웃

제작된 칩의 측정 결과를 그림 8에 보였다. 측정파형은 패턴 생성기로부터 출력된 2Gbps의 데이터를 FR-4 트레이스를 통과시킨 후(a)와 등화 필터를 통과한 출력의 아이-다이어그램(b)을 나타낸다. FR-4 40인치 모델과 15-m STP 케이블의 주과수 손실 특성이 유사하기 때문에 용이한 측정 환경을 위하여 FR-4 트레이스를 적용하였다.

2Gbps까지 비트 수신 오류 없이 측정이 되었으나, 데이터 입력 레이트를 증가할수록 수신 오율이 증가 하여 실제 칩 제작 후 측정시 설계목표인 5Gbps 대 역에서 미치지 못하고 최대 2Gbps에서 동작을 확인 하였다.

설계 목표치인 모의실험 결과보다 측정결과가 낮은 원인으로 등화기에 적용된 커패시턴스 소자 모델링 의 오류로 추정된다. 버랙터(RF용 소자)는 인가되는 모든 제어 전압 범위에 선형적으로 비례하는 커패시 턴스값을 가지지만 MOSFET의 커패시턴스 특성은 인가 전압에 대해 감소하다가 급증하는 비선형적인 특성을 가진다. 제어 전압이 원하는 선형구간에 위치 하지 못할 경우 원하는 커패시턴스값을 유지하지 못 한 채 제어범위를 벗나게 될 경우 원하는 보상의 제 어가 이루어지지 않는다. CMOS 로직 공정을 이용하 여 커패시턴스 값을 조절해야 할 경우 커패시턴스를 스위치로 ON/OFF 제어할 수 있는 구조로 적용한다 면 이러한 문제점을 해결할 수 있다. RF용 소자인 버 랙터를 사용할 경우 모든 제어전압에 대해 선형적인 커패시턴스 값을 가질 수 있어 5Gbps 고주파대역에 서 안정적으로 동작할 것으로 예상된다.

전체 수신기의 칩 사진을 그림 9에 나타내고, 실험

한 결과를 이용한 칩의 성능 비교 결과를 표 1에 정리하였다. 칩의 성능 비교를 위해 FR-4 전송선로를 Hspice의 w-element 모델을 이용하여 모델링 후 적용하였다.

Table 1. Performance comparison 표 1.성능 비교표

| Papers       | [3]     | [4]               | This work         |

|--------------|---------|-------------------|-------------------|

| Technology   | 0.18μm  | $0.13 \mu { m m}$ | 0.18μm 로직         |

| Operating    | 2 ECb/a | 10Gb/s            | 5Gb/s(simulation) |

| range        | 3.5Gb/s | 10Gb/S            | 2Gb/s(chip 측정)    |

| Transmission | RG-58   | FR-4              | FR-4 60inch       |

| line         | 15m     | 30inch            | FR-4 OUIICII      |

| Power        | 80mW    | 25mW              | 6mW               |

| dissipation  | @1.8V   | @1.2V             | @1.8V             |

| active       | 480×730 | 450×360           | 200×300           |

| area(µm)     | 400^730 | 400^300           | 200^300           |

## 1 / 결론

본 논문에서는 0.18 $\mu$ m CMOS 로직 공정을 이용한 소면적, 저전력의 적응형 등화기를 설계하였다. 적용형 알고리즘을 적용하기 위해 등화필터의 출력단으로부터 분리된 슬라이서의 내부 신호를 이용한 간단한 LMS 알고리즘 구조를 적용함으로서 등화필터의 성능을 저하시키지 않는다. 또한 유사한 DC 값을 갖는슬라이서의 내부 신호들을 사용하기 때문에 별도의대역필터 없이 LMS 알고리즘의 적용이 가능하여 200×300 $\mu$ m<sup>2</sup>의 적은 면적, 6 $\mu$ 에의 매우 낮은 전력으로최대 25dB의 이득 보상이 가능하였다. 등화 필터의단수를 증가시킬 경우 더 높은 이득을 얻을 수 있다. 측정결과 최대 2Gbps동작을 확인하였으나 시뮬레이션 값에는 미치지 못하였다. 안정된 RF용 버랙터(Varactor)를 사용할 경우 5Gbps 동작속도를 만족하는 저전력 등화기의 구현이 가능할 것으로 예측한다.

## 참고문헌

[1] Y. S. Sohn, S. J. Bae, H. J. Park, S. I. Cho, "A Decision Feedback Equalization Receiver for the STL SDRAM Interface with Clock-Date Skew compensation," *IEICE Trans*, vol.E87, May 2004.

[2] S. Gondi, Equalization and Clock and Data Recovery Techniques for Serial-Link Receivers, Ph.D. dissertation, UCLA, LA, CA, 2006.

- [3] J. S. Choi, M. S. Hwang, D. K. Jeong, "A 0.18-μm CMOS 3.5-Gb/s Continuous-Time Adaptive Cable Equalizer Using Enhanced Low-Frequency Gain Control Method," *IEEE JSSC*, vol.39, pp. 419-425. March 2004.

- [4] S. Gondi, J. Lee, K. Takeuchi, B. Razavi, "A 10Gb/s CMOS Adaptive Equalizer for Backplane Applications," *IEEE ISSCC Dig. Of Tech. Papers*, vol.1, pp.328–601, February 2005.

- [5] J. Lee, "A 20-Gb/s Adaptive Equalizer in 0.13-μm CMOS Technology," *IEEE ISSCC Dig. Of Tech. Papers*, pp.273-282, February 2006.

- [6] S. Gondi, B. Razavi, "Equalization and Clock and Data Recovery Techniques for 10-Gb/s CMOS Serial-Link Receivers," *IEEE JSSC*, vol.42, pp.1999-2011, September 2007.

- [7] G, Zhang, P. Chaudhari, M. M. Green, "A BiCMOS 10Gb/s Adaptive Cable Equalizer," *IEEE ISSCC Dig. Of Tech. Papers*, vol.1, pp.482–541, February 2004.

- [8] J. Buckwalter and A. Hajimiri, "A 10Gb/s Data-Dependent Jitter Equalizer," *IEEE Custom Integrated Circuits Conference*, pp.39–42, October 2004.

- [9] K. Yamaguchi, et al., "12Gb/s Duobinary Signaling with x2 Oversampled Edge Equalization," *IEEE ISSCC Dig. Of Tech. Papers*, vol.1, pp.70–585, February 2005.

- [10] R. Payne, et al., "A 6.25–Gb/s Binary Transceiver in 0.13– $\mu$ m CMOS for Serial Data Transmission Across High Loss Legacy Backplane Channels," *IEEE JSSC*, vol.40, pp.2646–2657, December 2005.

- [11] A. C. Carusone, "Jitter Equalization for Binary Baseband Communication," *IEEE International Symposium on Circuits and Systems*, vol.2, pp.936–939, May 2005.

- [12] G. Giustolisi, G. Palmisano, G. Palumbo, "A novel CMOS voltage Squarer," *IEEE International Symposium on Circuits and Systems*, pp.253–256, June 1997.

## 저 자 소 개

#### **김 태 호** (학생회원)

2007년 : 인하대학교 전자공학과

졸업 (공학사)

2009년 : 인하대학교 일반대학원

전자공학과 (공학석사)

2009년 3월~현재 : 인하대학교

전자공학과 박사과정 <주관심분야> High Speed

CMOS Interface IC

#### 김 상 호 (학생회원)

2007년 : 인하대학교 전자공학과 졸업 (공학사) 2008년 9월 ~ 인하대학교 일반대 학원 전자공학과 석사과정 <주관심분야> PLL

## **강 진 구** (정회원)

1983년 : 서울대학교 (공학사) 1990년 : New Jersey Institute

of Technology 전기 및 컴퓨터공

학 (공학석사)

1996년 : North Carolina State University 전기 및 컴퓨터공학

(공학박사)

\_\_\_\_\_\_ 1983년 ~ 1988년 : 삼성전자(반도체)

1996년 ~ 1997년 : 미국 INTEL Senior Design

Engineer

1997년 3월~현재: 인하대학교 전자공학부 교수 <주관심분야> 고속 CMOS 회로 설계, Mixed IC 설계, PLL/DLL/CDR, High Speed Interface IC,

Display IC