# Channel Protection Layer Effect on the Performance of Oxide TFTs

Sang-Hee Ko Park, Doo-Hee Cho, Chi-Sun Hwang, Shinhyuk Yang, Min Ki Ryu, Chun-Won Byun, Sung Min Yoon, Woo-Seok Cheong, Kyoung Ik Cho, and Jae-Hong Jeon

We have investigated the channel protection layer (PL) effect on the performance of an oxide thin film transistor (TFT) with a staggered top gate ZnO TFT and Al-doped zinc tin oxide (AZTO) TFT. Deposition of an ultra-thin PL on oxide semiconductor films enables TFTs to behave well by protecting the channel from a photo-resist (PR) stripper which removes the depleted surface of the active layer and increases the carrier amount in the channel. In addition, adopting a PL prevents channel contamination from the organic PR and results in high mobility and small subthreshold swings. The PL process plays a critical role in the performance of oxide TFTs. When a plasma process is introduced on the surface of an active layer during the PL process, and as the plasma power is increased, the TFT characteristics degrade, resulting in lower mobility and higher threshold voltage. Therefore, it is very important to form an interface using a minimized plasma process.

Keywords: ZnO TFT, AZTO TFT, channel protection layer, ALD, bias stability.

#### I. Introduction

Since the release of reports on a transparent amorphous InGaZnO thin film transistor (TFT) by Hosono and others [1] and a polycrystalline ZnO TFT by Wager and others [2], oxide semiconductors have attracted an astonishing amount of attention [3]. These are currently the subject of intensive material research, as they have diverse applications in displays, memory devices, and other electronics, such as ring oscillators [4]-[6]. The main concern in the area of displays is the application of oxide TFTs to the backplane of active matrix organic light emitting diodes (AMOLEDs) [7], TFT-LCDs [8], and electronic paper (e-paper) [9]. Oxide TFTs, which can be fabricated uniformly on a large substrate, have both high mobility and good stability. Therefore, we believe that oxide TFTs are the best candidate, especially for OLED driving devices.

Most oxide TFTs are comprised of sputtered zinc oxide [10], indium gallium zinc oxide (IGZO) [11], zinc tin oxide (ZTO)-based oxide [12], [13], or indium zinc oxide (IZO) [14], and several ZnO TFTs fabricated by atomic layer deposition have also been reported [15], [16]. Some of them have shown promising performance for application in an AM-OLED in terms of mobility. However, most of the research has focused on the composition of an oxide semiconductor, process parameters, thermal annealing conditions, semiconductor deposition methods, and electrical analyses, such as bias stability. Very few experimental works have been reported on the process effects on device performance [17].

It has been well established that the gate insulator/semiconductor interface has played the most important role in TFT performance [18], [19]. In this study, we report on how the gate insulator/semiconductor interface

Manuscript received May 17, 2009; revised Oct. 8, 2009; accepted Oct. 19, 2009.

This work was supported by the IT R&D program of MKE, Rep. of Korea [2006-S079-04, Smart window with transparent electronic devices].

Sang-Hee Ko Park (phone: +82 42 860 6276, email: shkp@etri.re.kr), Doo-Hee Cho (email: chodh@etri.re.kr), Chir-Sun Hwang (email: hwang-cs@etri.re.kr), Shinhyuk Yang (email: ysh@etri.re.kr), Min Ki Ryu (email: ryumk@etri.re.kr), Chun-Won Byun (email: cwbyun@etri.re.kr), Sung Min Yoon (email: sungmin@etri.re.kr), Woo-Seok Cheong (email: cws@etri.re.kr), and Kyoung Ik Cho (email: kicho@etri.re.kr) are with Convergence Components & Materials Research Laboratory, ETRI, Daejeon, Rep. of Korea.

Jae-Hong Jeon (email: jjh123@kau.ac.kr) is with the School of Electronics, Telecommunications, and Computer Engineering, Korea Aerospace University, Goyang, Gyeonggido, Rep. of Korea.

doi:10.4218/etrij.09.1209.0043

formation process affects oxide TFT performance in a staggered top gate structure with the adoption of an ultra-thin channel protection layer (PL). In addition, we investigate the effects of the PL process on the ZnO TFT characteristics.

## II. Experiment

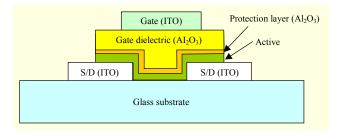

A transparent ZnO TFT and an Al-doped ZnSnO (AZTO) TFT were fabricated on a glass substrate by means of plasmaenhanced atomic layer deposition (PEALD) and sputtering, respectively, with the structure shown in Fig. 1. For the fabrication of ZnO TFT, 150 nm thick Sn-doped indium oxide (ITO) was deposited on the glass as source/drain (S/D) electrodes by sputtering and was then patterned using a wet etching process. ZnO film was deposited via PEALD [20] at a substrate temperature of 150°C using diethylzinc (DEZ) and in situ generated oxygen plasma as a Zn and oxygen precursor at an RF power of 60 W. The reactor pressure was kept at 3 Torr. In the PEALD method, the precursors were alternatively injected into the reactor using Ar as a carrier gas with a flow rate of 80 sccm. The pulsing times were 2.5 s for the DEZ, 1.5 s for oxygen plasma, and 4 s for Ar purge. A radio frequency pulse was applied at 60 W during the injection of O<sub>2</sub> gas for 1.5 s to generate oxygen plasma in situ. After 20 nm thick ZnO film deposition, 9 nm thick alumina, as a ZnO PL that also acts as a first gate insulator, was deposited at 150°C using PEALD at RF powers of 60 W, 100 W, or 130 W [21]. For PL growth, trimethylaluminum (TMA), and oxygen plasma were used as Al and O precursors, respectively. The active layer of ZnO and alumina (PL) was patterned via wet etching using a diluted HF solution. For comparison, another ZnO film was directly patterned without a PL, followed by deposition of a gate insulator, alumina. The gate insulator, a second alumina, was deposited with a thickness of 176 nm at a temperature of 150°C by means of ALD using TMA and water, followed by S/D pad opening by wet etching of the alumina using concentrated H<sub>3</sub>PO<sub>4</sub>. A sputtered ITO was used as a gate electrode. For the fabrication of an AZTO TFT, a 20 nm thick AZTO layer was formed by the co-sputtering of an Al<sub>2</sub>O<sub>3</sub>-ZnO (ZnO:Al) target and an SnO<sub>2</sub> target using an off-axis type RF magnetron sputter at room temperature [22]. The sputtering was performed in a mixed atmosphere of Ar and O<sub>2</sub> with a chamber pressure of 0.2 Pa. We deposited alumina as a PL using TMA and water as Al and O precursors, respectively, via ALD at 200°C [23]. AZTO and Al<sub>2</sub>O<sub>3</sub> films were also patterned, and the following processes were each the same as those of the ZnO TFT. Here again, we fabricated a comparison device that does not adopt a PL, and a gate insulator, alumina, was directly deposited onto a patterned AZTO film. After fabrication of the TFTs, we carried out post annealing at 200°C

Fig. 1. Cross-sectional view of a top gate oxide TFT with an oxide semiconductor protection layer.

for 2 hours for the ZnO TFT and at 300°C for 2 hours for the AZTO TFT.

Measurement of the characteristics of the TFT was conducted using an HP 4156 semiconductor parameter analyzer. A dielectric constant of 7.4 was obtained for alumina grown by ALD at 150°C by measuring the capacitance of a capacitor made using ITO as electrodes. The mobility ( $\mu$ ) and threshold voltage ( $V_{th}$ ) of the TFT were calculated using the saturation current equation of a field-effect transistor. The  $V_{th}$  was extracted according to the square root  $I_d$  vs. gate voltage ( $V_g$ ) plot.

### III. Results and Discussion

Polycrystalline ZnO, especially deposited using ALD or PEALD, is easily attacked even by a weak base such as a photoresist (PR) stripper. Therefore, lithography process damage causes serious performance degradation of a ZnO TFT with a thin active layer. This led us to use an ultra-thin PL for ZnO, which covers the ZnO simply for protection during the patterning process. We had to be very careful in the selection of ZnO PL, which practically acts as a first gate insulator, as most gate insulators such as SiN<sub>x</sub>, or SiO<sub>2</sub> deposited on an active layer using the plasma enhanced chemical vapor deposition (PECVD) method can make ZnO film conductive due to the H incorporation [24]. A shallow donor level generated by hydrogen can be formed in ZnO during the gate dielectric process to increase the carrier amounts in the active layer. Instead of gate insulators by PECVD, we adopted an alumina grown using PEALD at 150°C with an RF power of 60 W. The thickness of the PL, alumina, was optimized to 9 nm so that the ZnO could be protected from the PR and PR stripper.

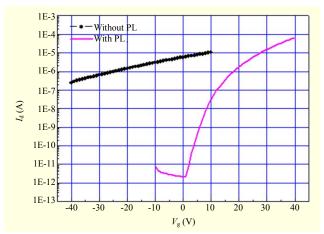

Figure 2 shows the characteristics of ZnO TFTs with and without a PL. We could not even determine the  $V_{\rm on}[25]$  of the ZnO TFT without PL because the drain current as a function of the gate voltage is almost linear within the general gate voltage range. We attributed this to the high carrier amount in the active layer and lots of charge trap site in the interface. On the contrary, adopting a PL of only 9 nm changed the TFT performance dramatically. It behaved in enhanced mode with a mobility of  $2.4 \, \mathrm{cm}^2/\mathrm{V} \cdot \mathrm{s}$  and a  $V_{\rm th}$  of  $22.7 \, \mathrm{V}$ .

Fig. 2.  $I_{ds}$ – $V_{gs}$  transfer curves of ZnO TFTs with and without an alumina PL at  $V_{ds}$ =15.5 V (W=40  $\mu$ m, L=20  $\mu$ m).

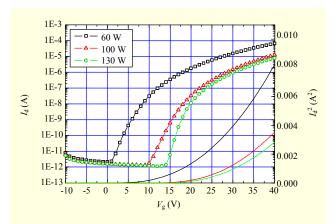

Fig. 3.  $I_{\rm ds}$ – $V_{\rm gs}$  transfer curves of ZnO TFTs with a PL deposited at various plasma powers of 60 W, 100 W, and 130 W ( $V_{\rm ds}$ =15.5 V, W=40  $\mu$ m, L=20  $\mu$ m).

When the ZnO film is exposed to a wet process, two possibilities should be considered. One is the exposure to water. It is known that water can be chemically adsorbed into an oxide film to generate an extra electron on the surface [26]. In the case of polycrystalline ZnO, water can penetrate into the active layer to generate electrons not only at the surface but also in the bulk film. Therefore, we have to apply a much higher negative voltage to deplete the whole channel as shown in Fig. 2. The other possibility to be considered is the PR stripper effect. A ZnO surface can also be exposed to oxygen in air, and adsorbed oxygen can form peroxide (O<sup>2</sup>-) or O<sup>-</sup> that depletes the back channel [27]. However, a PR stripper, the base, gets rid of the surface of the depleted ZnO film, again increasing electrons in a channel and making ZnO too conductive. The increased carrier from both effects and defects generated in both the channel and bulk film degrade the TFT behavior as shown in Fig. 2.

To investigate the effects of the PL process, we changed the plasma power during alumina deposition from 60 W to 130 W.

Figure 3 shows the transfer curves of TFTs that have ZnO film deposited with an RF power of 60 W and a PL deposited with RF powers of 60 W, 100 W, or 130 W. The mobility of the ZnO TFT with a PL deposited at 60 W, 100 W, and 130 W of plasma power are 0.94 cm<sup>2</sup>/V·s, 0.63 cm<sup>2</sup>/V·s, and 0.64 cm<sup>2</sup>/V·s, respectively. Since the mobility of a ZnO TFT is quite dependent on the applied electrical field [28], we calculated the mobility at a position of 25 V higher at the turn-on voltage ( $V_{on}$ ) to compare the device performance fairly.

While the subthreshold swings (SSs) of devices with a PL deposited at 60 W, 100 W, and 130 W are 1.7, 1.8, and 1.2 V/decade, the threshold voltages are 22.7 V, 26.4 V, and 26.9 V, respectively. Increased plasma power during alumina growth resulted in increased hysteresis as well. It seems that a high plasma power for the growth of a PL (the first gate insulator) induces charge trap sites in the interface to cause the hysteresis of TFTs and shift of  $V_{\rm th}$  to the higher voltage. Although the SSs are decreased due to the effect of reducing oxygen vacancy in the ZnO film with the help of oxygen plasma as the RF power for the PL process increases, most of the device performance is degraded with the increased RF power. This suggests that a minimization of plasma damage during the gate insulator process will be important for improving device performance.

To investigate the PL effect on other oxide semiconductors, particularly those that are relatively inert to a PR stripper, we fabricated top gate AZTO TFTs with and without a PL. In the case of the AZTO TFT, we adopted an alumina PL deposited with a water precursor instead of oxygen plasma since we discovered that the plasma process for the interface induces severe damage to the device [7]. When alumina is deposited with water, only a surface chemical reaction occurs between the chemisorbed TMA and water, and other side effects caused by plasma are not a concern.

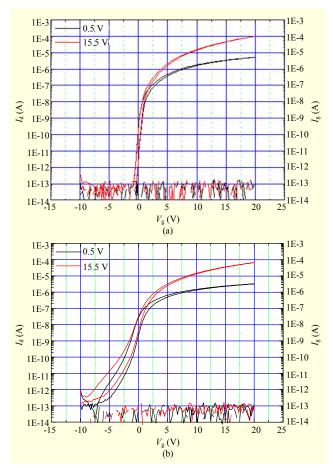

Figure 4 shows the transfer characteristics of AZTO TFTs. Contrary to the ZnO TFT which has a semiconductor film that is very sensitive to the water and base solution of PR stripper, the semiconductor film of the AZTO TFT is relatively inert to these chemicals and shows typical TFT performance without a PL. It has a mobility of 4.8 cm<sup>2</sup>/V·s,  $V_{th}$  of 0.98 V, and SS of 1.0 V/decade, while those of a TFT with a PL are  $10.9 \text{ cm}^2/\text{V} \cdot \text{s}$ , 4.05 V, and 0.26 V/decade. One notable thing is the hysteresis of an AZTO TFT without a PL compared to that with a PL. A large hysteresis may originate from the organic residue of PR in the interface. To get rid of this kind of residue completely, we can use oxygen plasma. This, however, induces more severe plasma damage to the interface, resulting in a larger hysteresis than in an AZTO TFT without a PL (the transfer curve is not shown here). The lower mobility and higher SS of an AZTO without a PL also indicate that there is serious

Fig. 4.  $I_{ds}$ – $V_{gs}$  transfer curves of AZTO TFTs (a) with and (b) without a PL (W=40  $\mu$ m, L=20  $\mu$ m).

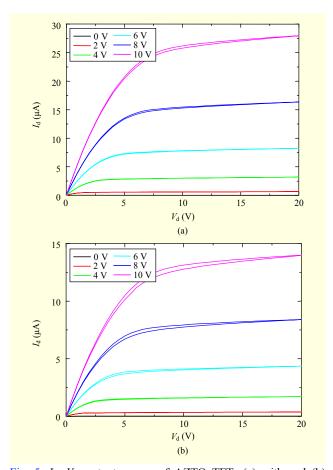

interface degradation during the active patterning process. When we fabricated the AZTO TFT, the sputtered AZTO film was exposed to air in order to deposit a PL in a PEALD chamber. This means that the main role of a PL in an oxide TFT is not to protect the oxide layer from water in air, but to protect the channel from damage during the photolithography process. The AZTO TFT without a PL also shows a smaller  $V_{\rm th}$  than that with a PL as in the ZnO TFT. This supports the behavior of a PR stripper, which removes the depleted surface even though the active layer is not dissolved by the stripper well. Figures 5(a) and (b) show the drain current-drain voltage  $(I_{\rm D}\text{--}V_{\rm D})$  output curves of AZTO TFTs with and without a PL, respectively. They show typical TFT characteristics, although the AZTO TFT without a PL shows a lower  $I_{\rm D}$  than the other AZTO TFT with a PL.

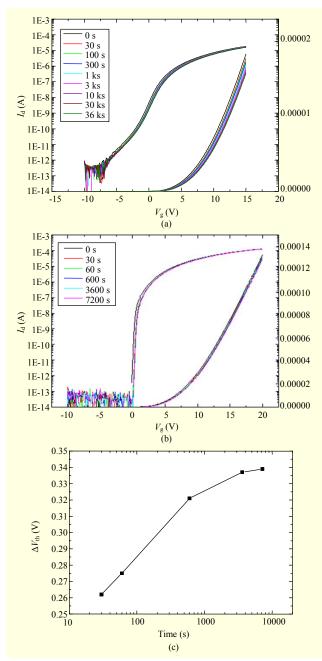

We investigated the bias stability of the AZTO TFT without and with a PL as shown in Fig. 6. When we applied a  $V_{\rm gs}$  of 20 V during 7,200 s, the  $V_{\rm th}$  of the AZTO TFT with a PL shifted only 0.33 V. Most of the  $V_{\rm th}$  shift occurred within the first 1,000 s, and it became saturated after 1,000 s at 0.33 V. Meanwhile, under a negative bias stress of -20 V, the  $V_{\rm th}$  shift

Fig. 5.  $I_{ds}$ – $V_{ds}$  output curves of AZTO TFTs (a) with and (b) without a PL (W=40  $\mu$ m, L=20  $\mu$ m).

was almost negligible (the data is not shown here). Although the SS is not good, even the AZTO TFT without a PL shows relatively stable behavior under gate bias stress. This is mostly due to the high chemical stability of the AZTO film and plasma free interface formation with the bulk alumina gate insulator grown using water precursor. The AZTO TFT with a PL is pretty stable with a good transfer curve under bias stress. This means that channel protection using a PL is very important, and, in particular, a plasma damage free process for the PL is necessary to obtain a highly stable oxide TFT.

## IV. Conclusion

We investigated the channel protection layer effect on the performance of oxide TFTs using a top gate ZnO TFT and AZTO TFT. Deposition of an ultra-thin PL on the oxide films enables TFTs to behave well by protecting the channel from the PR stripper, which removes the depleted surface of the active layer. In addition, adopting a PL prevents channel contamination from an organic PR and results in high mobility and a small SS. The PL process plays a critical role in the

Fig. 6. Change of transfer curve of AZTO TFT (a) without PL, (b) with PL, and (c)  $\Delta V_{\rm th}$  under a positive bias stress of 20 V for up to 7200 s.

performance of oxide TFTs. When plasma damage is induced on the surface of an active layer during the PL process, the TFT characteristics are degraded, resulting in lower mobility, and higher threshold voltage. Therefore, it is very important to form an interface without plasma damage during the PL process.

## References

[1] K. Nomura et al., "Room-Temperature Fabrication of Transparent

- Flexible Thin-Film Transistors Using Amorphous Oxide Semiconductors," *Nature*, vol. 432, no. 7016, 2004, pp. 488-492.

- [2] J. Wager, "Transparent Electronics," *Science*, vol. 300, no. 5623, 2003, pp. 1245-1246.

- [3] E.M.C. Fortunato et al., "Fully Transparent ZnO Thin Film Transistor Produced at Room Temperature," *Adv. Mater.*, vol. 17, no. 5, 2005, pp. 590-594.

- [4] H.N. Lee et al., "3.5 Inch QCIF+ AM-OLED Panel Based on Oxide TFT Backplane," *Tech. Dig. SID07*, California, USA, 2007, pp. 1826-1829.

- [5] H. Ohta and H. Hosono, "Transparent Oxide Optoelectronics," *Material Today*, vol. 7, no. 6, 2004, pp. 42-51.

- [6] I. Song et al., "Short Channel Characteristics of Gallium—Indium—Zinc—Oxide Thin Film Transistors for Three-Dimensional Stacking Memory," *IEEE Electron Device Letters*, vol. 29, no. 6, 2008, pp. 549-552.

- [7] S.-H. K. Park et al., "Transparent and Photo-Stable ZnO Thin-Film Transistors to Drive an Active Matrix Organic-Light-Emitting-Diode Display Panel," Adv. Mater., vol. 21, no. 6, 2009, pp. 678-682.

- [8] J. Lee et al., "World's Largest (15-inch) XGA AMLCD Panel Using IGZO Oxide TFT," *Tech. Dig. SID08*, California, USA, 2008, pp. 625-628.

- [9] M. Ito et al., "Amorphous Oxide TFT and Their Applications in Electrophoretic Displays," *Physica Status Solidi (a)*, vol. 205, no. 8, 2008, pp. 1885-1894.

- [10] R.B.M. Cross and M.M. De Souza, "Investigating the Stability of Zinc Oxide Thin Film Transistors," *Appl. Phys. Lett.*, vol. 89, no. 26, 2006, pp. 263513-263515.

- [11] J.K. Jeong et al., "High Performance Thin Film Transistors with Cosputtered Amorphous Indium Gallium Zinc Oxide Channel," *Appl. Phys. Lett.*, vol. 91, no. 11, 2007, pp. 113505-113507.

- [12] E.M.C. Fortunato et al., "High Mobility Indium Free Amorphous Oxide Thin Film Transistors," *Appl. Phys. Lett.*, vol. 92, no. 22, 2008, pp. 222103-222105.

- [13] J.K. Jeong et al., "Impact of Device Configuration on the Temperature Instability of Al-Zn-Sn-O Thin Film Transistor," *Appl. Phys. Lett.*, vol. 95, no. 12, 2009, pp. 123505-123507.

- [14] N.L. Dehuff et al., "Transparent Thin-Film Transistors with Zinc Indium Oxide Channel Layer," J. Appl. Phys., vol. 97, no. 6, 2005, pp. 64505-64508

- [15] S.-H. K. Park et al., "Transparent ZnO-TFT Arrays Fabricated by Atomic Layer Deposition," *Electrochemical and Solid-State Letters*, vol. 11, no. 1, 2008, pp. H10-H14.

- [16] J.H. Shin et al., "Light Effects on the Bias Stability of Transparent ZnO Thin Film Transistors," *ETRI Journal*, vol. 31, no. 1, 2009, pp. 62-64.

- [17] C.J. Kim et al., "Characteristics and Cleaning of Dry-Etching-Damaged Layer of Amorphous Oxide Thin-Film Transistor," *Electrochemical and Solid-State Letters*, vol. 12, no. 4, 2009, pp.

H95-H97.

- [18] I. Yagi, K. Tsukagoshia, and Y. Aoyagi, "Modification of the Electric Conduction at the Pentacene/SiO<sub>2</sub> Interface by Surface Termination of SiO<sub>2</sub>," *Appl. Phys. Lett.*, vol. 86, no. 10, 2005, pp. 103502-103504.

- [19] A.R. Hepburn et al., "Metastable Defects in Amorphous-Silicon Thin Film Transistors," *Physical Review Letters*, vol. 56, no. 20, 1986, pp. 2215-2217.

- [20] S.-H. K. Park et al., "Characteristics of ZnO Thin Films by Means of Plasma-Enhanced Atomic Layer Deposition," *Electrochemical* and Solid-State Letters, vol. 9, no. 10, 2006, pp. G299-G301.

- [21] J.W. Lim and S.J. Yun, "Electrical Properties of Alumina Films by Plasma-Enhanced Atomic Layer Deposition," *Electrochemical and Solid-State Letters*, vol. 7, no. 8, 2004, pp. F 45-F48.

- [22] D.-H. Cho et al., "Transparent Al–Zn–Sn–O Thin Film Transistors Prepared at Low Temperature," *Appl. Phys. Lett.*, vol. 93, no. 14, 2008, pp. 142111-142113.

- [23] S.J. Yun et al., "Dependence of Atomic Layer-Deposited Al<sub>2</sub>O<sub>3</sub> Films Characteristics on Growth Temperature and Al Precursors of Al(CH<sub>3</sub>)<sub>3</sub> and AlCl<sub>3</sub>," *J. Vac. Sci. Technol. A*, vol. 15, no. 6, 1997, pp. 2993-2997.

- [24] C.G. Van de Walle, "Hydrogen as a Cause of Doping in Zinc Oxide," *Phys. Rev. Lett.*, vol. 85, no. 5, 2000, pp. 1012-1015.

- [25] R.L. Hoffman, "ZnO-Channel Thin Film Transistor: Channel Mobility," J. Appl. Phys., vol. 95, no. 10, 2004, pp. 5813-5819.

- [26] J.S. Park et al., "Electronic Transport Properties of Amorphous Indium-Gallium-Zinc Oxide Semiconductor upon Exposure to Water," Appl. Phys. Lett., vol. 92, no. 7, 2008, pp. 72104-72106.

- [27] J.K. Jeong et al., "Origin of Threshold Voltage Instability in Indium-Gallium-Zinc Oxide Thin Film Transistors," *Appl. Phys. Lett.*, vol. 93, no. 12, 2008, pp. 123508-123510.

- [28] H. Yin et al., "Bootstrapped Ring Oscillator with Propagation Delay Time below 1.0 nsec/stage by Standard 0.5 µm Bottom-Gate Amorphous Ga2O3-In2O3-ZnO TFT Technology," *Electron Device Meeting, IEEE International*, 15-17, Dec. 2008, pp. 1-4.

Sang-Hee Ko Park received the BS and MS degrees in chemistry education from Seoul National University in 1987 and 1989, respectively, and the PhD in chemistry from the University of Pittsburgh in 1997. Her dissertation work included the mechanism of synthesis of organometallic compounds. After

graduation, she joined the Electronics and Telecommunications Research Institute, Korea, in 1998, where she has worked on the fabrication of electroluminescent displays, phosphors, and OLED passivation using ALD. She has been working on the development of transparent oxide TFTs.

**Doo-Hee Cho** received the PhD in materials chemistry from Kyoto University in 1996. He worked in the area of float glass manufacturing and LOW-E coating on float glass at the glass research center of Keumkang Chemical Co. from 1996 to 1998. Since he joined Electronics and Telecommunications Research Institute in

1998, he has been involved in specialty optical fiber material and transparent oxide TFT research. His major research interests include oxide TFTs and transparent display devices.

Chi-Sun Hwang received the BS degree from Seoul National University in 1991 and the PhD from Korea Advanced Institute of Science and Technology in 1996, both in physics. From 1996 to 2000, he worked to make a DRAM device with 0.18 µm technology at Hyundai Semiconductor Inc. Since he joined ETRI in

2000, he has been involved in flat panel display research, including active-controlled field emission displays, OLED, and transparent displays with oxide thin-film transistors.

Shinhyuk Yang received the ME degree in electronics engineering from Dankook University in 2008. He joined Electronics and Telecommunications Research Institute in 2007. He has been focusing on research and development of stability characteristics of oxide TFTs and flexible devices composed of

oxide/organic materials. He is now a candidate for the PhD with Kyung-Hee University.

Min Ki Ryu received the BS and PhD degrees from Pusan National University in 1998 and 2005, respectively, both in solid-state physics. Since he joined ETRI in 2006, he has been involved in oxide electronics, including oxide-TFTs and memory devices.

Chun-Won Byun received the BS and MS degrees in electrical and computer engineering from Hanyang University, Seoul, Korea, in 2002 and 2007, respectively. In 2007, he joined the Transparent Display Team of the Electronics and Telecommunications Research Institute (ETRI), Daejeon, Korea. His research

interests include transparent electronics and driving methods, as well as circuits for flat panel displays.

**Sung Min Yoon** received the BS in inorganic material engineering from Seoul National University, Seoul, Korea, in 1995, and the MS and PhD degrees in applied electronics from Tokyo Institute of Technology (TIT), Tokyo, Japan, in 1997 and 2000, respectively. His PhD work focused on the fabrication of an adaptive-

learning neuron-chip using a ferroelectric memory device. His research interests include the characterization of next-generation nonvolatile memories, device physics and process technologies for functional electronic devices, as well as oxide electronics. He was awarded the Best Presentation Award at the E-MRS Spring Meeting in 2008. He was granted fellowships by the Marubun Research Promotion Foundation in 2000 and Japan Society for the Promotion of Science (JSPS) Invitation Fellowship Program in 2009.

Woo-Seok Cheong received the BS degree from Yonsei University, Seoul, Korea, in 1992, and the MS and PhD degrees from Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 1994 and 1998, respectively. During his doctoral course, his research focused on charge-related deposition

phenomenon in chemical vapor deposition (CVD) and selective epitaxial growth (SEG). From 1998 to 2001, he was with Hyundai Electronics Inc. In 2002, he joined ETRI. His major interests are fabrication of nano-sized electronic devices, tunneling magnetoresistance (TMR) sensors in hybrid magnetic recording systems, carbon nanotubes, transparent conductive oxides, ionized physical vapor deposition equipment, new oxide semiconductors, flexible transistors, and highly stable oxide thin-film transistors. Currently, he is preparing the realization of transparent displays for carnavigation.

**Kyoung Ik Cho** received the BS degree in materials science from Ulsan Institute of Technology in 1979, and the MS and PhD degrees in material science and engineering from Korea Advanced Institute of Science and Technology, in 1981 and 1991, respectively. He joined the Electronics and Telecommunications

Research Institute (ETRI) in 1981. He has been working on the development of advanced display devices, and new electronic devices and materials. His current research interests include oxide TFTs, transparent displays, and flexible electronic devices.

Jae-Hong Jeon received the BS, MS, and PhD degrees in electrical engineering from Seoul National University, in 1995, 1997 and 2001, respectively. After graduation, he joined Samsung Electronics, Korea, as a senior engineer, where he worked on AM-LCD products. He moved to Korea Aerospace

University, Korea, in 2005, and is currently an associate professor with the School of Electronics, Telecommunications, and Computer Engineering. His research interests include active matrix displays and devices.