# New Solid-phase Crystallization of Amorphous Silicon by Selective Area Heating

Do Kyung Kim, Woong Hee Jeong \*\*, Jung Hyeon Bae, and Hyun Jae Kim\*

#### **Abstract**

A new crystallization method for amorphous silicon, called selective area heating (SAH), was proposed. The purpose of SAH is to improve the reliability of amorphous silicon films with extremely low thermal budgets to the glass substrate. The crystallization time shortened from that of the conventional solid-phase crystallization method. An isolated thin heater for SAH was fabricated on a quartz substrate with a Pt layer. To investigate the crystalline properties, Raman scattering spectra were used. The crystalline transverse optic phonon peak was at about  $519 \text{ cm}^{-1}$ , which shows that the films were crystallized. The effect of the crystallization time on the varying thickness of the SiO<sub>2</sub> films was investigated. The crystallization area in the 400nm-thick SiO<sub>2</sub> film was larger than those of the SiO<sub>2</sub> films with other thicknesses after SAH at 16 W for 2 min. The results show that a SiO<sub>2</sub> capping layer acts as storage layer for thermal energy. SAH is thus suggested as a new crystallization method for large-area electronic device applications.

Keywords: Selective area heating, Crystallization, Polycrystalline Si, Capping layer

#### 1. Introduction

Polycrystalline Si (poly-Si) is one of the most important materials for fabricating large-area electronic devices and solar cells. Poly-Si provides higher device reliability, better electrical performance, and a lower defect density than amorphous silicon (a-Si). Many crystallization technologies for poly-Si production have been proposed, including solid-phase crystallization (SPC) [1], rapid thermal annealing (RTA) [2], metal-induced lateral crystallization (MILC) [3], and excimer laser annealing (ELA) [4]. SPC requires a long annealing time, though. RTA has been proposed to reduce the crystallization time, as its temperature is higher than that of SPC, but it has caused problems such as glass bending. MILC has been used to reduce the crystallization time and temperature by employing the catalytic effect of metals such as Ni, but metal contamination occurred on the active layer. One of the most promising crystallization technologies for obtaining high-quality poly-Si is ELA, but it has a high process cost. Thus, these technologies that require high temperature, long annealing time, and high cost are not suitable for large and flexible displays.

To reduce the process temperature, time, and cost, various crystallization technologies for a-Si films with jouleheating-induced crystallization, radio-frequency thermal plasma annealing, and selective area laser annealing had been studied. Hong et al. proposed a crystallization technology for a-Si films that uses Joule-heating [5]. Haruta et al. attempted the rapid crystallization of a-Si utilizing the radio-frequency-inductive coupling thermal plasma torch of argon [6]. Viatella et al. developed selective area crystallization using surface masking of the film during standard laser irradiation [7]. Other groups had presented effective methods for selective laser crystallization to improve electrical performance and carrier mobility. The problem of non-uniformity has remained, however, in the case of largearea AMOLEDs [8]. In this paper, a new crystallization method with a non-laser process that uses selective area heating (SAH) for high-reliability TFTs is suggested. Glass substrates have low thermal damage due to radiant thermal energy. In this study, the energy was limited to a welldefined selective area. The effect of the SiO<sub>2</sub> capping layer with various thicknesses on the crystallization of a-Si by SAH was studied in detail. Processes for mass production

Manuscript Received August 31, 2009; Revised September 11, 2009; Accepted for publication September 16, 2009.

This work was supported by the Korea Science and Engineering Foundation [KOSEF, R0A-2007-000-10044-0 (2007)] and by the Korea Research Foundation [KRF, KRF-2007-357-D00136 (2007)] of the Korean Government (MOST).

\*Member, KIDS; \*\*Student Member, KIDS

Corresponding author: Hyun Jae Kim

School of Electrical and Electronic Engineering, Yonsei University, 262 Seongsanno, Seodaemun-Gu, Seoul 120-749, Korea

**E-mail**: hjk3@yonsei.ac.kr **Tel**: +82-2-2123-5865 **Fax**: +82-2-871-7323

of large-area displays were proposed.

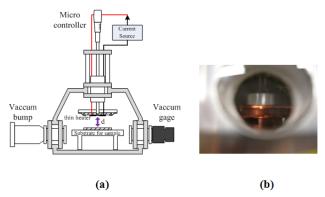

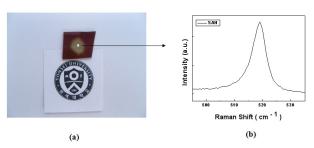

## 2. EXPERIMENTAL METHODOLOGY

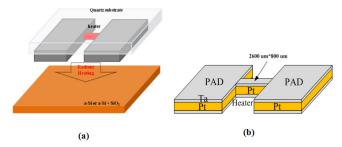

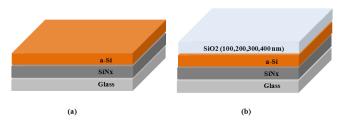

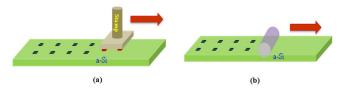

A 200-nm-thick SiN<sub>x</sub> film and a 200-nm-thick a-Si film were deposited successively on a glass substrate using plasma-enhanced chemical vapor deposition (PECVD). The substrate temperature was kept lower than 150°C during the deposition. SiO2 layers with various thicknesses were deposited on the a-Si films by RF sputtering. Figure 1 (a) shows the experimental setup for the SAH that was provided with a stamp-type thin heater with a micro-controller. The gap between the heater and the sample was about 0.3 mm. The sample was loaded onto a plate in the vacuum chamber, where the SAH was performed via joule heating. Figure 1 (b) shows an emission image of the SAH at 16 W. The surface temperature of the heater was measured with an optical pyrometer. Figure 2 (a) shows the radiant heating in the schematic diagram of the SAH. A Pt thin heater was patterned on a quartz substrate for selective heating of the a-Si film, as shown in Figure 2 (b). A 5,000 Å-thick Pt film was deposited by DC sputtering. Pt proved to be a suitable material for the thin heater due to its resistance to oxidation, its high melting point (1,769°C), and its simple deposition [9]. The area of the thin heater was 2,600 µm x 800 µm, and its thickness was 500 nm. The thin heater had a 20-nm-thick Ta adhesion layer and a 50-nm-thick Ta capping layer for improved reliability. Figure 3 (a) shows the a-Si layer sample. Figure 3 (b) shows the SiO<sub>2</sub> capping layer samples with various thicknesses for the investigation of the effect of the capping layer thickness on the crystallization process. After the crystallization of the a-Si films via thin heater annealing, the properties of the poly-Si were investigated using Raman spectroscopy. The Raman spectra were fitted with a Si wa-

Fig. 1. (a) Experimental setup and (b) emission image of the thin heater.

**Fig. 2.** (a) Schematic diagram of the crystallization process of SAH and (b) structure of the thin heater.

Fig. 3. (a) Si layer sample and (b)  $SiO_2$  capping layer sample with various  $SiO_2$  thicknesses (100-400 nm).

fer. The peak position and full width at half maximum of the Si wafer were 519.891cm<sup>-1</sup> and 3.17cm<sup>-1</sup>, respectively. The Raman spectra were measured at room temperature in a confocal geometry using a 514.532nm Ar-ion laser. To avoid laser-induced crystallization, the power of the laser was induced under 0.5mW.

## 3. RESULTS AND DISCUSSION

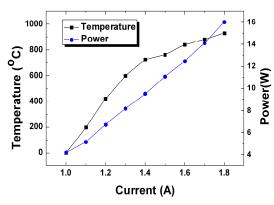

Applied power was calculated by applying current and measuring the voltage. The input current was induced from 1A to 1.8 A. The applied power can be described as follows:

$$P = V \times I \tag{1}$$

where P is the applied power, V is the measured voltage, and I is the applied current. The temperature of the thin heater was measured using an optical pyrometer. Figure 4 shows the surface temperature of the thin heater, which was increased in proportion to the applied power. The heater was damaged by electromigration under high current densities. To improve the reliability of the thin heater, the Pt thin heater was provided with an adhesion layer and a capping layer [9]. These layers protected the heater from electromigration and increased its lifetime. Figure 5 (a) shows the photograph of the crystallized Si area in the a-Si layer sample using SAH at 16 W for 4 min. The color of the crystallized area was brighter than that of the a-Si area, and the

**Fig. 4.** Relationship between the applied power and the surface temperature of the thin heater.

Fig. 5. Photograph of the crystallized Si using (a) the SAH and (b) the Raman spectra of the a-Si.

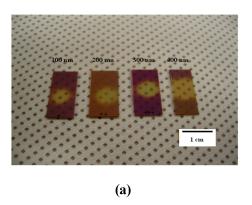

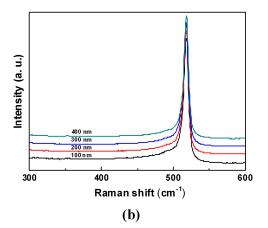

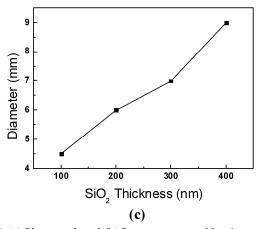

sharp seemed like a circle due to radiant thermal energy. The crystallinity of the a-Si films was measured by Raman spectroscopy. The crystalline transverse optic (TO) phonon peak of the a-Si films was observed at around 519cm<sup>-1</sup> at position "a," as shown in Figure 5 (b). It was a poly-Si peak in the SAH-created material [10]. The glass substrate had no damage because the radiant thermal heating was exposed to the well-defined selected area. Figure 6 (a) shows the image of the SiO<sub>2</sub> samples with various thicknesses after SAH at 16 W and 2 min. The Si with the 400-nm-thick SiO<sub>2</sub> capping layer produced a larger crystallized area than the Si with other capping layer thicknesses. The Raman spectra data of the poly-Si with various SiO2 thickness samples show nearly the same poly-Si peaks in Figure 5 (b). As the SiO2 capping layer thickness increased, the diameter of the crystallized Si area also increased, as shown in Figure 5 (c). To study the crystallinity, the crystal volume fraction (X<sub>c</sub>) was obtained from the Raman spectra and calculated using the following formula [11]:

$$Xc = \frac{Im + Ic}{Im + Ic + Ia} \tag{2}$$

**Fig. 6.** (a) Photograph and (b) Raman spectra with micropatterned SiO2 layer after SAH at 16 W for 2 min, respectively. (c) Relationship between the SiO2 layer thicknesses and diameters of the crystallized Si area.

where  $I_a$  is an indicator of the amorphous state,  $I_m$  is an indicator of the intermediate state, and  $I_c$  is an indicator of the crystalline state. According to Equation (2), the crystal volume fractions of the SiO<sub>2</sub> thin films with capping layer thicknesses after the SAH values of 100, 200, 300, and 400nm were 92.6%, 93.4%, 93.8%, and 94.4%, respectively.

**Fig. 7.** (a) The proposed stamp and (b) the roll-to-roll process using a new crystallization method with thin heaters.

Figure 5 (b) shows the variations in the crystal volume fraction with increasing capping layer thickness. The volume fraction gradually increased with the increase in the SiO2 capping layer thickness. The volume fraction differences might have been due to an increase in the thermal energy stored in the multilayer structure [12]. Enhanced containment of the thermal energy in the film might have occurred from both the radiant energy and the conductive thermal energy in the capped samples.

Figure 7 shows the proposed processes using a new crystallization method with thin heaters. It can be adopted to crystallize a-Si thin films in the predetermined active area on large substrates effectively and repeatedly. SAH is suggested as a low-cost and promising technology for large-area electronic devices.

# 4. CONCLUSION

A new crystallization method for highly reliable selective area crystallization was proposed. Because radiant energy was exposed to the well-defined area, the glass substrate had no thermal budget via SAH. The crystallization time was made shorter than that in the conventional SPC method using a stamp-type isolated thin heater and an SiO<sub>2</sub> capping layer. The crystalline TO phonon peak was observed at about 519 cm<sup>-1</sup>. The crystallinity gradually in

creased with the increase in the SiO<sub>2</sub> capping layer thickness, which was due to the increase in the thermal energy stored in the SiO<sub>2</sub> capping layer. This new crystallization method is proposed for cost-effective processes such as stamping and roll-to-roll processes.

## References

- [1] A. Nakamura, F. Emoto, E. Fujii, A. Yamamoto, Y. Uemoto, K. Senda, and G. Kano, J. Appl. Phys. 66, 4248 (1989).

- [2] X. Zhang, T. Zhang, M. Wong, and Y. Zohar, J. MICROELECTROMECHANICAL SYSTEMS Vol. 7, 356 (1998).

- [3] J.H. Choi, D.Y. Kim, B.K. Choo, W.S. Sohn, and J. Jang, *Electrochemical and Solid-State Lett.* **6**, G16 (2003).

- [4] K. Shimizu, O. Sugiura, and M. Matsumura, *IEEE TRANSACTIONS ON ELECTRON DEVICES* Vol. 40, 112 (2003).

- [5] W.E. Hong, and J.S. Ro, Thin Solid Films 515, 5357 (2007).

- [6] K. Haruta, M. Ye, Y. Takemura, T. Kobayashi, T. Ishikawa, J. K. Saha, H. Shirai, J. Non- Crystalline Solids 354, 2333 (2008).

- [7] J. Viatella, S.M. Lee, and R. K. Singh, J. The Electrochemical Society 146, 4605 (1999).

- [8] K. C. Park, J. H. Jeon, Y. I. Kim, J. B. Choi, Y. J. Chang, Z. F. Zhan, and C. W. Kim, Solid-State Electronics 52, 1691 (2008).

- [9] Samara L. Firebaugh, Klavs F. Jensen, and Martin A. Schmidt, J. MICROELECTROMECHANICAL SYSTEMS Vol. 7, 1057 (1998).

- [ 10 ] D. K. Kim, W. H. Jeong, C. H. Lee, T. H. Jeong, K. H. Kim, T. H. Hwang, N. S. Roh, and H. J. Kim, *J. Molecular Crystals and Liquid Crystals* (2009) in press

- [11] J. M. Owens, D. Han, B. Yan, J. Yang, K. Lord, and S. Guha, in *Proc. Mater. Res. Soc. Symp.* (2003), p.762.

- [ 12 ] J. Viatella, R.K. Singh, *Materials Science and Engineering*, **B47**, 78 (1997).