**JPE 9-5-5**

# A New Zero Voltage Transition Bridgeless PFC with Reduced Conduction Losses

Mohammad Mahdavi † and Hosein Farzanehfard \*

†\*Dept. of Electrical and Computer Eng., Isfahan University of Technology (IUT), Iran

#### **ABSTRACT**

In this paper a new zero voltage transition PWM bridgeless PFC is introduced. The auxiliary circuit provides soft switching condition for all semiconductor devices. Also, in the resonant path of the auxiliary circuit, only two semiconductor devices exist. Therefore the resonant conduction losses are low. Furthermore, the auxiliary circuit semiconductor elements consist of only one diode and one switch. The proposed auxiliary circuit is applied to a bridgeless PFC converter to further reduce conduction and switching losses. In this paper, the operating modes of this converter are explained and the resulting ideal and simulation waveforms are shown. The presented experimental results justify the theoretical analysis.

**Keywords:** Boost converter, Bridgeless PFC, Power Factor Correction (PFC), Soft switching, Zero Voltage Transition (ZVT)

#### 1. Introduction

By increasing the use of rectifiers in electrical equipments, undesirable harmonics are injected to the power grid and thus can cause many problems<sup>[1]</sup>. To reduce the effect of this nonlinear load, some international standards like IEC 61000-3-2 are introduced<sup>[2]</sup>. Most of the power supplies use conventional rectifier with a large filter capacitor at the end of rectification. This causes excessive peak current, high harmonic distortion and low power factor of about 0.5-0.7. Therefore, the improvement of input power factor has become mandatory<sup>[3], [4]</sup>.

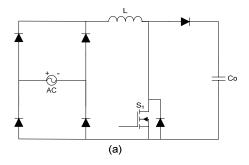

The usual topology employed in power factor correction (PFC) is a rectifier followed by a boost converter as

Manuscript received Jan. 20, 2009; revised July 7, 2009 <sup>†</sup>Corresponding Author: mu.mahdavi@gmail.com Tel: +98-311-3912450, Fax: +98-311-3912451, IUT. <sup>\*</sup>Dept. of Electrical and Computer Eng., IUT.

shown in Fig. 1(a)<sup>[5]</sup>. This conventional PFC converter has three elements in power flow path. To reduce conduction losses, two methods are introduced in the literature. First method is bridgeless PFC as shown in Fig. 1(b) and the other one is single stage PFC (S<sup>2</sup>PFC)<sup>[6-8]</sup>. In higher power applications, S<sup>2</sup>PFC is not applied since it will result in extra voltage and current stresses for semiconductor devices and it will require bulky filters. Therefore, bridgeless PFC is a better candidate for high power applications. To reduce the converter weight and volume, high switching frequency is unavoidable<sup>[3,4,9]</sup>. At high frequencies, MOSFET is the proper choice. Usually zero voltage switching techniques are applied to MOSFET since they can eliminate switching losses as well as capacitive turn on losses<sup>[5-8]</sup>.

Several soft switching bridgeless PFC converters are introduced in literatures<sup>[4,13-21]</sup>. However, they all suffer from high number of auxiliary elements (especially

Fig. 1. (a) Conventional PFC converter. (b) Conventional bridgeless PFC.

semiconductor devices) to provide soft switching. Also, in some converters, the auxiliary switch operates under hard switching condition <sup>[13-15]</sup>. The proposed converter has less number of semiconductor components and the auxiliary switch operates under soft switching conditions. The proposed converter has only five auxiliary elements (one switch, one diode, two capacitors and one inductor). The converters in references <sup>[4,16,17]</sup> have three semiconductors in the resonant path while the proposed converter has two semiconductors in resonant path. Therefore the conduction losses during the resonant are reduced.

In this paper, a new zero voltage transition (ZVT) PWM Bridgeless PFC is introduced. In the next section, the operation of proposed converter is analyzed. In section III, the design procedure and experimental considerations are explained. The simulation results are presented in section IV and to confirm the theoretical analysis, a prototype of the converter is implemented and the experimental results are shown in section V.

## 2. Proposed bridgeless PFC circuit operation

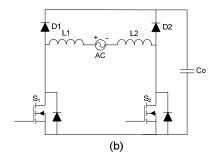

The power stage of proposed ZVT-PFC converter is shown in Fig. 2(a). The circuit in doted box is the

proposed auxiliary circuit which provides soft switching. The auxiliary circuit is composed of  $D_3$ ,  $L_r$ ,  $C_{r1}$ ,  $C_{r2}$  and  $S_3$ . The converter operates like a conventional PWM bridgeless PFC except for the switches' turn off and turn on instants. Zero voltage switching (ZVS) at turn off instant is provided by  $C_{r1}$  and  $C_{r2}$ , while ZVS at turn on instant is prepared by turning on the auxiliary switch for a fixed time.

The converter operation is symmetrical in two cycles of input line. Therefore, the converter operation in one line cycle (positive half line cycle) is explained. To simplify the converter operation analysis, it is assumed that the converter is operating at steady state and all circuit elements are ideal. In addition, the input boost inductance is supposedly large enough to be considered as an ideal dc current source ( $I_{\rm in}$ ) in a switching cycle. Also, it is assumed that the output capacitance is sufficiently large to be considered an ideal dc voltage source ( $V_{\rm O}$ ) as shown in Fig. 2(b).

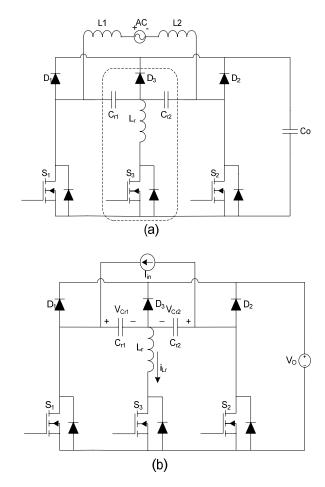

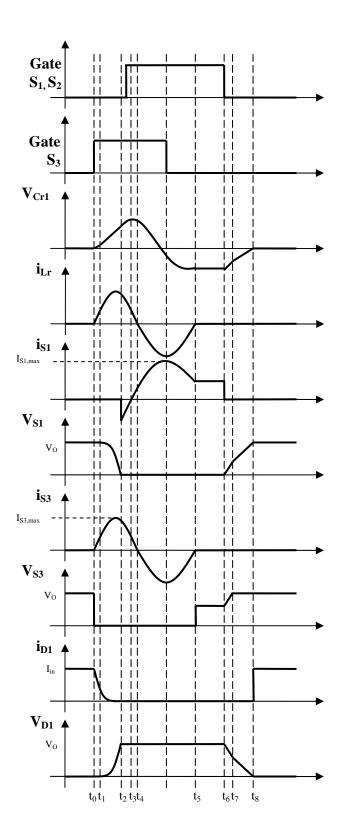

Based on the above assumptions, circuit operation in a switching cycle can be divided into nine modes as shown by the equivalent circuits in Fig. 3. The theoretical waveforms are illustrated in Fig. 4. Before the first mode, it is assumed that  $D_1$  and the body diode of  $S_2$  are conducting and all other semiconductor devices are off. Also,  $C_{r2}$  is charged to  $V_O$  and  $C_{r1}$  is discharged completely.

## $\triangleright$ Mode 1: [t<sub>0</sub>-t<sub>1</sub>] (Fig. 4(a))

This mode begins by turning on  $S_3$  and a resonance starts between  $L_r$ ,  $C_{r1}$  and  $C_{r2}$ . Therefore,  $S_3$  is turned on under zero current switching (ZCS) condition. The resonant inductor current is:

$$i_{Lr}(t) = \frac{V_O}{Z_1} \sin(\omega_1(t - t_0))$$

(1)

where

$$Z_1 = \sqrt{\frac{L_r}{C_{r1} + C_{r2}}}, \omega_1 = \frac{1}{\sqrt{L_r(C_{r1} + C_{r2})}}$$

(2)

This mode ends when  $C_{r1}$  current  $(I_{Cr1})$  reaches the input current  $(I_{in})$ . The current through  $C_{r1}$  and the duration of this mode is:

Fig. 2. (a) Proposed ZVT bridgeless PFC converter.

(b) Equivalent circuit of proposed ZVT bridgeless PFC in a switching cycle.

$$i_{C_{r1}}(t_1) = \frac{i_{Lr}(t_1)}{2} = I_{in}$$

(3)

$$t_1 - t_0 = \frac{\sin^{-1}(\frac{2I_{in}Z_1}{V_O})}{\omega_1} \tag{4}$$

# ightharpoonup Mode 2: [t<sub>1</sub>-t<sub>2</sub>] (Fig. 4(b))

In this mode  $I_{Cr1}$  is equal to  $I_{in}$  and thus, the voltage of  $C_{r1}$  increases linearly while the resonance between  $L_r$  and  $C_{r2}$  continues. The voltages of these two capacitors are as following:

$$V_{C_{r1}}(t) = V_O(1 - \cos \omega_1 t_1) + \frac{I_{in}}{C_{r1}}(t - t_1)$$

(5)

$$V_{C_{r_2}}(t) = -V_O(\cos(\omega_1 t_1))\cos(\omega_2 (t - t_1))$$

where

$$\omega_2 = \frac{1}{\sqrt{L_r C_{r^2}}} \tag{7}$$

This mode lasts until the voltage of two resonant capacitors become equal. At this time, the voltage across  $S_1$  reaches zero. Therefore,  $t_2$  can be obtained by making (5) equal to (6).

## $\triangleright$ Mode 3: [t<sub>2</sub>-t<sub>3</sub>] (Fig. 4(c))

In this mode,  $C_{r1}$  and  $C_{r2}$  are in parallel ( $C_{eq}$ = $C_{r1}$ + $C_{r2}$ ) and begin to resonant with  $L_{r1}$ .  $S_1$  is turned on at ZVS. The resonant current of  $L_r$  and the voltage of  $C_{r1}$  and  $C_{r2}$  are obtained from (8) and (9).

$$i_{Lr}(t) = \frac{V_{C_{r2}}(t_2)}{Z_1} \sin(\omega_1(t - t_2))$$

$$-i_{Lr}(t_2)\cos(\omega_1(t - t_2))$$

(8)

$$V_{C_{r_1}}(t) = V_{C_{r_2}}(t) = V_{C_{r_2}}(t_2)\cos(\omega_1(t - t_2))$$

$$-i_{L_r}(t_2)Z_1\sin(\omega_1(t - t_2))$$

(9)

This mode continues until  $S_1$  body diode current becomes zero. In other words, this mode ends when  $i_{Lr}$  reaches  $2I_{in}$ . The duration of this mode is calculated by solving the following equation.

$$2I_{in} = \frac{V_{C_{r_2}}(t_2)}{Z_1} \sin(\omega_1(t_3 - t_2))$$

$$-i_{I_x}(t_2)\cos(\omega_1(t_3 - t_2))$$

(10)

#### $\triangleright$ Mode 4: [t<sub>3</sub>-t<sub>4</sub>] (Fig. 4(d))

The current through  $S_1$  increases sinusoidally. This mode ends when the  $S_1$  current reaches  $I_{in}$  and  $L_r$  current reaches zero. Note that  $V_{Cr1}$  or  $V_{Cr2}$  waveforms still follow equation (9). Duration of this mode is:

$$t_4 - t_3 = \frac{\tan^{-1}(\frac{Z_1 i_{Lr}(t_2)}{V_{C_{r_2}}(t_2)})}{\omega_1} - (t_3 - t_2)$$

(11)

# ightharpoonup Mode 5: [t<sub>4</sub>-t<sub>5</sub>] (Fig. 4(e))

At the beginning of this mode,  $S_3$  current is reversed and becomes negative. The current through the body diode of  $S_3$  is divided equally between  $C_{r1}$  and  $C_{r2}$ . The current

through  $C_{r1}$  is an extra current stress on  $S_1$  and the current through  $C_{r2}$  reduces the current flowing in  $S_1$  body diode. Due to simultaneous gating of  $S_1$  and  $S_2$ , if the current flowing through  $C_{r2}$  is larger than  $I_{in}$ , then  $S_2$  switch conducts instead of its body diode. During this mode,  $S_3$  is turned off under ZVS. The voltages of  $C_{r1}$  and  $C_{r2}$  are equal in this mode and are obtained like the previous mode from (9). The duration of this mode is half of the resonance period. The current of  $L_r$  can be calculated from (8). This mode ends when  $L_r$  current reaches zero.

#### $\triangleright$ Mode 6: [t<sub>5</sub>-t<sub>6</sub>] (Fig. 4(f))

This mode begins when  $L_r$  current reaches zero and the voltage across  $S_3$  rises to  $V_{O^-}V_{Cr1,2}(t_5)$ . This mode is similar to conventional boost converter and the input inductor is charged. The input current waveform is controlled by the duration of this mode. Voltages of  $C_{r1}$  and  $C_{r2}$  are equal and constant in this mode and can be obtained by (12).

$$V_{C_{r_1}}(t_5) = V_{C_{r_2}}(t_5) = V_{C_{r_2}}(t_2)\cos(\omega_1(t_5 - t_2))$$

$$-i_{L_r}(t_2)Z_1\sin(\omega_1(t_5 - t_2))$$

(12)

## ightharpoonup Mode 7: [t<sub>6</sub>-t<sub>7</sub>] (Fig. 4(g))

By turning off  $S_1$  at the beginning of this mode,  $S_1$  current is forced to flow through  $C_{r1}$  and  $C_{r2}$ . The voltage of  $S_1$  increases linearly. Therefore,  $S_1$  is turned off under soft switching condition (ZVS). This mode is over when the  $C_{r2}$  voltage reaches  $V_O$ . The duration of this mode is:

$$t_6 - t_5 = C_{r2} \frac{Vo - V_{C_{r1,2}}(t_4 - t_5)}{I_{in}}$$

(13)

## ightharpoonup Mode 8: [t<sub>7</sub>-t<sub>8</sub>] (Fig. 4(h))

Once  $C_{r2}$  Voltage reaches  $V_O$  at the end of the previous mode,  $D_3$  starts to conduct in this mode. The voltage of  $C_{r2}$  is clamped at  $V_O$  and  $C_{r1}$  discharges. This stage lasts until  $V_{Cr1}$  reaches zero. The duration of this mode is:

# ightharpoonup Mode 9: [ $t_8$ - $t_0$ ] (Fig. 4(i))

$D_1$  turns on at the beginning of this mode and the input inductor energy is transferred to the output. This mode is similar to turn off interval in conventional boost converter.

Fig. 3. Theoretical Waveforms of the proposed PFC converter.

Fig. 4. Equivalent circuit of each mode.

# 3. Design Considerations

Design considerations of this converter are explained in five sections.

1. The resonant elements ( $C_{r1}$ ,  $C_{r2}$  and  $L_r$ ):

To provide soft switching, two conditions must be satisfied. First,  $I_{Cr1}$  must reach  $I_{in}$  in mode 1. Therefore from (1) and (3), the following is established:

$$Z_1 \le \frac{V_O}{2I_{in}} \tag{14}$$

Second condition arises from mode 2. At the end of this mode, the voltage of two capacitors must reach the same voltage to provide zero voltage across  $S_1$ . Therefore

$$V_{O}(1 - \cos \omega_{l}t_{1}) + \frac{\pi I_{in}}{\omega_{l}C_{r1}} \leq V_{O}(\cos(\omega_{l}t_{1}))$$

$$\Rightarrow \cos(\omega_{l}t_{1}) - \frac{\pi I_{in}}{2V_{O}\omega_{l}C_{r1}} \geq 0.5$$

(15)

The resonant inductor value is selected based on the output power and the main diode turn off speed <sup>[22]</sup>. By selecting resonant inductor and the above considerations, the resonant capacitors are chosen.

2. Selection of  $S_1$ ,  $S_2$  and  $S_3$ :

The peak current and the voltage stresses are obtained from the following equations:

$$V_{SW1,2,3\,\text{max}} = V_{O\,\text{max}} \tag{16}$$

$$I_{SW1,2 \max} = I_{IN \max} + \frac{\Delta I_L}{2} + \frac{1}{2} \sqrt{\left(\frac{V_{C_{r_2}}(t_2)}{Z_1}\right)^2 + i_{L_r}(t_2)^2}$$

(17)

$$I_{SW3 \,\text{max}} = \sqrt{\left(\frac{V_{C_{r2}}(t_2)}{Z_1}\right)^2 + i_{Lr}(t_2)^2}$$

(18)

#### 3. Selection of $D_1$ , $D_2$ and $D_3$ :

The peak current and voltage stresses are obtained from the following equations:

$$V_{D1.2\,\text{max}} = V_{O\,\text{max}} \tag{19}$$

$$I_{D1,2,3\,\text{max}} = I_{IN\,\text{max}} + \Delta I_L/2 \tag{20}$$

## 4. Selection of $L_1$ , $L_2$ and $C_0$ :

The boost inductance  $L_1+L_2$  and the output filter capacitance  $C_O$  are selected to minimize the input current ripple and the output voltage ripple, respectively. The design method of input inductor and output capacitor can be obtained in the same way as in a conventional PWM converter is attained  $^{[23]}$ .

#### 5. Control circuit:

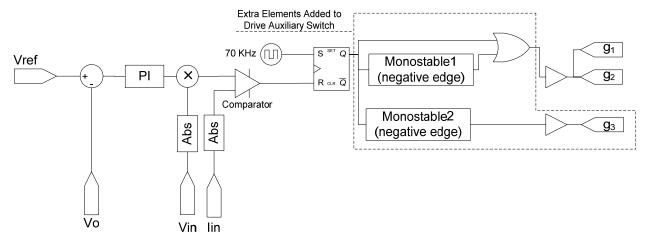

In general, the control method of this converter can be the same as conventional PWM-PFC. For simplicity, peak current mode control is used in this paper as shown in Fig. 5. The differences between the proposed converter controller and the conventional PWM-PFC controller are in the presence of two monostables, a gate driver and a XOR gate as shown in the doted box in Fig.5. The extra components are required to drive the auxiliary switch. If these four extra elements are added to any control method used for conventional PWM-PFC, then that control system can be used for the proposed PFC and, thus, conventional PFC control ICs can be employed. Based on the converter operation explained in the previous section, the on time of monostable 1 is equal to on time of  $S_3$  while the on time of monostable2 is equal to the delay time between turning on signals of  $S_1$  and  $S_3$ .

#### 4. Simulation Results

The proposed bridgeless PFC is simulated by PSIM when operating at 300W with  $V_{AC}\!\!=\!\!110~V_{rms},~V_{O}\!\!=\!\!200~V_{DC}$  and  $f_{sw}\!\!=\!\!70KHz$ . According to the above design considerations, the circuit elements are obtained as  $L_{r}\!\!=\!\!6\mu H,~C_{r1}\!\!=\!\!C_{r2}\!\!=\!\!30nF,~L1\!\!=\!\!L2\!\!=\!\!300\mu H,~C_{O}\!\!=\!\!1000\mu F.$

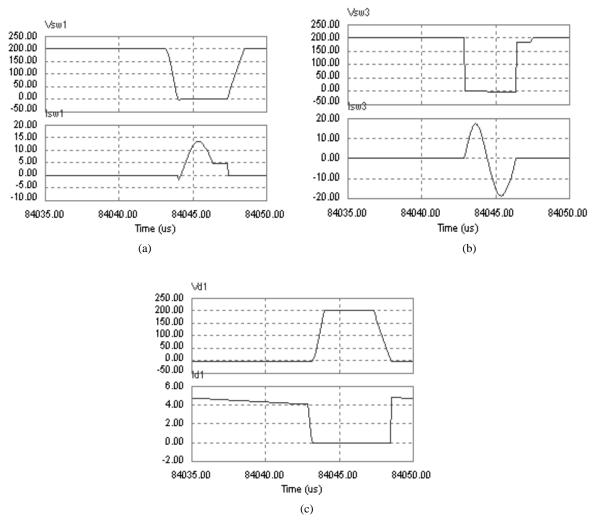

The simulation results in Fig. 6, show soft switching for semiconductor devices. The ZVS of main switches  $(S_1, S_2)$ ,

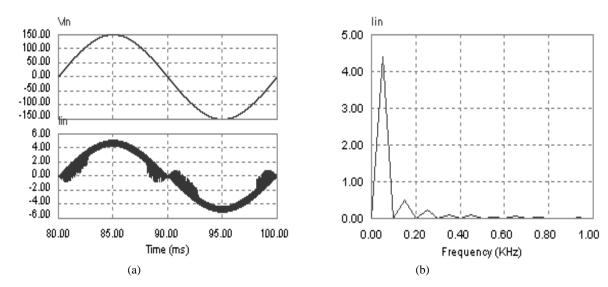

ZCS of auxiliary switch  $S_3$  and ZVS of main diode ( $D_1$ ,  $D_2$ ) are illustrated respectively in Fig. 6(a-c). The input line voltage, line current and input current harmonics are shown in Fig. 7. The input current is practically sinusoidal with low total harmonic distortion (THD) and high power factor (PF). All line current harmonics are below the IEC61000-3-2 requirements <sup>[2]</sup>.

## 5. Experimental Results

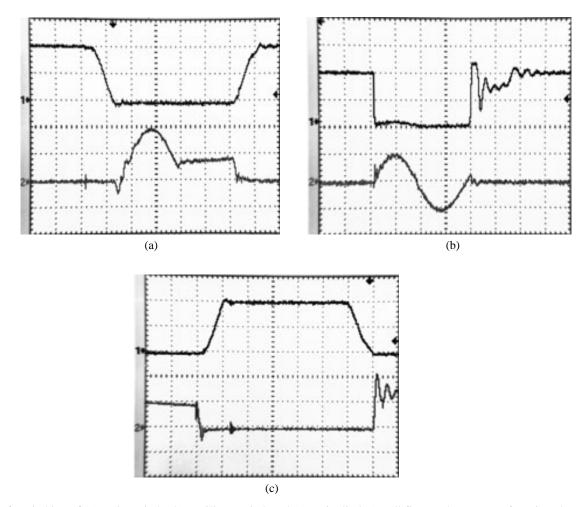

A prototype of simulated PFC converter is implemented to show the validity of theoretical analysis and simulation results. The proposed bridgeless PFC converter is realized by IRFP460 for switches and FES8JT for all diodes. The voltage and current of all semiconductor devices in the proposed PFC converter are shown in Fig. 8. The ZVS of main switches  $(S_1, S_2)$ , ZCS of auxiliary switch  $S_3$  and ZVS of main diode  $(D_1, D_2)$  are shown respectively in Fig. 8(a-c). The zero level of each channel is shown by "1" and "2" on the left side of each figure. In comparison to simulation results, the experimental results exhibit ringing starting at  $t_5$ . This is due to the resonance between parasitic inductances,  $L_{\rm L}$  and junction capacitance of  $S_3$ .

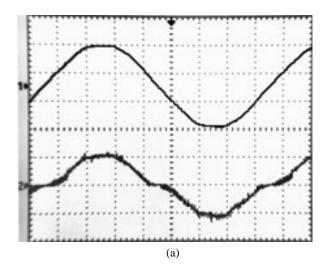

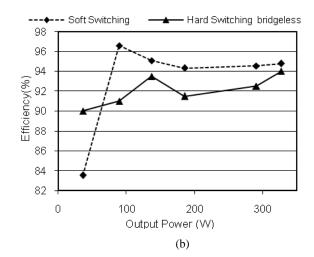

The input current and voltage and the efficiency of this converter in different loads are shown in Fig. 9. The waveforms of input voltage and current are almost in phase and the measured power factor is close to unity especially when the input voltage is fully sinusoidal. On average, the efficiency is improved by 2% for different loads.

# 6. Conclusions

In this paper, a new ZVT PWM bridgeless PFC is introduced and realized. The auxiliary circuit provides soft switching condition for all semiconductor devices. Only one diode and one switch are used in the auxiliary circuit. Since only two semiconductor devices exist in the resonant path of the auxiliary circuit, the conduction losses of resonant path are reduced. The proposed auxiliary circuit is applied to a bridgeless PFC converter in order to further reduce conduction and switching losses. The presented simulation and experimental results of the proposed converter show high efficiency of about 96% and near unity power factor for input current.

Fig. 5. Control circuit block diagram.

Fig. 6. Soft switching of (a) main switch, (b) auxiliary switch and (c) main diode(In all figures top waveform is voltage and bottom one is current).

Fig. 7. (a) top: line voltage and bottom: input line current. (b) Input current harmonics.

Fig. 8. Soft switching of (a) main switch, (b) auxiliary switch and (c) main diode (In all figures the top waveform is voltage (100V/div) and bottom is current (5A/div). Time scale is  $1 \mu s/div$ ).

Fig. 9. (a) top: line voltage and bottom: input line current (Voltage scale is 100 V/div and Current scale is 5 A/div). (b) Efficiency comparison of the proposed bridgeless PFC converter with its conventional counterpart.

#### References

- B. Singh, V. Garg, G. Bhuvaneswari, "An input current waveshaping AC-DC converter for rectifier loads", *Journal* of *Power Electronics*, Vol.8, No.1, PP. 1-9, 2008.

- [2] IEC 61000-3-2, International Electro technical Commission Geneve, Switzerland, 1998.

- [3] C. M. Wang, "A new single-phase ZCS-PWM boost rectifier with high power factor and low conduction losses", *IEEE Trans. Ind. Electron.*, Vol. 53, No. 2, Apr. 2006.

- [4] C. M. Wang, "A novel zero-voltage-switching PWM boost rectifier with high power factor and low conduction losses", *IEEE Trans. Ind. Electron.*, Vol. 52, No. 2, Apr. 2005.

- [5] E. Adib, H. Farzanehfard, "Family of isolated zero current transition PWM converters", *Journal of Power Electronics*, Vol. 9, No. 2, PP. 156-163, Mar. 2009.

- [6] E. Adib, H. Farzanehfard, "Zero-voltage transition current-fed full-bridge PWM converter" *IEEE Trans. Power Electron.*, Vol. 24, No. 4, PP. 1041-1049, Apr. 2009.

- [7] E. Adib, H. Farzanehfard, "Family of soft-switching PWM converters with current sharing in switches" *IEEE Trans. Power Electron.*, Vol. 24, No. 4, PP. 979-985, Apr. 2009.

- [8] M. R. Amini, H. Farzanehfard, "Novel Family of PWM Soft-Single-Switched DC–DC Converters With Coupled Inductors" *IEEE Trans. Ind. Electron.*, Vol. 56, No. 6, PP. 2108-2114, June 2009.

- [9] M. Kazerani, P. D. Ziogas, and G. Joos, "A novel active current wave shaping technique for solid-state input power factor conditioners", *IEEE Trans. Ind. Electron.*, Vol. 38, No. 1, PP. 72–78, Feb. 1991.

- [10] P. N. Enjeti, R. Martinez, "A high performance single-phase ac to dc rectifier with input power factor correction," in Proc. IEEE APEC, 1993, PP. 190–196.

- [11] L. Huber, Y. Jang, M. M. Jovanovic, "Performance Evaluation of Bridgeless PFC Boost Rectifiers" *IEEE Trans. Power Electron.*, Vol. 23, No. 3, PP. 1381–1390, May 2008.

- [12] C. Qiao, K. Smedley, "A Topology Survey of Single-Stage Power Factor Corrector with a Boost Type Input-Current-Shaper" *IEEE Trans. Power Electron.*, Vol. 16, No. 3, May 2001.

- [13] H. Y. Tsai, T. H. Hsia, D. Chen, "A novel soft-switching bridgeless power factor correction circuit", European Conference on Electronics and Applications, PP. 1–10, Sep. 2007.

- [14] I. D. Kim, E. C. Nho, S. H. Choi, J. S. Lai, "A simple ZVT PWM single-phase rectifier with reduced conduction loss and unity power factor", *Journal of Power Electronics*, Vol.7, No.1, PP. 55-63, 2007.

- [15] I. D. Kim, E. C. Nho, S. H. Choi, J. S. Lai, "Simple ZVT PWM single-phase rectifier with reduced conduction loss and unity power factor", 37th IEEE PESC conference, 2006.

- [16] C.M. da, C. Duarte, I. Barbi, "A new ZVS-PWM active clamping high power factor rectifier analysis design and experimentation", IEEE PESC Record, PP. 230–236, 1998.

- [17] A. F. de Souza, I. Barbi, "A new ZVS-PWM unity power factor rectifier with reduced conduction losses", *IEEE Trans. Power Electron*, Vol. 10, No. 6, Nov. 1995.

- [18] I. Kim, B. I. Bose, "A new ZCS turn-on and ZVS turn-off unity power factor PWM rectifier with reduced conduction

- loss and no auxiliary switches", *Electric Power Applications, IEE Proceedings*, Vol 147, No 2, PP. 146–152, Mar. 2000.

- [19] R. Srinivasan, R. Oruganti, "A unity power factor converter using half-bridge boost topology", *IEEE Trans. Power Electron*, Vol. 13, No. 3, PP. 487–500, May 1998.

- [20] M. Mahdavi, H. Farzanehfard, "Zero Current Transition Bridgeless PFC without Extra Voltage and Current Stress", *IEEE Trans. Ind. Electron.*, Vol. 56, No. 7, PP. 2540-2547 July 2009

- [21] M. Mahdavi, H. Farzanehfard, "A New Soft Switching Bridgeless PFC without Any Extra Switch", *International Review of Electrical Engineering*, Vol. 3, No. 5, , PP. 858-863, Oct 2008.

- [22] MCMURRAY W: 'Selection of snubbers and clamps to optimize the design of transistor switching converters', *IEEE Trans. Ind. Appl.*, 16, (4), PP. 513–523, 1980.

- [23] Unitrode Product and Applications Handbook 1995–1996, Unitrode Corp., Merrimack, NH, pp. 10-303–10-322, 1995.

Mohammad Mahdavi was born in Isfahan, Iran, in 1984. He received the B.S and M.S. degrees in electrical engineering from Isfahan University of Technology, Isfahan, Iran, in 2006 and 2009 respectively, where he is currently working toward the Ph.D. degree in

electrical engineering in the Department of Electrical and Computer Engineering, The isfahan university of technology (IUT). His research interest is soft switching techniques in PFC converters.

Hosein Farzanehfard was born in Isfahan, Iran in 1961. He received the B.S and M.S degrees in electrical engineering from university of Missouri, Columbia, Missouri, USA at 1983 and 1985 respectively. He received the Ph.D degree from Virginia Tech.,

Blacksburg, Virginia, USA at 1992. Since 1993, he has been a faculty member at department of electrical and computer engineering, Isfahan University of Technology, Isfahan, Iran. He is currently an associate professor and the president of Information and Communication Technology Institute. His research interests include high frequency soft switching converters, pulse power applications, power factor correction, active power filters and high frequency electronic ballasts. He is the author of more than 90 technical papers published in journals and conference proceedings.