논문 2009-04-04

## 아날로그 회로의 난검출 고장을 위한 효과적인 진단 및 테스트 기법

(Effective Techniques for Diagnosis and Test of Hard-to-Detect Faults in Analog Circuits)

### 이 재 민\*

(Jae-Min Lee)

Abstract: Testing of analog(and mixed-signal) circuits has been a difficult task for test engineers and effective test techniques to solve these problems are required. This paper develops a new technique which increases fault detection and diagnosis rates for analog circuits by using extended MTSS (Modified Time Slot Specification) technique based on MTSS proposed by the author. High performance current sensors with digital outputs are used as core components for these techniques. A fault diagnosis structure with minimal hardware overhead in ATE is also described.

Key words: Analog circuits, Current test, Current sensor, Hard-to-detect faults, Fault diagnosis structure, Specification-based test, Extended time slot specification (EMTSS)

#### 1. 서 론

다수의 IP들이 하나의 칩에 집적되는 SoC는 보 통 그 내부에 아날로그 회로와 디지털회로를 함께 포함하고 있다. SoC 회로는 높은 복잡도로 인한 입 출력의 제한 때문에 기존의 집적회로에 비해 더욱 효과적인 테스트가 필요하다. 아날로그 회로나 혼합 신호 회로의 테스팅은 디지털 회로의 테스팅과는 달리 보편화된 고장 모델이 충분히 개발되어 있지 않고 테스팅 기법도 디지털 방식에 비해 복잡하며 높은 고장 검출율과 진단율을 얻는 것이 쉽지 않다. 지금까지 고장 진단을 위한 방안으로서 디지털 영 역에서 사용되고 있는 내장 자체 테스트 (BIST) 방 식이 이용되어 왔다. Jhihong You[1]등은 심볼릭 시뮬레이션에 의해 피테스트 회로의 고장들을 평가 하는 테스트-전-시뮬레이션을 제안하였는데 강고장 에는 효과를 보이지만 약고장 검출에는 적합하지 않다. 한편 테스트-후-시뮬레이션 기법은[2] 회로

토폴로지(topology)로부터 얻어진 소자의 매개변수 값을 구하는 기법인데 약고장에 효과가 있는 반면 강고장에는 그다지 적절하지 못한 방법이다. 이러한 기존의 기법들 대부분은[3,4,5] 하드웨어의 구현이어렵고 회로 크기의 크기도 커서 실용적이지 못하다. 저자는 이러한 기존 방법의 단점을 고려하여 보다 효과적으로 아날로그 및 혼합신호를 테스트할수 있는 기법을 이전 연구에서 제안하였다[6,7]. 고정밀 저항을 가변하여 저류감지기의 탐지범위를 조정할 수가 있었던 기존 방법은 진단이 까다로운 고장들을 고유한(unique) 응답 패턴으로 유도할 수 있는 가능성을 가지고 있다. 고장 진단은 고장검출 기능과는 달리 고장의 위치를 발견할 수 있는 테스트 과정이므로 SoC등에 적용하여 임베디드 IP 코어의고장 유무를 찾는데에도 유용한 방법이 될 수 있다.

이러한 점을 고려하여 본 논문에서는 기존의 MTSS기법을 확장한 Extended MTSS 기법을 검출이 매우 까다로운 고장의 테스트에 확장 적용하여 고장 검출율 및 고장 진단율을 향상시키는 방법과 부가하드웨어 오버헤드를 최소화하는 고장 진단구조에 대해 논한다.

\* 교신저자(Corresponding Author)

논문접수 : 2009. 01. 05., 수정일 : 2009. 03. 06.,

채택확정: 2009. 03. 16

이재민 : 관동대학교 전자정보통신공학부

#### 2. Specification 기반의 전류 테스트

#### 2.1 전류센서를 이용한 고장 검출과 고장 진단

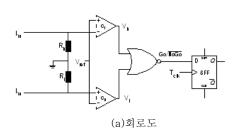

제안하는 아날로그 회로 테스트에서는 전류테스트 기법을 사용하므로 회로의 고장 사양을 검출하기 위해 전류감지기가 반드시 필요하다. 그림 1의 전류 감지기는 회로 사양을 벗어나는(out-of-specification) 고장이 발생하여 이를 테스트하고자할 때 파라메타로 전류를 사용한다. 만약 전류감지기가 피테스트 회로(CUT)내 어떤 가지에 흐르는 정상전류와 고장 전류를 비교하여 출력을 얻을 수 있다면 이 고장은 검출될 수 있을 것이다. 저자에 의해 제안된바 있는 그림 1의 내장 전류감지기는 피테스트 회로인 아날로그 회로 내 테스트 대상 노드로부터 전류를 감지하여 이것이 회로의 정상 동작주파수 내에서 최소전류(Imin)와 최대전류(Imax)의 범위 내에 있는지 또는 벗어났는지의여부(INSPEC 또는 OFFSPEC)를 판단한다[6].

| I <sub>in</sub>                                     | C <sub>1</sub> | C <sub>2</sub> | Go/NoGo | Q |

|-----------------------------------------------------|----------------|----------------|---------|---|

| I <sub>in</sub> <i<sub>min</i<sub>                  | нісн           | row            | D       | 0 |

| I <sub>min</sub> ≤I <sub>in</sub> ≤I <sub>nex</sub> | LOW            | LOW            | 1       | 1 |

| l <sub>is</sub> >[ <sub>sux</sub>                   | LOw            | нісн           | 0       | 0 |

(b)동작표

그림 1. 디지털 출력이 가능한 전류 센서 Fig. 1. Current sensor with digital output

# 2.2 Time Slot Specification와 Modified Time Slot Specification 테스트 기법

전류감지기를 사용한 테스팅은 간단하면서도 구조적 테스트 용이화 설계에 적합하지만 고장 종류와 위치를 찾아내는 능력은 매우 제한되어 있다. 여기서 사용하는 전류 테스팅은 기본적으로 내장 전류감지에 의해 감지된 전류의 크기에 의

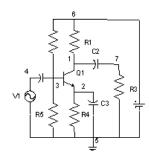

존하는 방식이므로 피테스트 회로의 아날로그 신호 변화를 세밀히 측정하는 것이 쉽지 않다. 사양기반 의(specification-based) 기술은 고장의 종류에 따 른 다양한 고장 신호를 검출하기 위해서는 결함에 기인한 신호 변화를 구별해 내는데 유용하다. 구체 적인 방법으로서 다음에 기술하는 Time Slot Specification(TSS)기법과 Modified TSS(MTSS) 기법이 제안된바 있다[6,7]. 테스트 구간을 적절한 시간 구간(time slot)으로 분할 한 후 각 시간 구간 에서의 INSPEC과 OFFSPEC 상태(표 1에서 각각 I 와 O로 표시)를 판정한 뒤 이를 정상신호와 그것 과 비교하여 고장유무를 판별한다. 시간구간을 적용 하여 측정한 신호들은 고유한 패턴으로 나타나므 로 이를 통해 고장의 위치와 함께 고장의 종류도 판별할 수 있게 된다. 시뮬레이션 결과 테스트 노드 에서 단락고장(Class A), 개방고장(Class B), +6 sigma 고장(Class C) 그리고 -6 sigma 고장(Class D)들이 각기 고유한 패턴을 나타내었다. 표 1은 그 림 2의 회로내 노드 6에서 흐르는 전류값을 MTSS기법으로 측정한 결과이다(이 예제의 경우 는 TSS 기법으로 측정하여도 동일한 결과를 얻음).

그림 2. 벤치마크 회로(1-stage amp.)

Fig. 2. Benchmark circuit(1-stage amp.)

표 1 . 노드 6에서 측정한 MTSS 신호 패턴 Table 1. MTSS signal patterns at node 6

| Time slot<br>Fault Type | А | В | С | D | Е | F |

|-------------------------|---|---|---|---|---|---|

| Fault Free              | I | I | I | I | I | I |

| class A                 | 0 | 0 | 0 | 0 | 0 | 0 |

| class B                 | О | 0 | 0 | 0 | 0 | О |

| class C                 | О | 0 | I | I | 0 | О |

| class D                 | I | 0 | 0 | 0 | 0 | I |

아날로그 회로의 내부 노드와 출력은 강고장이나 약고장이 발생할 때 비록 그 노드가 가질 수 있는 최대값과 최소값 범위내에 있으면서도 정상값을 갖지 못할 수 있다. 이러한 고장들은 TSS 기법으로도 충분히 검출해 낼 수 없어 높은 고장 검출율을얻기 어렵다. 이러한 문제를 해결하기 위해 수정된 TSS방식이 제안되었다[6]. 기존의 방식에서

감지구간으로 사용하고 있는 최소전류 (Imin)와 최대전류(Imax)를 크기가 다음으로 큰 전류값들로 대치하여 TSS 패턴을 구한다. 이 방법을 사용하면 TSS 방법으로 테스트를 할 때 시간분할 구간 내에서 완전-INSPEC인 고장이 부분-INSPEC으로 나타나 검출이 가능할 뿐만 아니라 고유한 고장 패턴을 나타내게 된다.

#### 3. 난고장의 테스트

#### 3.1 난고장 검출에서의 문제점

TSS 방식을 피테스트 회로에 적용할 때 두가지 테스트의 어려움이 존재한다. 일반적으로 약고장은 강고장에 비해서 고장 전달효과가 적어 거의 정상신호의 패턴과 거의 흡사한 경향이 많아서 고장의 검출이나 진단이 용이하지 않다.

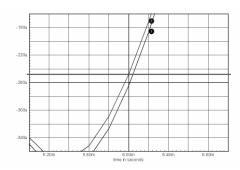

그림 3. MTSS에 의해 지연고장 형태로 검출된 1단 증폭기내 약고장

Fig. 3. A parametric fault detected as a delay fault in 1-stage amp by MTSS

그런데 MTSS(Modified Time Slot Specification) 기법을 적용하면 이러한 약고장들이 그림 3과 같이 일부 지연고장 형태로 검출되어 고 장 검출율과 고장 진단율이 향상된다[7]. 1단 증폭기의 C3 소자의 -6-sigma고장이 노드 6 테스트

포인트에서 지연고장의 형태로 검출되는 것을 확인할 수 있다. 파형 (1)은 고장 신호를 파형 (2)는 정상 신호를 나타내며 약 0.12ms의 지연을 보이고 있다. 그런데 비록 MTSS기법이 일부 난고장을 지연고장의 형태로 검출하여 고장 검출율과 고장 진단율을 향상시키기는 하지만 다양한 고장들에 대해 만족할 만한 고장 검출율과 고장 진단율을 보이지 못하고 있어 이에 대한 개선이 필요하다.

#### 3.2 제안하는 고장 진단율 향상 기법

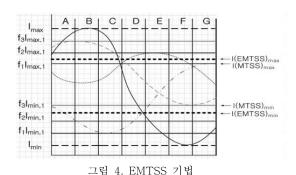

고장에 대한 테스트용이도를 항상시키기 위해서는 고장 유무뿐만 아니라 고장의 위치를 파악하는 것이 필요하다. 기존의 연구[6,7]에서 제안한 MTSS 기법을 사용하였을 때 각 고장의 TSS신호 패턴이 고유한 형태로 나타날 확률은 12%에서 최대 36%정도로 나타났다. 고장에 대한 TSS 신호패턴이 고유하게 나타날 확률을 항상시키면 고장 진단율 또한 향상되는데 이는 기존의 MTSS 기법을 확장하여 적용하므로써 가능하다. 그림 4에 나타낸 것처럼 MTSS기법에서 사용하는 I(MTSS)min과 I(MTSS)max를 Imax와 Imin를 벗어나지 않는 범위내에서 일정한 크기를 이동한 값으로 대치하여 TSS 패턴을 구하는 것이다.

그림 5(a)에서 I(MTSS)min과 I(MTSS)max을 사용하여 구한 신호 패턴에서는 고장 1과 고장 3이동일한 패턴으로서 구별이 불가능 하지만 전류경계값을 I(EMTSS)min및 I(EMTSS)max의 위치로 이동하였을 때 신호패턴이 그림 5(b)와 같이 서로 다른 TSS 신호패턴을 보여 고장 1과 고장 3이 구별된다.

Fig. 4. Extended MTSS technique

MTSS 기법을 사용할 때 피테스트 회로의 종류 나 특성에 따라 적합한 Imax와 Imin의 값을 임의로 자유롭게 설정할 수 있는 것이 제안하는 테스트 기 법의 최대 강점이다. 이렇게 하므로써 MTSS 패턴들의 고유성(uniqueness)을 높일 수 있고 나아가고장 진단율 또한 향상시킬 수 있게 된다.

|      | А | В | С | D | Е | F | G |

|------|---|---|---|---|---|---|---|

| 무고장  | О | 0 | Ι | I | О | 0 | 0 |

| 고장 1 | О | О | 0 | I | I | Ι | I |

| 고장 2 | I | I | I | 0 | О | I | I |

| 고장 3 | О | О | 0 | I | I | Ι | I |

(a)기존 MTSS 패턴

|      | А | В | С | D | Е | F | G |

|------|---|---|---|---|---|---|---|

| 무고장  | О | О | I | I | О | О | 0 |

| 고장 1 | I | О | 0 | I | I | Ι | I |

| 고장 2 | I | I | I | I | О | Ι | Ι |

| 고장 3 | О | О | 0 | I | I | Ι | Ι |

(b)확장 MTSS 개념을 적용하여 구한 패턴

그림 5. MTSS와 EMTSS를 적용하여 구한 패턴들 Fig. 5. Signal patterns obtained by MTSS and EMTSS

#### 4. 외부테스트 포인트를 이용한 진단 구조

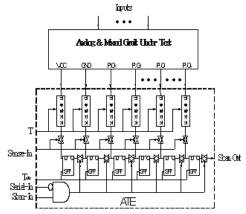

그림 6은 전류감지기를 자동테스트장치(Automatic Test Equipment : ATE)에 내장시키고 피테 스트 회로의 외부 단자를 테스트 포인트로 사용하여 고장검출과 진단을 행하는 테스트 구조이다.

먼저 테스트 입력이 ATE에 의해 피 테스트 회로에 인가되고 static 플립플롭들이 LOW로 리셋된다. 이 때 Tclk 신호를 HIGH로, Scan-In 신호를 LOW로 주면 레지스터 체인이 비활성화 된다. 다시 Sense-In 신호를 HIGH로 하면 전류감지기의 출력이 static 플립플롭의 입력으로 인가되면서 테스트가 본격적으로 이루어진다. 선 테스트(pre-test) 단계에서는 최초 또는 희망하는 time slot이 끝날 때 Tclk 신호가 동작한다. 전류감지기에 의해 INSPEC / OFFSPEC이 정해지고 그 값이 플립플롭에 래치된다. 플립플롭 체인으로 구성된 LIFO내에 저장된내용이 스캔 출력되고 플립플롭이 리셋된 뒤 다시다음 time slot에서 같은 테스트 과정을 반복하게된다.

그림 6. 집적회로의 외부노드(테스트 포인트)를 이용한 고장진단 구조

Fig. 6. Fault diagnosis structure using external test node(points) of integrated chip

#### 5. 테스트 포인트 선택

아날로그 회로를 테스트할 때 피 테스트 회로내 고장들에 대해 최대 진단율을 얻을 수 있는 최적의 테스트 포인트 집합을 선택하는 것은 매우 중요한 일이다. 일반적으로 테스트 포인트를 결정하는 과 정은 먼저 진단 가능한 고장을 확인하기 위해 고장 시뮬레이션을 행하고 최대 검출율과 진단율을 구해 내는 것이다.

실제로 고장 시뮬레이션을 행하기 전에 아날로 그 회로내 테스트 포인트를 찾는 것은 쉽지 않은 일이다. 여기서 제안하는 방법은 휴리스틱 조건에따라 테스트 포인트(circuit branch)를 선택한 다음 시뮬레이션을 행하는 것이다.

테스트 포인트를 선택하는 휴리스틱(heuristic) 조건들은 다음과 같다.

- (1)회로의 대칭성 미분회로나 멀티 바이브레이터 등과 같이 대칭구조를 이루고 있는 회로들은 테 스트 포인트 선택 시 대칭의 한쪽 부분만을 고려 한다.

- (2)테스트 모드에서 전류 변화가 큰 가지(branch)를 선택한다.

- (3)전원이 공급되는 가지는 큰 전류변화가 가능한 곳이다.

- (4)고장 소자 인근 가지는 보통 다른 곳보다 전류 변화가 클 가능성이 있다.

(5)능동 소자의 바이어스 회로 내 소자 고장은 큰 전류변화를 야기할 가능성이 높다.

이상의 휴리스틱 조건들을 충분히 이용하여 테 스트 포인트를 선택한 후 그 가운데 최소 갯수의 테스트 포인트를 선택하는 과정이 필요하다.

표 2는 테스트 포인트로 선택된 가지 1, 가지 2, 가지 3에서 검출되는 고장들을 나타낸 것이다. 고장 A, 고장 B, 고장 C를 모두 검출하기 위하여 테스트 포인트로서 선택은 가지 1과 가지 2 두 개를 테스트 포인트로 선택하는 것이다. 다른 가지의 조합 즉 가지 1과 가지 3 또는 가지 2와 가지3등의 조합으로는 모든 고장을 검출할 수 없다.

표 2. 최소의 테스트 포인트 선택의 예 Table 2. Example for selection of minimal test points

| 테스트<br>포인트<br>고장 | 가지<br>1 | 가지<br>2 | 가지<br>3 |

|------------------|---------|---------|---------|

| А                | 진단      | 진단      | 진단      |

| A                | 가능      | 가능      | 가능      |

| В                | 진단      | 검출      | 검출      |

| D                | 가능      | 안됨      | 안됨      |

| C                | 검출      | 진단      | 검출      |

| C                | 안됨      | 가능      | 안됨      |

#### 6. 실험 결과

제안하는 확장 TSS기법이 난고장 검출과 진단에 유효한가를 확인하기 위하여 밴치마크 회로를 이용하여 실험하였다[8]. 표 3은 확장 TSS기법으로 구한 벤치마크 회로 대한 고장 검출율과 고장 진단율을 나타낸 것이다.

비교기에서는 주출력에서 100%의 고장 검출율을 얻었고 고장 진단율은 66%를 얻어 기존 방식[5]에 비해 크게 향상됨을 알 수 있다. 상태가변필터 역시 100%와 59%의 고장 검출율과 고장 진단율을 얻었고 미분증폭기의 경우 100%와 50%, 단안정 멀티바이브레이터의 경우는 100%와 77%의고장 검출율과 고장 진단율을 얻었으며, Op-amp의경우 98%와 49%의 고장 검출율과 고장 진단율을 얻어 기존 방식의 87%와 5%에 비해 크게 개선된

결과를 얻을 수 있었다. 약고장의 경우 고장 진단율은 강고장에 비해 다소 떨어지지만 이전의 MTSS 방식을 적용한 것에 비해 크게 향상되었다. 각 피테스트 회로에 대한 실험 결과를 분석해 보았을 때기본 방법에서와 마찬가지로 약고장에 대해서는 주출력보다 전원단자에서 높은 진단율을 얻을 수 있었고 반면 강고장에 대해서는 주출력 쪽이 전원단자보다 높은 진단율이 얻어짐을 알 수 있었다.

표 3. 벤치마크 회로 대한 기존의 방식[7]과 제안하는 방식의 EMTSS에 의한 고장 검출율과 진단율(주출력에서 측정) 비교

Table 3. Comparison of fault detection and diagnosis rates between conventional technique[7] and proposed technique on benchmarks by extended MTSS technique(patterns are sensed at PO)

|    |         | 고장 검출율(%) |          |     |     |     |         |    | 고장 진단율(%) |         |      |         |  |

|----|---------|-----------|----------|-----|-----|-----|---------|----|-----------|---------|------|---------|--|

|    | 강고장     |           | 고장 약고장 합 |     | 강고장 |     | 약고장     |    | 합         |         |      |         |  |

|    | A<br>방식 |           | A<br>방식  |     |     |     | A<br>방식 |    | A<br>방식   | B<br>방식 | l    | B<br>방식 |  |

| C1 | 100     | 100       | 100      | 100 | 100 | 100 | 22.9    | 76 | 20.2      | 56      | 21.0 | 66      |  |

| C2 | 100     | 100       | 100      | 100 | 100 | 100 | 16.7    | 73 | 5.6       | 45      | 11.1 | 59      |  |

| СЗ | 100     | 100       | 100      | 100 | 100 | 100 | 0       | 37 | 31.3      | 68      | 13.6 | 49      |  |

| C4 | 100     | 100       | 98       | 98  | 99  | 99  | 26.7    | 56 | 18.4      | 45      | 21.4 | 50      |  |

| C5 | 100     | 100       | 100      | 100 | 100 | 100 | 31.2    | 82 | 28.6      | 62      | 30.3 | 77      |  |

(C1:비교기, C2:State Variable Filter, C3:1-stage amp, C4:미분증폭기, C5:단안정 멀티바이 브레이터, A방식:기존방식[7], B방식:제안하는 방식)

#### 7. 결 론

본 논문에서는 아날로그 회로뿐만 아니라 혼합 신호 회로의 테스트에 효과적으로 적용할 수 있는 사양기반(specification-based)의 테스트 기법을 제 시하였다. 저자가 제안한바 있는 고성능 전류감지기를 사용하는 기존 MTSS기법을 확장한 EMTSS방법을 사용하면 검출율과 특히 진단율을 높일 수 있음을 보였고 DFT (design for testability) 방식에서 문제가 되는 하드웨어 오버헤드를 최소화 하기위한 방법으로서 ATE에 부가회로를 수용하는 진단구조에 대해 기술하였다. 제안한 방법은 기존 방식에 비해 높은 고장 검출율과 진단율을 갖으며 강고장과 약고장 모두에 대해서 효과임을 알 수 있다. 경계주사 기법에 응용할 경우 SOC (Systemon-a-Chip)의 혼합신호 회로테스트에 효과적으로적용할 수 있을 것이다.

#### 참고문헌

- [1] Jhihong You, E. Sanchez-Sinencio, Jose Pineda deGyvez, "Analog system-Level fault diagnosis based on a symbolic method in the frequency domain", IEEE Trans. Instrum. and Meas., Vol. 44, No. 1, Feb. 1995.

- [2] E. L. Salama, and F. Z. Amer, "Parameter identification approach to fault diagnosis of switched capacitor circuits", IEE Proc. Electron Trans. Cir. and Syst., Vol. 139, pp.467-472, Feb. 1991.

- [3] Linda S. Milor, "A tutorial introduction to research on analog and mixed-signal circuit testing", IEEE Trans. Cir. and Syst., Vol. 45, No.10, pp.1389-1407, October 1998.

- [4] M. Aminian and F. Aminian, "A comprehensive examination of neural network architectures for analog fault diagnosis", Proceeding of International Joint Conference on Neural Networks, Vol. 3, pp. 2304–2309, 2001.

- [5] Jun-Weir Lin, Chung-Len Lee, Chau-Chin Su and Jwu-E Chen, "Fault diagnosis for linear analog circuits", Proceedings of the Ninth Asian Test Symposium, 2000. (ATS 2000), pp.25-30, 2000.

- [6] J. M. Lee, et al, "Time Slot Specification Based Approach to Analog Fault Diagnosis using Built-In Current Sensors and Test Point Insertion", Proceedings of ATS02, pp.1167-1170, Oct. 2002.

- [7] J. M. Lee, "Specification-based Analog and Mixed-signal Circuits Test with Minimal Built-In Hardware Overhead", Proceedings of KIERE Summer Conference, pp.633-636, June 2006.

- [8] J. M. Lee, "Specification-based Analog and Mixed-signal Circuits Test with Minimal Built-In Hardware Overhead", Proceedings of KIERE Summer Conference, pp.633-636, June 2006.

#### 저 자 소 개

#### 이 재 민(Jae-Min Lee)

1979년 한양대 전자공학 과 학사. 1981년 한양대 전자공학 과 석사. 1987년 한양대 전자공학

1990년-1991년 University of Illinois at Urbana- Champaign Beckman Institute 연구원.

과 박사.

현재, 관동대학교 전자정보통신공학부 교수. 관심분야: SoC 설계 및 테스트, 임베디드 시스템 응용, 신재생에너지시스템

Email: leejm@kd.ac.kr