**JPE 9-6-9**

# Digital Control of a Power Factor Correction Boost Rectifier Using Diode Current Sensing Technique

Jong-Won Shin<sup>†</sup>, Byeong-Cheol Hyeon<sup>\*</sup>, and Bo-Hyung Cho<sup>\*</sup>

†\*Department of Electrical Engineering, Seoul National University, Seoul, Korea

#### **ABSTRACT**

In this paper, a digital average current mode control using diode current sensing technique is proposed. Although the conventional inductor current sensing technique is widely used, the sensed signal of the current is negative. As a result, it requires an additional circuit to be applied to general digital controller ICs. The proposed diode current sensing method not only minimizes the peripheral circuit around the digital IC but also consumes less power to sense current information than the inductor current sensing method. The feasibility of the proposed technique is verified by experiments using a 500W power factor correction (PFC) boost rectifier.

**Keywords:** Digital control, Average current mode control, Diode current, Power factor correction

#### 1. Introduction

Digital control of switching power converters has been an emerging issue recently. The many advantages of digital control such as robustness to aging and environmental change, noise immunity, ease of reprogramming and intelligent control are well known to power supply designers <sup>[1-3]</sup>. The decreasing cost of digital ICs is reinforcing digital control as a more powerful candidate in switching power supply design.

Various researches on current mode control of boost rectifiers employing a digital controller have been reported. References [4] and [5] propose the direct duty cycle calculation method for valley current mode control. They

This paper proposes a diode current sensing technique that can obtain average current information. The proposed current sensing method simplifies the peripheral circuit of

sample the minimum inductor current in one switching cycle. However, the sampled current information at the switch turn-on or turn-off instant may not be accurate

because of switching noise, which may cause the controller to become unstable. Furthermore, controlling

the peak or valley of the inductor current hardly shows

better performance than controlling the average of the inductor current from the viewpoint of harmonic distortion

A sampling technique which can sense the average

current of the inductor while minimizing the effect of

switching noise is proposed in [7]. The sampling instant of

the inductor current varies between the switch conduction

and power factor [6].

interval and the diode conduction interval to minimize the noise in current waveform.

Manuscript received Aug. 17, 2009; revised Sept. 24, 2009

<sup>&</sup>lt;sup>†</sup>Corresponding Author: nf84@snu.ac.kr

Tel: +82-880-1785, Fax: +82-878-1452, Seoul National Univ.

<sup>\*</sup>Dept. of Electrical Eng., Seoul National Univ., Korea

the digital IC by generating a positive voltage signal and reducing the power consumption in the sensing resistor.

In Section 2, a circuit structure using the proposed sensing technique will be shown and compared with the conventional inductor current sensing technique. The selection of sampling instant in the switching period and the power consumption in current sensing will also be analyzed. Experimental results to verify the analysis in Section 2 will be provided in Section 3.

# 2. Proposed Diode Current Sensing Technique

#### 2.1 Circuit Structure

Various current sensing methods exist in switching power converter designs. The resistive current sensing scheme, which obtains the current information from the voltage across a series resistor in the current path, is widely used due to its simplicity and cost effectiveness.

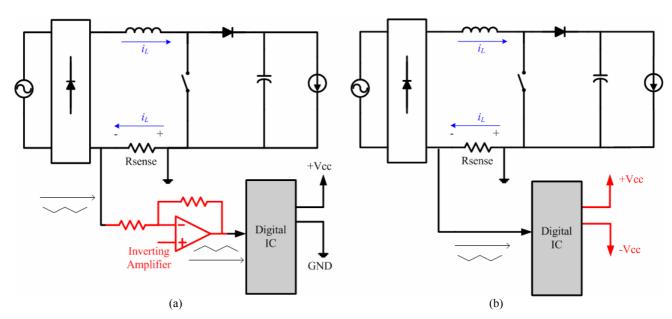

Conventional current sensing circuits in a boost rectifier are shown in Fig. 1. The gate driver and the output voltage sensing circuit are omitted for simplicity in Figs. 1 and 2. The sensing resistor, Rsense, is located in the inductor current path and generates current information in the form of negative voltage. However, this negative voltage cannot

be directly used by a digital controller IC.

The maximum and minimum analog input signal of an analog-to-digital (A/D) converter is determined by the external bias voltage of the IC. If the IC is biased by a certain positive voltage and ground, i.e. +3.3V and 0V, the IC cannot recognize the negative voltage information.

One way to solve this problem is by using an external inverting amplifier to change the sign of the sensed signal as in Fig. 1(a). It should be noted that the bandwidth and the gain characteristic of an analog operational amplifier must be considered in designing a current control loop.

Biasing the digital IC with both positive and negative voltage, i.e. +3.3V and -3.3V, can be the other solution to receiving negative voltage as the input of an A/D converter as in Fig. 1(b). Although it eliminates the external analog amplifier, the need for an additional negative voltage source in the auxiliary power converter and the low resolution of the A/D converter are the major drawbacks of this scheme.

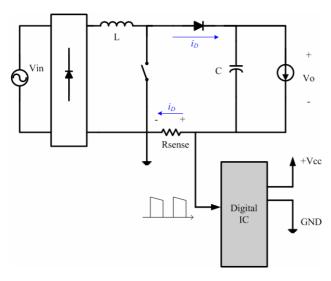

The circuit structure of a boost converter using the proposed sensing method is shown in Fig. 2. The sensed signal which contains the diode current information is positive. Therefore the proposed sensing circuit has a simple structure because it is freed of an external amplifier and negative bias voltage. The effect of the sensing resistor on the output voltage is negligible because the

Fig. 1. Conventional circuits with inductor current sensing using (a) an external amplifier and (b) biasing by both positive and negative voltage.

Fig. 2. Boost rectifier with the proposed diode sensing scheme.

voltage across the Rsense is very small with respect to the output voltage ripple.

# 2.2 Sampling Time for Average Current Mode Control

Average current mode control is preferred in PFC applications because of its good performance such as high power factor and low THD (Total Harmonic Distortion) [6]. Comparing the sampled inductor current information and the current reference determines the current control mode of the converter in the digital control design. The one sample per switching cycle sampling method is widely used due to the low calculation burden in low-to-medium performance digital ICs. Therefore, when

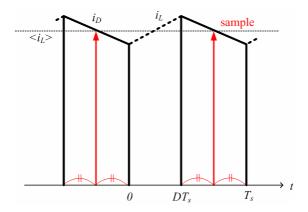

Fig. 3. Sampling time in the proposed current sensing technique.

contrasted with the analog current mode control, the digital controller cannot recognize the overall trajectory of a current waveform in one switching period. Thus selecting the current sampling instant directly determines the mode of current control.

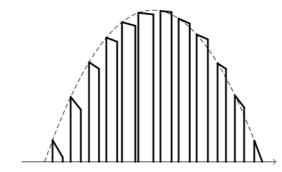

Acquiring the average current information from the diode current is easier in digital control than in analog control. The time domain in Fig. 3 shows the diode current waveform and the sampling time to gain the average current information in the proposed sensing technique.  $T_s$ , D,  $i_L$ ,  $i_D$ , and  $\langle i_L \rangle$  are the switching period, duty ratio, inductor current, diode current and average inductor current respectively. Assuming the two consecutive turn-on times of the switch are zero and  $T_s$  respectively, the sampling action must occur at:

$$T_{sample} = \left\{ D + \frac{1}{2} (1 - D) \right\} T_s , \qquad (1)$$

where the middle of the diode conducting interval achieves the average inductor current.

In PFC applications, however, D keeps changing in the entire line period according to the rectified line voltage variation. Especially in the case where the line voltage approaches zero, D is almost unity and the diode conduction time becomes extremely short. Then sampling accurate current information can not be guaranteed

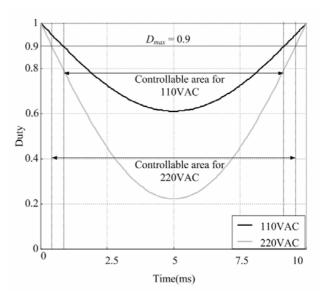

Fig. 4. Controllable area when the maximum duty cycle is limited.

Fig. 5. Estimated power loss in sensing resistor.

because of the turn-off noise of the switch. Limiting the maximum duty cycle helps to avoid noisy sensing by securing the minimum diode conduction time though the controllable area slightly shrinks. Fig. 4 shows the controllable area when the maximum D is limited to 0.9 in a 50Hz line frequency situation. Higher line voltage acquires a wider controllable area.

# 2.3 Power Consumption in Sensing Resistor

The inductor current sensing method is generally used to obtain current information. When a series resistor is used as a current sensor, which is widely used in industrial fields, the inductor current sensing scheme consumes

Table 1. Circuit parameters of prototype rectifier shown in Fig. 2.

| Parameter            | Value            |

|----------------------|------------------|

| Vin                  | 110VAC           |

| Line Frequency       | 50Hz             |

| Vo                   | 400VDC           |

| Maximum Output Power | 500W             |

| Maximum Duty Ratio   | 0.9              |

| Switching Frequency  | 65kHz            |

| Controller IC        | dsPIC33FJ16GS502 |

| L                    | 570uH            |

| С                    | 660uF            |

| Rsense               | 50m Ω            |

more power than the proposed diode current sensing. The power loss in a series resistor may be trivial in medium or full load operations, but it may dominate the loss in a light load condition or in standby mode operation.

RMS currents in the inductor, switch and diode should be calculated first to estimate the power losses in a sensing resistor. Assuming that  $I_{S,rms}$ ,  $I_{D,rms}$ , and  $I_{L,rms}$  are the RMS currents of the switch, diode and inductor respectively, their relationship is as following:

$$I_{S,rms} = I_{L,rms} \sqrt{1 - \frac{8}{3\pi} \frac{\sqrt{2}v_{in}}{v_o}},$$

(2)

$$I_{D,rms} = I_{L,rms} \sqrt{\frac{8}{3\pi} \frac{\sqrt{2}v_{in}}{v_o}},$$

(3)

$$I_{L,rms} = \frac{P_o}{\eta v_{in}} = \frac{v_{in}}{R_{in}},$$

(4)

where  $v_{in}$ ,  $v_o$ ,  $P_o$ ,  $\eta$ , and  $R_{in}$  are the RMS value of the line voltage, the output voltage, the output power, rectifier efficiency and emulated input resistance of the rectifier respectively. A detailed derivation of (2)-(3) is presented in the Appendix.

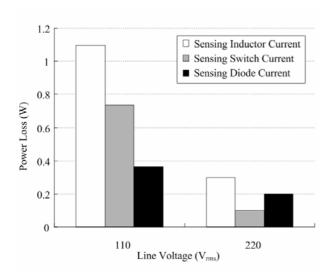

The calculated power consumption in a  $50m\Omega$  sensing resistor in a 400V output voltage and 500W output power situation based on (2)-(4) is illustrated in Fig. 5. The efficiencies for a 110VAC and a 220VAC are considered to be 93% and 97% respectively which are the

Fig. 6. The current sampling instant of the proposed sensing technique (5us/div).

Fig. 7. (a) Input current and input voltage in 80% load or 400W operation (5A/div, 75V/div, 5ms/div).

(b) Harmonic component measurement results of the proposed diode current sensing method and the conventional inductor current sensing method.

(c) THD of the conventional and the proposed diode current sensing method and the conventional inductor current sensing method.

Fig. 8. Converter operation in step load change situation (input current 5A/div, 100V/div, output current 1A/div, 50ms/div).

experimentally measured values of the prototype hardware. The proposed sensing technique consumes less power than the conventional inductor current sensing technique. This is obvious because the sensing resistor in the diode current sensing method carries a smaller RMS current than in the inductor current sensing method. The difference in power loss between the two schemes becomes severe when the input voltage is lower and the duty ratio is larger. According to Fig. 5, the proposed diode current sensing technique outperforms not only the inductor current sensing method but also the switch current sensing method under low line voltage circumstances.

## 3. Experimental Results

To verify the feasibility of the proposed diode current sensing technique, a 500W boost rectifier employing the proposed method is implemented as in Fig. 2. The circuit parameters of the hardware are shown in Table I. The Rsense in the prototype rectifier is selected to be  $50 \mathrm{m}\Omega$  to minimize the power loss while acquiring a sufficient signal-to-noise ratio. DC/DC converter operation employing the proposed sensing technique is verified in [8].

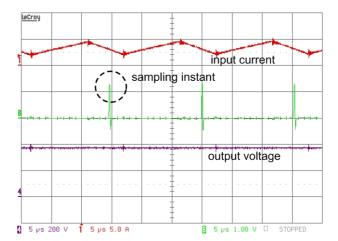

The operation of the rectifier is shown in Fig. 6. The top and bottom traces are the input or inductor current and the output voltage respectively. The middle trace represents

the A/D conversion triggering signal of the digital controller IC. It latches up when the A/D converter of the digital IC is enabled. It is confirmed that the current signal is sampled in the midpoint of the diode conducting interval as shown in Fig. 3.

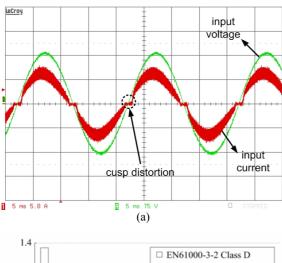

Fig. 7(a) illustrates the rectifier operation under 80% load or 400W operation. Cusp distortions are observed when the line voltage crosses the zero volt line. This is due to a limitation of the maximum duty cycle to guarantee the minimum diode conduction time and accurate current information as explained in Section 2.2. The power factor is measured to be 0.983.

The harmonic components of the input current are shown in Fig. 7(b). White bars are the harmonic regulations in EN61000-3-2 Class D equipments. Gray and black bars represent the harmonics of the conventional inductor current sensing scheme and the proposed diode current sensing scheme respectively. The data in Fig. 7(b) are collected under the same experimental circumstances. 110VAC 50Hz line voltage and 400W output power, except for the maximum duty cycle limitation. For the inductor current sensing method, a relatively sufficient maximum duty of 98% is applied because there is no need to maintain the minimum diode conduction interval. It can be confirmed that the proposed diode current sensing method as well as the conventional inductor current sensing method meets the regulations of EN61000-3-2. It should be noted that the data in Fig. 7(b) is observed without the EMI filter.

The THDs based on the harmonic data shown in Fig. 7(b) are in Fig. 7(c). The proposed method does not outperform the conventional method from the viewpoint of THD because the maximum duty ratio limitation induces a distortion in the input current waveform. However, if a proper noise filter is added between the current sensing resister and the digital IC to attenuate the turn-off noise, the maximum duty cycle limit can be increased and the THD can be improved.

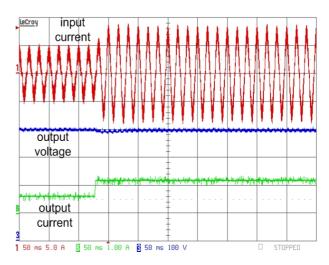

Fig. 8 shows rectifier operation when the load current steps from 0.625A (50% load, 250W output power) to 1.25A (100% load, 500W output power). Top, middle, and bottom traces show the input current, output voltage and output current respectively. RMS inductor current increases and output voltage is controlled to maintain

400V as the load changes. The rectifier is confirmed to be stable with the proposed diode current sensing technique.

#### 4. Conclusions

A diode current sensing technique for digital average current mode control of a PFC boost rectifier has been proposed and analyzed. The proposed method simplifies the additional circuit structure of a digital controller IC. Also, the proposed diode current sensing method consumes less power in resistive sensing than the inductor current sensing method. The feasibility and performance of the proposed technique have been verified by experimental results with a 500W boost rectifier.

# **Appendix**

The derivation of (2) is presented in [9]. In this paper, (3) is solved in detail by a process similar to the one shown in [9].

The RMS value of the diode current over a line period is:

$$I_{D,rms} = \sqrt{\frac{1}{T_{line}}} \int_{0}^{T_{line}} i_{D}^{2}(t)dt$$

(a1)

where  $T_{line}$  is the line voltage period and  $i_D(t)$  is the instantaneous diode current. Because the diode current is not continuous in the line period but partially scattered in each switching period as in Fig. 9, the integral in (a1) is equivalent to the sum of the integrals in every switching period as in (a2):

$$I_{D,rms} = \sqrt{\frac{1}{T_{line}}} \sum_{n=1}^{\frac{T_{line}}{T_{*}}} \int_{0}^{T_{line}} i_{D}^{2}(t)dt$$

$$= \sqrt{\frac{1}{T_{line}}} T_{s} \sum_{n=1}^{\frac{T_{line}}{T_{*}}} \frac{1}{T_{s}} \int_{0}^{T_{line}} i_{D}^{2}(t)dt . \tag{a2}$$

Generally  $T_s$  is much smaller than  $T_{line}$ . The approximation in (a3) is as:

$$I_{D,rms} \cong \sqrt{\frac{1}{T_{line}} \lim_{T_s \to 0}} \left[ T_s \sum_{n=1}^{\frac{T_{line}}{T_s}} \frac{1}{T_s} \int_0^{T_{line}} i_D^2(t) dt \right]$$

$$= \sqrt{\frac{1}{T_{line}}} \int_0^{T_{line}} \left[ \frac{1}{T_s} \int_t^{t+T_s} i_D^2(t') dt' \right] dt . \tag{a3}$$

The term in the bracket in (a3), the square of the RMS diode current over one switching period, should be derived first to achieve  $I_{D,rms}$ . It can be re-expressed in (a4) as:

$$\frac{1}{T} \int_{t}^{t+T_s} i_D^2(t') dt' = (1 - d(t)) i_L^2(t) , \qquad (a4)$$

$$1 - d(t) = \frac{v_{pk}}{v_o} \sin(\omega t), \qquad (a5)$$

$$i_L(t) = \frac{v_{pk}}{R_{in}} \left| \sin(\omega t) \right|, \tag{a6}$$

where  $i_L(t)$ ,  $v_{pk}$  and  $\omega$  are the instantaneous inductor current, the peak value of the line voltage and the line frequency in rad/s. Substituting (a5) and (a6) into (a4) yields:

$$\frac{1}{T_s} \int_t^{t+T_s} i_D^2(t') dt' = \frac{v_{pk}^3}{R_{in}^2 v_o} \sin^3 \omega t .$$

(a7)

From (a7) and (a3), (a8) is achieved as follows:

$$I_{D,rms} = \sqrt{\frac{1}{T_{line}} \int_{0}^{T_{line}} \frac{v_{pk}^{3}}{R_{in}^{2} v_{o}} \sin^{3} \omega t dt}$$

(a8)

which can be further simplified and rearranged due to the symmetry of the sine function as (a9).

$$I_{D,rms} = \sqrt{\frac{2}{T_{line}}} \frac{v_{pk}^{3}}{R_{in}^{2} v_{o}} \int_{0}^{T_{line}} \sin^{3} \omega t dt$$

$$= \frac{v_{pk}}{R_{in}} \sqrt{\frac{2v_{pk}}{T_{line} v_{o}}} \int_{0}^{T_{line}} \sin^{3} \omega t dt$$

(a9)

Fig. 9. Typical diode current waveform in a half of line frequency. Switching period is exaggerated with respect to the line period.

Replacing the  $\omega t$  term in (a9) into  $\tau$  yields:

$$I_{D,rms} = \frac{v_{pk}}{R_{in}} \sqrt{\frac{2v_{pk}}{T_{line}v_o}} \int_0^{\pi} \sin^3 \tau d\tau \frac{dt}{d\tau}$$

$$= \frac{v_{pk}}{R_{in}} \sqrt{\frac{2v_{pk}}{T_{line}v_o}} \frac{1}{\omega} \int_0^{\pi} \sin^3 \tau d\tau$$

$$= \frac{v_{pk}}{R_{in}} \sqrt{\frac{2v_{pk}}{T_{line}v_o}} \frac{T_{line}}{2\pi} \int_0^{\pi} \sin^3 \tau d\tau . \tag{a10}$$

From the fact that  $\frac{1}{\pi} \int_0^{\pi} \sin^3 \theta d\theta = \frac{4}{3\pi}$ , (a10) can be rearranged as:

$$I_{D,rms} = \frac{v_{pk}}{R_{in}} \sqrt{\frac{v_{pk}}{v_o}} \frac{4}{3\pi} = \frac{v_{pk}}{\sqrt{2}R_{in}} \sqrt{\frac{v_{pk}}{v_o}} \frac{8}{3\pi}$$

$$= \frac{v_{in}}{R_{in}} \sqrt{\frac{v_{pk}}{v_o}} \frac{8}{3\pi}$$

(a11)

which is same as (3).

#### References

- [1] Yan-Fei Liu, et. al., "Recent Developments in Digital Control Technologies for DC-DC Switching Power Converters," in Proceeding of International Power Electronics and Motion Control Conference ECCE Asia, pp. 307-314, May 2009.

- [2] Maged N.F. Nashed, "Design of a Digital PWM Controller for a Soft Switching SEPIC Converter," *Journal of Power Electronics*, Vol. 4, No. 3, pp. 152-160, July 2004.

- [3] Jeong-Gyu Lim, et. al., "Digital Control of Phase-Shifted Full-Bridge PWM Converter," *Journal of Power Electronics*, Vol. 8, No. 3, pp. 201-209, July 2008.

- [4] Wangfeng Zhang, et al., "A direct duty cycle calculation algorithm for digital power factor correction (PFC) implementation," in Proceeding of Power Electronics Specialists Conference, pp. 2326-2332, June 2004.

- [5] Wangfeng Zhang, et al., "A digital Power Factor Correction(PFC) Control Strategy Optimized for DSP," *IEEE Trans. Power Electronics*, Vol. 19, No. 6, pp. 1474-1485, Nov. 2004.

- [6] L. Rosetto, et. al., "Control Techniques for Power Factor Correction Converters," in Proceeding of International Power Electronic and Motion Control Conference, 1994.

- [7] David M. Van de Sype, et. al., "A sampling algorithm for digitally controlled boost PFC converters," *IEEE Trans. Power Electronics*, Vol. 19, No. 3, pp.649-657, May 2004.

- [8] Jong-Won Shin, et. al., "Digital Average Current Mode Control of Boost Converter Using Diode Current Sensing Technique," in Proceeding of Power Electronics Annual Conference, KIPE, pp.305-307, July 2009.

- [9] Robert. W. Erickson and D. Maksimovic, "Fundamentals of Power Electronics," 2nd Edition, Kluwer Academic Publishers, 2001.

Jong-Won Shin was born in Korea in 1984. He received a B.S. degree from Seoul National University (SNU), Seoul, Korea in 2006, where he is currently working toward his Ph.D. in the School of Electrical Engineering. His research interests are in the

areas of high-efficiency power converters, battery balancing, power factor correction circuits and their control. Mr. Shin is a Student Member of IEEE and the Korean Institute of Power Electronics (KIPE).

Byeong-Cheol Hyeon received a B.S. degree in electrical engineering from KyungPook National University (KNU), Daegu, Korea, in 2004 and a M.S. degree from Seoul National University (SNU), Seoul, Korea, in 2006 where he is currently pursuing a Ph.D.

His interests include resonant converters, multiple output converters and power factor correction (PFC) circuits. Mr. Hyeon is a Student Member of IEEE and the Korean Institute of Power Electronics (KIPE).

**Bo-Hyung Cho** was born in Korea 1952. He received his B.S. and M.E. degrees in Electrical Engineering from the California Institute of Technology, Pasadena. He received his Ph.D. also in Electrical Engineering, from Virginia Polytechnic

Institute and State University (Virginia Tech), Blacksburg, Virginia. Prior to his research at Virginia Tech, he worked for two years as a technical staff member in the Power Conversion Electronics Department, TRW Defense and Space System Group. He was involved in the design and analysis of spacecraft power processing equipment. From 1982 to 1995, he was a professor in the Department of Electrical Engineering, Virginia Tech, Blacksburg, Virginia. He joined the school of Electrical Engineering, Seoul National University, Seoul, Korea in 1995 and he is presently a professor. His main research interests include power electronics, the modeling, analysis and control of spacecraft power processing equipment, power systems for space stations and space platforms, and distributed power systems. In 1989 Prof. Cho received a Presidential Young Investigator Award from the National Science Foundation. He is a member of Tau Beta Pi.