# 플라즈마 식각공정에서 발생하는 실리콘 게이트 전극의 Notching 현상

# 이원규

강원대학교 화학공학과 (2008년 12월 15일 접수, 2009년 1월 13일 채택)

# Notching Phenomena of Silicon Gate Electrode in Plasma Etching Process

#### Won Gyu Lee

Department of Chemical Engineering, Kangwon National University, Kangwon 200-701, Korea. (Received December 15, 2008; accepted January 13, 2009)

반도체 소자의 실리콘 게이트 전극 식각공정은 산화막에 대한 높은 식각 선택비와 정확한 식각형상 제어 등의 공정요구 조건을 충족시키기 위해 고밀도 플라즈마 식각공정을 사용하나 식각 후 notching이 발생되는 문제점을 보이고 있다. 특이하게 도핑 되지 않은 비정질 실리콘을 게이트 전극 물질로 사용한 경우 발생된 notching의 위치가 가장 외곽에 위치한 게이트 전극선의 바깥쪽에서 주로 발생되는 것이 관찰 되었다. 본 연구에서는 Cl<sub>2</sub>/HBr/O<sub>2</sub>의 식각기체 구성으로 notching 발생이 식각변수들에 따라 받는 경향성을 파악하고, 식각장치 내에서 실리콘 기관에 도달하는 식각 이온들의 진행경로를 분석하였다. 주 원인은 플라즈마 내의 식각 활성종 이온들이 대전효과에 의하여 궤적의 왜곡이 일어나 notching 현상이 발생되는 것으로 파악되었다. 이 결과를 바탕으로 도핑 되지 않은 비정질 실리콘 게이트 식각에서 발생하는 notching의 형성기구를 정성적으로 설명하였다.

HBr and  $O_2$  in  $Cl_2$  gas ambient for the high density plasma gate etching has been used to increase the performance of gate electrode in semiconductor devices. When an un-doped amorphous silicon layer was used for a gate electrode material, the notching profile was observed at the outer sidewall foot of the outermost line. This phenomenon can be explained by the electron shading effect: i.e., electrons are captured at the photoresist sidewall while ions pass through the photoresist sidewall and reach the oxide surface at a narrowly spaced pattern during the over etch step. The potential distribution between gate lines deflects the ions trajectory toward the gate sidewall. In this study, an appropriate mechanism was proposed to explain the occurrence of notching in the gate electrode of un-doped amorphous silicon.

Keywords: notching, ion trajectory, gate, high density plasma, silicon etching

#### 1. 서 론

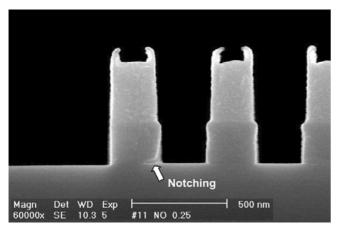

고밀도 플라즈마를 이용한 반도체 소자공정의 실리콘 게이트 전 극 식각 공정은 비등방성 식각특성과 낮은 particle 발생특성 등 우수한 장점[1,2]을 가지고 있으나 식각 후 notching이 발생되는 문제점을 갖고 있다. Notching은 게이트 전극의 하부가 측면 방향으로 비 정상적으로 식각되는 현상이다. 고밀도 플라즈마 장치를 사용하여 식각 공정을 진행할 때, 방향성이 적고 빠르게 운동하는 전자들은 감광막(photoresist)의 측면에 포획되고 주 식각(main etch) 단계에 이은 추가식각(over-etch) 시 패턴의 간격이 좁은 지역에서는 주로 이온들만이입사 되어 게이트 산화막의 포면은 양(positive)으로 대전된다. 동시에 가장 외곽에 있는 게이트 전극선은 바깥쪽의 넓은 지역에서 계속적으로 전자의 공급으로 안쪽의 게이트들에 비해 상대적으로 음(negative)의 대전상태가 되며 결국 양이온들의 진행 방향에 영향을 주게 되어 게이트의 하부에 notching을 발생시킨다. Figure 1과 같이 notching은 주로 가장 외곽에 있는 게이트 전극선의 안쪽에서 발생하

게 되는 것으로 알려져 있다[3]. Notching은 플라즈마의 전자 온도에 비례하는 특성과 폴리실리콘 게이트 전극 패턴간의 연결된 상태와 전극간의 간격에 따라 정도의 차이가 발생하며[4,5], 또한 발생되는 notching의 깊이는 폴리실리콘의 n<sup>+</sup> 도핑 농도에 크게 의존한다[6]. 게이트 전극의 식각공정은 얇은 게이트 산화막을 사용하고 높은

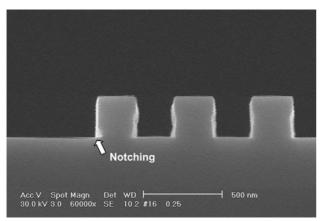

식각 선택비, 수직의 식각형상, 정확하고 재현성 있는 CD (critical dimension) 조절 등이 요구되고 있다. 이 같은 조건을 충족시키기 위해 식각기체 구성에 HBr 또는 산소 등을 Cl<sub>2</sub>에 첨가하여 사용하는 것이 일반적이다[7,8]. Figure 2의 게이트 전국 물질은 notching이 가장 덜 발생되는 것으로 알려진 도핑 되지 않은 비정질 실리콘으로, 발생된 notching은 가장 외곽에 위치한 게이트 전국선의 바깥쪽에서 발생되어 종래에 보고된 폴리실리콘 게이트 전국의 notching [5,9]과 다른 특징을 보이고 있다.

본 연구에서는 Cl<sub>2</sub>/HBr/O<sub>2</sub>의 식각기체 구성으로 도핑 되지 않은 비정질 실리콘 게이트 식각을 진행할 때 Figure 2와 같은 notching 발 생이 식각변수들에 따라 받는 경향성을 파악하고, 자체 고안한 검 증용 패턴을 이용하여 식각장치 내에서 실리콘 기판에 도달하는 100 이원규

Figure 1. Typical notching in doped polysilicon gate line after high density plasma etching.

Figure 2. Notching in undoped amorphous silicon gate at etching at outside-wall foot of the outermost line.

식각 이온들의 진행경로를 분석하였으며, 이 결과를 바탕으로 도핑되지 않은 비정질 실리콘 게이트 식각에서 발생하는 notching의 형성기구에 대한 해석 결과를 제시하였다.

#### 2. 실 험

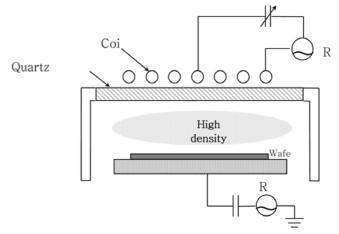

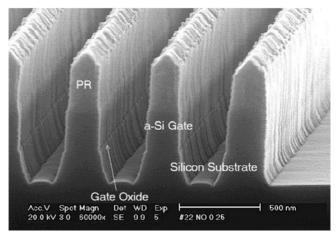

실험에 사용된 장치는 Figure 3과 같은 저압 고밀도 실리콘 식각장비였다. 시편은 P-type wafer 위에 5 nm의 열산화막, 250 nm의 도핑되지 않은 비정질 실리콘막, 무기계 반사방지막 층을 순차적으로 적층하고 감광막 0.7 µm에 게이트 길이가 0.25 µm인 패턴을 이용하였다. Notching의 관찰은 게이트 전국간의 간격이 0.25 µm에서 2.0 µm의 범위로 나누어져 있는 패턴(이때 각 게이트 전극은 연결되지 않았음)에서 하였고, 기본적인 식각기체의 구성은 Cl<sub>2</sub>/HBr/O<sub>2</sub>였다. Notching의 발생 요소 중 이온 및 라디칼이 미치는 영향을 파악하기위해 source 및 bias power를 변화시켰고, 각 식각기체의 효과를 알아보기 위해 Cl<sub>2</sub>/HBr의 구성비를 바꾸며 notching 발생을 관찰하였다. 식각 과정의 이온 궤적(ion trajectory) 분석을 위한 구조를 아래와같이 제작 하였다. 게이트 전극의 식각에 있어 패터닝된 감광막의측면에 전자가 대전되는 것이 이온의 궤적에 어떠한 영향을 미치는지를 알기 위한 것으로서, 감광막의 유무에 따른 하층부의 형상의 차이

Figure 3. Schematic of high density plasma silicon etcher.

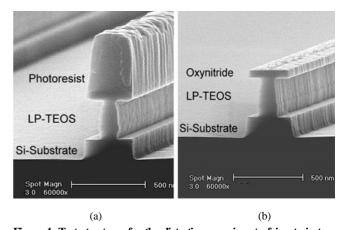

Figure 4. Test structures for the distortion experiment of ion trajectory (a) with photoresist mask and (b) with oxynitride mask only.

를 관찰할 수 있도록 설계하였으며 구조는 Figure 4와 같다. 제작 방법은 실리콘 기판 위에 LPCVD (low pressure chemical vapor deposition) TEOS (tetraethylorthosilicate) 산화막을 300 nm, oxynitride 60 nm를 순차적으로 중착하고 게이트 전극 형상의 감광막을 패터닝하였다. 이렇게 패턴이 형성된 기판을 산화막 식각장치를 이용해 산화막까지 식각한 후, 실리콘 식각장치에서 기판실리콘을 130 nm 정도 식각하였고, 순차적으로 9:1 BOE (buffered oxide etchant)에서 15 sec간 담그어 Figure 4(a)와 같이 LPCVD TEOS 산화막의 측면 부분을 제거시켰다. 이때, 한 시편은 그대로 실험을 실시하고 다른 한 시편은 Figure 4(b)와 같이 감광막을 제거하여 동일한 공정조건으로 식각을 실시 하였다. Notching 두께의 측정 및 관찰은 SEM (scanning electron microscope)을 이용하였다.

### 3. 결과 및 고찰

3.1. 도핑 되지 않은 비정질 실리콘 게이트 전극선의 notching 형성 도핑되지 않은 비정질 실리콘 게이트 식각 후에 가장 외곽에 위치한 게이트 전극선의 바깥쪽과 간격이 아주 넓은 게이트 전극선 (isolated line)에서 notching이 주로 발견된다. 이 때 notching의 깊이는 over-etch 시간에 따라 증가하며, 게이트 전극선 간의 간격이 넓어질 수록 notching의 깊이도 증가하는 특성을 보이는 것으로 선행연구

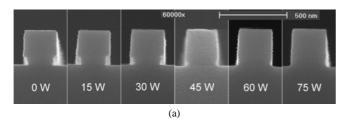

Figure 5. Notching profiles in un-doped amorphous silicon gate line according to (a) the variation of bias power under the fixed condition of 3 mT/xW bias power/300 W source power/35 sccm Cl<sub>2</sub>/35 sccm HBr/7 sccm O<sub>2</sub> and (b) the variation of source power under the fixed condition of 3 mT/30 W bias power/xW source power/35 sccm Cl<sub>2</sub>/35 sccm HBr/7sccm O<sub>2</sub>.

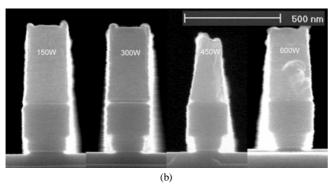

Figure 6. Notching profiles in un-doped amorphous silicon gate line according to the flow ration ratio of HBr and  $Cl_2$  under the fixed condition of 3 mT/300 W source power/30 W bias power/x sccm  $Cl_2/x$  sccm HBr/7 sccm  $O_2$ .

에서 나타났다[10]. Over-etch 시간에 따라 거의 선형적 증가특성을 보이는 것은 notching이 돌발적으로 발생하는 것이라기보다는 어떠한 인자에 의해 지속적으로 진행되는 것을 뜻한다. 이와 같이 notching을 유발시킬 수 있는 인자를 알기 위해 이온 및 라디칼의 밀도를 변화시킬 수 있는 source power와 기판으로 향하는 이온의 충돌에너지를 조절할 수 있는 bias power를 각각 변화시키며 실험한 결과 notching 깊이는 source power에 따라 증가하고 bias power에 감소하는 특성을 Figure 5에서와 같이 관찰할 수 있다. Bias power의 증가에따라 notching의 깊이가 감소하는 것은 notching을 유발하는 주요 인자가 bias power에 의해 힘을 받을 수 있는 이온이라는 것을 보인다. 즉, bias power의 증가에 의해 이온의 직진성이 개선되어서 notching의 정도가 변화하는 것으로 판단된다.

식각 시간을 포함한 나머지 조건은 동일하게 하고  $Cl_2$ 와 HBr의 유량비를 바꾸면서 over-etch를 진행한 결과를 Figure 6에 나타냈다. Isolated line에서 HBr 없이  $Cl_2$  플라즈마만으로 식각을 진행한 경우 선택비 부족으로 게이트 전극 바로 옆에 micro-trench가 발생되었으

Figure 7. Final gate etching profile after over-etch step with the recipe; 3 mT/300 W source power/30 W bias power/35 sccm  $Cl_2/35$  sccm HBr/7 sccm  $O_2$ . The process sequence was composed of main-etch step, gate oxide removal with  $C_2F_6$  plasma and over-etch step, sequentially.

나, notching은 전혀 발생하지 않았다. 이와 같은 HBr 첨가 유량에 따른 notching 두께의 변화는 Cl 이온에 비해 충돌특성이 강한 Br 이온에 기인한 것으로 보여진다. 여기서 게이트 전국선 간의 간격이 넓은 지역에서 Br 이온의 충돌특성에 의해 발생된 notching은 이온 궤적과 밀접한 연관이 있는 것으로 생각할 수 있다. 게이트 전국선 간의 간격이 좁은 부분(dense pattern)에서 notching의 모양은 위쪽으로 진행되고 측면으로는 적게 발생된 모양을 띤다[10]. Over-etch dense pattern에서 전자들은 감광막 측면에 포획되고 좁은 간격으로 이온들이 주로 입사하게 된다. 입사 된 이온은 over-etch과정에서 이미 노출된 산화막 표면을 양으로 대전시키게 되어서 결국 간격이좁은 부분의 산화막의 표면 포텐셜을 높이게 된다. 간격이 좁은 부분에 있어서 이 같은 산화막의 표면 포텐셜 증가 현상은 그 이후로 입사 되는 이온의 궤적을 포텐셜이 상대적으로 낮은 게이트의 측 벽 방향으로 넓게 휘게 만들어 notching의 높이가 위로 진행되는 결과를 나타내는 것으로 판단된다.

이에 대한 확인을 위해 main etch 후 CF6 플라즈마로 게이트 산화막을 제거하고 난 뒤, over-etch를 실시한 결과 기판 실리콘이 식각될 때, Figure 7과 같이 notching은 더 이상 발생하지 않는 결과를 얻을 수 있었다. 이 사실들로서 게이트 산화막이 노출된 over-etch에서더 이상 식각에 참여하지 못하는 이온이 산화막 표면에 대전되고이로 인해 이후로 유입되는 Br 이온의 궤적 변화가 notching을 유발시키는 것임을 확인할 수 있었다. 이러한 관점에서 게이트 전극선간의 간격이 넓어지게 되면, 산화막 표면의 포텐셜 증가가 점점 낮아지게 되어 이온의 궤적은 대부분 직진성을 회복하게 된다. 하지만 감광막과 게이트 전극의 측벽은 포획된 전자에 의해 포텐셜이상대적으로 낮아지게 되고 그에 의해 이온의 궤적이 게이트 전극측벽쪽으로 휘어져서 게이트 바로 옆의 산화막 표면은 양(positive)으로 대전된다. 이 같은 포텐셜의 급격한 변화에 의해 휘어진 Br 이온은 게이트 측벽의 밑부분에서 충돌을 일으켜 notching을 보다 깊게 만들게 된다.

102 이원규

Figure 8. Comparison of test structures in Figure 4 after etching with 3 mT/300 W source power/30 W bias power/35 sccm Cl<sub>2</sub>/35 sccm HBr/7 sccm O<sub>2</sub>/30 sec.

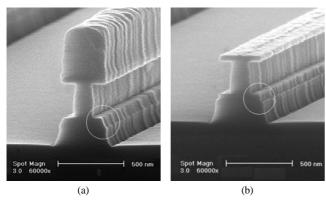

Figure 9. Etching profiles of test structure with photoresist mask according to the level of bias power.

#### 3.2. 비정질 실리콘 게이트 전극선의 notching 발생 기구

Figure 8은 Figure 4의 테스트 패턴을 3 mT/300 W source power/30 W bias power/35 sccm Cl<sub>2</sub>/35 sccm HBr/7 sccm O<sub>2</sub>의 공정 조건에서 30 sec간 식각 후의 SEM 사진이다. Figure 8에서 기판 실리콘의 식각된 상부의 모서리 부분은 감광막의 유무에 따른 형태 차이가 현저하 게 난다. 감광막 대신 oxynitride를 마스크로 사용하여 식각한 경우 에는 형상이 원래의 모양과 비슷하게 거의 90°를 유지하는 반면에 감광막이 있는 경우는 모서리 부분이 많이 식각되어서 형상이 수 직한 부분으로부터 약 30°정도가 기울어져 있음을 관찰할 수 있다. 이 같은 현상으로 볼 때, 플라즈마 sheath를 통과하는 이온의 궤적은 직진성을 가지고 기판 표면으로 향하지만, 플라즈마로부터 발생된 전자들이 먼저 감광막의 측면에 포획됨에 따라 감광막 측면은 상 대적으로 낮은 전위가 되어서 그 주위를 지나는 이온의 궤적에 변 화를 가져오게 된다. 결국 감광막이 있는 패턴을 식각할 때, 감광막 에 대전된 전자에 의해서 그 주위를 통과하는 이온의 궤적이 패턴 쪽으로 휘게 되어 모서리 부분으로 쏠려진 것으로 보인다. 감광막 이 없는 경우에 있어서도 기판 실리콘의 측면이 약간의 식각되는 현상이 관찰되는데, 이는 플라즈마에서 발생된 이온의 직진성이 완 전하지 않기 때문으로 보여진다.

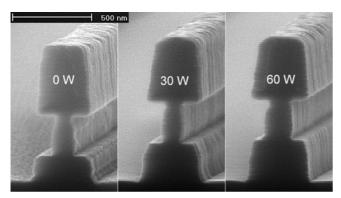

Figure 9는 Figure 8에서 사용된 감광막이 있는 상태의 시편을 공정 시간을 포함한 다른 모든 조건은 동일하게 하고 bias power를 각각 0 W, 30 W, 60 W로 변경하여 식각을 한 결과이다. Bias power가

Figure 10. Schematic model for the formation of notching at the dense and outside of the outmost lines with un-doped amorphous silicon.

증가하게 되면 그에 따른 식각속도 증가로 패턴의 높이는 보다 높아짐을 관찰할 수 있었으며, 패턴의 모서리 부분의 형상이 서로 다른 것을 관찰할 수 있다. 0 W bias power의 조건에서 패턴의 모서리 부분은 미약하게 recess되었지만, 이온 에너지가 낮아서 전반적인 식각은 일어나지 않았고, 30 W의 경우 Figure 8(a)에 나타난 것과 비슷한 결과가 나타났다. 그러나 bias power를 좀더 증가 시켜서 60 W가 되었을 때, 모서리 경사가 80° 이상으로 보다 수직한 형태를 나타난다. 이는 감광막에 대전된 전자에 의해 왜곡되었던 이온의 궤적이 bias power의 증가로 그 영향에서 벗어나 직진성을 가지기 때문이며 이것은 bias power의 증가에 의해 notching의 깊이가 감소한다는 결과와 일치한다[10].

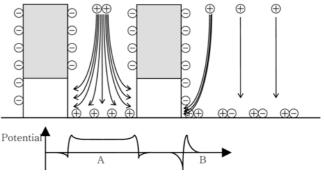

Figure 10은 도핑 되지 않은 비정질 실리콘 게이트 전극 식각과정에서 형성되는 notching의 발생 기구를 정성적으로 제시한 것이다. 게이트 전극선 간의 간격이 좁은 지역(dense pattern)에서의 notching 현상은 게이트 전극선 사이에 노출된 산화막 표면(Figure에서 "A" 지역)이 이온에 의해 양(positive)으로 대전되어서 포텐셜이 높아지고 따라서 좁은 전극선 사이로 입사되는 이온의 궤적이 보다 넓은 범위로 휘어서 결국 분산되는 효과로 인해 notching의 깊이가 얇고 넓게 나타난다. 한편, 게이트 전극선 간의 간격이 넓은 지역(isolated pattern)에서 발생되는 notching은 다음에 열거된 일련의 순서로 보다 명확히 설명이 가능하다.

첫 번째로 플라즈마로부터 발생된 빠른 운동성의 전자는 패턴 형성을 위한 감광막 측면에 포획되어서 상대적으로 음(negative)의 포텐셜을 형성하고 전자로 대전된 감광막의 주위를 통과하는 이온은 진행 경로가 왜곡되어서 게이트 측면으로 몰리게 된다.

두 번째로 게이트 측면으로 몰린 이온들로 인해 main-etch 동안 다른 지역에 비해 비교적 빠른 속도로 식각되며, 하층부인 게이트 산화막이 노출된 over-etch 단계에서는 그 지역의 포텐셜은 다른 부분에 비해 양(positive)으로 대전되게 된다.

세 번째로 이러한 양의 대전은 게이트 바로 옆쪽에서 급격한 포 텐셜 차이를 만들게 되어서 이후 진입하는 이온의 방향을 게이트 측면에 수직으로 왜곡 시킨다. 이 때 휘어진 이온의 출동 에너지가 Br 이온과 같이 무거워서 충분히 클 때 notching을 발생시킨다.

이와 같이 플라즈마 내의 식각 활성종 이온들의 궤적의 왜곡에 의한 notching현상은 감광막의 대전효과에 의한 영향이 커서 대전 효과를 최소화 할 수 있는 공정 상태에서 식각을 진행하면 비정질 실리콘의 notching 발생을 크게 억제 할 수 있을 것으로 판단된다.

## 4. 결 론

반도체 소자제조의 게이트 전극 식각 공정은 선택비, 전극형상제 어, CD 변화 억제 등 많은 공정 요구 조건을 만족시켜야 한다. 도핑 되지 않은 비정질 실리콘 게이트 전극선 식각공정에서 첨가 기체 로 HBr의 사용은 Br 이온에 의한 식각 속도 향상과 선택도 등의 측 면에서 유용한 특성이 나타난다. 그러나 도핑 되지 않은 비정질 실 리콘을 사용한 게이트 식각에서 발생되는 notching은 게이트 간의 간격이 넓은 지역에서 심해지는 특징이 발견되었다. 실험 결과에 따르면, notching은 선택비를 향상 시키기 위해 첨가된 HBr 중 Br 이 온이 게이트 측벽에서의 충돌로 발생하게 된 것임을 알 수 있었다. 이와 같이 Br 이온에 기인한 notching은 게이트 간의 간격이 좁은 지 역에서는 이온의 궤적이 넓게 분산되고 간격이 넓은 지역에서는 집중되는 특성을 가지고 있었다. 따라서 좁은 전극선 사이로 입사 되는 이온의 궤적이 보다 넓은 범위로 휘어서 결국 분산되는 효과 로 인해 notching의 깊이가 얇고 넓게 나타나는 반면에 간격이 넓은 지역에서는 포텐셜의 급격한 변화에 의해 휘어진 Br 이온의 게이트 밑부분에 충돌이 집중되어 깊은 notching이 만들어지게 된다.

# 참 고 문 헌

- 1. K. E. Petersen, IEEE Proc., 70, 420 (1982).

- H. Namatsu, M. Nagase, K. Kurihara, K. Iwadate, and K. Murase, Microelect. Eng., 27, 71 (1995).

- N. Fujiwara, T. Maruyama, and M. Yoneda, Jpn. J. Appl. Phys., 34, 2095 (1995).

- T. Nozawa, T. Kinoshita, T. Nishizuka, and A. Nariai, *Jpn. J. Appl. Phys.*, 34, 2107 (1995).

- 5. G. S. Hwang and K. P. Giapis, J. Vac. Sci. Technol. B, 15, 70 (1997).

- K. K. Chi, H. S. Shin, W. J. Yoo, and C. O. Jung, *Jpn. J. Appl. Phys.*, 35, 2440 (1996).

- 7. K. Miwa and T. Mukai, J. Vac. Sci. Technol. B, 20, 2120 (2002).

- V. M. Donnelly and N. Layadi, J. Vac. Sci. Technol. A, 16, 1571 (1998).

- J. Foucher, G. Cunge, L. Vallier, and O. Joubert, *Microelect. Eng.*, 61-62, 849 (2002).

- 10. C. K. Ko and W. G. Lee, J. Ind. Eng. Chem., in press (2009).