# Low-Power 512-Bit EEPROM Designed for UHF RFID Tag Chip

Jae-Hyung Lee, Ji-Hong Kim, Gyu-Ho Lim, Tae-Hoon Kim, Jung-Hwan Lee, Kyung-Hwan Park, Mu-Hun Park, Pan-Bong Ha, and Young-Hee Kim

In this paper, the design of a low-power 512-bit synchronous EEPROM for a passive UHF RFID tag chip is presented. We apply low-power schemes, such as dual power supply voltage (VDD=1.5 V and VDDP=2.5 V), clocked inverter sensing, voltage-up converter, I/O interface, and Dickson charge pump using Schottky diode. An EEPROM is fabricated with the 0.25  $\mu m$  EEPROM process. Power dissipation is 32.78  $\mu W$  in the read cycle and 78.05  $\mu W$  in the write cycle. The layout size is 449.3  $\mu m \times 480.67~\mu m$ .

Keywords: Low-power, EEPROM, UHF RFID, tag chip, sensing scheme, dual power, charge pump.

# I. Introduction

Radio frequency identification (RFID) is the technology to provide various communication services between objects by collecting, storing, and revising information regarding these objects by using RFID tags installed or attached to them. RFID tags are classified according to communication ability, battery existence, and read/write function as shown in Table 1 [1]. They are standardized by Electronic Product Code (EPC) Global. Currently, passive RFID tags are more widely used than their active counterparts because they are low-cost and small-sized. Therefore, more effort has been devoted to the development of the passive tags [2].

A class 1 generation 2 tag is a passive tag like class 0 and class 2 tags, but it has advantages of cost and size. It can read and write, but it also has a lock function for security and a kill function, which causes the tag to be reprogrammed or instructs it to self-destruct. These advantages are expected to apply in logistics, traffic, and inventory management; therefore, there is a great deal of research progressing in this area.

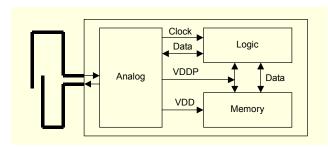

A passive UHF RFID tag comprises an antenna and a tag chip as shown in Fig. 1. The tag chip consists of analog, logic, and memory blocks [3]. In the analog block there is a demodulator to convert frequency into data, a modulator to convert data into frequency, and a voltage multiplier to convert energy from the antenna into supply voltage in the analog circuit. The logic controls the operation modes of the analog block, checks the protocol, performs the cyclic redundancy check (CRC), and checks for errors. The memory block must be read out and written in; therefore, non-volatile memory, that is, EEPROM, which keeps data during power-down, is often used. A low-power circuit is required to transfer data to the

Manuscript received May 14, 2007; revised Dec. 04, 2007.

Jae-Hyung Lee (phone: +82 55 285 1023, email: leejaehyung@changwon.ac.kr), Tae-Hoon Kim (email: kimth@changwon.ac.kr), Mu-Hun Park (email: mhpark@changwon.ac.kr), Pan-Bong Ha (email: pha@changwon.ac.kr), and Young-Hee Kim (phone: +82 11 542 3408, email: youngkim@changwon.ac.kr) are with the Department of Electronic Engineering, Changwon National University. Gyeongnam. Rep. of Korea.

Ji-Hong Kim (email: lapael81@empal.com), Gyu-Ho Lim (email: ghlim@changwon.ac.kr), and Jung-Hwan Lee (email: junghwan.lee@magnachip.com) are with MagnaChip Semiconductor, Cheongju, Rep. of Korea.

Kyung-Hwan Park (email: khpark\_2001@etri.re.kr) is with Convergence Components & Materials Research Laboratory, ETRI, Daejeon, Rep. of Korea.

Table 1. Classification of RFID tags.

| EPC tag | Capabilities                                                                                            | Memory                                    |

|---------|---------------------------------------------------------------------------------------------------------|-------------------------------------------|

| Class 0 | Read only (i.e., the EPC number is encoded onto the tag during manufacture and can be read by a reader) |                                           |

| Class 1 | Read, write once→write many (Generation 2)                                                              | 96 bits<br>128/256 bits<br>(Generation 2) |

| Class 2 | Read, write.                                                                                            | Larger memory                             |

| Class 3 | Class 2 capabilities plus a power source to provide increased range and/or advanced functionality       |                                           |

| Class 4 | Class 3 capabilities plus active communication and the ability to communicate with other active tags    |                                           |

| Class 5 | Class 4 capabilities plus the ability to communicate with passive tags as well                          |                                           |

Fig. 1. Architecture of RFID tag chip.

reader and to check identifications because the voltage multiplier of the analog block transforms UHF signal into power [4].

# II. Circuit Design

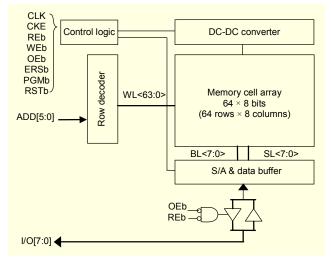

Figure 2 shows a block diagram of the 512-bit synchronous EEPROM. It consists of a cell array (64 rows × 8 columns), a row decoder, a data buffer, control logic to generate control signals at different operation modes, and a DC-DC converter to provide high voltages (VPP and VPPL). The interface signals are clock control signals, command control signals, address bus, and bi-directional data bus. The clock control signals are clock (CLK) and clock enable (CKE). For command control signals, there are REb (read enable), WEb (write enable), OEb (output enable), ERSb (erase), PGMb (program), and RSTb (reset).

The width of the address bus is 6, and that of the data is 8. One of 64 bytes is selected by 6 address lines, and the unit of operation is one byte in both read and write modes. The main features of the EEPROM are shown in Table 2.

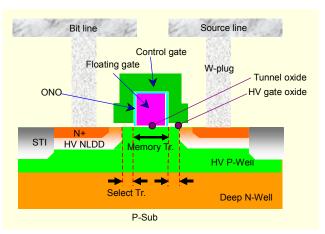

Figure 3 shows the cross-sectional view of an EEPROM cell.

Fig. 2. Block diagram of 512-bit synchronous EEPROM.

Table 2. Main features of the EEPROM.

| Items             | Main features                     |  |  |

|-------------------|-----------------------------------|--|--|

| Technology        | 0.25 μm EEPROM process            |  |  |

| Memory cell       | EEPROM                            |  |  |

| ONO thickness     | 100 Å                             |  |  |

| Operating modes   | Erase / program / read / stand-by |  |  |

| Supply voltage    | VDD=1.5 V / VDDP=2.5 V            |  |  |

| BL sensing scheme | Clocked inverter                  |  |  |

| Charge pump       | Dickson pump                      |  |  |

Fig. 3. Cross-sectional view of EEPROM cell.

The dielectric between the control gate and the floating gate is surrounded by oxide-nitride-oxide to get a high coupling ratio, and the EEPROM is in the triple-well [5]. The cells can be erased and programmed by Fowler-Nordheim tunneling. The control gate is connected to the word-line (WL), that is, the

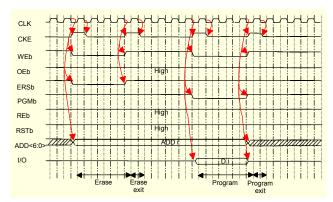

Fig. 4. Write timing diagram of synchronous EEPROM.

Fig. 5. Read timing diagram of synchronous EEPROM.

output node of the row decoder. The EEPROM has four operating modes: program, erase, read, and stand-by. They operate synchronously with the clock signal. Write mode includes program and erase modes. Dual power supply voltage, VDD (1.5 V) and VDDP (2.5 V), is used to reduce the current in both read and write modes.

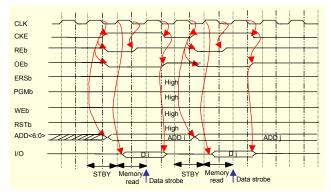

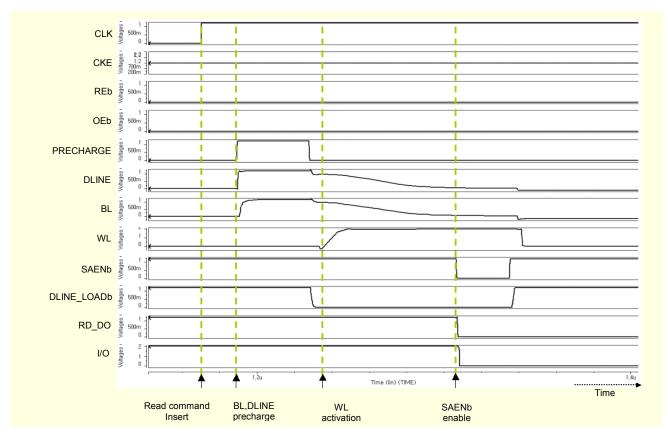

Figure 4 shows a write timing diagram in which one byte cell is first erased and then data is programmed. Figure 5 shows a read timing diagram of the synchronous EEPROM. Data in the read cycle is transferred by the logic circuit of the tag chip at the rising edge of the next clock cycle after the read command is enabled.

Table 3 shows bias voltage levels of the EEPROM cell for the four operating modes. The WL voltage of the selected cell is 16.5 V, that is VPP (boosted voltage), in the program mode. The bit-line (BL) voltage is 15 V (VPP) in the erase mode. The non-selected BL voltage is 11.5 V (VPP-5 V) in the program mode and 11 V (VPP-4 V) in the erase mode. When normal transistors that have low break-down voltage are connected to the row decoder and column select circuits, device reliability problems occur. For that reason, high voltage transistors with threshold voltages between 0.87 V and 1.29 V have to be used to stand high voltage in the row decoder and column select circuits. If only VDDP is used, the circuits operate properly, but power

Table 3. Bias voltage conditions for the four operation modes of the EEPROM cell.

|                 | Program       |                          | Erase         |                          | Read          |                          | Stand-<br>by  |

|-----------------|---------------|--------------------------|---------------|--------------------------|---------------|--------------------------|---------------|

|                 | Selected cell | Non-<br>selected<br>cell | Selected cell | Non-<br>selected<br>cell | Selected cell | Non-<br>selected<br>cell | Selected cell |

| Word-<br>line   | 16.5          | 0                        | 0             | 11                       | 2.5           | 0                        | 0             |

| Bit-line        | 0             | 11.5                     | 15            | 11                       | 1.5           | Floating                 | Floating      |

| Source-<br>line | Floating      | Floating                 | Floating      | Floating                 | 0             | 0                        | 0             |

| HV-<br>Pwell    | 0             | 0                        | 15            | 0                        | 0             | 0                        | 0             |

| Deep-<br>Nwell  | 2.5           | 2.5                      | 15            | 15                       | 2.5           | 2.5                      | 2.5           |

Fig. 6. Clocked inverter sensing circuit.

dissipation increases in proportion to VDDP in the read mode. On the other hand, if only VDD is used in the circuits, power dissipation decreases; however, circuits that have transistors with a threshold voltage of 1.29 V do not operate properly. Therefore dual power supply voltage (VDDP for high voltage transistors and VDD for the others) is used to reduce power dissipation.

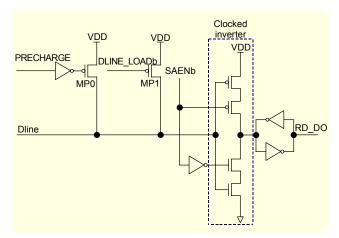

A clocked inverter sensing method is applied to read out the data of EEPROM cells in the read mode [8]. Usually, a current sensing circuit is used for the non-volatile memory [6]. This is not proper in the EEPROM design for RFID tag chips because the current dissipation of the sensing circuit is large. Therefore, a low-speed low-power read data (RD) sense amplifier should be used without a reference current biasing circuit. The clocked inverter sensing circuit is shown in Fig. 6.

A short pulse is generated by the PRECHARGE signal before the control gate voltage (WL) is active in the read mode. It drives a PMOS transistor, MPO, to the precharge DLINE signal to VDD. After the WL is active, the DLINE signal keeps the VDD

Fig. 7. Block diagram of the DC-DC converter.

Table 4. VREF, VREF\_VPP, VPP, and VPPL voltage levels in different operating modes.

|          | Program | Erase | Read | Stand-by |

|----------|---------|-------|------|----------|

| VREF     | 0.75    | 0.685 | 0    | 0        |

| VREF_VPP | 1.5     | 1.37  | 0    | 0        |

| VPP      | 16.5    | 15    | 2.5  | 2.5      |

| VPPL     | 11.5    | 11    | 2.5  | 2.5      |

Fig. 8. Voltage-up converter circuit.

level because current cannot flow through the programmed cells. On the other hand, the DLINE signal is almost 0 V because current flows through the non-programmed cells. If there is enough data to be transferred to the DLINE signal, the SAENb signal in the clocked inverter is enabled, and the data is read out to DLINE. The load transistor, MP1, acts like an active load while WL is selected. It prevents DLINE falling to 0 V because the leakage current during EEPROM is off.

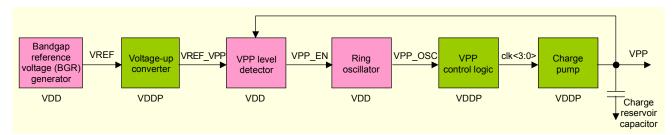

Figure 7 shows a block diagram of the DC-DC converter, which uses a Dickson charge pump [7] to generate high voltage

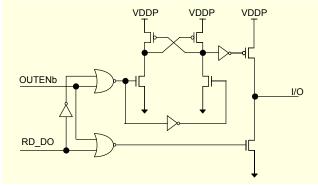

Fig. 9. I/O interface circuit.

Table 5. Power dissipation comparison in the program mode.

|                                       | PN diode | Schottky diode |

|---------------------------------------|----------|----------------|

| Power dissipation in the program mode | 65.7 μW  | 57.7 μW        |

in the write mode. It consists of a bandgap reference voltage generator, a VPP level detector, a ring oscillator, a VPP control logic, and a charge pump.

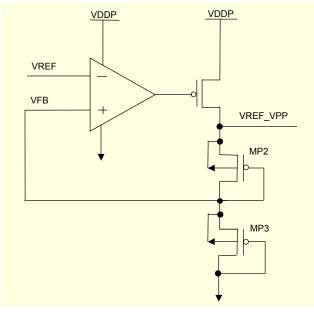

If VPP is lower than the target voltage of the load current, VPP\_EN becomes high. Then, a ring oscillator oscillates to increase VPP. That causes a positive charge to pump into the VPP node and VPP increases. If VPP is higher than the target voltage, then VPP EN (the output of the VPP level detector) is low and pumping stops in order to keep the output voltage to VPP by using negative feedback. To decrease power dissipation, VDD power is used in the bandgap reference voltage generator, VPP level detector, and ring oscillator circuits, and VDDP power is used in the voltage-up converter, VPP control logic, and charge pump circuits. In the VPP level detector circuit, an eleventh of VPP, which is divided by NMOS diodes in series, is compared with VREF VPP to control the charge pump. The VREF VPP is 1.5 V in the program mode and 1.37 V in the erase mode as shown in Table 4. For low power dissipation, the VDD power source which is lower than the VDDP power source is used in the bandgap reference voltage generator. However, it cannot generate the reference voltage, 1.5 V, using only VDD power.

Fig. 10. Timing diagram for the case of critical path in the read cycle.

For this reason, a low-power voltage-up converter circuit is used to boost VREF, which can guarantee the reference voltage, VREF\_VPP. Power dissipation can be lower when the voltage converter is used compared to using only a VDDP power source.

Figure 8 shows a voltage-up converter circuit which doubles the VREF in the reference voltage generator [8]. It generates the input voltage of the VPP level detector. The voltage-up converter consists of a differential amplifier, a common source amplifier, and a voltage divider using PMOS diodes. Identical PMOS diodes, MP2 and MP3, make up a voltage divider. The feedback voltage (VFB) is set to half of VREF\_VPP. When VREF and VFB are equal by negative feedback, VREF\_VPP makes VREF double.

The RD\_DO data voltage swings between VDD and VSS. The I/O data voltage swings between VDDP and VSS. If the I/O voltage swings between VDD and VSS, it induces a short circuit in the adjacent block connected to I/O signal because it swings between VDDP and VSS. For this reason, the VDD-to-VDDP voltage-level translator shown in Fig. 9 is needed for the I/O interface.

The Dickson charge pump generates VPP and VPPL in the write mode. It has lower power dissipation by using the lower forward bias diode voltage drop. For this reason, a Schottky diode is used for the pump. Table 5 compares the power

dissipation of the Dickson charge pump using a PN diode and using a Schottky diode in the program mode. The power dissipation using a Schottky diode is approximately 12% lower than that using a PN diode.

# III. Simulation and Test Results

The EEPROM is designed using the 0.25 µm EEPROM process for UHF RFID tag chips. Figure 10 shows timing diagrams of CLK from the analog block; command control signals CKE, REb, and OEb from the logic block; and PCHARGE, DLINE\_LOADb, and SAENb from the control logic block as shown in Fig. 2. When a read command enters at the rising edge, PCHARGE makes DLINE and BL precharge to VDD. The WL is active after the BL is precharged. When data is transferred to the BL, valid data comes out of the I/O by SAENb through the RD\_DO within half a clock period.

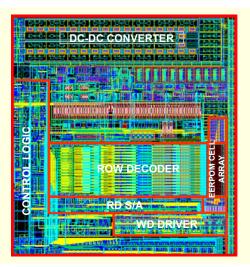

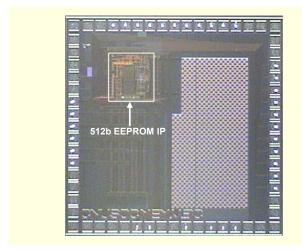

Figure 11 shows a layout image for the 0.25  $\mu$ m EEPROM process. The areas of the analog, logic, and cell array are marked. The layout size is 449.3  $\mu$ m  $\times$  480.67  $\mu$ m. Figure 12 shows an image of the fabricated EEPROM.

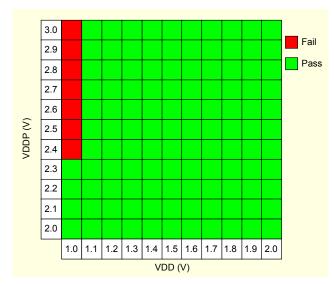

Figure 13 is a shmoo plot of the fabricated EEPROM. Functions are tested by performing the read cycle after the erase cycle and the read cycle after the program cycle, using

Fig. 11. EEPROM layout.

Fig. 12. Image of the fabricated EEPROM IP.

Fig. 13. Shmoo plot of the fabricated EEPROM.

Table 6. Power dissipation results at VDD=1.5 V, VDDP=2.5 V, and Temp=25 °C.

| Operating mode |      | Operating current | Dissipated power |  |

|----------------|------|-------------------|------------------|--|

| Erase          | VDD  | 24.7 μΑ           | 61.1 μW          |  |

|                | VDDP | 9.6 μΑ            |                  |  |

| Program        | VDD  | 23.4 μΑ           | 78.1 μW          |  |

| riogiaiii      | VDDP | 17.2 μΑ           | /6.1 μ W         |  |

| Read           | VDD  | 16.8 μΑ           | 28.7 μW          |  |

|                | VDDP | 1.4 μΑ            | 26.7 μW          |  |

the timing diagrams of Figs. 4 and 5. All cases are passed except at VDD=1.0 V. This means that the EEPROM has a wide operation margin.

Table 6 shows power dissipation test results for different operating modes. The results show that the designed 512-bit EEPROM is suitable for RFID tag chip memory applications.

### IV. Conclusion

In this paper, the design of a low-power 512-bit synchronous EEPROM with EEPROM cells for a passive UHF RFID tag chip was presented. Dual power supply voltage, VDD (1.5 V) and VDDP (2.5 V), was used to reduce the current and the power in the read and write modes. Also, a sensing method using clocked inverter in the read mode was applied. The VREF\_VPP was made by using a voltage-up converter in the write cycle. A level translator was applied to the I/O interface to reduce short circuiting. A Schottky diode was used for lower power dissipation in the Dickson charge pump.

We demonstrated that the EEPROM fabricated with a 0.25  $\mu$ m EEPROM process has a wide operation margin and low power dissipation of 78.1  $\mu$ W in the program mode, 61.11  $\mu$ W in the erase mode, and 28.7  $\mu$ W in the read mode. The proposed EEPROM is suitable for UHF RFID class 1 generation 2 tag chip applications.

### References

- [1] http://www.epcglobalinc.org.

- [2] R. Weinstein, "RFID: A Technical Overview and Its Application to the Enterprise," *IT Professional*, vol. 7, no. 3, May/June 2005, pp. 27-33.

- [3] U. Karthaus and M. Fischer, "Fully Integrated Passive UHF RFID Transponder IC with 16.7 μW Minimum RF Input Power," IEEE J. of Solid-State Circuits, vol. 38, Oct. 2003, pp. 1602-1608.

- [4] G.Yaron, S.J. Prasad, M.S. Ebel, and B.M.K. Leong, "A 16K

E<sup>2</sup>PROM Employing New Array Architecture and Designed-In Reliability Features," *IEEE JSSC*, vol. SC-17, Oct. 1982, pp. 833-840.

[5] J.H. Lee and M.K. Ko, "A Novel EEPROM Cell for Smart Card Application," *Microelectronic Engineering*, vol. 71, no. 3/4, May 2004, pp. 283-287.

[6] F. Xu, X. He, and L. Zhang, "Key Design Techniques of a 40 ns 16K Bits Embedded EEPROM Memory," *ICCCAS*, vol. 2, Jun. 2004, pp. 1516-1520.

[7] J.F. Dickson, "On-Chip High-Voltage Generation in MNOS Integrated Circuits Using an Improved Voltage Multiplier Technique," *IEEE Journal of Solid-State Circuits*, vol. 11, June 1976, pp. 374-378.

[8] Y.H. Kim et al., "A Low-Power EEPROM Design for UHF RFID Tag Chip," *Journal of KIMICS*, vol. 10, no. 3, Mar. 2006, pp. 486-495.

Jae-Hyung Lee received the BS and MS degrees in electrical engineering from Changwon National University, Rep. of Korea, in 2005 and 2007, respectively. He is currently pursuing a PhD program at Changwon National University. His research interests include low-voltage low-power embedded memory IP

design and RFID tag chip design.

**Ji-Hong Kim** received the BSEE and MS degrees from Changwon National University, Rep. of Korea, in 2005 and 2007, respectively. In 2007, he joined the Mobile Display Driver IC (MDDI) device team, MagnaChip Semiconductor Ltd., Cheongju, Rep. of Korea. He is working on the development of the HV13 product. His research

interests include CDP design, low-power embedded memory, display driver IC, analog design, and low- and high-voltage device characteristics.

Gyu-Ho Lim received the BSEE degree from Changwon National University, Rep. of Korea, in 2002, and the MS and PhD degrees in electrical engineering from Changwon National University, Rep. of Korea, in 2004 and 2007, respectively. In 2007, he joined the Display Solution Research and Development Division,

Magnachip Semiconductor, Ltd., Cheongju, Rep. of Korea. He has worked on mobile display driver IC (MDDI) design. His research interests include low-voltage low-power embedded memory IP design (1T-RAM), MDDI design, CMOS image sensor design, RFID tag chip design, and analog IC design.

**Tae-Hoon Kim** received the BS degree in electrical engineering from Changwon National University, Rep. of Korea, in 2007. He is currently working towards a master's degree at Changwon National University. His research interests include embedded memory and DC-DC converter IP design.

**Junghwan Lee** received the PhD degree in chemical engineering from Drexel University, Philadelphia, PA, in 1996, the MS degree from Korea Advanced Institute of Science and Technology (KAIST), Seoul, Rep. of Korea in 1985, and the BS degree from Hanyang University, Seoul, Rep. of Korea, in 1983. In

1989, he joined MagnaChip Semiconductor Inc., which is a spin-off from Hynix Semiconductor Inc., in October 2004. He worked on the development of 4M, 16M, and 64M DRAM as a device and worked as a process integration engineer until 1996. Since 1996, he has been a project leader for the development of embedded memories, such as embedded DRAM, Flash, and EEPROM. Currently, his research interests include high voltage devices, power devices, Schottky diodes, and 1 TRAM. Before joining MagnaChip Semiconductor, he worked as a device researcher for Samsung Electronics from 1985 to 1988. During that time, he worked on the development of SRAM memories such as 16K, 64K, and 256K SRAM.

**Kyung-Hwan Park** received the BS degree in electronic engineering from Hanyang University, Seoul, Rep. of Korea, in 1991 and the MS and PhD degrees from Korea Advanced Institute of Science and Technology, Rep. of Korea, both in electrical and electronic engineering, in 1993 and 1997, respectively. From 1997 to 2000, he was a

senior engineer at the DACOM R&D Center, Rep. of Korea. In 2001, he joined Electrical and Telecommunications Research Institute, Korea as a senior member of research staff. His technical interests are in the fields of RF/Analog CMOS Circuits and RF system design.

Mu-Hun Park received the BSEE degree from Kyungpook National University, Rep. of Korea, in 1990, and the MS and PhD degrees in electrical engineering from Tohoku University, Japan, in 1993 and 1996, respectively. In 1998, he joined the Department of Electronic Engineering, Changwon National University,

Rep. of Korea, where he is currently an associate professor. His research interests include signal processing and image signal processing.

Panbong Ha received the BS degree from Pusan National University, Rep. of Korea in 1981, and the MS and PhD degrees in electronic engineering from Seoul National University, Rep. of Korea, in 1983 and 1993, respectively. In 1993, he joined the TDX Division of ETRI, Rep. of Korea. From 1993 to 1995, he worked

on the detection of DTMF and R2 MF signaling using DSP chips. In 1987, he joined the Department of Electronic Engineering, Changwon National University, Rep. of Korea, where he is currently a professor. From 1998 to 1999, he was visiting professor at the Communication Research Center of Lancaster University, UK. His research interests include digital systems using FPGAs and embedded systems, and SoC designs, such as low-voltage low-power embedded memory, display drivers, CMOS image sensors, power ICs, and RFID tag chips.

Young-Hee Kim received the BSEE degree from Kyungpook National University, Rep. of Korea, in 1989, and the MS and PhD degrees in electrical engineering from Pohang University of Science and Technology (POSTECH), Rep. of Korea, in 1997 and 2000, respectively. In 1989, he joined the Memory Research and

Development Division, Hyundai Electronics Industries, Ltd., Ichon, Rep. of Korea. From 1989 to 2001, he worked on the design of 4M, 16M, 64M, and 256M DRAM chips. In 2001, he joined the Department of Electronic Engineering, Changwon National University, Rep. of Korea, where he is currently an associate professor. His research interests include low-voltage low-power embedded memory IP design, display driver IC design, CMOS image sensor design, power IC design, RFID tag chip design, and analog IC design.