## Implementation and Performance Analysis of a Digital IF Transceiver for an SDR-based Reconfigurable Base Station

Bong-Guk Yu\* Regular Member, Sung Woong Ra\*\* Lifelong Member

## **ABSTRACT**

This paper presents the implementation and performance test of a Digital IF transceiver for a SDR-based mobile communication base station. The transceiver is reconfigurable to HSDPA and to three profiles, 7 MHz, 3.5 MHz, and 1.75 MHz, each incorporating the IEEE 802.16d WiMAX standard. The transceiver can be reconfigured to other standard profiles through software downloaded onto identical hardware platforms. Experimental results show that the transceiver can be reconfigured to other systems and the performance of the transceiver satisfies the recommended performance criteria of each standard.

**Key Words**: SDR (Software Defined Radio), Digital IF, HSDPA (High Speed Downlink Packet Access), WiMAX, OFDM, Transceiver

## I. Introduction

Recently, mobile communication systems have been recommended to support several frequency bandwidth profiles according to the required user bandwidth in various radio environments. Upcoming fourth-generation mobile systems based on Orthogonal Frequency Division Multiplexing (OFDM) technology have a range of system bandwidth profiles [1]-[3].

In view of the implementation issues, a base station with conventional hardware architecture consisting of a Radio Frequency (RF) part, an Intermediate Frequency (IF) part and a baseband modem part is not sufficiently flexible to accommodate several bandwidth profiles efficiently. Therefore, a software radio architecture that can flexibly adopt the various system profiles is needed for the future mobile communication base station [4],[5]. SDR technology is a promising feature that makes it possible to accommodate several standards through software changes on an identical hardware platform for mobile communication systems<sup>[6]</sup>.

Software radio architectures can be identified where the analog to digital conversion takes place in view of translating an RF analog signal to a digital signal. As analog to digital conversion takes place near the receiving antennas, it is evident that software architecture can achieve increasing flexibility via increased programmability found in digital filter technology, as in [7].

Many studies related to the Digital IF transceiver using SDR technology have been conducted. The research into Digital IF transceivers for mobile base stations using SDR technology has mainly focused on the implementation and design of the transceiver to support a single standard, such as W-CDMA (Wideband Code Division Multiple Access) [8]. In addition, several studies on Digital IF transmitter or receiver architecture to reduce the hardware implementation complexity have been performed, especially for the handset application requiring low power consumption [9]-[11]. However, the study and the implementation structure of the digital IF transceiver using SDR technology which can adopt the heterogeneous system for the mobile base

<sup>\*</sup> 한국전자통신연구원 이동통신연구본부(bgyu2@etri.re.kr), \*\* 충남대학교 전자공학과 통신연구실(swra@cnu.ac.kr) 논문번호: KICS2008-05-204, 접수일자: 2008년 5월 8일, 최종논문접수일자: 2008년 9월 1일

station has not yet been reported.

In this study, we present an SDR-technology-based digital IF transceiver for a mobile communication base station that is reconfigurable to an HSDPA standard and to three bandwidth profiles, 7 MHz, 3.5 MHz, and 1.75 MHz, incorporating the IEEE 802.16d WiMAX standards. In addition, the test results show the performance of the implemented transceiver satisfies the recommended performance criteria of each standard by revealing the EVM value of the downlink IF output taken from the measurement instruments.

This paper is organized as follows. In section II, the overall Digital IF transceiver architecture and design specifications are described. In section III, the implemented base station and the transceiver board, including the printed circuit board (PCB) assembly, is presented. In section 4, the test result, including the reconfiguration function to the other system standards through a software download is verified by examining the downlink IF transceiver output signals. Finally, conclusions are presented in Section V.

## II. Design of the Digital IF Transceiver

In this section, we introduce the overall implemented Digital IF transceiver architecture and design specifications. The main functions of the Digital IF transceiver include the frequency up-conversion of a baseband signal from a modem to an analog IF signal, in addition to the frequency down-conversion of an analog IF signal from an RF transceiver to a digital baseband signal. The RF transceiver down-converts the RF signal from a receiver antenna to an analog IF signal in the heterodyne architecture system. In addition, the Digital IF transceiver has a channelization function that splits one Analog to Digital Converter (ADC) output signal into two paths for two FAs signal processing events on the down-conversion side, and it combines the two FAs digital signals into one combined digital signal for the up-conversion side. The one combined digital signal is then entered into the

Digital to Analog Converter (DAC) on the up-conversion side, as the designed transceiver supports two FAs diversity paths in both the uplink and downlink directions.

Digital IF technologies incorporate solutions to problems that easily occur on conventional heterodyne systems using analog components such as rejection of in-phase and quad-phase signal mismatch and DC offset problems. Therefore, Digital IF transceivers can provide higher performance than analog IF transceivers having signal distortion by nonlinearity, because they can combine multiple FAs on a digital domain using the complex quadrature modulation and demodulation technique for a multicarrier system.

## 2.1 The design of transmitter parts

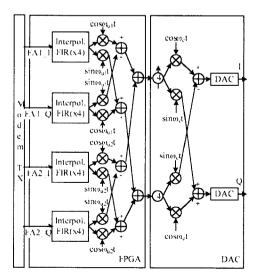

The transmitter architecture of the presented Digital IF transceiver for a base station supporting two FAs is shown in Fig. 1. As seen in the figure, the transceiver takes a functional block for frequency up-conversion and digital combining of two FA signals for the downlink direction.

In the HSDPA system, digital in-phase and quad-phase baseband signals received from a modem corresponding to each FA are sent to the Digital IF transmitter at a rate of 4 oversamples of the fundamental frequency of 3.84 Mbps and at a

Fig. 1. Transmitter architecture of transceive

rate of two oversamples of the fundamental frequency for the WiMAX system. Each digital signal is interpolated to a higher sample rate signal by passing through the x 4 interpolation Finite Impulse Response (FIR) filters. As can be seen in Fig. 1 each signal is modulated to a higher frequency using a numerically controlled oscillator (NCO) to remove the image signals. After this digital complex quadrature modulation (DCQM), the two FA signals are digitally combined to each in-phase and quad-phase signal entering the commercial DAC chip.

Finally, DAC generates the IF analog two-channel output signal centered on 80 MHz and this signal is passed over to the RF transceiver. When  $S_I(t)$  is I-channel DAC input signal from FPGA expressed in (1), it can be shown easily that the resulting analog IF I-channel signal  $A_I(t)$  is expressed by the following equation (2).

$$\begin{split} S_{t}(t) &= \left(I_{1}(t)\cos w_{w1}t - Q_{1}(t)\sin w_{w1}t\right) + \left\{I_{2}(t)\cos w_{w2}t - Q_{2}(t)\sin w_{w2}t\right\} \\ &\qquad \qquad (1) \\ A_{t}(t) &= S_{t}(t)\cos w_{t}t - S_{t}(t)\sin w_{t}t \\ &= \left\{\left[I_{t}(t)\cos w_{s}t - Q_{t}(t)\sin w_{s}t\right] + \left\{I_{2}(t)\cos w_{s}t - Q_{2}(t)\sin w_{s}t\right\}\right\}\cos w_{t}t \\ &- \left\{\left[I_{t}(t)\sin w_{s}t + Q_{t}(t)\sin w_{s}t\right] + \left\{I_{2}(t)\sin w_{s}t + Q_{2}(t)\sin w_{s}t\right\}\right\}\sin w_{t}t \\ &= I_{1}(t)\cos(w_{s1}t + w_{s1}t) - Q_{t}(t)\sin(w_{s1}t + w_{s1}t) \\ &+ I_{2}(t)\cos(w_{s2}t + w_{s1}t) - Q_{2}(t)\sin(w_{s2}t + w_{s2}t) \end{split}$$

Similarly, Q-channel signal So(t) and Ao(t) are

$$S_{Q}(t) = (I_{1}(t)\sin w_{v1}t + Q_{1}(t)\cos w_{v1}t) + (I_{2}(t)\sin w_{v2}t + Q_{2}(t)\cos w_{v2}t)$$

$$A_{Q}(t) = S_{I}(t)\sin w_{I}t + S_{Q}(t)\cos w_{I}t$$

$$= \{(I_{I}(t)\cos w_{v1}t - Q_{I}(t)\sin w_{v1}t) + (I_{2}(t)\cos w_{v2}t - Q_{2}(t)\sin w_{v2}t)\}\sin w_{I}t$$

$$+ \{(I_{I}(t)\sin w_{v1}t + Q_{I}(t)\cos w_{v1}t) + (I_{2}(t)\sin w_{v2}t + Q_{2}(t)\sin w_{v2}t)\}\cos w_{I}t$$

$$= I_{I}(t)\sin(w_{v1}t + w_{v1}t) + Q_{I}(t)\cos(w_{v1}t + w_{v2}t)$$

$$+ I_{2}(t)\sin(w_{v2}t + w_{v2}t) + Q_{2}(t)\sin(w_{v2}t + w_{v2}t)$$

$$(4)$$

where  $I_i(t)$  and  $Q_i(t)$ , i = 1, 2, are in-phase and quad-phase signals, respectively, associated with two baseband channels. Here,  $\omega_{u1} = 16.16$  MHz,  $\omega_{u2} = 20.96$  MHz, and  $\omega_c = 61.44$  MHz for the HSDPA system. For WiMAX systems,  $\omega_{u1} = 12$  MHz,  $\omega_{u2} = 20$  MHz, and  $\omega_c = 64$  MHz respectively.

## 2.2 The design of receiver parts

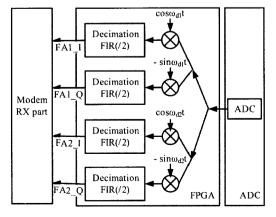

Figure 2 shows the transceiver architecture of the receiver side for the uplink direction. The receiver side has two main functions, frequency down-conversion and channelization, that split one ADC output signal into two paths. The input of this receiver is an analog IF signal from an RF transceiver. Here, the RF transceiver down-converts the RF signal from a receiver antenna to an analog IF signal. The analog IF signal to Digital IF receiver side involves analog to digital conversion through an ADC operating with a specific sampling clock rate.

Band-pass sampling or sub-sampling is considered in the sampling process for the presented transceiver receiver design. For band-pass signals, band-pass sampling states that sampling rate at the rates just more than two times of the signal bandwidth can perfectly reconstruct the original information using in-band alias. Therefore, this sampling scheme can be efficiently implemented at an IF or RF sampling stage with sampling rates lower than the Nyquist sampling rate. For a Digital IF transceiver using a band-pass sampling scheme, the ADC sampling frequency must be selected carefully so that digital images do not overlap each other after the analog to digital conversion [12],[13].

The sampled signal is then split into two paths for FA channel splitting. After being demodulated to the baseband signal using the NCO blocks, the output signal is down-sampled by two through a decimation filter adapted to each in-phase and

Fig. 2. Receiver architecture of transceiver

quad-phase path for HSDPA. Here,  $\omega_{d1}=16.16$  MHz, and  $\omega_{d2}=20.96$  MHz for HSDPA, as shown in Fig. 2. When the transceiver is reconfigured to the WiMAX system,  $\omega_{d1}=12$  MHz, and  $\omega_{d2}=20$  MHz.

## 2.3 Design of the digital FIR Filters

As the signal bandwidths and digital sample rates differ for each system and profiles, the filters should be designed individually. The same filter was used on the down-conversion side for the receiver. All interpolation filters have the same type of raised cosine filter and the same number of tabs, specifically, 129. We focused on the FIR performance and speed rather than logic cell dimensions when we designed the digital filters. The designed digital FIR filter specifications are shown in Table 1, according to the HSDPA system and three WiMAX profiles.

| Table 1. FIR filter specification | ons. |

|-----------------------------------|------|

|-----------------------------------|------|

| Profile                 | HSDPA            | WiMAX            |                  |               |  |

|-------------------------|------------------|------------------|------------------|---------------|--|

|                         |                  | 7 MHz            | 3.5 MHz          | 1.75 MHz      |  |

| FIR type                | Raised<br>cosine | Raised<br>cosine | Raised<br>cosine | Raised cosine |  |

| Interpol. rate          | x 4              | x 4              | x 8              | x 16          |  |

| Decim. rate             | x 2              | x 4              | x 8              | x 16          |  |

| Rolloff factor          | 0.22             | 0.115            | 0.115            | 0.115/0.115   |  |

| # of Taps               | 129              | 129              | 129              | 129/129       |  |

| Sampling<br>freq. (MHz) | 64               | 64               | 64               | 64/8          |  |

| Cutoff freq.<br>(MHz)   | 2.8              | 3.5              | 2                | 2/1.2         |  |

| Coeff, width<br>(bits)  | 16               | 16               | 16               | 16/16         |  |

# II. Implementation of Digital IF Transceiver

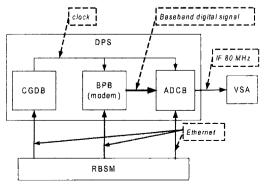

In this section, we introduce the implemented reconfigurable dual mode base station termed ReMO (Reconfigurable Mobile Convergence for a two-mode access system) briefly. In addition, we discuss about the presented Digital IF transceiver including PCB assembly module. The ReMO system, which incorporates a heterodyne architecture, was developed to verify the feasibility of applying SDR technology to a mobile communication base station reconfigurable to a HSDPA system based on WCDMA (Wideband Code Division Multiple Access) technology and to an IEEE 802.16d WiMAX system based on OFDM technology<sup>[14], [15]</sup>. The ReMO system uses SDR technologies in which modems and other functional blocks can be reconfigured easily, with software downloaded onto identical hardware platforms <sup>[16]</sup>.

The ReMO based on SDR technology was developed adopting the open hardware platform architecture of Advanced Telecom Computer Architecture (ATCA). Therefore, all the functional hardware blocks and components of the ReMO system, including the implemented Digital IF transceiver board, termed the Analog Digital Conversion Block (ADCB), follow the ATCA architecture. The Digital Processing Sub-system (DPS) rack, which manages the digital signal processing function and external network interfaces of the ReMO, is shown in Fig. 3 as the board marked with a dotted red line.

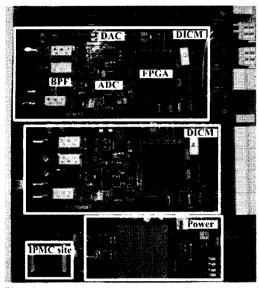

The implemented ADCB hardware board is represented in Fig. 4. It includes two Digital IF Conversion Modules (DICMs), an intelligent platform management controller module (IPMC), and a power module. The DICM module is mounted on an ADCB board as a daughter board for easy troubleshooting. The ADCB board can adopt two DICMs to support a two-path transmitter and receiver diversity. One DICM module on an ADCB board can process two channels simultaneously for one (A or B) diversity path. In the DICM, we used a commercial DAC chip, the AD9777, made by Analog Devices, which converts a digital signal to

Fig. 3. DPS rack of ReMO system

Fig. 4. Appearance of the ADCB board hardware

an analog signal [17]. The chip has x2/x4/x8 interpolation functionality internally and has an output sample speed as high as 400 Msps. In the HSDPA, the DAC is operating at a data rate of 245.76 (4 x 61.44) MHz and uses two half-band filters to achieve x 4 interpolation function internally. Finally, it outputs an IF analog signal of 80 MHz after being up-converted by 61.44 MHz via DCQM. The DAC is operating at a data rate of 256 (4 x 64) MHz for the WiMAX. In addition, we used a commercial off-the-shelf ADC chip, the AD6645, made by Analog Devices, which converts an analog signal to a digital signal [18]. The sampling clock for ADC and DAC on a DICM is provided by the PLL module on board, and alternated to others according to the configured system profiles and specific system clock speed. We selected an ADC sampling frequency of 61.44 MHz, i.e., interpolated by 16 with a fundamental frequency of 3.84 MHz for the HSDPA system. When ReMO is reconfigured to the WiMAX system, the transceiver is operating with a 64 MHz ADC sampling clock rate, i.e., interpolated by 8 with a fundamental frequency of 7 MHz \* 8/7 = 8 MHz incorporate with WiMAX 7 MHz profile. In addition, the demodulated signal is then down-sampled by 4 through a decimation filter adapted to each I and Q path. The adopted ADC satisfies both of these sampling clock rates, because it has a maximum 80 Msps sampling rate.

Generally, for a Digital IF transceiver, a DAC data sample rate must be considered in selecting the IF frequency. Because the adopted DAC can operate at a conversion rate of 400 Msps, theoretically, we can boost the IF frequency up to 100 MHz by the Nyquist sampling criteria. In the ReMO system, we selected an IF frequency of 80 MHz in both the HSDPA and WiMAX.

The overall digital signal processing for the Digital IF block is implemented with a Field Programmable Gate Array (FPGA) chip, the Vertex II series XC2VP70 (manufactured by Xilinx Inc.) [19]. This FPGA chip provides interpolation filtering, a digitally programmable NCO, DCOM, FA combining for a digital up-conversion process, and FA channelization, demodulation, and decimation filtering for down-conversion. The FPGA also provides a high-speed serial communication interface named Multi Gigabit Transceiver (MGT) between the ADCB board and the BPB modem board. Because MGT technology uses the digital low voltage differential signaling (LVDS) format, it is robust against noise and crosstalk between the physical signal lines. Therefore, it can provide a reliable high-speed communication interface. In ReMO, the speed of this serial communication is as high as 614.4 Mbps and 1.2288 Gbps for a HSDPA downlink and uplink transmission respectively, and 640 Mbps for both WiMAX links. The small sized IPMC module on an ADCB board provides management functions, such as reset sequence and power supply management. The IPMC is located on every blade of the ReMO system, following ATCA standards, and supports a Reconfigurable Base Station Manager (RBSM) to monitor each device of the blade over the IPM Bus. Here, the RBSM is a middleware platform that performs reconfiguration, management, and operation of the overall ReMO systems.

## IV. Test Results of the Digital IF Transceiver

In this section, we examine the experimental results of the presented Digital IF transceiver board. We conducted the performance test for a downlink by reconfiguring to other system profiles sequentially. The aim of the test was to identify the reconfigurability to other system profiles on the same hardware platform and to certify that the measured performance of the transceiver achieves the criteria that each standard demands.

#### 4.1 The test environments

The Fig. 5 represents the overall test configuration for downlink. The interface between the BPB and the ADCB is a fabric interface, which is one of the five ATCA backplane interfaces. The ADCB up-converts the digital baseband modem signal from a Baseband Processing Block (BPB) to an IF analog signal of 80 MHz. This analog IF signal was measured using Vector Signal Analyzer (VSA) equipment commercially available. The VSA measures the frequency response spectrum and constellation of the downlink IF transceiver output signal and provides the precise EVM value.

The system clock for the ADCB was a Phase Locked Loop (PLL) clock locked to the 10 MHz reference clock provided by the Clock Generation and Distribution Block (CGDB) board. The CGDB board generates and distributes the required clock signal for overall ReMO systems. The reconfiguration to the HSDPA system and to three WiMAX profiles was accomplished by downloading the corresponding FPGA configuration file for each system through a RBSM control. In addition, the reconfiguration function was verified by examining the frequency response spectrum and constellation of the downlink IF transceiver output signal. Table

Fig. 5. Overall test configurations

Table 2. Input test signal parameters

| Profile                | HSDPA            | WIMAX            |         |             |  |

|------------------------|------------------|------------------|---------|-------------|--|

|                        |                  | 7 MHz            | 3.5 MHz | 1.75<br>MHz |  |

| Duplexing              | FDD              | FDD              | FDD     | FDD         |  |

| Modulation &<br>Coding | 16 QAM<br>TC 3/4 | 64 QAM RS-CC 3/4 |         |             |  |

| Frame<br>Duration (ms) | 2                | 5                | 5       | 8           |  |

| CP                     | -                | 1/8              |         |             |  |

| N FFT                  | -                | 256              |         |             |  |

| N_used                 |                  | 200              |         |             |  |

| Channel                | HS-<br>PDSCH     | -                | -       | -           |  |

2 shows the major input signal parameters for each system to verify the transceiver performance.

For the HSDPA transmitter test, the generated signal at the BPB entering the ADCB through the MGT is a signal having 2 ms frame duration, a turbo-coded 16 QAM modulated signal, i.e., 16 QAM-TC 3/4. For WiMAX, the generated signal at the BPB is an OFDM signal having 5 ms frame duration, a code rate of 3/4 Reed-Solomon convolutional-coded and 64 QAM modulated signal, i.e., 64 QAM-3/4 modulation and coding scheme (MCS) with a different signal bandwidth according to each profile. Each profile of the WiMAX system had the same FFT size but different sub-carrier spacing according to the signal bandwidth of each profile. All input signals were 64 QAM modulated.

The considered performance criterion was EVM, which is the most widely used modulation quality metric in digital communications systems. EVM is the root-mean-square (rms) value of the error vector over time at the instants of the symbol clock transitions [20]. By convention, EVM is usually normalized to the outermost symbol magnitude at the symbol times and expressed as a percentage, as shown in the following equation:

$$EVM = \left(\frac{rms \ error \ vector}{outermost \ symbol \ magnitude}\right) \times 100\%$$

(5)

Moreover, EVM may be normalized to the square root of the average symbol power. In this way, EVM can be related to the SNR:

$$SNR = -20 * \log \left( \frac{EVM}{100\%} \right)$$

(6)

## 4.2 Test results on HSDPA performance

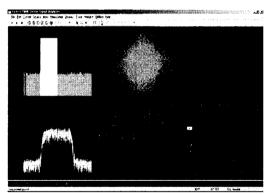

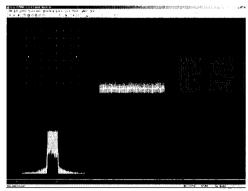

To verify reconfigurability to the HSDPA system according to the RBSM mode change commands, we measured the spectrum and constellation of the downlink IF output using VSA equipment that is commercially available. The measured EVM value of the signal is shown in Fig. 6 as -39.2 dB.

The minimum requirement for transmit modulation is that the EVM shall not be worse than 12.5 %rms when the base station is transmitting a composite signal that includes 16 QAM modulation <sup>[21]</sup>. The EVM value of 12.5 %rms is evaluated to the SNR of 18.1 dB according to Eq. (6). Considering the estimated SNR loss of 10 dB in the RF and an implementation margin of 5 dB, the output EVM value of the Digital IF transceiver should be larger than the SNR of 33.1 dB to meet the recommended criteria. As a result, the measured EVM value of -39.2 dB (SNR of 39.2 dB) satisfies the condition with a 6.1 dB margin.

Fig. 6. Performance of the HSDPA (EVM = -39.2 dB)

## 4.3 Test results on WiMAX performance

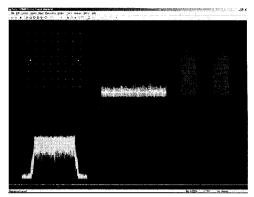

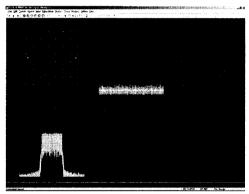

We also conducted the same test for the WiMAX systems. The test results of the three WiMAX profiles are presented in order in Figs. 7, 8, and 9. In a WiMAX system, the term Relative Constellation Error (RCE) is usually used rather than EVM, though these terms are equivalent. As can be seen in Figs. 7 through 9, a similar EVM value of less than -43 dB regardless of the operating WiMAX bandwidth profiles was obtained regardless of the operating WiMAX bandwidth profiles.

Fig. 7. Performance of the WiMAX 7 MHz profile (EVM = -43.2 dB)

Fig. 8. Performance of the WiMAX 3.5 MHz profile (EVM = -44.1 dB)

Fig. 9. Performance of the WiMAX 1.75 MHz profile (EVM = -43.6 dB)

The recommended allowed transmitter SNR performance of 64 QAM - 3/4 burst type MCS in [20] is less than -31 dB of EVM (and the same as 31 dB of RCE). This result indicates that the output EVM value of the Digital IF transceiver should be less than -40 dB to meet the recommended criteria considering the estimated 4 dB SNR loss of RF

and implementation margin of 5 dB. Additionally, the exact measured EVM values in this test were -43.2 dB, -44.1 dB, and -43.6 dB for the corresponding WiMAX 7 MHz, 3.5 MHz, and 1.75 MHz bandwidth profiles, respectively. Therefore, the measured EVM values of all three profiles satisfy the abovementioned condition with a 3 or 4 dB margin.

## V. Conclusions

In this paper, we suggested the software radio architecture of the reconfigurable Digital IF transceiver and verified the feasibility by implementing the transceiver that can support the HSDPA system and three WiMAX profiles using SDR technologies. Verification was performed using off-the-shelf equipment to examine the spectrum and the constellation on an IF output. In addition, the developed transceiver was successfully reconfigured to other systems, satisfying the recommended performance criteria of all supported system profiles.

If the suggested SDR technology based transceiver architecture is applied to a mobile communication base station, especially in upcoming 4G systems with various bandwidth profiles, rapid deployment to the upgraded technology would be possible with low cost and time to market consistently.

#### References

- [1] http://www.wimaxforum.org

- [2] http://standards.ieee.org

- [3] 3GPP TS 36.211 v0.2.2, "Technical Specification Group Radio Access Network; Physical Channels and Modulation (Rel.8)" 2006-12.

- [4] J. Mitola, "Software Radio Architecture Evolution: Foundations, Technology Tradeoffs, and Architecture Implications," IEICE Trans. Commun., Vol.E83-B, No.6, pp.1165-1173, Jun. 2000.

- [5] J. Mitola, "The software radio architecture," IEEE Commun. Mag., Vol.33, pp.26-38, May 1995.

- [6] http://www.sdrforum.org

- [7] David B.Chester, "Digital IF Filter Technology for 3G Systems: An Introduction," IEEE Commun. Mag., pp.102-107, Feb. 1999.

- [8] Won-Cheol Lee, Woon-Yong Park, "Implementation of SDR-Based Digital IF for Multi-Band W-CDMA Transceiver," IEICE Trans. Commun., Vol.E87-B, No.10, pp.2980-2990, Oct. 2004.

- [9] Vincent W. Leung, Lawrence E. Larson, Prasad S. Gudem, "Improved Digital-IF Transmitter Architecture for Highly Integrated W-CDMA Mobile Terminals," IEEE Trans. on Vehicular Tech., Vol.54, No.1, pp.20-32, Jan. 2005.

- [10] Shiann-Shiun Jeng, Shu-Ming Chang, Bor-Shuh Lan, "Multi-Mode Digital IF Downconverter for Software Radio Application," IEICE Trans. Commun., Vol.E86-B, No.12, pp.3498-3512, Dec. 2003.

- [11] Hiroshi Tsurumi, Hiroshi Yoshida, Shoji Otaka, Hiroshi Tanimoto, Yasuo Suzuki, "Broadband and Flexible Receiver Architecture for Software Defined Radio Terminal Using Direct Conversion and Low-IF Principle," IEICE Trans. Commun., Vol.E83-B, No.6, pp.1246-1253, Jun. 2000.

- [12] R. G. Vaughan, N. L. Scott, and D. R. White, "The theory of bandpass sampling," IEEE Trans. Signal Process., Vol.39, No.9, pp.1973-1983, Sept. 1991.

- [13] R.E. Crochiere and L.R. Rabiner, Multirate Digital Signal Processing, Prentice-Hall, 1983.

- [14] 3GPP TS 25.211 v5.6.0, "Technical Specification Group Radio Access Network; Physical Channels and mapping of transport channels onto physical channels (FDD) (Rel.5)" 2004-9.

- [15] 802.16-2004 IEEE Standard for Local and metropolitan area networks Part 16:Air Interface for Fixed Broadband Wireless Access Systems, 01 October 2004.

- [16] Duk-Bai Kim, Huirae Cho, Chanyong Lee, Gweon-Do Jo, Jin-Up Kim, "SDR-Based Reconfigurable Base Station Platform," IEICE Trans. Commun., Vol.E89-B, No.12, pp.3188-3196, Dec. 2006.

- [17] Analog Devices Inc.: AD9777, 16bit, 160MSPS, 2x /4x /8x Interpolating Dual TxDAC, D/A Converter.

- [18] Analog Devices Inc.: AD6645, 14bit, 80MSPS A/D Converter.

- [19] Xilinx Inc., Virtex<sup>TM</sup> II Pro and Virtex II Pro X FPGA User Guide, March, 2005.

- [20] Agilent Technologies, "Testing and Troubleshooting Digital RF communications Receiver Designs," Application Note 1314.

- [21] 3GPP TS 25.104 v5.9.0, "Technical Specification Group Radio Access Network; Base Station Radio transmission and reception (FDD)(Rel.5)" 2004-9.

## 유 봉 국 (Bong-Guk Yu)

정회원

1992년 2월 충남대학교 전자공학 과공학사 1994년 2월 충남대학교 대학원 전자공학과 공학석사 2007년 8월 충남대학교 대학원 전자공학과 공학박사 수료 1994년 1월~2000년 4월 SK

Telecom(주) 중앙연구원 선임연구원 2005년 3월~현재 한국전자통신연구원 선임연구원 <관심분야> SDR, CR, MIMO 모뎀 기술, OFDM,이동 통신 신호처리

## 나 성 웅(Sung Woong Ra)

종신회원

1976년 2월 서울대학교 전기공학 과 공학사 1978년 2월 한국과학기술원 전기 및 전자공학과 공학석사 1992년 8월 한국과학기술원 전기 및 전자공학과 공학박사 1980년 7월~현재 충남대학교 공

과대학 전자공학과 교수 <관심분야> 영상처리, 영상코딩, MPEG-IV, 화상회의 시스템