# BGA 검사 소켓 핀의 불량 분석 연구

김명식·배규식<sup>†</sup> 수원대학교 전자재료공학과

## Failure Analysis of BGA Test Socket Pins

Myung-Sik Kim and Kyoo-Sik Bae<sup>†</sup>

Department of Electronic Materials Engineering, The University of Suwon, Suwon, 445-743, Korea

(2008년 7월 2일 접수 : 2008년 9월 1일 최종수정 : 2008년 9월 2일 채택)

Abstract BGA test sockets failed earlier than the expected life-time due to abnormal signal delay, shown especially at the low temperature ( $-50^{\circ}$ C). Analysis of failed sockets was conducted by EDX, AES, and XRD. A SnO layer contaminated with C was found to form on the surface of socket pins. The formation of SnO layer was attributed to the repeated Sn transfer from BGA balls to pin surface and instant oxidation of fresh Sn. As a result, contact resistance increased, inducing signal delay. Abnormal signal delay at the low temperature was attributed to the increasing resistivity of Sn oxide with decreasing temperature, as manifested by the resistance measurement of SnO<sub>2</sub>.

Key words BGA Socket, failure analysis, fretting corrosion, SnO, contact resistance.

#### 1. 서 론

반도체 소자는 회로설계, 마스크 제작 등의 사전 공정, 웨이퍼 표면에 전자부품과 회로를 구성하는 가공(Fabrication) 공정, 웨이퍼 상의 칩을 개개로 잘라서 실장(Packaging) 하는 과정을 거쳐 최종적으로 검사(Test)를 통과하면 완 제품으로 만들어진다. 검사는 기본적으로 검사장비의 로 드보드(Load Board)에 장착된 소켓(Socket)을 실장된 소 자와 접촉시켜 전기적 특성을 평가하는 것이다. 이때 반 도체 소자의 외부단자와 직접 접촉하는 것은 검사 소켓에 돌출되어 있는 스프링(Spring or Pogo) 형태의 핀(Pin)으로 서 보통 Be/Cu 재질의 몸체에 표면을 Au/Ni 도금한 형 태이다.<sup>1,2)</sup> 이때, Au (0.2~1.0 µm)는 산화방지층으로, 그 리고 Ni (5~10 μm)은 납땜성을 향상시키고 기지층의 Cu 확산을 방지하는 역할을 한다. 한편, 최근에 많은 반도 체 소자의 실장은 BGA (Ball Grid Array) 형<sup>3)</sup>으로 만 들어지며, 이때 Sn계 무연 솔더 범프가 단자의 외부에 형성되어 있어 검사 시 핀과 직접 접촉하게 된다. 검사는 보통 상온 또는 고온(85~120°C), 그리고 저온(-5~-40°C) 에서 각각 한차례 실시한다.

그런데, 집적회로의 초미세화에 따라 소자의 피치(Pitch)

†Corresponding author

E-Mail: ksbae@suwon.ac.kr (K. S. Bae)

는 mm대로 작아지고 범프의 숫자는 수백 개 이상으로 증가함에 따라 핀의 숫자도 증가하였다. 또한 여러 개의 소자를 동시에 그리고 짧은 시간에 검사해야만 공정비를 낮출 수 있다. 이러한 초고속 대량 검사 과정에서 소켓 핀은 상온(또는 고온)과 저온에서 각각 한차례 반도체 소 자의 BGA 범프와 접촉하게 된다. 그런데, 소켓의 수명이 아직도 많은 남아 있는데도 몇몇 핀에서 수백 피코 초 (pS)의 신호지연(Signal Delay)이 발생하는 문제점이 최근 보고되었다. 그런데 이러한 신호지연은 고온에서보다는 저 온 시험에서 현저하게 나타나며, 신호지연이 발생한 소 자를 수동으로 시험하면 소자 자체는 정상으로 확인된다. 따라서 불량의 원인은 소자가 아니라 소켓에 있는 것으 로 나타나는 데, 문제가 된 소켓 핀의 저항을 측정하면 Table 1에서 예시한 바와 같이 특정 핀이 저온에서(-5℃) 비정상적으로 높은 저항 값을 나타낸다. 이러한 저항 증 가 현상은 여러 회사에서 제조한 모든 소켓에서 공통적 으로 발생한다. 문제는 이러한 신호지연이 일어나면 소자 자체는 결함이 없는데도 불량소자로 판정되어 폐기되거 나, 검사를 다시 해야 하므로 제조원가 상승의 큰 요인 이 된다는 것이다. 그런데, 소켓 핀에서 나타나는 이러한 문제점의 원인에 대해서는 아직까지 문헌으로 보고된 바 가 없다. 본 연구에서는 소켓 제조업체에서 제공한 불량 핀을 분석하고 모의실험을 통하여 결함의 생성 원인과 기 제를 규명하고자 하였다.

498 김명식 · 배규식

Table 1. Typical test resistance values of failed pins

|         |         | -       |

|---------|---------|---------|

| Pin No. | R.T.(Ω) | L.T.(Ω) |

| 1       | 0.356   | 0.571   |

| 2       | 0.541   | 0.555   |

| 3       | 0.523   | 0.551   |

| 4       | 1.785   | 4.380   |

| 5       | 0.503   | 3.453   |

| 6       | 0.590   | 0.626   |

| 7       | 0.518   | 0.621   |

|         |         |         |

### 2. 실험 방법

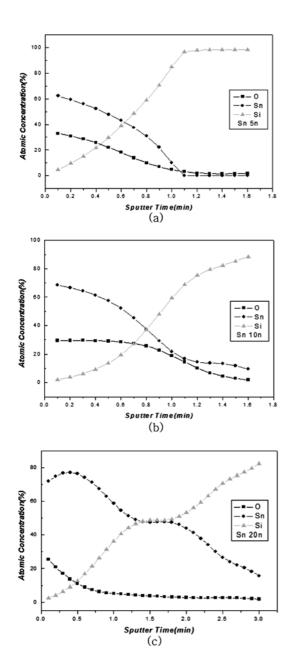

소켓 제조업체로부터 제공받은 사용 전의 핀과 높은 저 항을 나타낸 불량 핀의 표면을 별도의 전처리 없이 SEM (Scanning Electron Microscopy)으로 관찰하고 EDX (Energy Dispersive X-ray Spectroscopy)로 성분 분석을 하였으며, 표면 생성물의 화학 구조는 XRD (X-Ray Diffractometry)로 분석하였다. 또한 핀 표면의 깊이에 따른 화학 조성의 변화는 AES (Auger Electron Microscopy)에 의해 분석하였다. 한편, 고온과 저온에서 핀과 접촉하는 솔더 볼의 경도 차이를 알아보기 위하여 막대형 Sn-3.0Ag-0.7Cu 솔더를 같은 크기로 절단하여 5~80℃ 범위 에서 비커스 경도계로 측정하였다. 이때 저온은 액화질 소, 고온은 Hot Plate로 온도조절을 하였다. 또한, Sn 박 막의 산화속도를 확인하기 위하여 Si 기판위에 Sn을 DC 스퍼터로 5~20 nm 증착한 후  $5 \times 10^2$  Torr  $O^2$  분위기에 서 200℃ 3시간 산화 열처리한 후 깊이에 따른 조성을 AES로 분석하였다. 또한, 핀 표면에 생성되는 부착물로 추측되는 Sn 산화물의 온도에 따른 저항 변화를 알아보기 위하여 SnO2 나노 분말(입자크기 20 nm)을 1톤의 하중 으로 압축하고 800°C에서 3시간 소결하여 성형한 후 은 전극을 도포하여 만든 원통형의 시편을 델타 챔버에 넣어 -20~80°C 범위에서 저항을 측정하였다.

## 3. 결과 및 고찰

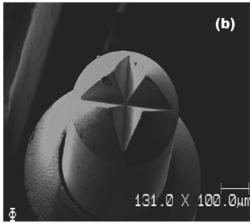

Fig. 1은 제조업체에서 제공한 편의 외관과 사용 전후의 솔더 볼과의 접촉부위를 저배율로 관찰한 SEM 사진이다. 검사 시 왕관(crown) 모양의 편 머리 부분이 솔더볼을 수 μm 깊이로 파고 들어가 압착을 하면서 전기적접촉이 일어난다. 사용 전에는 깨끗하던 접촉부위(Fig. 1-(b))가 반복 검사로 인해 검게 변하고 잔존물(debris)이 표면 곳곳에 부착되어 있음을 볼 수 있다(Fig. 1-(c)).

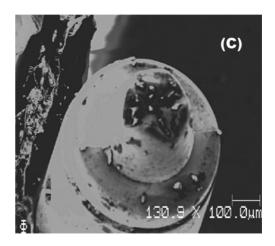

Fig. 2는 사용 전 및 약 10,000회 상은 및 저온 시험에서 사용한 소켓 핀의 머리 부분을 EDX로 분석한 결과이다. 사용 전의 핀(Fig. 2-(a))에는, 예상대로 표면층의 Au만이 검출되어 되었으나, 사용한 핀의 접촉 부분(검은 색)(Fig. 2-(b))에서는 Au외에 Ni, Cu, Sn, 그리고

**Fig. 1.** SEM micrographs of a socket pins : (a) overall appearance, (b) top view (before tests), and (c) top view (after tests).

상당량의 C과 O가 검출되었다. 이는 반복 접촉을 통해 Au 표면층이 일부 벗겨져 Ni층이 노출되고, 동시에 BGA 볼로부터 Sn이 전이되어 온 때문으로 판단된다. Cu가 검출된 것은 Ni층도 일부 벗겨졌기 때문이다. 한편, 접촉부위에서 멀리 떨어진 쪽에서는 사용 전의 상태를 유지

Fig. 2. EDX surface analysis results for socket pins : (a) before, and (b) after tests.

하여 Sn이 검출되지 않았다. 따라서 핀 표면의 위치와 사용회수에 따라 표면 상태는 다르게 나타남을 알 수 있다. 또한 핀 표면 곳곳에 산재하는 잔존물(Fig. 1-(c))에도 Sn은 검출되지 않았고 C (12 wt.%)가 다량 함유된 것으로 나타났다. 이로 미루어 C는 검사 챔비 안에서 발생되는 유기 오염물이 핀에 불규칙적으로 부착된 것으로 판단된다. 이 유기 오염물은 팩키지와 소켓이 장착되는 보드의 플라스틱 재료에서 기인하며 특히 고온에서 많이 발생하는 것으로 알려져 있다.4)

핀에 부착된 생성물의 깊이에 따른 조성을 확인하기 위하여 핀의 접촉 부위에 대해 AES 분석을 하였다(Fig. 3). Fig. 2의 EDX 표면 분석 결과에서와 같이 사용 전의 핀에서는 Au만이 균일하게 나타났다(Fig. 3-(a)). 반면, 사

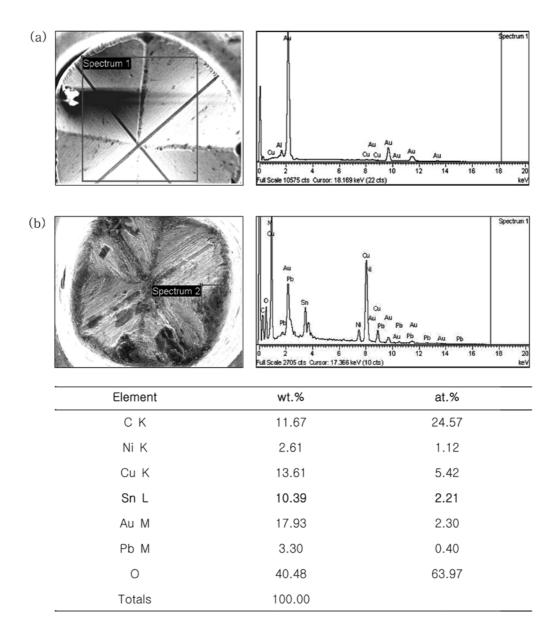

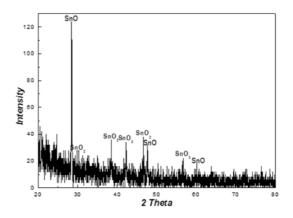

용한 핀(Fig. 3-(b))에서는 Sn, O, C 이 Cu 층 위에 축적되어 있음을 알 수 있다. 이 부위에서는 Au는 물론 Ni층 까지 벗겨져 Au와 Ni는 검출되지 않았다. 이 표면 층에서의 Sn과 O 원자 비율은 거의 일정하며 O가 Sn 보다 약간 많게 나타났다. 따라서 표면층은 균일한 조성의 Sn-O 화합물 층에 깊이에 따라 다른 양의 C(또는 C-O)이 불순물형태로 고용되어 있는 것으로 생각된다. 그리고, 표면 쪽의 C 오염물 함량이 높은 것은 곳 곳에 산재하는 잔존물의 영향으로 판단된다. 이 Sn 산화물 층의 두께는 스퍼터 시간으로부터 환산하면 약50 nm로 추정된다. 이 AES 결과로부터 확인된 Sn-O 층의 정확한 조성과 결정상을 확인하기 위하여 XRD 분석을 하였다(Fig. 4). 가장 큰 피크를 나타낸 상은 SnO

500 김명식 · 배규식

Fig. 3. AES depth profiles of socket pins: (a) before, and (b) after tests.

Sputter Time(min)

(b)

#### 이었으며 SnO<sub>2</sub>상도 부가적으로 나타났다.

두 금속표면이 진동에 의해 마찰하면서 부식이 일어나 는 현상을 마찰부식(Fretting Corrosion)이라 한다. <sup>4-7)</sup> 마 찰부식은 자동차나 공작기계 같은 기계류의 부품은 물론 커넥터, Wire Crimp 같은 전자부품에서도 흔히 일어나 는 현상이며, 특히 커넥터의 경우에는 광범위하게 연구 되어온 분야이다. 커넥터에서 마찰부식이 일어나는 일반 적인 순서는 두 금속표면이 진동에 의해 마찰을 반복하 면서 한 표면의 금속산화물이 다른 한 쪽으로 전이(Transfer) 하고 이 전이된 금속산화물이 쌓이고 또 떨어져 나가기 도 한다. 이러한 과정이 반복되면서 금속산화물의 두께가 증가하는 데, 금속산화물은 대개가 비저항이 높은 절연 체이므로 접촉저항(Contact Resistance)의 증가를 야기하 여 전기 접촉의 성능을 저하시키는 결과를 가져오게 된 다. 이때 두 금속의 경도가 다를 경우 연한(Soft) 금속 에서 단단한(Hard) 금속 쪽으로 전이가 일어난다. 그런 데 커넥터의 경우에는 두 금속표면이 나란히 평행으로 맞 닿아 있으며 계속적으로 상대적인 수평방향 운동을 하지 만, BGA 소켓의 경우에는 매번 한 쪽 금속, 즉 BGA 볼은 새로운 소자로 바뀌어 접촉되며 접촉하는 방향도 서로

Fig. 4. XRD patterns of tested socket pins.

**Fig. 5.** Changes in hardness of Sn-0.3Ag-0.7Cu solder as a function of temperature.

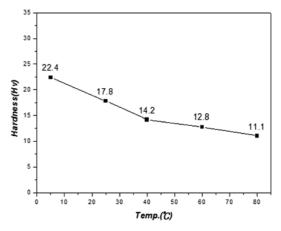

수직이다. 따라서, 소켓 핀에서 일어나는 접촉에 의한 불 량현상은 상대적으로 연한 금속인 무연솔더의 주성분인 Sn이 더 단단한 Au 도금 층으로 전이하면서 시작하는 것으로 생각할 수 있다. 이때, BGA 솔더 볼의 표면에 생성되어 있는 자연산화막(SnO 또는 SnO<sub>2</sub>)이 전이하는 경우를 생각할 수 있으나, 솔더의 표면에 생기는 Sn 자 연산화막의 두께가 수 nm에 지나지 않기 때문에<sup>8,9)</sup> 자 연산화막이 전이될 가능성은 희박하다. 왜냐하면 소켓의 핀이 솔더 볼을 파고드는 깊이는 수 μm로 자연산화막 두께보다는 훨씬 클 뿐 아니라 자연산화막은 취성이 높 아 반복되는 검사 과정에서 파쇄되어 막 형태보다는 입 자 형태로 남아 있어야 하지만 SEM 관찰에서 생성된 산 화막은 박막의 형태를 취하기 때문이다. 일단 BGA 볼 로부터 소켓 핀으로 전이된 금속 Sn은 산화되며, 이 과 정이 반복되어 Sn 산화물층이 형성되는 것으로 추론된다. 소켓 핀과 BGA 솔더 볼과의 반복 접촉 시 검사 온 도에 따라 솔더로 부터 핀으로 전이되는 Sn의 양은 솔 더의 경도에 의존한다. 가장 널리 사용되고 있는 무연솔 더인 Sn-3.0Ag-0.7Cu의 온도에 따른 경도 변화의 측정 결과를 Fig. 5에 나타내었다. 저온(5°C)에 비해 고온(80°C)에서는 경도가 약 반 정도로 감소하였다. 따라서, 검사는 고온과 저온에서 반복되어 실시되지만 Sn의 전이와산화는 고온검사 시 더 많이 발생하는 것을 의미한다. 그러나, 저항의 증가로 인한 불량 현상은 저온검사에서 우선적으로 발생하였다.

Sn 또는 Sn계 무연솔더에 생성되는 초기 자연산화막은 수 nm 두께의 SnO이며, 온도가 높거나 산화시간이길면 산소가 유입되는 표면층부터 SnO<sub>2</sub>로 변화하게 된

**Fig. 6.** AES depth profiles of Sn thin film after annealing at  $200^{\circ}$ C for 3hrs: (a) 5 nm, (b) 10 nm, and (c) 20 nm.

다. 그리고, 일단 표면에 자연산화막으로 형성되면 산소 의 Sn 내로의 확산속도가 매우 낮기 때문에 더 이상의 산화는 매우 느리게 진행된다. <sup>8,9)</sup> 소켓 핀의 경우에도 Sn 이 전이하여 산화되는 과정이 반복되는 데, 이를 모의실 험 하고자 가능한 한 얇게 Sn을 증착하고 산소분위기에서 열처리한 후 AES로 깊이에 따른 조성분석을 하였다. Fig. 6 에서 알 수 있는 바와 같이 솔더의 용융온도에 비해 매우 고온인 200℃에서 3시간이나 열처리하였지만 O가 Sn보다 원자 분률(atomic%)이 훨씬 작게 나와 산화가 충분히 진 행되지 않았음을 보여준다. Sn의 두께가 가장 얇은 5 nm 경우에도 같은 결과를 나타내었다. 이는 초기 자연산화 막이 생긴 후 더 이상의 산화는 거의 일어나지 않음을 보여준다. 그런데, 위의 Fig. 3과 4의 결과에서 핀 표면 에는 50 nm 정도의 SnO(SnO2)가 형성되었는데, 이것이 가능하기 위해서는 BGA 볼로부터 전이되는 Sn의 두께 는 nm 이하로 매우 얇아서, 전이되는 즉시 산화되기 때 문으로 볼 수 있다.

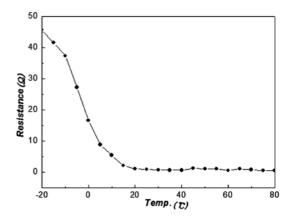

SnO₂는 센서로 널리 쓰이는 대표적인 가스 감응 물질이다. 센서의 동작온도가 300~400°C이므로 고온에서의 SnO₂ 특성은 매우 많이 연구되었으며, 온도가 올라가면비저항이 감소하는 반도체 특성을 갖고 있다. 10~12 반면 SnO₂의 저온에서의 특성과 SnO의 물성은 비교적 알려진 것이 없다. 그런데, 소켓 핀의 불량현상은 저온에서현저하므로 SnO₂의 저온에서의 온도에 따른 저항 변화를 델타 챔버를 이용하여 측정하였다. Fig. 7은 800°C에서 소결한 SnO₂ 후막에 대한 저항 값의 변화이다. 20°C까지는 거의 변화가 없다가 그 이하에서는 급격히 증가하여 고온에서와는 반대되는 경향성을 나타내었다. 이 현상은 솔-겔법으로 제조한 SnO₂의 비저항이 상온에서 0°C로 내려갈수록 증가하는 연구결과 110에서도 확인된다. 따라서, 불량 소켓 핀의 저항이 저온에서 약 3배 정도 높이나타난 것은 표면에 생성된 Sn 산화막의 저온 특성에 의

Fig. 7. Changes in electrical resistance of  $SnO_2$  thick films as a function of temperature.

502 김명식 · 배규식

한 것으로 추론된다. 그러나, SnO도 저온에서 비저항이 증가하는 지는 앞으로 실험을 통해 확인되어야 한다.

#### 4. 결 론

BGA 검사 소켓을 반복 사용할 때 저온검사 시 비정 상적인 신호지연이 나타나는 불량 현상이 보고되었다. 소 켓 제조업체에서 제공한 불량 소켓 핀의 표면을 EDX와 AES로 분석한 결과, Sn과 O가 균일한 조성으로 분포되 어 있고 깊이에 따라 다른 함량의 C이 검출되었다. 이 핀 표면에 생성된 층을 XRD로 분석한 결과 주된 결정 상은 SnO이었으며 두께는 약 50 nm이었다. 한편, C는 검사 챔버 안에서 발생되는 유기 오염물이 핀에 불규칙 적으로 부착된 것으로 판단된다. 따라서 표면층은 깊이 에 따라 다른 양의 C(또는 C-O)이 불순물형태로 고용 되어 있는 SnO층으로 분석되었다. 이 표면층은 BGA 무 연솔더의 주성분인 Sn이 핀으로 전이하고 산화하는 과 정이 반복되어 생성되며, 이 비저항이 높은 절연체인 Sn 산화물이 핀의 접촉저항 증가를 야기하고 따라서 신호지 연이 발생하게 된다. 특히, Sn-3.0Ag-0.7Cu 무연솔더의 경도가 저온(5°C)에 비해 고온(80°C)에서 약 반 정도로 나타나 고온에서의 Sn 전이와 산화가 더 현저할 것으로 판단되었다. 또한, Sn 및 Sn계 무연솔더는 nm 대의 자연 산화막이 일단 형성되면 더 이상의 산화는 매우 느리게 진 행된다. 따라서, 50 nm 정도의 SnO층이 형성된 것은 nm 이하의 매우 얇은 Sn이 핀 표면으로 전이하고 즉시 산화하기 때문이다. 한편,  $SnO_2$ 의 비저항이  $20^{\circ}$ C까지는 거의 변화가 없다가 그 이하에서는 급격히 증가하는 것으로 나타나, 불량 소켓 핀의 저항이 저온에서 약 3배 정도 높이 나타난 것은 표면에 생성된 Sn 산화막의 저온 특성에 의한 것이다.

## 참 고 문 헌

- 1. G. W. Mills, IEEE-CHMT, 2(4), 476 (1979).

- 2. I. Pal, Advanced Packaging, 14(11), 40 (2005).

- 3. K. K. Lee, E. G. Choi, Y. H. Chu, J. S. Kim, B. S. Lee and H. K. Ahn, Kor. J. Mater. Res., 18(1), 38 (2008).

- 4. M. Antler, IEEE-CHMT, 8(1), 87 (1985).

- 5. R. D. Malucci, IEEE-CHMT, 24(3), 399 (2001).

- J. W. Hong, K. W. Lee and K. S. Bae, Kor. J. Mater. Res. 16(7), 430 (2006).

- Y. W. Park, T. S. N. Sankara Narayanan and K. Y. Lee, Tribology Int'l, 41, 616 (2008).

- D. Burlacu, L. Nguyen and J. Kivilahti, ECTC-2005 (IEEE), 1874(2005).

- 9. S. G. Cho, J. Yu, S. K. Kang, and D. Y. Shih, J. of the Microelectronics & Packaging Soc., 12(1), 35 (2005).

- Z. A. Post and P.E. Ritt, IRE Trans. on Component Parts (IEEE), 5(2), 81 (1958).

- E. A. Morais, L. V. de A. Scalvi, V. Garaldo, S. J. L. Rebeiro and C. V. Santilli, Mat. Res., 6(4), 1516 (2003).

- J. K. Choi, P. S. Cho and J. J. Lee, J. Mater. Res., 18(4), 193 (2008).