(8-hydroxyquinoline)),

# Small Molecular Organic Nonvolatile Memory Cells Fabricated with in Situ O<sub>2</sub> Plasma Oxidation

Sung-Ho Seo, Woo-Sik Nam, and Jea-Gun Park

Abstract—We developed small molecular organic nonvolatile 4F2 memory cells using metal layer evaporation followed by O2 plasma oxidation. Our memory cells sandwich an upper α-NPD layer, Al nanocrystals surrounded by Al<sub>2</sub>O<sub>3</sub>, and a bottom α-NPD layer between top and bottom electrodes. Their nonvolatile memory characteristics are excellent: the V<sub>th</sub>, V<sub>p</sub> (program), V<sub>e</sub> (erase), memory margin (I<sub>on</sub>/I<sub>off</sub>), data retention time, and erase and program endurance were 2.6 V, 5.3 V, 8.5 V,  $\approx 1.5 \times 10^2$ ,  $1 \times 10^5$  s, and  $1 \times 10^3$ cycles, respectively. demonstrated symmetrical current versus voltage characteristics and a reversible erase and program indicating potential for terabit-level nonvolatile memory.

Index Terms—Organic nonvolatile memory, α-NPD, O<sub>2</sub> plasma, Al nanocrystals

#### I. Introduction

It has recently been reported that small molecular organic devices fabricated with a sandwich structure of top metal layer, small-molecular organic layer, middle metal layer, conductive organic layer, and bottom metal layer demonstrated nonvolatile memory behaviors such as  $I_{on}$  (reading after programming)/ $I_{off}$  (reading after erasing) of greater than  $1\times10^1$  and response times of  $\sim10$  ns. The organic conductive layers of these devices are AIDCN (2-amino-4, 5-imidazoledicarbonitrile), Alq<sub>3</sub> (Aluminum tris

1'biphenyl4-4''diamine (α-NPD) [1-8]. These small molecular organic nonvolatile memories need to use Al nanocrystals produced by aluminum (Al) evaporation at rates below 0.3 Å/s in the middle metal layer. As a result, they show very bad reproducible bi-stable switching current versus voltage (I-V) characteristics because the shape and distribution of Al nanocrystals embedded in small molecular organic layers are, respectively, irregular and nonuniform [9]. The current conduction mechanism by which they achieve nonvolatile memory could not be clarified because reported experimental results have not been repeatable [9~12]. Therefore, we proposed a new fabrication process that produces uniform metal nanocrystals (metal layer evaporation followed by in situ O<sub>2</sub> plasma oxidation) and used it to make 4F<sup>2</sup> memory cells with a sandwich structure with a-NPD layers separating the top and bottom Al electrodes from a middle layer consisting of Al nanocrystals surrounded by Al<sub>2</sub>O<sub>3</sub>. We then tested the devices' nonvolatile memory characteristics such as memory margin, data retention time, and endurance of erase and program cycles.

and

N,N'-bis(1-naphthyl)-1,

#### II. EXPERIMENTS

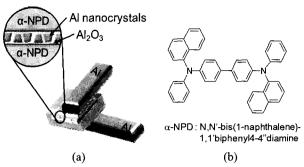

The  $4F^2$  crossover memory cells were fabricated with a sandwich structure consisting of bottom Al electrode, lower conductive organic layer ( $\alpha$ -NPD), Al nanocrystals surrounded by  $Al_2O_3$ , upper conductive organic layer ( $\alpha$ -NPD), and top Al electrode, as shown in Fig. 1. To isolate them from the substrate, the crossover cells are fabricated on thermally grown  $SiO_2$  on the Si wafer. To avoid contamination (e.g. H, O, N, Cl, and F atoms), all fabrication processes were carried out in the same

Manuscript received Feb. 27, 2008; revised Mar. 7, 2008. Nano-SOI Process Laboratory, Hanyang University, 17 Haengdangdong, Seongdong-gu, Seoul 133-791, South Korea E-mail: parkjgl@hanyang.ac.kr

Fig. 1. Organic nonvolatile  $4F^2$  memory cell with  $Al/\alpha$ -NPD/ (Al nanocrystals surrounded by  $Al_2O_3$ ) / $\alpha$ -NPD /Al device structure: (a) memory cell and (b) chemical structure of  $\alpha$ -NPD.

evaporator without breaking vacuum. The 80-nm-thick bottom Al electrode was thermally evaporated at a rate of  $5\,\text{Å/s}$  at a chamber pressure of  $10^{-5}$  Pa by using a first shadow mask with a line width of 1 mm. The  $30{\sim}50\text{-nm}$ -thick lower conductive organic layer ( $\alpha\text{-NPD}$ ) was thermally evaporated at a rate of  $1.0\,\text{Å/s}$  using a 7-mm-square second mask.

Next, the middle Al layer was thermally evaporated at a rate of 1.0 Å/s using a 4-mm-square third shadow mask, and the wafer was transferred to the O<sub>2</sub> plasma chamber (5x10<sup>-4</sup> Pa. 200 Watt, 40 volts, and 300 seconds) to oxidize the Al middle layer (Al nanocrystals surrounded by Al<sub>2</sub>O<sub>3</sub>). After this step, the surface morphology and chemical composition of the middle Al layer were observed using AES and XPS. Next, the second 35-nm-thick conductive organic layer (\alpha-NPD) was thermally evaporated at a rate of 1.0 Å/s using a 7-mm-square fourth mask. Finally, the 80nm-thick top Al electrode was thermally evaporated at a rate of a 5 Å/s using a fifth mask, which was cross patterned against the bottom Al electrode. All memory fabrication processes were carried out in an in situ multichamber apparatus simply by changing and aligning the masks. After fabrication, we first evaluated the current versus voltage (I-V) characteristics of the crossover cells. The sample for cross-sectional transmitted electronmicroscopy (X-TEM) observation was prepared using rough and fine focused-ion-beam (FIB) etching. The crystal structure of the Al nanocrystals was characterized using ultra-high-voltage TEM (1.2 MV).

# III. RESULTS AND DISCUSSIONS

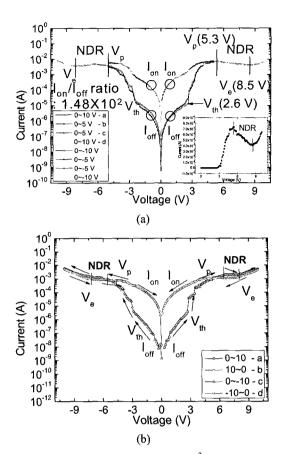

We first examined whether the devices described above had the potential for memory behavior. Fig. 2(a)

**Fig. 2.** Electrical characteristics of organic 4F<sup>2</sup> nonvolatile memory cell: (a) DC I-V curves and (b) symmetrical reversible I-V.

shows the I-V characteristics of our 4F<sup>2</sup> memory cells.

The current increased slightly at applied biases from 0 V up to  $V_{th}$  (2.6 V). This current is called  $I_{off}$ , and the state of the cell when Ioff flows is called either the lowcurrent state or the high-resistance state. The current increased abruptly at applied biases from V<sub>th</sub> to V<sub>p</sub> (program voltage: 5.3 V) and then decreased as applied bias increased from V<sub>p</sub> to V<sub>e</sub> (erase voltage: 8.5 V), showing a negative differential resistance (NDR) region (see the inset in Fig. 2(a)). Finally, the current increased slightly at applied biases above V<sub>e</sub> (8.5 V up to 10 V), which follows another low current state (called the second low current state). Note that the current path of I<sub>off</sub> is extended to the second low current state if the crossover cell is fabricated with a conductive organic layer (\alpha-NPD) without Al nanocrystals surrounded by Al<sub>2</sub>O<sub>3</sub>. After the first applied voltage was swept from 0 to 10 V (called erase), as shown in a in Fig. 2(a), the second applied bias was swept from 0 to V<sub>p</sub> or 5 V (called program), and then the current followed the highresistance state (I<sub>off</sub>). After the second applied bias (5 V:

program voltage) was swept, as shown by line b in Fig. 2(a), the third applied bias (reading after program) was again swept from 0 to  $V_p$  (5 V), as shown by line c in Fig. 2(a), and then the current followed Ion. This shows that the device reads Ioff (the low current state) at 1 V after erase (biasing 10 V above V<sub>e</sub>). Otherwise, the device reads I<sub>on</sub> (the high current state) at 1 V after program (biasing 5 V or  $V_p$ ). Surprisingly, the ratio of  $I_{on}$  to  $I_{off}$ (memory margin) is  $\approx 1.5 \times 10^2$ , which is a sufficient current difference (bistable resistance difference) for nonvolatile memory behavior. After the third applied bias (5 V: reading after program), was swept, as shown by line c in Fig. 2(a), the fourth applied bias (erase following reading after program) was swept from 0 to 10 V, as shown by line d in Fig. 2(a), and then the current followed I<sub>on</sub>, V<sub>p</sub>, NDR, and second low current state. The symmetry of the I-V characteristics between the positive and negative applied voltages gives us another way being non-volatile memory behavior. For example, the device reads I<sub>off</sub> at 1 V after erasing in the negative bias region (biasing -10 V) but reads Ion at 1 V after programming in the negative bias region (biasing -5 V). The  $V_{th}$ ,  $V_{p}$ , and  $V_{e}$  values obtained in several  $4F^{2}$ memory cells were uniformly distributed. Figure 2(b) shows the I-V characteristics of other 4F<sup>2</sup> memory cells as a reference for whether or not our memory cell can reversible process to charge or discharge electrons on Al nanocrystals while bias is applied. The current followed the I<sub>off</sub>, V<sub>th</sub>, V<sub>p</sub>, NDR, and V<sub>e</sub>, above V<sub>e</sub> (second low current state) path when the applied bias was swept from 0 to 10V, as shown by line a in Fig. 2(b). After erase, the current path followed the second low current state, V<sub>e</sub>, NDR, V<sub>p</sub>, and I<sub>on</sub> when the applied bias was swept back from 10 to 0 V, as shown by line b in Fig. 2(a). The current path shown by line d in Fig. 2(a) is very similar to the current path shown by line b in Fig. 2(b). The small current path difference between line d in Fig. 2(a) and line b in Fig. 2(b) is associated with the process difference in which the current path shown by line b in Fig. 2(b) precedes reading after program and is followed by erase, while the current path shown by line d in Fig. 2 (a) does program at the second low current state, followed by erase. The symmetrical I-V characteristics in the negative applied bias region were repeated like those in the positive applied bias region. It is obvious that this memory cell has a reversible process for erase

and program, which would produce erase and program endurance cycles sufficient for a commercial non-volatile memory. In addition, the symmetrical I-V for both positive and negative applied bias in small molecular organic non-volatile memory is completely different from that in resistive random-access memory [1-6, 13-17].

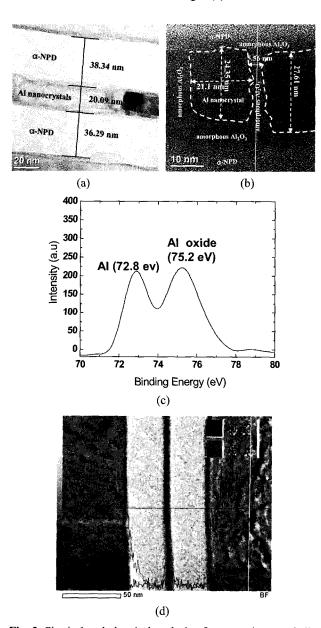

We also observed our 4F<sup>2</sup> memory cell physically and chemically. An X-TEM image of one of the 4F<sup>2</sup> memory cells we fabricated is shown in Fig. 3(a).

**Fig. 3.** Physical and chemical analysis of an organic nonvolatile  $4F^2$  memory cell: X-TEM image (at a 200-kV acceleration voltage), (b) magnified X-TEM image (at a 1.25-MV acceleration voltage), (c) XPS profile, and (d) EDS profile.

The thicknesses of the upper  $\alpha$ -NPD layer, the middle layer, and the lower  $\alpha$ -NPD layer were, respectively, about 38.34, 20.09, and 36.29 nm. A magnified X-TEM image (obtained at a 1.2-MV acceleration voltage) of the cell shown in Fig. 3(a) is shown in Fig. 3(b), where both the height and width of the uniformly distributed Al nanocrystals can be seen to be about 20 nm. The nanocrystals were well isolated from one another by the insulating Al<sub>2</sub>O<sub>3</sub> surrounding them, and the isolation distance was less than 5 nm. The chemical composition of the middle metal layer surface was obtained using Xray photoelectron spectroscopy (XPS) and is shown in Fig. 3(c). The surface of the middle metal layer was composition profile of Al (binding energy: 72.8 eV) and Al<sub>2</sub>O<sub>3</sub> (binding energy: 75.2 eV). In addition, the chemical composition profile of the X-TEM image in Fig. 3(b) was observed using energy dispersive x-ray spectrometry (EDS) and is shown in Fig. 3(d). The oxygen signal was delineated in the middle nanocrystal layer. From Figs. 3(a-d), it is evident that Al nanocrystals embedded in the α-NPD layer are well oxidized, isolated from one another, and thus covered by the insulating Al<sub>2</sub>O<sub>3</sub>. These physical and chemical results clearly indicate that metal layer evaporation followed by in situ O<sub>2</sub> plasma oxidation is an excellent process for fabricating a reliable small molecular organic nonvolatile memory embedded with Al nanocrystals surrounded by insulating Al<sub>2</sub>O<sub>3</sub>.

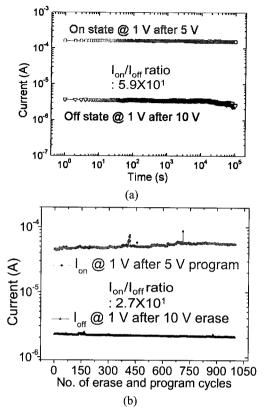

We estimated non-volatile memory characteristics, such as data retention time and endurance characteristics of erase and program cycles, for our small molecular organic nonvolatile memory, as shown in Fig. 4. The I<sub>on</sub> (reading at 1 V after program of 5 V) was  $\approx 1.5 \times 10^{-4}$  A, while the Ioff (reading at 1V after erase of 10 V) was  $\approx 2.5 \times 10^{-6}$  A. The ratio of  $I_{on}$  to  $I_{off}$  (memory margin) is  $\approx 6 \times 10^{1}$ , which is a sufficient current difference for nonvolatile memory behavior, as shown in Fig. 4(a). None of the current levels for the states changed significantly after a retention time of 1x10<sup>5</sup> sec. indicating that our memory may be nonvolatile from the viewpoint of data retention time. More evaluation about data retention will be done in the future. Figure 4(b) shows our memory cell's endurance characteristics for erase and program cycles. The ratio of Ion (reading at 1 V after program of 5 V) to Ioff (reading at 1 V after erase of 10 V) is  $\approx 2.7 \times 10^{1}$ . None of the current levels for the

**Fig. 4.** Electrical characteristics of organic  $4F^2$  nonvolatile memory cell: (a) pulse retention and (b) DC endurance.

states changed significantly after erase and program cycles of  $1 \times 10^3$ . This result indicates that our memory may be nonvolatile from the viewpoint of erase and program cycle endurance characteristics. We will further evaluate the commercial level of nonvolatile memory in the future.

# IV. CONCLUSIONS

The process used to fabricate reliable and uniform Al nanocrystals embedded in conductive organic layers is key engineering issue in producing reliable small molecular organic nonvolatile memory cells. Metal layer evaporation followed by in situ  $O_2$  plasma oxidation produces much more reliable layers than Al evaporation at rates below 0.3 Å/s. Devices fabricated with in-situ  $O_2$  plasma oxidation showed reversible current path for erase and program. That is, they exhibited nonvolatile memory behavior. The ratio of  $I_{on}$  to  $I_{off}$  (memory margin), data retention time, and erase and program endurance were  $\approx 1.5 \times 10^2$ ,  $1 \times 10^5$ s, and  $1 \times 10^3$  cycles, respectively. These experiments will contribute to the

development of a small molecular nonvolatile memory with multi-current states in one 4F<sup>2</sup> memory cell

## ACKNOWLEDGMENTS

This project was supported by "The National Research Program for 0.1-Terabit Non-volatile Memory Development" sponsored by the Korean Ministry of Commerce, Industry and Energy.

### REFERENCES

- [1] L. P. Ma, J. Liu, and Y. Yang, *Appl. Phys. Lett.* 80 (2002) 2997.

- [2] L. Ma, S. Pyo, J. Ouyang, Q. Xu, and Y. Yang, Appl. Phys. Lett. 82 (2003) 1419.

- [3] L. D. Bozano, B. W. Kean, M. Beinhoff, K. R. Carter, P. M. Rice, and J. C. Scott, *Adv. Funct. Mater.* 15 (2005) 1933.

- [4] J. He, L. Ma, J. Wu, and Y. Yang, *J. Appl. Phys.* 97 (2005) 064507.

- [5] S. Pyo, L. Ma, J. He, Q. Xu, and Y. Yang, J. Appl. Phys. 98 (2005) 54303.

- [6] L. D. Bozano, B. W. Kean, V. R. Deline, J. R. Salem, and J. C. Scott, *Appl. Phys. Lett.* 84 (2004) 607.

- [7] S. H. Kang, T. Crisp, I. Kymissis, and V. Buloviæ, Appl. Phys. Lett. 85 (2004) 4666.

- [8] J. Chen and D. Ma, *Appl. Phys. Lett.* 87 (2005) 023505.

- [9] J. G. Park, G. S Lee K. S. Chae, Y. J. Kim, and T. Miyata, J. Korean Phys. Soc. 48 (2006) 1.

- [10] J. Ouyang, C. Chu, C. Szmanda, L. Ma, and Y. Yang, Nat. Mater. 3 (2004) 918.

- [11] C. W. Chu, J. Ouyang, J. H. Tseng, and Y. Yang, Adv. Mater. 17 (2005) 1440.

- [12] R. J. Tseng, C. Tsai, L. Ma, J. Ouyang, C. S. Ozkan, and Y. Yang, *Nat. Nanotechnol.* 1 (2006) 72.

- [13] B. O. Cho, T. Yasue, H. Yoon, M. S. Lee, I. –S. Yeo, U. I. Chung, J. T. Moon, and B. I. Ryu, *Electron Devices Meeting*. 2006 IEDM (2006).

- [14] A. Beck, J. G. Bednorz, Ch. Gerber, C. Rossel, andD. Widmer, *Appl. Phys. Lett.* 77 (2000) 139

- [15] Krzysztof Szot, Wolfgang Speier, Gustav Bihlmayer, and Rainer Waser, Nature Material 5 (2006) 312-320

- [16] Chia-Hsun Tu, Yi-Sheng Lai, and Dim-Lee Kwong, Appl. Phys. Lett. 89 (2006) 062105

- [17] Qidan Ling, Yan Song, Shi J. Ding, Chunxiang Zhu, Daniel S. H. Chan, Dim-Lee Kwong, En-Tang Kang, and Koon-Gee Neoh, Adv. Mater. 17 (2005) 455

Jea-Gun Park of the Dept. of Electrical & Computer Engineering at Hanyang University, Seoul has been interested in defect engineering in semiconductor materials and nano-scale device development

since he received Ph.D. at Dept. of Material Science & Engineering, the North Carolina State University, U.S.A. His interests in defect engineering continued during a 17-year career at the Samsung Electronics Co., Semiconductor division (1985-2001) and broadened beyond defect engineering to the development of "Pure Silicon Wafer" (free of agglomerated defects in CZ Si) which has used as a standard wafer for DRAM devices. Since coming to Hanyang University in 1999 his research interests have developed 'Super Silicon Wafer" (pure silicon wafer containing extremely proximity gettering effect) which has used a standard wafer for flash memory devices. Currently, his mayor research areas are the development of strained Si on insulator C-MOSFET beyond 45nm, nano CMP slurry(STI, Poly Si, and Cu CMP), flexible and transparent Si OLED, and Terabit polymer random access memory. Now, he is the head of Advanced Semiconductor Material and Device Development Center at Hanyang university, the National Nano SOI Laboratory(sponsored by the Korean minister of science and technology), and The National Program for 0.1 **Terabit** Non-volatile Memory Development(sponsored by the Korean Ministry of Commerce, Industry and Energy).

In addition, he has taught industrial short courses, published three books in Korean, published 172 papers, given 227 talks, has issued 84 patents, and has submitted 147 patents.

**Sung-Ho Seo** got a Bachelor's of Engineering degree in Chemical Engineering from Hanyang University, Korea in 2004. And he received a Master of Engineering degree in Division of Nanoscale

Semiconductor Engineering from Hanyang University in 2006. Now, he is Ph. D's course in Division of Nanoscale Semiconductor Engineering, Hanyang University. His major research field is development of next generation terabit level nonvolatile memory, especially, development of high reliability small-molecular-weight organic nonvolatile memory.

Woo-Sik Nam received a Bachelor of Engineering degree in Electronics and Computer Engineering and a Master of Engineering degree in Electronic and Computer Engineering from Hanyang University, Seoul,

Korea, in 2005 and 2007, respectively. He is currently a Ph. D degree in Electronics and Computer Engineering, Hanyang University. His main research interests include next generation nonvolatile memory and organic nonvolatile memory specially.