## Design and Implementation of a SDR-based Digital Filter for CDMA Systems

Bong-Guk Yu, Young-Jo Bang, Dae-Ho Kim, Kyu-Tae Lee, Sung Woong Ra

**Abstract**—In this study, Software Defined Radio (SDR) technology-based digital filterbank architecture applicable to a multiple-channel processing system such as a wireless mobile communication system using Code Division Multiple Access (CDMA) technology is proposed. The technique includes a micro-processor to redesign Finite Impulse Response (FIR) filter coefficients according to specific system information and to download the filter coefficients to one digital Band Pass Filter (BPF) to reconfigure another system. The feasibility of the algorithm is verified by computer simulation and by implementing a multiple-channel signal generator that is reconfigurable to other system profiles, including those of a Wideband Code Division Multiple Access (WCDMA) system and a CDMA system.

Index Terms—Software Defined Radio (SDR), Filter, FIR, WCDMA, CDMA.

#### 1 INTRODUCTION

ULTIPLE-channel systems such second-generation mobile digital systems, Interim Standard (IS)-95 Division Multiple Access (CDMA) systems with a frequency bandwidth of 1.25 MHz for each Frequency Assignment (FA), and third-generation Wideband Code Division Multiple Access (WCDMA) systems with a 5 MHz bandwidth for one FA necessarily require a filtering operation to process each channel using a filter bank [1]-[2]. As a mobile communication service provider that deploys a mobile communication network with a CDMA

• Bong-Guk Yu is with Electronics and Telecommunications Research Institute (ETRI), Daejon, Korea (phone: +82 42 860 5681). E-mail: bgyu2@etri.re.kr

Young-Jo Bang is with Electronics and Telecommunications Research Institute, Korea.

E-mail: yjbang@etri.re.kr Dae-Ho Kim is with Electronics and Telecommunications Research

Dae-Ho Kim is with Electronics and Telecommunications Research Institute, Korea.

E-mail: daeho@etri.re.kr

Kyu-Tae Lee is with Kongju National University, Chungnam, Korea.

E-mail: ktlee@kongju.ac.kr

Sung Woong Ra is with Chungnam National University, Daejon, Korea.

E-mail: swra@cnu.ac.kr

Manuscript received July 25, 2008; revised September 20, 2008. This work was supported in part by the Korea (Rep. of) MIC (Ministry of Information adn Communication).

system generally uses a multiple channels, equipment such as a CDMA signal generator or a relay using the CDMA technology must generate or relay multiple FA signals. Such a multiple-channel system necessarily requires a filtering operation using a filter so as to pass only a desired band of signals and not pass a non-desired band of signals. Usually, analog Surface Acoustic Wave (SAW) filters are normally used in IF (Intermediate Frequency) bands for a cellular handset and a relay station for cellular mobile communication [3].

In multiple-channel processing systems, the number of Band Pass Filters (BPF) used to process a channel signal is equal to the number of channels processed by the BPF [4]. Therefore, a conventional multiple-channel processing system is limited as both the size and cost increase as the number of processed channels increases. In addition, each multiple-channel system has its own system bandwidth. Upcoming 4G mobile systems based on Orthogonal Frequency Division Multiplexing (OFDM) technology have a range of system bandwidth profiles [5]-[7]. Thus, a type of software radio architecture that can flexibly adapt to a range of system profiles is required for multiple-channel filtering processing [8]-[9].

Software Defined Radio (SDR) technology is a promising feature for the next generation of mobile communications and the associated measurement system. It makes it possible to reconfigure required system profiles through software changes on an identical hardware platform. As it adopts software technology and various DSP (Digital Signal Processing) technologies such as digital filtering onto the IF and RF areas due to recent increase in the Analog-to-Digital Conversion (ADC) sampling speed, it is able to provide a high-performance and cost-effective solution in different systems [10].

The purpose of the present study is to provide a SDR-technology-based digital filter bank architecture that incorporates the advantages of changing the filter coefficients of one digital BPF and enabling the selective processing of each channel, thereby providing an efficient multiple-channel processing system. The feasibility of the algorithm was verified by implementing a multiple-channel signal generator that is reconfigurable to other system profiles, including those for a WCDMA system and a CDMA system. This paper is organized as follows. In Section 2, the novel digital filterbank architecture using one digital filter is presented. In Section 3, implementation of the multiplechannel signal generator is discussed, and its experimental results are presented to verify the suggested filtering algorithm. Finally, conclusions are presented in Section 4.

# 2 DESIGN OF RECONFIGURABLE FILTERBANK ARCHITECTURE

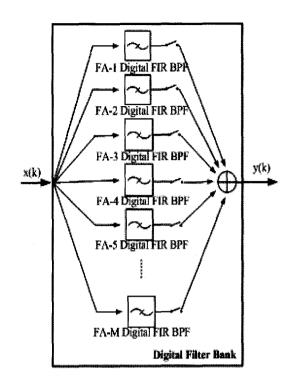

In this section, the suggested SDR-based reconfigurable digital filterbank architecture is introduced. A general block diagram of digital filter bank for a multiple-channel processing system is shown in Fig. 1. The typical digital filterbank includes M number of BPFs, and the output signal y(k) is the sum of the signal output by filtering an input signal x(k) according to the switch selection through the first to the M-th BPFs.

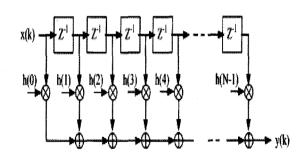

The conventional structure of a general Finite Impulse Response (FIR) BPF of the digital filterbank shown in Fig. 1 is presented in Fig. 2. As shown in Fig. 2, when the digital FIR BPF has N-numbered filter taps, the filter includes N-1 delay elements. Here, filter coefficients

Fig. 1. Typical digital filterbank

Fig. 2. Conventional digital FIR filter structure

h(n) respectively multiplied to signals passing through the first to (N-1)-th delay elements are denoted as h(0), h(1), h(2), ..., h(N-1).

In Fig. 1, if the digital filterbank of a general multiple-channel processing system includes M numbered BPFs, the output signal y(k) is the sum of the signal output after filtering an input signal x(k) according to the switch selection for each channel, as in the following equation:

$$y(k) = w_1 y_1(k) + w_2 y_2(k) + \dots + w_M y_M(k)$$

$$= w_1 \sum_{n=0}^{N-1} h_1(n) x(k-n)$$

$$+ w_2 \sum_{n=0}^{N-1} h_2(n) x(k-n) + \dots$$

$$+ w_M \sum_{n=0}^{N-1} h_M(n) x(k-n)$$

$$w_m = 0, \text{ if } FA = "OFF"$$

$$w_m = 1, \text{ if } FA = "ON"$$

$$(1)$$

Here, N is the number of filter coefficients and  $w_m$  is defined as a variable that is either 0 or 1 according to the ON/OFF state of the channel as input information of individual system profiles.

The channel output signal of the m-th BPF represented by  $y_m(k)$  can be achieved by the convolution of x(k) with the m-th BPF which has the filter coefficient of  $h_m(n)$ . As shown in (1), in typical multiple-channel processing systems, the number of BPFs for processing multiple-channel signals is equal to the number of channels to be processed by the BPF. Therefore, the required number of BPFs increases as the number of processed channels increases. As a result, factors such as the implementation complexity, size and cost for processing a channel also increase.

This paper proposes simple and efficient digital filterbank architecture to replace multiple BPFs with one BPF using SDR technology. It involves the use of a micro-processor to calculate the filter coefficient of the BPF according to the input information such as the system profiles and the channel ON/OFF status information. The output signal y(k) in (1) can be expressed as the following alternative form:

$$y(k) = \sum_{n=0}^{N-1} \{w_1 h_1(n) + w_2 h_2(n) + \dots + w_M h_M(n)\} x(k-n)$$

$$= \sum_{n=0}^{N-1} h_{all}(n) x(k-n)$$

(2)

Here,  $h_{all}(n)$ , which is the impulse response of the overall digital filterbank, is the total sum of the filter coefficients for each channel,  $h_1(n)$ ,  $h_2(n)$ ,  $h_3(n)$ , ...,  $h_M(n)$ . In addition, the final filter coefficients  $h_{all}(n)$  may be expressed with the  $h_M(n)$  and the ON or OFF state information of each channel when all digital FIR BPFs have N filter taps.

$$h_{all}(n) = \sum_{m=1}^{M} w_m h_m(n), n = 0, 1, 2, \dots N - 1$$

$$w_m = 0, \text{ if } FA = "OFF"$$

$$w_m = 1, \text{ if } FA = "ON"$$

(3)

Where

$$h_m(n) = h_B(n) \cdot f_m(n)$$

$$= h_B(n) \cdot exp(j2\pi f_m n/f_s)$$

$$m = 1, 2, \dots M$$

(4)

Here,  $h_B(n)$  is a Low Pass Filter (LPF) coefficient,  $f_m(n)$  is the center frequency of the m-th channel, and  $f_s$  is the sampling frequency.

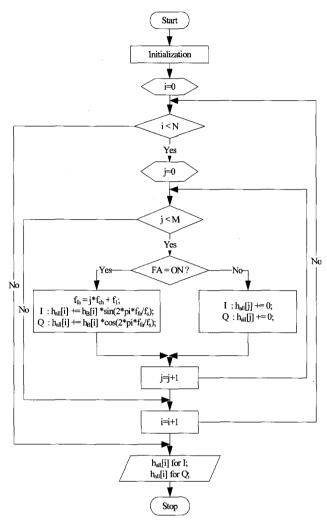

Using the suggested filtering method based on digital low-IF technology, M BPFs with the filter coefficients  $h_m(n)$  can be replaced by one BPF with the final filter coefficients  $h_{all}(n)$ . Fig. 3 is a flowchart showing the generation of the filter coefficients,  $h_{all}(n)$  in a micro-processor. Here, M is the total number of channels and N is the total number of filter taps.

The processor determines whether the channel is in an ON state or an OFF state corresponding to the channel information entered through the user interface. If the channel is determined as in an ON state, the processor calculates the filter coefficients using the equation below and stores these values in the memory.

$$f_{f\dot{a}} = j * f_{ch} + f_1;$$

$$I : h_{all}(i) + = h_B(i) * \sin(2 * \pi * f_{fa}/f_s);$$

$$Q : h_{all}(i) + = h_B(i) * \cos(2 * \pi * f_{fa}/f_s);$$

(5)

Here,  $f_f a$ ,  $f_{ch}$ ,  $f_1$ , and  $f_s$  represent the center frequency of each FA, the FA spacing, the center frequency of the first FA, and the sampling

Fig. 3. Flowchart of the proportional filter coefficients design algorithm

frequency, respectively. In 5,  $h_B(n)$  is given as a LPF coefficient of the system and  $h_{all}(i)$  is a value obtained by accumulating a given calculated value to a  $h_{all}(i)$  value as the calculated sum of the previous channel. Equation (5) expresses (4) as in-phase and quad-phase filter coefficients, which are orthogonal modulation values.

The micro-processor, which stores the initialization values shown in Table 1 for each system profile, the total number of channels of the system, the number of taps, the low-pass filter coefficients, the sampling frequency, the spacing between the channels, and the center frequency of the first channel, generates a filter coefficient using the information according to

#### TABLE 1 Initialization Variables

| Variables | Descriptions                                     |  |

|-----------|--------------------------------------------------|--|

| M         | total number of FAs of a multiple-channel system |  |

| N         | number of taps                                   |  |

| $h_B(n)$  | low-pass filter coefficients                     |  |

| $f_s$     | sampling frequency [MHz]                         |  |

| $f_{ch}$  | FA spacing [MHz]                                 |  |

| $f_1$     | center frequency of 1st FA [MHz]                 |  |

the application of the channel selection signal. This information may be received from a channel selection input unit or may be programmed by the micro-processor in advance.

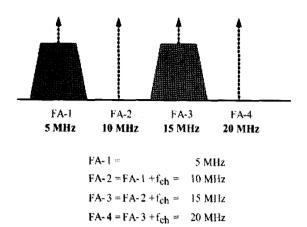

For example, if the total channel numbers of the multiple-channel system M is 4, if the channel spacing is given as 5 MHz, and if the center frequency of the first channel is given as 5 MHz, the center frequencies from the first channel to the fourth channel are obtained as 5, 10, 15, and 20 MHz, respectively. The controller receives the four-bit signal "1010" as the selection information from the channel selection input and stores the ON/OFF information of each channel, for example where the first channel = "ON", the second channel = "OFF", the third channel = "ON", and the fourth channel = "OFF". After the controller stores each channel as ON or OFF, the controller calculates the final N low-IF band filter coefficients by multiplying the center frequencies,  $f_j = \sin(2*\pi*f_{fa}*t)$  for the in-phase signal and  $f_j = \cos(2*\pi*f_{fa}*t)$ for the quad-phase signal of each ON state channel to the predetermined LPF coefficient of  $h_B(n)$ . It then sums the multiplied values. The controller generates a filter coefficient using the center frequency and the ON/OFF information of each channel such that the output spectrum shown in Fig. 4 may be output.

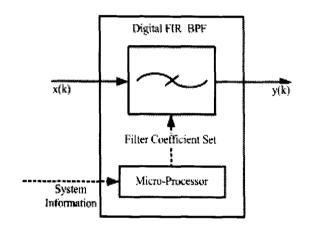

The multiple-channel filterbank system according to the suggested SDR-based digital filtering technique is shown in Fig. 5. The controller in Fig. 5 receives system profiles and channel selection information and calculates the filter coefficients  $h_{all}(n)$  of the BPF so that it may simultaneously and selectively generate at least one channel by one BPF.

Fig. 4. Signal generation example (when M=4)

Fig. 5. Suggested digital filerbank Structure

### 3 IMPLEMENTATION AND TEST RESULTS OF A MULTIPLE-CHANNEL SIGNAL GENERATOR

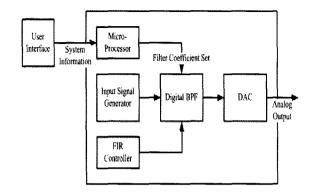

In this section, simulation results of the proposed algorithm and the implemented multiple-channel signal generator to verify the feasibility of the proposed algorithm is presented for the specific system profiles such as WCDMA and CDMA system. Fig. 6 shows a block diagram of the implemented multiple-channel signal generator, and includes a microprocessor, an input signal generator, a digital BPF, a FIR controller, and a digital-to-analog converter (DAC).

The user interface is used to enter system information such as the system profiles and channel information of the state ON or OFF

Fig. 6. The architecture of the implemented multiple-channel signal generator

TABLE 2

Initialization Variables of the Implemented

System Profiles

| Variables | System Profiles |      |  |

|-----------|-----------------|------|--|

| variables | WCDMA           | CDMA |  |

| M         | 4               | 14   |  |

| N         | 240             | 960  |  |

| $h_B(n)$  | -               | -    |  |

| $f_s$     | 50              | 50   |  |

| $f_{ch}$  | 5               | 1.25 |  |

| $f_1$     | 5               | 3.75 |  |

of the respective channels. This can include equipment such as a computer, a user terminal, and a keypad. The signal transmission between the user interface and the micro-processor located in the multiple-channel generator can be realized by a universal input/output serial interface. The micro-processor, which stores the initialization values shown in Table 2 for each system profile, generates filter coefficients  $h_{all}(n)$  according to the algorithm shown in Fig. 3. The micro-processor then reconfigures the digital BPF by downloading the filter coefficients.

The input signal generator generates an input signal that is applied to the digital BPF. The generated signal may be a random signal or a PN sequence signal, as the implemented multiple-channel generator is used as a signal generator with the suggested algorithm. If the suggested filtering algorithm is used with IF signal filtering for a CDMA relay system, the input may become an uplink CDMA signal that is transmitted to the base station.

Fig. 7. Simulated output spectrum of a WCDMA system(a) and a CDMA system(b)

The BPF filters the input signal applied from the input signal generator using the changed filter coefficient and outputs the filtered signal. The digital BPF is reconfigured to other system profiles through downloading with a filter coefficient set in real time. The filter coefficient of the digital BPF is changed according to the application of the filter coefficient generated by the controller. The BPF can be a Field Programmable Gate Array (FPGA) or a digital signal processor chip. Next, the FIR controller provides a control signal and an operation clock signal for the digital filtering of the BPF in real-time, and controls an internal register configuration that drives the DAC. The DAC converts the digital signal that is output after filtering by the BPF into an analog signal for measurement. Additionally, the DAC output signal can be up-converted to a higher RF band signal.

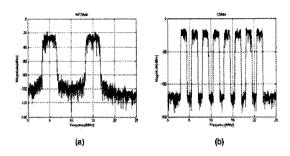

The suggested algorithm was simulated with MATLAB to verify the feasibility according to the flow chart shown in Fig. 3. The initialization variables adopted for the simulation have parameters that are identical to those on Table 2. The simulation results are shown in Fig. 7 for a WCDMA system and a CDMA system, respectively. The figure shows that the proposed algorithm using one BPF with the previously designed LPF filter coefficients successfully generates the multiple-channel signals that are centered on each different channel frequency.

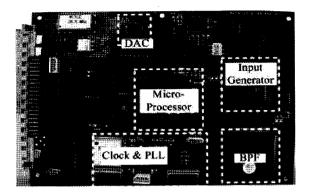

The implemented hardware board of the multiple-channel signal generator is shown in Fig. 8. It includes a commercial-off-the-shelf (COTS) digital FIR filter chip, a micro-

Fig. 8. Appearance of the multiple-channel signal generator hardware

processor, a clock supply module, Complex Programmable Logic Devices (CPLD), and a DAC. The adopted FIR filter chip has a maximum operating speed of 83 MHz and filter coefficients with a resolution of 12 bits. A Z-80 series micro-processor is in charge of the operational control of the overall system, the user interface, and the filter coefficient calculation according to the intended system profiles. The micro-processor has a maximum clock speed of 30 MHz, a 20-bit address bus and an 8-bit data bus. A commercial DAC chip, the AD9772 by Analog Devices was used; converts a filtered digital signal to an analog signal [11]. The chip, which has 14-bit resolution, can operate at a maximum conversion rate of 160 Msps and shows 74 dBc of Spurious Free Dynamic Range (SFDR) when the input analog bandwidth is 25 MHz. The DAC chip operates at an on board system clock speed of 50 MHz.

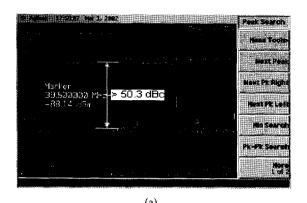

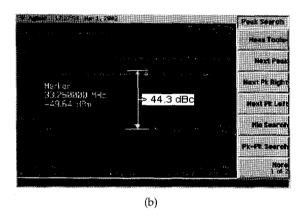

Fig. 9(a) shows the output signals of the implemented multiple-channel signal generator at a low IF spectrum. In the example shown in Fig. 9(b), the BPF is reconfigured according to the filter coefficients generated by the microprocessor according to the user interface applying the WCDMA system profile and channel selection information to activate the first and third channels. Fig. 9(b) illustrates the output signals of the generator when reconfigured to a CDMA system.

Normally, RF performance tests such as an Inter-Modulation (IM) performance test of RF devices, antennas, relay systems, and cables

Fig. 9. Output of the generator when reconfigured to a WCDMA system (a) and to a CDMA system (b)

require at least two simultaneous signal generator outputs. However, these tests can be cost-effectively performed using a single set of equipment when adopting the proposed algorithm. Moreover, SDR technology enables the multiple-channel signal generator to be reconfigurable to other standard profiles that have been adopted in existing cellular, PCS, WCDMA or OFDM mobile communication systems through filter coefficients that can be downloaded onto identical hardware platforms.

#### CONCLUSIONS

In this paper, a novel digital filtering algorithm based on SDR technology that enables reconfiguration to other system profiles through software changes is proposed. The proposed algorithm uses one digital FIR filter to process multiple channels, enabling it to provide the simple and efficient filtering typically used in the relay system of a mobile communication system. Therefore, if the proposed algorithm is applied to a cellular relay system, the analog SAW filter and the RF switch in such a system can be replaced with one digital BPF using SDR technology regardless of the system profile.

Additionally, an implemented multiplechannel signal generator that can support WCDMA and CDMA profiles is presented. This verifies the feasibility of the proposed algorithm, as shown in computer simulation results. SDR technology enables the digital filterbank to be reconfigurable to standard profiles, such as that of a multi-code CDMA system, through filter coefficients that can be downloaded onto identical hardware platforms. In the same way, any type of signal can be generated, including those used in upcoming fourth-generation mobile systems based on multi-channel OFDM technology.

#### REFERENCES

- [1] TIA/EIA/IS-95, Mobile Station-Base Station Compatibility Standard for Dual-Mode Wideband Spread Spectrum Cellular Systems, July 1993.

- [2] 3GPP TS 25.104 v5.9.0, Technical Specification Group Radio Access Network; Base Station Radio transmission and reception (FDD) (Rel.5), September 2004.

- [3] Clemens C.W. Ruppel, L. Reindl, R. Weigel, SAW Devices and Their Wireless Communications Applications, IEEE Microwave Magazine, pp.65-71, June 2002.

- R.E. Crochiere and L.R. Rabiner, Multirate Digital Signal Processing, Prentice-Hall, 1983.

- [5] http://www.wimaxforum.org

- http://standards.ieee.org

- [7] 3GPP TS 36.211 v0.2.2, Technical Specification Group Radio Access Network; Physical Channels and Modulation (Rel.8), December 2006.

- [8] J. Mitola, Software Radio Architecture Evolution: Foundations, Technology Tradeoffs, and Architecture Implications, IEICE Trans. Commun., vol.E83-B, no.6, pp.1165-1173, June 2000.

- [9] J. Mitola, The software radio architecture, IEEE Commun. Mag., vol.33, pp.26-38, May 1995.

- [10] http://www.sdrforum.org[11] Analog Devices Inc.: AD9772A, 14bit, 160 MSPS, TxDAC+ with 2x Interpolation Filter.

Bong-Guk Yu received the B.S. and M.S. degree in electronics engineering from Chungnam National University, Korea, in 1992 and 1994, respectively. From 1994 to 2000, he was with SK Telecom R and D center, Seoul, Korea, engaged in research on mobile communication systems and engineering. Since March 2005, he has been with Electronics and Telecommunications

Research Institute (ETRI) in Korea, and has engaged in the research and development of the 4th generation mobile communication systems. His research interests include the wireless communication systems, Mixed signal processing, software defined radio (SDR) and cognitive radio.

Sung Woong Ra received the B.S. degree in electrical engineering from Seoul National University, Seoul, and the M.S., Ph.D. degrees in electronics engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 1976, 1978 and 1992, respectively. He joined Chungnam National University and is now a professor in the De-

partment of Electronics Engineering. His research interests are image signal processing and image coding.

Young-Jo Bang received the M.Sc. and Ph.D. degrees in electrical engineering from the Korea Advanced Institute of Science and Technology (KAIST), Taejon, Korea, in 1991 and 1997, respectively. In 1997, he joined Electronics and Telecommunications Research Institute (ETRI), Taejon, Korea, where he is currently a Senior Member of Research Staff. His re-

search interests include multiple-input multiple-output (MIMO), mobile WiMAX systems, and iterative detection/decoding.

Daeho Kim received the B.S. and M.S. degrees from the Kyongpook National University, Korea, in 1989 and 1991, respectively, and the Ph.D. degrees from the Chungnam National University, Korea, in 2005, all in electronics engineering. He is currently an Team Leader in Electronics and Telecommunications Research Institute (ETRI), Korea. His research interests include broad-

band wireless communications, DSP and VLSI applications, and multimedia signal processing.

**Kyutae Lee** received his B.S. degree in Electronics Engineering from Korea University, Korea, 1984 and M.S. degree in Electronics Engineering from Korea University, Korea, 1986 and Ph.D. degree in Computer and Electronics Engineering from Korea University in 1991. He joined the faculty of Kongju National University, Korea where he is currently a professor

in Division of Infomation Communication Engineering. His research interests include DSP programming, Reconfigurable open architecture, Software Defined Radio system and Circuit and System. He is a member of Institute of Webcasting, Internet TV, and Telecommunication.