# A 1.2 V 7-bit 1 GS/s CMOS Flash ADC with Cascaded Voting and Offset Calibration

Young-Chan Jang\*, Jun-Hyun Bae\*, Ho-Young Lee\*\*, Yong-Sang You\*\*, Jae-Whui Kim\*\*, Jae-Yoon Sim\*, and Hong-June Park\*

Abstract—A 1.2 V 7-bit 1 GS/s CMOS flash ADC with an interpolation factor of 4 is implemented by using a 0.13 μm CMOS process. A digital calibration of DC reference voltage is proposed for the 1<sup>st</sup> preamp array to compensate for the input offset voltage of differrential amplifiers without disturbing the high-speed signal path. A 3-stage cascaded voting process is used in the digital encoder block to eliminate the conescutive bubbles up to seven completely, if the 2<sup>nd</sup> preamp output is assumed to have a single bubble at most. ENOB and the power consumption were measured to be 5.88 bits and 212 mW with a 195 MHz 400 mV<sub>p-p</sub> sine wave input.

Index Terms—Flash ADC, offset, reference calibration, voting

# I. Introduction

Recently, the high speed flash ADCs with the resolution of 6 to 7-bits and the sampling rate up to 1 GS/s are widely used for the multi-band OFDM Ultra-Wideband (UWB) receiver[1] and the digital read-channel of optical and magnetic data storage devices such as DVD[2,3] Blu-Ray Disk and Hard Disk. Since these flash ADCs are usually integrated on the same chip with the large digital signal processing blocks and the supply voltage of digital blocks is reduced to a small value with scaling, it is convenient to reduce the supply voltage of ADC to the same value as the digital supply voltage. With a reduced supply

voltage, flash ADCs are sensitive to the analog noise such as the input offset voltages of amplifiers and comparators, and the reference voltage fluctuation. Especially, when the flash ADC is implemented using the interpolation method to reduce the chip area, the input offset voltage of amplifiers can cause the consecutive bubbles which can not be removed by the conventional 3-input majority voter [4].

In this work, a 7-bit 1 GS/s CMOS flash ADC with the supply voltage of 1.2 V was implemented by using a 0.13  $\mu$ m CMOS process. A reference voltage calibration scheme was used at the 1<sup>st</sup> preamp stage for the offset voltage control, and the 3-stage cascaded voting process was proposed to eliminate the consecutive bubbles up to seven in the thermometer code.

# II. CIRCUIT DESCRIPTION

### 1. Architecture

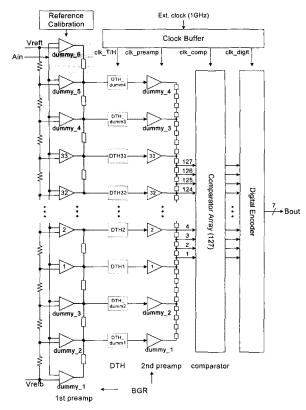

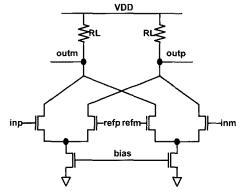

Fig. 1 shows the block diagram of the proposed ADC. It consists of the arrays of 1<sup>st</sup> preamp, distributed track/hold (DTH), 2<sup>nd</sup> preamp, comparator, the resistor interpolation network, and the digital encoder block [3]. Although the signals and circuits are shown in the single-ended version in Fig. 1 for simplicity, they are implemented in the differential version for high noise immunity. The 1<sup>st</sup> preamp array consists of 39 4-input differential amplifiers (including 6 dummies). The circuit schematic of the differential amplifier is shown in Fig. 2 [2]. The differential output voltage of the amplifier can be represented by.

$$V_{outp} - V_{outn} = A_{vl} \cdot \left\{ (V_{inp} - V_{inm}) - (V_{refp} - V_{refm}) \right\}$$

(1)

The gain  $A_{vl}$  of the 1<sup>st</sup> preamp was adjusted to a constant value of about 10 dB by a replica biasing circuit. To

E-mail: baecha@postech.ac.kr

Manuscript received Nov. 24, 2008; revised Dec. 5, 2008.

<sup>\*</sup> Postech, Dep. EE, Pohang, Korea

<sup>\*\*</sup> Samsung Electronics CO., Ltd., Giheung, Korea

Fig. 1. Block diagram of proposed ADC.

Fig. 2. 1st preamp circuit.

compensate for the input offset voltage of this  $1^{\rm st}$  preamp array, the differential

DC reference voltage( $V_{refp}$ - $V_{refm}$ ) is digitally calibrated after the power-on reset. Also the conventional resistor averaging scheme is applied to the output nodes of the differential amplifiers to further compensate for the input offset voltage [2,5].

The DTH array [3] consists of 37 pairs (including 4 dummies) of PMOS switches. The parasitic input capacitors of the 2<sup>nd</sup> preamp are used as the sampling capacitors. The 2<sup>nd</sup> preamp array consists of 37 differential pairs (including 4 dummies), each of which consists of an NMOS-

input differential pair with resistive loads [2,3] and a PMOS switch for equalization.

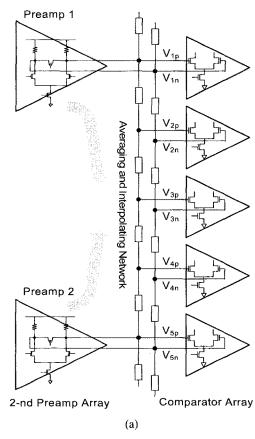

A differential interpolation scheme with a factor of 4 was implemented as shown in Fig. 3(a). The output nodes of the two adjacent amplifiers in the 2<sup>nd</sup> preamp array are connected by a resistor string with four output nodes. Each output node of a resistor string is connected to a comparator input. This interpolation scheme reduces the number of 1<sup>st</sup> preamp, DTH and 2<sup>nd</sup> preamp, and hence the input capacitance of ADC into one fourth. The gain of the 2<sup>nd</sup> preamp array was adjusted to around 12 dB by a replica biasing circuit to compensate for the gain loss by

**Fig. 3.** (a) 2<sup>nd</sup> preamp array and interpolation with a factor of 4 (b) Schematic of comparator.

the resistor interpolation network [5]. The bandwidths of the 1<sup>st</sup> and 2<sup>nd</sup> preamps were about 800 MHz and 1.1 GHz at the 200 fF load, respectively. 33 amplifiers of the 1<sup>st</sup> and 2<sup>nd</sup> preamp arrays (excluding dummies) gave the 5-bit resolution and the resistor interpolation with a factor of 4 gave the additional 2-bit resolution, which gave the total 7-bit resolution.

The 127 comparators following the 2<sup>nd</sup> preamp array generate a 127-bit thermometer code, which is converted into a 7-bit binary code via a quasi-gray encoding by the digital encoder block. As shown in Fig. 3(b), a comparator consists of an input differential pair, a regenerative flip-flop and a SR latch [6].

The proposed ADC can generate consecutive bubbles in the thermometer code because of the interpolation scheme with the factor of 4. Since the conventional 3-input voting process[4] can eliminate only a single bubble, a 3-stage cascaded voting process was used in the digital encoder block of this work to eliminate the consecutive bubbles up to 7. The 2<sup>nd</sup> preamp output is assumed to have a single bubble at most. The bias and reference voltages were generated by a band-gap reference circuit.

# 2. Digital Calibration of Reference Voltage

Since a low supply voltage of 1.2 V is used in this work, the analog input voltage ranges from 750 mV to 1150 mV (400 mV swing, 800 mV differential swing). The 1<sup>st</sup> preamp is required to have a 5-bit resolution, which gives the input voltage resolution of 12.5 mV (25 mV differential). With a 10% variation of MOSFET gate length and a 15% variation of resistor load, however, the Monte Carlo simulation showed that the input offset voltage of the 1<sup>st</sup> preamp was about 20 mV, which was larger than the input voltage resolution.

To reduce the input offset voltage to a value smaller than 12.5 mV, two approaches were used. One is the conventional resistor averaging scheme applied to the output nodes of the 1<sup>st</sup> preamp array [2,5]. The other is a digital calibration scheme of DC reference voltage of differential amplifiers, which was proposed in this work. If the input offset voltage is larger than the input voltage resolution, the conventional resistor averaging network is no longer good enough to reduce the effect of input offset voltage.

The digital offset calibration schemes published in the literatures [7,8] adjust the relative driving strength of either branch of a differential pair. These methods increase

the junction capacitance along the high-speed analog signal paths because of the added components, and hence they may slow down the circuit operation. In contrast to the above-mentioned published digital offset calibration schemes, the digital calibration scheme proposed in this work negligibly affects the high speed signal path because only the differential DC reference voltage of each 4-input differential pair of the 1st preamp array is adjusted without affecting the signal input voltage. Recently, the digital offset calibration scheme which adjusts the reference voltage was published in [9]. However, the on-chip calibration capability of this work was not implemented in [9].

During the initial calibration interval after the power-on reset, the input offset voltage of each differential pair is reduced to a value smaller than half of the input voltage resolution  $(0.5 \times 12.5 \text{ mV})$  as long as the original input offset voltage is smaller than twice the input voltage resolution ( $\pm 25 \text{ mV}$ ).

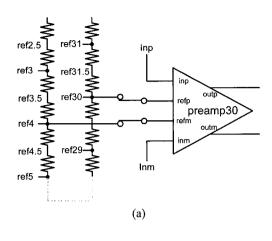

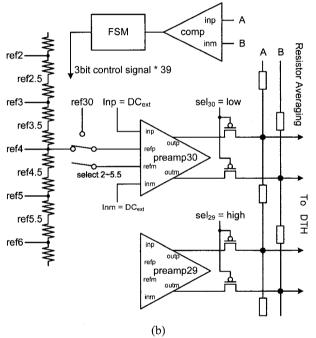

In this work, the digital offset calibration scheme was applied to the 1<sup>st</sup> preamp array. Fig. 4(a) shows the connectivity of a 4-input differential amplifier (preamp30) of the 1<sup>st</sup> preamp array during this normal operation before the digital offset calibration is performed. The analog input nodes (inp, inm) are connected to the differential analog input voltage( $A_{in}$  of Fig. 1), The positive and negative reference voltage input nodes (refp, refm) are connected to the corresponding nodes of the reference resistor ladder (ref30, ref4), respectively. The reference resistor ladder is a single-line resistor ladder laid out in the U-shaped form. The refp and refm nodes of the adjacent amplifier (preamp29) are connected to the ref29, and ref5 nodes of the reference ladder. The mid-point nodes such as ref29.5 and ref4.5 nodes are used for calibration only.

Fig. 4(b) shows the procedure of the digital offset calibration scheme proposed in this work. During the calibration mode, only one of the 39 amplifiers in the 1<sup>st</sup> preamp array is connected to the resistor averaging network with all the other amplifiers disconnected by the PMOS switches. Each amplifier of the 1<sup>st</sup> preamp array is calibrated one by one. When *preamp30* is enabled during the calibration mode, both *inp* and *inm* are connected to a common analog input voltage (0.95 V in this work, the mid-point of input voltage swing). Therefore the differential input voltage of *preamp30* is 0. The *refp* node of *preamp30* is connected to the *ref4* node of the reference ladder. The negative feedback loop composed of a comparator and a FSM

**Fig. 4.** (a) Operation of the 1<sup>st</sup> preamp before the offset calibration (b) Digital calibration procedure for input offset voltage control of 1st preamp.

which are implemented on chip determines the connection point of the refm node. At first, the refm node is connected to the ref2 node. Then, the differential output voltage  $(V_{outp}-V_{outm})$  of the preamp30 is positive. After that, the refm node is moved to the next higher node (ref2.5). This sweep operation is continued until the differential output voltage  $(V_{outp}-V_{outm})$  changes its polarity to negative or the ref5.5 node is reached. This sweeping operation corresponds to the input offset voltage change of 43.75 mV with a resolution of 6.25 mV. During the normal operation, the refm node of preamp30 is fixed at the node determined during the calibration mode.

Although the mismatches among the resistors of the

reference ladder may cause the non-linearity problem, they do not affect the monotonic property of the reference voltage. Therefore, the resistor mismatches do not affect the accuracy of the reference voltage calibration step. Also, the nonlinearity of the MOSFET switches between the reference ladder and the 1st preamp array do not increase the distortion of the 1st preamp, because the CMOS transmission gate switches are used to reduce the non-linearity of the switches and the signals which are selected by the switches are DC signal. Additionally, the resistance of the switches reduces the DC reference fluctuation caused by the external transient noise[10].

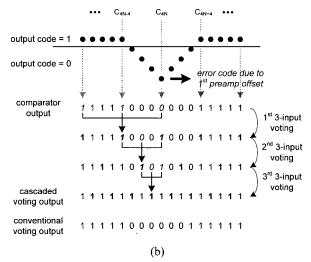

# 3. 3-Stage Cascaded Voting Process

The input offset voltages of the 1<sup>st</sup> and 2<sup>nd</sup> preamps and comparators and the occasional meta-stability of comparators may generate bubbles in the thermometer code at the comparator output. Although the conventional 3-input majority voter can remove an isolated bubble, it cannot remove consecutive bubbles. Since the interpolation with a factor of 4 is used at the 2<sup>nd</sup> preamp output, it may generate consecutive bubbles at the interpolated output even though there is only a single bubble at the 2<sup>nd</sup> preamp output.

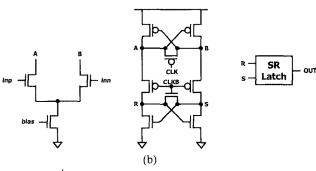

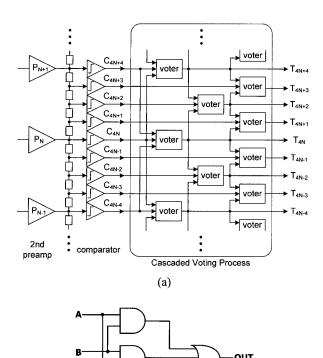

Fig. 5(a) shows the circuits performing the proposed 3-stage cascaded voting process. The voting is performed in three stages by using the conventional 3-input majority voters, shown in Fig. 5(b). The 3-input voter was implemented with static logic gates. The partial thermometer codes ( $\cdots$ , $C_{4N+4}$ ,  $C_{4N}$ ,  $C_{4N-4}$ , $\cdots$ ) are the comparator output codes corresponding to the direct outputs from the 2<sup>nd</sup> preamps. It is assumed that there is only a single bubble at most in these partial codes ( $\cdots$ , $C_{4N+4}$ ,  $C_{4N}$ ,  $C_{4N-4}$ , $\cdots$ ). Among the entire thermometer codes ( $\cdots$ , $C_{4N+4}$ ,  $C_{4N+3}$ ,  $C_{4N+2}$ ,  $C_{4N+1}$ ,  $C_{4N-1}$ ,  $C_{4N-2}$ ,  $C_{4N-3}$ ,  $C_{4N-4}$ , $\cdots$ ), the above mentioned partial thermometer codes have the largest probability of bubble errors due to the use of interpolation.

Therefore, the codes  $\cdots$ ,  $C_{4N+4}$ ,  $C_{4N}$ ,  $C_{4N-4}$ ,  $\cdots$  are voted first at the 1<sup>st</sup> stage. This generates the bubble-free codes  $\cdots$ ,  $T_{4N+4}$ ,  $T_{4N}$ ,  $T_{4N-4}$ ,  $\cdots$ . After the 1<sup>st</sup> stage voting, the 2<sup>nd</sup> stage voting was performed for the corrected codes ( $\cdots$ ,  $T_{4N+4}$ ,  $T_{4N}$ ,  $T_{4N-4}$ ,  $\cdots$ ) and the interpolated codes ( $\cdots$ ,  $C_{4N+2}$ ,  $C_{4N-2}$ ,  $\cdots$ ) from the mid-point of the interpolation resistor string. This 2<sup>nd</sup> stage voting generates the bubble-free

(b)

Fig. 5. (a) Cascaded voting process (b) Circuit of the 3-input voter.

codes  $\dots, T_{4N+2}, T_{4N-2}, \dots$ , since the 2 inputs out of 3 inputs of all the 2<sup>nd</sup> stage voters are bubble-free. Similarly, the 3<sup>rd</sup> stage voting generates the bubble-free codes  $\dots, T_{4N+3}, T_{4N-1}, T_{4N-1}, T_{4N-3}, \dots$  Therefore, this 3-stage cascaded voting process eliminates all the bubbles in the resultant codes, as long as there are no consecutive bubbles in the original partial codes  $(\dots, C_{4N+4}, C_{4N}, C_{4N-4}, \dots)$ .

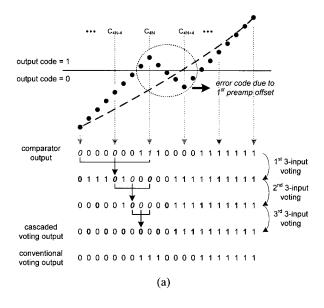

Fig. 6 shows the examples of cascaded voting process. We assumed that there is only a single bubble at most in the partial codes  $(\cdots, C_{4N+4}, C_{4N}, C_{4N-4}, \cdots)$  of Fig. 5, which are the comparator outputs directly corresponding to the  $2^{nd}$  preamp outputs. In this case, the maximum number of consecutive bubbles in the entire code is seven.

Fig. 6(a) and (b) show the cases of four and seven consecutive bubbles, respectively. The proposed 3-stage cascaded voting process eliminates the bubbles completely.

Since only a single 3-input voter was assigned to each comparator output in the proposed voting scheme, this scheme did not cause any hardware increase compared to the conventional 3-input voting scheme. Although the 5-input voter can eliminate completely up to 2 consecutive bubbles, it has the twice the gate count of the 3-input voter.

**Fig. 6.** Examples of the cascade voting process (a) the voting for the bubbles in the transition region (b) the voting for the maximum votable consecutive bubbles.

However, the cascaded voting can result in increased latency.

### III. MEASUREMENT RESULTS

To measure the output binary code, the decimation scheme was used at the output of the digital encoder. The decimation block reduces the frequency of the output binary code from 1 GHz to 100 MHz.

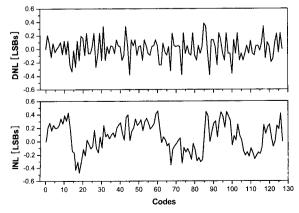

Table 1 shows the measured performance summary of the fabricated ADC chip. Fig. 7 shows the chip layout and the chip microphotograph. The active chip area is 1.28 mm<sup>2</sup>. Fig. 8 shows the measured DNL and INL plots in LSB

Fig. 7. (a) Chip layout (b) Chip microphotograph.

Table 1. Performance summary (measurements).

| 1 GS/s                                            |

|---------------------------------------------------|

| 7-bit                                             |

| 195 MHz                                           |

| 400 mV <sub>P-P</sub>                             |

| +0.38/-0.465 LSB,                                 |

| +0.454/-0.474 LSB                                 |

| 37 dB, 5.86 bits                                  |

| @1 Gsample/s                                      |

| 1 P 6 M 0.13-μm CMOS                              |

| 1.2 V                                             |

| 212 mW                                            |

| 1.28 mm <sup>2</sup> (800 $\mu$ m × 1600 $\mu$ m) |

|                                                   |

Fig. 8. Measured DNL and INL.

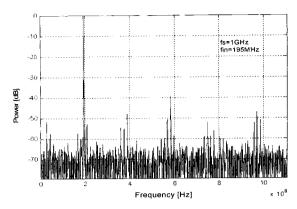

Fig. 9. Measured power spectrum.

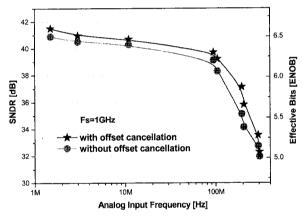

Fig. 10. SNDR versus input frequency at 1 GS/s.

units versus the input code. The maximum DNL and INL are  $\pm 0.38/-0.465$  LSBs and  $\pm 0.454/-0.474$  LSBs, respectively. Fig. 9 shows the power spectrum of the ADC output code at the sampling frequency of 1 GS/s, the supply voltage of 1.2 V, and the 400 mV<sub>p-p</sub> 195 MHz sine wave input. Fig. 10 shows the measured SNDR versus the analog input frequency at the sampling rate of 1 GS/s, where the digital calibration of reference voltage for offset voltage control enhanced the SNDR from 35.13 dB to 37.14 dB with a 195 MHz 400 mV<sub>p-p</sub> sine wave input. The power consumption was measured to be 212 mW at the sampling frequency of 1 GS/s.

# IV. CONCLUSIONS

A 1.2 V 7-bit 1 GS/s CMOS flash ADC with the interpolation factor of 4 was implemented by using a 0.13  $\mu m$  CMOS process. The input bandwidth was measured to be 195 MHz at the supply voltage of 1.2 V and the 400  $mV_{p\text{-}p}$  sine wave input. ENOB, SNDR, and the power consumption were measured to be 5.88 bits, 37.14 dB, and

212 mW, respectively.

The ADC chip consists of the arrays of the 1<sup>st</sup> preamp, the distributed track and hold circuit, the 2<sup>nd</sup> preamp followed by the interpolation network, the comparator, and the digital encoder block.

A digital calibration of DC reference voltage was proposed for the 1<sup>st</sup> preamp array to reduce the input offset voltage without disturbing the high-speed analog signal path.

A 3-stage cascaded voting process was proposed for the digital encoder block to eliminate the consecutive bubbles generated by the interpolation scheme. The circuit for this voting process consists of the conventional 3-input majority voters. There is no hardware increase in this cascaded voting process compared to the conventional 3-input voting. The consecutive bubbles up to 7 bits can be completely eliminated with the proposed voting process, if the 2<sup>nd</sup> preamp output is assumed to have a single bubble at most.

### ACKNOWLEDGMENTS

This work was supported by IDEC, and BK21 program, KOREA.

### REFERENCES

- [1] Cheng-Chung Hsu, et al, "A 7b 1.1 GS/s Reconfigurable Time-Interleaved ADC in 90 nm CMOS," VLSI Circuits, 2007 IEEE Symposium on, 14-16 June 2007 Page(s):66 - 67

- [2] M. Choi and A. A. Abidi, "A 6-b 1.3 GSample/s A/D converter in 0.35-μm CMOS," *IEEE JSSC*, Vol. 36, No. 12, pp. 1847-1858, Dec. 2001.

- [3] G. Geelen, "A 6-bit 1.1 Gsample/s CMOS A/D converter," *IEEE ISSCC*, pp. 128-129, Feb. 2001.

- [4] C. W. Mangelsdort, "A 400-MHz Input Flash Converter with Error Correction," *IEEE JSSC*, Vol. 25, No. 1, pp. 184-191, 1990.

- [5] P. C. S. Scholtens and M. Vertregt, "A 6-b 1.6-Gsample/s flash ADC in -0.18-μm CMOS using averaging termination," *IEEE JSSC*, Vol. 37, No. 12, pp. 1599-1609, Dec. 2002.

- [6] G. M. Yin, F. Op't Eynde, and W. Sansen, "A High Speed CMOS Comparator with 8-bit Resolution," *IEEE JSSC*, Vol. 27, No. 2, pp. 208-211, Feb. 1992.

- [7] K. J. Wong and C. K. Yang, "Offset Compensation in Comparators With Minimum Input-Referred Supply Noise," *IEEE JSSC*, Vol. 39, No. 5, pp. 837-840, May 2004.

- [8] C. K. Yang, V. Stojanovic, S. Modjtahedi, M. A. Horowitz, and W. F. Ellersick, "Serial-link transceiver based on 8-Gsamples/s A/D and D/A converters in 0.25 μm CMOS," *IEEE JSSC*, Vol. 36, No. 11, pp. 1684-1692, Nov. 2001

- [9] B. Verbruggen, et al, "A 7.6 mW 1.75 GS/s 5 bit flash A/D converter in 90 nm digital CMOS," VLSI Circuits, 2008 IEEE Symposium on, pp. 14-15, 18-20 June 2008.

- [10] Sanghoon Hwang and Minkyu Song, "A Low-Noise and Small-Size DC Reference Circuit for High Speed CMOS A/D Converters," *Journal of Semiconductor Technology and Science*, Vol. 7, No. 1, pp. 43-50, Mar., 2007

Young Chan Jang was born in Daegu, Korea, in 1976. He received the B.S. degree in Electronic Engineering from Kyung-Pook National University, Korea, in 1999 and the M.S. and Ph.D. degrees in Electronic Engineering from Pohang University

of Science and Technology (POSTECH), Korea, in 2001 and 2005, respectively. In 2005, he rejoined the Advanced Technology Development team, Samsung Electronics, where he has been working in the area of high-speed memory design. His current research area is high-performance mixed-mode circuit design for VLSI systems such as high-performance signaling, clock generation, and analog-to-digital conversion.

Jun Hyun Bae was born in Ui-Seong, Korea, on 1981. He received the B.S. degree in the Department of Electronic and Electrical Engineering from Kyung-Pook National University, Korea, in 2004 and M.S. degree in Electronic Engineering from Pohang

University of Science and Technology (POSTECH), Korea, in 2007, respectively. He is currently pursuing the Ph.D. degree in the Department of Electronic and Electrical Engineering from Pohang University of Science and Technology (POSTECH), Korea. His interests include data converters, high-speed interface circuits and ultralow-voltage analog circuits.

Jae-Yoon Sim received the B.S., M.S., and Ph.D. degrees in Electronic and Electrical Engineering from Pohang University of Science and Technology, Korea, in 1993, 1995, and 1999, respectively. From 1999 to 2005, he was a Senior Engineer at

Samsung Electronics, Korea. From 2003, to 2005, he was a post-doctoral student with the University of Southern California, Los Angeles. In 2005, he joined the Faculty of Electronic and Electrical Engineering, Pohang University of Science and Technology, Korea, where he is currently an Assistant Professor. His research interests include PLL/DLL, high-speed links, memory circuits, and ultra low-power analog.

Hong June Park received the B.S. degree from the Department of Electronic Engineering, Seoul National University, Seoul, Korea, in 1979, the M.S. degree from the Korea Advanced Institute of Science and Technology, Taejon, in 1981, and the Ph.D.

degree from the Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, in 1989. He was a CAD engineer with ETRI, Korea, from 1981 to 1984 and a Senior Engineer in the TCAD Department of Intel from 1989 to 1991. In 1991, he joined the Faculty of Electronic and Electrical Engineering, Pohang University of Science and Technology (POSTECH), Kyungbuk, Korea, where he is currently Professor. His research interests include high-speed CMOS interface circuit design, signal integrity, device and interconnect modeling. Prof. Park is a member of IEEK, IEEE and IEICE.