# A Quadrature VCO Exploiting Direct Back-Gate Second Harmonic Coupling

Nam-Jin Oh

## **Abstract**

This paper proposes a novel quadrature VCO(QVCO) based on direct back-gate second harmonic coupling. The QVCO directly couples the current sources of the conventional LC VCOs through the back-gate instead of front-gate to generate quadrature signals. By the second harmonic injection locking, the two LC VCOs can generate quadrature signals without using on-chip transformer, or stability problem that is inherent in the direct front-gate second harmonic coupling. The proposed QVCO is implemented in 0.18  $\mu$ m CMOS technology operating at 2 GHz with 5.0 mA core current consumption from 1.8 V power supply. The measured phase noise of the proposed QVCO is -63 dBc/Hz at 10 kHz offset, -95 dBc/Hz at 100 kHz offset, and -116 dBc/Hz at 1 MHz offset from the 2 GHz output frequency, respectively. The calculated figure of merit(FOM) is about -174 dBc/Hz at 1 MHz offset. The measured image band rejection is 46 dB which corresponds to the phase error of 0.6°.

Key words: Back-Gate Coupling, CMOS, Injection Locking, Quadrature VCO, Second Harmonic Coupling.

# I. Introduction

With the demand for lower cost and higher integration of wireless transceiver building blocks, a low power design is a great concern for radio frequency integrated circuit(RFIC) designers. For the digital wireless transceivers, a quadrature voltage controlled oscillator(VCO) plays an important role to down-convert the received radio frequency signal or up-convert the baseband analog signal with mixers.

Many papers have described how to generate accurate quadrature signals<sup>[1]~[4]</sup>. The most popular method is to use a differential VCO running at double the frequency of the desired frequency, and then to obtain quadrature waveforms via frequency division. However, a higher oscillation frequency and the frequency division result in increased power consumption. As well, this approach generally shows poor quadrature accuracy, as it requires an accurate 50 % duty cycle VCO<sup>[4]</sup>.

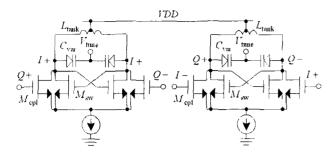

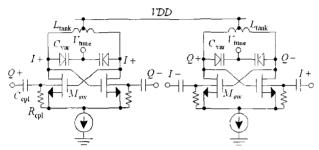

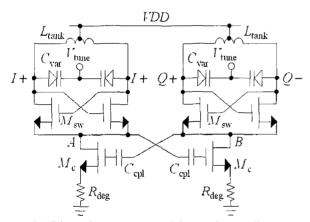

Another way is to force two cross-coupled differential *LC* VCOs to run in quadrature by coupling transistors. This technique exploits a good phase noise performance of *LC*-oscillators. Examples of quadrature VCO(QVCO) topologies have been published by directly coupling two *LC* VCOs<sup>[2]~[5]</sup> as shown in Fig. 1(a) and (b). The third way is based on two injection locked oscillators with a second harmonic coupling using an on-chip transformer<sup>[6]</sup>. However, the on-chip transformer occupies a large die area while achieving a good phase noise performance. The

fourth way is to exploit the direct front-gate second harmonic coupling as shown in Fig.  $1(c)^{[7]\sim[10]}$ . In this method, the source nodes of each current source should be degenerated with resistors to reduce the transconductance of the current source coupling transistor, Mc, which is necessary for stability. If the loop gain of the current source is higher than one, then a parasitic oscillation occurs and thereby results in an AM modulated output waveform<sup>[7]</sup>. Furthermore, the degenerated resistor consumes voltage headroom.

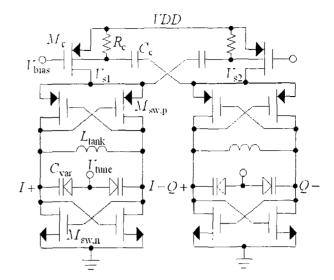

In this paper, a direct back-gate second-harmonic coupling quadrature VCO is proposed, in which the current source coupling transistors are coupled through body-terminals called back-gates. By doing that, the new QVCO does not use the large size on-chip transformer, and overcomes the stability problem since the back-gate input gives a lower gain<sup>[11]</sup>.

# II. Circuit Design

Quadrature VCO based on back-gate coupling is verified in [5] as shown in Fig. 1(b). By the same token, the technique can be utilized for the second harmonic coupling. Fig. 2 shows the proposed direct back-gate second-harmonic QVCO. The oscillator design is based on the complementary cross-coupled differential pair that uses a symmetric inductor that has a differential value of 5.9 nH with a differential Q factor of 11 around 2 GHz, which is 1.5 times higher than that of the singled

Manuscript received September 1, 2008; revised September 18, 2008. (ID No. 20080901-033J) Department of Electronic Engineering, Chungju National University, Chungju, Korea.

(a) Conventional parallel-coupled QVCO

(b) Parallel back-gate coupled QVCO

(c) Direct front-gate second harmonic coupling (bias is not shown)

Fig. 1. Several quadrature VCO topologies.

ended inductor. The MOS varactor with a total width of 60  $\mu$ m and a channel length of 1  $\mu$ m has a minimum value of 170 fF and a maximum value of 470 fF with tuning voltage of  $\pm 0.3$  V gate bias voltage around 0 V.

The two LC oscillators are direct coupled at common nodes of  $V_{s1}$  and  $V_{s2}$  through the back-gate terminal with the resistor and capacitor network.

Without using a large size transformer or resistors for source degeneration, the proposed QVCO reduces the power consumption while achieving the low phase noise and quadrature waveforms. When the current source of  $M_c$  are cross-coupled with  $C_c$  and  $R_c$ , the coupling forces the second harmonic to be 180° out of phase, which in turn forces each LC oscillator to generate quadrature signals. During the first period of oscillation, the coupling would try to force each second harmonic signal to

Fig. 2. Proposed direct back-gate second-harmonic coupling QVCO.

180° out of phase, but actually would be less than 180°. During the following period, the injection locking would continuously force the two oscillators to run at 180° out of phase, and finally generate quadrature signals.

As the inherent device noise causes small perturbation in the waveforms, the injection locking forces the two oscillators to generate quadrature signals. These phenomena are the same with those presented in using transformer or front-gate injection locking<sup>[4],[5]</sup>.

It can be verified by forcing the two oscillators to start in-phase and finally generate quadrature signals. Perfect quadrature signals can be achieved when the two oscillators match perfectly. However, for small tank mismatches, the injection-locking will still force the two oscillators in quadrature with a small quadrature error. To set the sequence of in-phase and quadrature signals, a small size PMOS ring oscillator is added in parallel with the tank [4]. The ring oscillator is designed to consume around one-seventh of the oscillator core current and thereby degrades the overall phase noise performance very little. Simulation results show that the QVCO can be designed to have the phase error less than 5° by setting up  $\pm 0.5$ % inductor mismatch and choosing appropriate ring oscillator size.

## III. Measurement Results

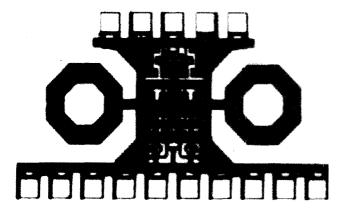

To verify the proposed idea, the circuit has been fabricated in SMIC's 0.18  $\mu$ m CMOS technology. The fabricated chip is shown in Fig. 3. The chip size is  $700 \times 1,200 \ \mu$  m² including the pads. All the pads are electrostatic discharge(ESD) protected to prevent from an unexpected high voltage discharge.

For the buffers, small size transistors are used to mi-

Fig. 3. Chip micrograph. The die size is  $700 \times 1,200 \, \mu \, \text{m}^2$ .

nimize the frequency shift of the oscillation frequency. Also, a passive single sideband(SSB) mixer is implemented on-chip to measure the image band rejection (IBR) which is directly related to the in-phase (I) and quadrature (Q) mismatch in real chip implementation.

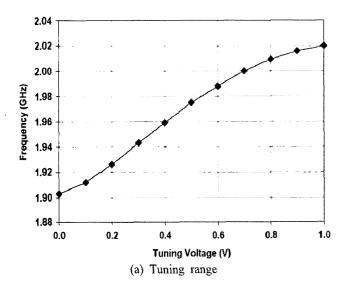

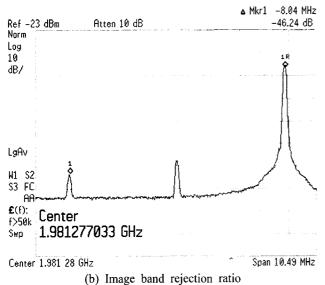

Fig. 4. Measurement results from the SSB mixer output.

Octagonal-shape symmetric inductors are implemented for the tank to have higher quality factor rather than using single-ended inductors.

Fig. 4 shows the measured tuning range, and the output spectrum of the SSB mixer up-converter. An accurate 4 MHz baseband signal is applied to the SSB mixer from the Agilent Vector Signal Generator to measure the IBR. As shown in Fig. 4(b), the measured IBR is 46 dB, which corresponds to the phase error of about 0.6° assuming the IBR is entirely caused by I/Q phase error.

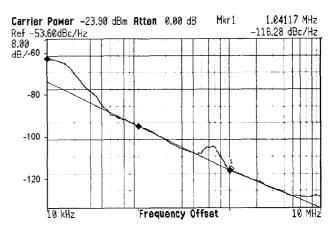

Fig. 5 shows the phase noise performance. The measured phase noise is -63 dBc/Hz at 10 kHz offset, -95 dBc/Hz at 100 kHz offset, and -116 dBc/Hz at 1 MHz offset from the 2 GHz output frequency, respectively. Table 1 summarizes the measurement results of the proposed QVCO compared to those of other low phase noise VCOs.

## IV. Conclusion

In this paper, a novel quadrature VCO is proposed by exploiting an injection locking through a direct backgate coupling between the two LC VCOs. Operating at around 2 GHz, the proposed VCO is implemented using 0.18  $\mu$ m CMOS technology. With 5.0 mA core current consumption from a 1.8 V power supply, the proposed VCO achieves the phase noise performance of -116

Fig. 5. Measured phase noise performance.

Table 1. Performance comparison of low phase noise VCOs.

| Ref.         | Freq.<br>[GHz] | Power [mW] | Phase noise [dBc/Hz] | FOM<br>[dBc/Hz] | Tech. [ μ m] |

|--------------|----------------|------------|----------------------|-----------------|--------------|

| [5]          | 1.1            | 5.4        | -120 [@1M]           | -173.5          | 0.18         |

| [8]          | 2              | 26.5       | -126.5 [@1M]         | -178.3          | 0.13         |

| [12]         | 2.45           | 7.2        | -119 [@1M]           | -178.0          | 0.18         |

| This<br>work | 1.91~2.01      | 9          | -116 [@1M]           | -174            | 0.18         |

dBc/Hz at 1 MHz offset frequency and the phase error of about 0.6°. The calculated figure of merit(FOM) of the proposed VCO is about -174 dBc/Hz at 1 MHz offset, which is comparable to other low phase noise VCO performance.

# References

- [1] M. Tiebout, "Low-power low-phase-noise differentially tuned quadrature VCO design in standard CMOS", *IEEE J. Solid-State Circuits*, vol. 36, pp. 1018-1024, Jul. 2001.

- [2] P. Andreani, A. Bonfanti, L. Romanò, and C. Samori, "Analysis and design of a 1.8-GHz CMOS LC quadrature VCO", *IEEE J. Solid-State Circuits*, vol. 37, pp. 1737-1747, Dec. 2002,

- [3] A. Ravi, K. Soumyanath, R. E. Bishop, B. A. Bloechel, and L. R. Carley, "An optimally transformer coupled, 5 GHz quadrature VCO in a 0.18 μm digital CMOS process", *Symp. VLSI Circuits Digest of Technical Papers*, pp. 141-144, Jun. 2003.

- [4] S. L. J. Gierkink, S. Levantino, R. C. Frye, C. Samori, and V. Boccuzzi, "A low-phase-noise 5-GHz CMOS quadrature VCO using superharmonic coupling", *IEEE J. Solid-State Circuits*, vol. 38, pp. 1148-1154, Jul. 2003.

- [5] H.-R. Kim, C.-Y. Cha, S.-M. Oh, M.-S. Yang, and S.-G. Lee, "A very low-power quadrature VCO with back-gate coupling", *IEEE J. Solid-State Circuits*, vol. 39, pp. 952-955, Jun. 2004.

- [6] C. C. Meng, Y. W. Chang, and S. C. Tseng, "4.9-

- GHz low-phase-noise transformer-based superharmonic-coupled GaInP/GaAs HBT QVCO", *IEEE Microwave and Wireless Components Letters*, vol. 16, pp. 339-341. Jun. 2006.

- [7] T. M. Hancock, G. M. Rebeiz, "A novel superharmonic coupling topology for quadrature oscillator design at 6 GHz", *IEEE Radio Frequency Integrated Circuits Symp.*, pp. 285-288, Jun. 2004.

- [8] D. Guermandi, P. Tortori, E. Franchi, and A. Gnudi, "A 0.83~2.5-GHz continuously tunable quadrature VCO", *IEEE J. Solid-State Circuits*, vol. 40, pp. 2620-2627, Dec. 2005.

- [9] P. Tortori, D. Guermandi, E. Franchi, and A. Gnudi, "Quadrature VCO based on direct second harmonic locking", *International Symp. Circuits and Systems*, pp. I-169-I-172, May. 2004.

- [10] A. Mazzanti, F. Svelto, "A 1.8-GHz injection-locked quadrature CMOS VCO with low phase noise and high phase accuracy", *IEEE Tran. Circuits and Systems-I:Regular papers*, vol. 53, pp. 554-560, Mar. 2006.

- [11] Nam-Jin Oh, Yeon-Guk Ryu, and Jung-Soo Ahan, "Quadrature VCO based on direct back-gate second harmonic coupling", in *Institute of Electronics Engineers of Korea(IEEK)*. Conf., pp. 457-458, Jul. 2007.

- [12] D. Leenaerts, C. Dijkmans, and M. Thompson, "A 0.18 μm CMOS 2.45 GHz low-power quadrature VCO with 15 % tuning range", in *Proc. Rad. Freq. Integr. Circuits Symp.*, pp. 67-70, Jun. 2002.

## Nam-Jin Oh

received B.S. degree in physics from Hanyang University, Seoul, Korea, in 1992, M.S. degree in electrical engineering from North Carolina State University, Raleigh, NC, USA, in 1999, and Ph.D. degree from Information and Communications University, Daejeon, Korea, in 2006. From 1992 to 1997, he was with LG Corporate Insti-

tute of Technology, Seoul, Korea. From 1999 to 2001, he was with Samsung Electronics, Suwon, Korea. From May to July 2004, he had an internship at PHYCHIPs, Inc., Daejeon, Korea. From 2006 to 2007, he was with Auto-ID Lab., Fudan University, China, as a post-doctor. He has been a professor of department of electronic engineering, Chungju National University, Korea. His research interests include analog and mixed-signal integrated circuits, digital integrated circuits, system level behavioral simulation of wireless communications, and device modeling of CMOS active and passive circuits.