# A Versatile Universal Capacitor-Grounded Voltage-Mode Filter Using DVCCs

Hua-Pin Chen and Sung-Shiou Shen

In this paper, a versatile three-input five-output universal capacitor-grounded voltage-mode filter is proposed. The circuit employs two differential voltage current conveyors as active elements together with two grounded capacitors and four resistors as passive elements. The proposed configuration can be used as either a singleinput five-output or three-input two-output. Unlike the previously reported works, it can simultaneously realize five different generic filtering signals: lowpass, bandpass, highpass, bandreject, and allpass. It still maintains the following advantages: (i) the employment of all grounded capacitors, (ii) no need to employ inverting-type input signals, (iii) no need to impose component choice, (iv) orthogonal control of the resonance angular frequency  $\omega_0$ and the quality factor Q, and (v) low active and passive sensitivity performances.

Keywords: Analog electronics, active filters, current conveyors.

# I. Introduction

As a current-mode active device, the differential voltage current conveyor (DVCC) has the advantages of both the second-generation current conveyor (CCII) (such as large signal bandwidth, great linearity, and wide dynamic range) and the differential difference amplifier (DDA) (such as high input impedance and arithmetic operation capability) [1]. This element is a versatile building block whose applications appear in the literature [1]-[7]. Many voltage-mode multifunction filters using current conveyors have been proposed [8]-[12]. However, these configurations require at least four active components.

In 2003, Chang and others proposed a voltage-mode multifunction filter with a single input and four outputs [13]. In 2004, Horng and others proposed another multifunction filter with a single input and three outputs [14]. However, with these two proposed configurations only three standard filter signals can be simultaneously obtained. In 2006, Horng and others. proposed four voltage-mode universal biquadratic filters with a single input and five outputs [15]. The proposed circuits can realize highpass (HP), bandpass (BP), lowpass (LP), bandreject (BR), and allpass (AP) simultaneously, but need a component-matching condition to realize the AP filter response. Also, each of the proposed circuit employs many more passive components.

In 2007, Chen [16] proposed another voltage-mode universal biquadratic filter with a single input and five outputs using two differential difference current conveyors (DDCCs), two grounded capacitors, and three resistors. The circuit uses one Z+ output device, whereas the proposed circuit uses two Z outputs. The circuit uses three Y inputs, whereas the proposed circuit uses only two Y inputs. The two capacitors in each of the two DVCCs are similarly positioned at the Z output

Manuscript received Dec. 25, 2006; revised May 28, 2007.

Hua-Pin Chen (phone: +886 2 2273 3567, ext. 165, email: hpchen@dlit.edu.tw) and Sung-Shiou Shen (phone: +886 2 2273 3567, ext. 168, email: shen@dlit.edu.tw) are with the Department of Electronic Engineering, De-Lin Institute of Technology, Taipei, Taiwan.

terminals. The circuit in [16] can realize the AP filter without any component-matching condition. However, it needs to make capacitor  $C_1$  float and insert another voltage input signal  $V_{in}$  into the floating terminal of capacitor  $C_1$ . In this paper, the proposed circuit also can realize the AP filter without any component-matching condition and still employ the grounded capacitor, unlike the biquad reported in [16].

On the other hand, some universal voltage-mode biquads with multiple inputs and one output have been proposed [17]-[24]. However, these configurations cannot be realized by using only grounded capacitors. Also, they suffer from either inverting-type input signals or component-matching conditions. In 2003, Chang and Chen [25] proposed a universal voltagemode filter with three inputs and a single output. The circuit has additional advantages, such as the employment of only grounded capacitors, no need for inverting-type input signals, and no need for component-matching conditions. However, it still suffers from orthogonal control of  $\omega_0$  and Q. In this paper, the proposed circuit has the same advantages reported by Chang and Chen [25] in addition to one more important advantage—orthogonal control of  $\omega_0$  and Q. The proposed new circuit offers the following features: (i) simultaneous realization of LP, BP, HP, BR, and AP responses with the single-input five-output or three-input two-output in the same configuration; (ii) the employment of all grounded capacitors; (iii) no need to employ inverting-type input signals; (iv) no need to impose component choice; (v) orthogonal control of the  $\omega_0$  and Q; and (vi) low active and passive sensitivity performance. In Table 1, the main features of the proposed new circuit are compared with those of previous works.

Table 1. Summary of recent filters specifications.

| Criteria<br>Circuits | (i) | (ii) | (iii) | (iv) | (v) | (vi) |

|----------------------|-----|------|-------|------|-----|------|

| The new circuit      | yes | yes  | yes   | yes  | yes | yes  |

| Ref. [16] in 2007    | no  | yes  | yes   | no   | yes | no   |

| Ref. [15] in 2006    | no  | yes  | yes   | no   | yes | yes  |

| Ref. [14] in 2004    | no  | yes  | yes   | yes  | no  | yes  |

| Ref. [13] in 2003    | no  | yes  | yes   | yes  | no  | yes  |

| Ref. [25] in 2003    | no  | yes  | yes   | yes  | no  | yes  |

| Ref. [24] in 2005    | no  | no   | no    | yes  | yes | no   |

| Ref. [23] in 2004    | no  | no   | no    | no   | no  | no   |

# II. The Proposed Circuit

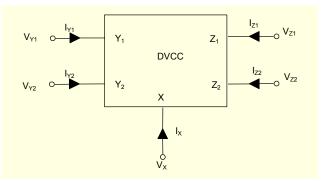

The block diagram of the DVCC is shown in Fig. 1 and its terminal relations are given by

Fig. 1. Block diagram of the DVCC.

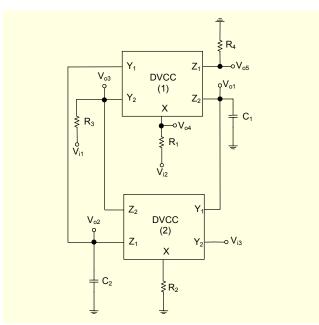

The proposed versatile universal voltage-mode circuit comprises two DVCCs, two grounded capacitors and four resistors, as shown in Fig. 2. The use of grounded capacitors is particularly attractive for integrated circuit implementation [25]. Derived by each nodal equation of the proposed circuit, the input-output relationship matrix form of Fig. 2 can be expressed as

$$\begin{bmatrix} sC_1 & G_1 & -G_1 & 0 & 0 \\ -G_2 & sC_2 & 0 & 0 & 0 \\ G_2 & 0 & G_3 & 0 & 0 \\ 0 & -1 & 1 & 1 & 0 \\ 0 & -G_1 & G_1 & 0 & G_4 \end{bmatrix} \begin{bmatrix} V_{o1} \\ V_{o2} \\ V_{o3} \\ V_{o4} \\ V_{o5} \end{bmatrix} = \begin{bmatrix} G_1V_{i2} \\ -G_2V_{i3} \\ G_3V_{i1} + G_2V_{i3} \\ 0 \\ -G_1V_{i2} \end{bmatrix}, (2)$$

where

$$G_1 = \frac{1}{R_1}$$

,  $G_2 = \frac{1}{R_2}$ ,  $G_3 = \frac{1}{R_3}$ , and  $G_4 = \frac{1}{R_4}$ .

From the above matrix form, the following five output voltages can be derived:

$$V_{o1} = \frac{1}{\Delta} [(sC_2G_1G_3)V_{i1} + (sC_2G_1G_3)V_{i2} + (sC_2G_1G_2 + G_1G_2G_3)V_{i3}],$$

(3)

$$V_{o2} = \frac{1}{\Delta} [(G_1 G_2 G_3) V_{i1} + (G_1 G_2 G_3) V_{i2} - (s C_1 G_2 G_3) V_{i3}], \tag{4}$$

$$V_{o3} = \frac{1}{\Delta} [(s^2 C_1 C_2 G_3 + G_1 G_2 G_3) V_{i1} - (s C_2 G_1 G_2) V_{i2} + (s^2 C_1 C_2 G_2) V_{i3}],$$

(5)

Fig. 2. Block diagram of the proposed versatile voltage-mode biquad based on DVCCs.

$$V_{o4} = \frac{1}{\Delta} \left[ -(s^2 C_1 C_2 G_3) V_{i1} + (s C_2 G_1 G_2 + G_1 G_2 G_3) V_{i2} - (s^2 C_1 C_2 G_2 + s C_1 G_2 G_3) V_{i3} \right],$$

(6)

$$V_{o5} = \frac{1}{\Delta} \left( \frac{G_1}{G_4} \right) \left[ -(s^2 C_1 C_2 G_3) V_{i1} - (s^2 C_1 C_2 G_3) V_{i2} - (s^2 C_1 C_2 G_3 + s C_1 G_2 G_3) V_{i3} \right], \tag{7}$$

where

$$\Delta = s^2 C_1 C_2 G_3 + s C_2 G_1 G_2 + G_1 G_2 G_3. \tag{8}$$

Depending on the status of the three biquad input voltages,  $V_{i1}$ ,  $V_{i2}$ , and  $V_{i3}$ , numerous filter functions are obtained. There are two cases shown as follows.

**Case 1**. If  $V_{i2} = V_{i3} = 0$  and  $V_{i1} = V_{in}$ , then

$$\frac{V_{o1}}{V_{in}} = \frac{1}{\Delta} (sC_2 G_1 G_3) , \qquad (9)$$

$$\frac{V_{o2}}{V_{in}} = \frac{1}{\Delta} (G_1 G_2 G_3) , \qquad (10)$$

$$\frac{V_{o3}}{V} = \frac{1}{\Delta} (s^2 C_1 C_2 G_3 + G_1 G_2 G_3), \qquad (11)$$

$$\frac{V_{o4}}{V_{in}} = \frac{1}{\Delta} \left( -s^2 C_1 C_2 G_3 \right), \tag{12}$$

$$\frac{V_{o5}}{V_{in}} = \frac{1}{\Delta} \left[ -\left(\frac{G_1}{G_4}\right) (s^2 C_1 C_2 G_3) \right], \tag{13}$$

where

$$\Delta = s^2 C_1 C_2 G_3 + s C_2 G_1 G_2 + G_1 G_2 G_3. \tag{14}$$

It can be seen from (9) to (13) that a BP filter response is obtained from  $V_{o1}$ , an LP filter response is obtained from  $V_{o2}$ , a BR filter response is obtained from  $V_{o3}$ , and two HP filter responses are obtained from  $V_{o4}$  and  $V_{o5}$ , respectively. If  $V_{i3} = 0$  and  $V_{i1} = V_{i2} = V_{in}$ , then the AP transfer function is easily obtained from the node of  $V_{o3}$  as

$$\frac{V_{o3}}{V_{in}} = \frac{s^2 C_1 C_2 G_3 - s C_2 G_1 G_2 + G_1 G_2 G_3}{s^2 C_1 C_2 G_3 + s C_2 G_1 G_2 + G_1 G_2 G_3}.$$

(15)

Obviously, from (9) to (15), it can be seen that the proposed circuit is a universal voltage-mode filter, too. Also, (9) to (15) demonstrate that the BP gain constant  $H_{\rm BP}$ , the LP gain constant  $H_{\rm LP}$ , the BR gain constant  $H_{\rm BP}$ , the first HP gain constant  $H_{\rm HPI}$ , the second HP gain constant  $H_{\rm HPI}$ , and the AP gain constant  $H_{\rm AP}$  are given by

$$H_{\mathrm{BP}} = \frac{G_{\mathrm{3}}}{G_{\mathrm{2}}}, H_{\mathrm{LP}} = H_{\mathrm{BR}} = 1, H_{\mathrm{HP1}} = -1, H_{\mathrm{HP2}} = -\frac{G_{\mathrm{1}}}{G_{\mathrm{4}}},$$

and

$$H_{AP} = 1$$

. (16)

Case 2. The specialization of the numerators in (4) and (5) result in the five generic filter functions:

- (i) lowpass:  $V_{i3} = 0$ ,  $V_{i1} = V_{in}$  or  $V_{i2} = V_{in}$ , and  $V_{out} = V_{o2}$ ;

- (ii) bandpass:  $V_{i1} = V_{i3} = 0$ ,  $V_{i2} = V_{in}$ , and  $V_{out} = V_{o3}$ ;

- (iii) highpass:  $V_{i1} = V_{i2} = 0$ ,  $V_{i3} = V_{in}$ , and  $V_{out} = V_{o3}$ ;

- (iv) bandreject:  $V_{i2} = V_{i3} = 0$ ,  $V_{i1} = V_{in}$ , and  $V_{out} = V_{o3}$ ;

- (v) allpass:  $V_{i3} = 0$ ,  $V_{i1} = V_{i2} = V_{in}$ , and  $V_{out} = V_{o3}$ .

Note that there are not any component-matching conditions and inverting-type voltage input signals to realize all of the filter responses. In all cases the resonance angular frequency  $\omega_0$  and quality factor Q are given by

$$\omega_o = \sqrt{\frac{G_1 G_2}{C_1 C_2}} \quad \text{and} \quad Q = G_3 \sqrt{\frac{C_1}{C_2 G_1 G_2}}$$

(17)

The  $\omega_o$  and Q can be properly controlled by  $G_1$  and/or  $G_2$  and  $G_3$ , in that order.

From cases 1 and 2, we can note that the proposed circuit can act as a universal voltage-mode with single input and five outputs and can realize voltage-mode BR, LP, BP, and two HP filter signals from the five output terminals, without any component-matching conditions. When another input signal is inserted into the circuit, the AP filter response can be easily

realized without any component-matching condition. On the other hand, it also can act as a universal voltage-mode filter with three inputs and two outputs and can realize five generic voltage-mode filter signals from the same configuration without any component-matching conditions and inverting-type voltage input signals to realize all of the filter responses. Obviously, the filter configuration with multiple inputs and multiple outputs seems to be more suitable than a single input and multiple outputs configuration or the multiple inputs and a single output configuration.

## III. Effect of Non-idealities

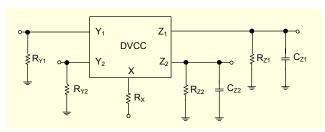

Equations (3) to (17) have been obtained by considering the ideal description of the DVCC. Ports Y1 and Y2 exhibit an infinite input resistance. Port X exhibits zero input resistance and the output ports  $Z_1$  and  $Z_2$  show an infinite output resistance. Practically, when implementing the active element using transistors, these resistances assume some finite value depending upon the device parameters. Similarly, the high frequency effects also need to be accounted for by assuming capacitances at these ports. The non-ideal DVCC symbol with various parasitic elements is shown in Fig. 3. It is shown that port X exhibits low-value parasitic serial resistance Rx, and ports Y<sub>1</sub> and Y<sub>2</sub> exhibit high-value parasitic resistance R<sub>Y1</sub> and  $R_{Y2}$ , respectively. The ports  $Z_1$  and  $Z_2$  exhibit high-value parasitic resistance R<sub>Z1</sub> and R<sub>Z2</sub> in parallel with low-value capacitors  $C_{Z1}$  and  $C_{Z2}$ . It is to be noted that the proposed circuit employs resistors at the X terminals of the DVCCs; therefore, most of the parasitic R<sub>x</sub> can be easily merged.

Taking the non-idealities of the DVCC into account, the relationships of the terminal voltages and currents can be rewritten as  $V_X = \beta_{1k}(s)V_{Y1} - \beta_{2k}(s)V_{Y2} + R_XI_X$ ,  $I_{Y1} = I_{Y2} = 0$ ,  $I_{Z1} = +\alpha_{1k}(s)I_X$ ,  $I_{Z2} = -\alpha_{2k}(s)I_X$ , where  $\beta_{1k}(s)$  represents the voltage transfers from the  $V_{Y1}$  terminal to the  $V_X$  terminal of the k-th DVCC,  $\beta_{2k}(s)$  represents the voltage transfers from  $V_{Y2}$  terminal to  $V_X$  terminal of the k-th DVCC,  $\alpha_{1k}(s)$  represents the current transfers from  $I_X$  terminal to  $I_{Z1}$  terminal of the k-th DVCC, and  $\alpha_{2k}(s)$  represents the current transfers from  $I_X$  terminal of the k-th

Fig. 3. Blick diagram of the DVCC with its parasitic elements.

DVCC. Thus,  $\alpha_{1k}(s)$ ,  $\alpha_{2k}(s)$ ,  $\beta_{1k}(s)$ , and  $\beta_{2k}(s)$  can be approximated by LP functions, which can be considered to have a unity value for frequencies much lower than their corner frequencies [3]-[7]. By assuming the circuit is working at frequencies much lower than the corner frequencies of  $\alpha_{2k}(s), \quad \beta_{1k}(s),$ and  $\beta_{2k}(s)$ ,  $\beta_{1k}(s) = \beta_{1k} = 1 - \varepsilon_{1kv}$  and  $\varepsilon_{1kv}$  ( $|\varepsilon_{1kv}| \langle \langle 1 \rangle$ ) which denotes the voltage tracking error from the  $V_{Y1}$  terminal to the  $V_X$ terminal of the k-th DVCC,  $\beta_{2k}(s) = \beta_{2k} = 1 - \varepsilon_{2kv}$  and  $arepsilon_{2k \nu}$  ( $\left|arepsilon_{2k \nu}\right|$   $\left<\left<\right>$  1) which denotes the voltage tracking error from the  $V_{Y2}$  terminal to the  $V_X$  terminal of the k-th DVCC,  $\alpha_{1k}(s) = \alpha_{1k} = 1 - \varepsilon_{1ki}$ , and  $\varepsilon_{1ki}(\varepsilon_{1ki}) < 1$  which denotes the current tracking error from the  $I_X$  terminal to the  $I_{Z1}$  of the kth DVCC, and  $\alpha_{2k}(s) = \alpha_{21k} = 1 - \varepsilon_{2ki}$  and  $\varepsilon_{2ki}$  $(|\varepsilon_{2ki}| \langle \langle 1)$  which denote the current tracking error from  $I_X$ terminal to  $I_{\mathbb{Z}}$  of the k-th DVCC, the denominator of the transfer functions becomes

$$D(s) = s^{2}C_{1}C_{2}G_{3} + \alpha_{21}\alpha_{22}\beta_{12}\beta_{21}sC_{2}G_{1}G_{2}'$$

$$+ \alpha_{12}\alpha_{21}\beta_{11}\beta_{12}G_{1}G_{2}G_{3},$$

(18)

where

$$G_1' = \frac{1}{R_{X1} + R_1}$$

,  $G_2' = \frac{1}{R_{X2} + R_2}$ , and  $G_3 = \frac{1}{R_3}$ .

The resonance angular frequency  $\,\omega_{o}\,$  and quality factor Q are obtained by

$$\omega_o = \sqrt{\frac{\alpha_{12}\alpha_{21}\beta_{11}\beta_{12}G_1G_2}{C_1C_2}},$$

(19)

$$Q = \frac{G_3}{\alpha_{22}\beta_{21}} \sqrt{\frac{\alpha_{12}\beta_{11}C_1}{\alpha_{21}\beta_{12}C_2G_1'G_2'}} . \tag{20}$$

The low active and passive sensitivities of  $\omega_o$  and Q are shown as

$$S_{\alpha_{12}}^{\omega_o} = S_{\alpha_{21}}^{\omega_o} = S_{\beta_{11}}^{\omega_o} = S_{\beta_{12}}^{\omega_o} = S_{G_1^{-}}^{\omega_o} = S_{G_2^{-}}^{\omega_o} = \frac{1}{2}, \tag{21}$$

$$S_{C_1}^{\omega_o} = S_{C_2}^{\omega_o} = -\frac{1}{2},\tag{22}$$

$$S_{\alpha_{12}}^{\mathcal{Q}} = S_{\beta_{11}}^{\mathcal{Q}} = S_{C_1}^{\mathcal{Q}} = \frac{1}{2},$$

(23)

$$S_{\alpha_{21}}^{\mathcal{Q}} = S_{\beta_{12}}^{\mathcal{Q}} = S_{C_2}^{\mathcal{Q}} = S_{G_1^{'}}^{\mathcal{Q}} = S_{G_2^{'}}^{\mathcal{Q}} = -\frac{1}{2},$$

(24)

$$S_{G_3}^{\mathcal{Q}} = 1, \qquad (25)$$

$$S_{\alpha_{22}}^{Q} = S_{\beta_{21}}^{Q} = -1$$

. (26)

## IV. Simulation Results

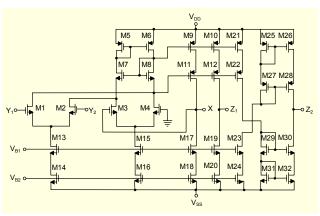

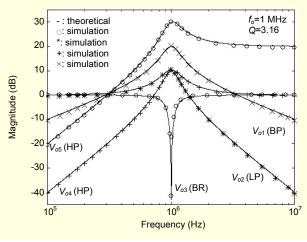

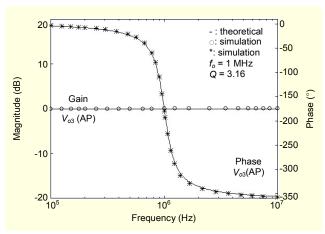

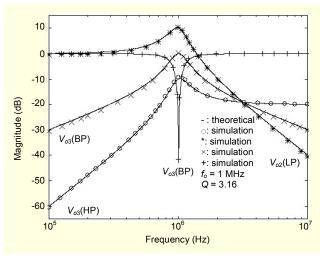

Finally, to verify the theoretical prediction of the proposed biquad circuit, a simulation using H-Spice with a TSMC 0.25 μm process [26] was performed. The symmetrical cascaded CMOS implementation of the DVCC is shown in Fig. 4 [4] with the NMOS and PMOS transistor aspect ratios  $(W/L = 5\mu/1\mu)$  and  $(W/L = 10\mu/1\mu)$ , respectively. The supply voltages were  $V_{DD}$ =- $V_{SS}$ =1.25 V, and the biasing voltages were  $V_{B1}$ =-0.2 V and  $V_{B2}$ =-0.45 V. The proposed circuit was designed for f<sub>0</sub>=1 MHz and Q=3.16 by choosing  $R_1 = R_3 = 5 \text{ k}\Omega$ ,  $R_2 = R_4 = 50 \text{ k}\Omega$ , and  $C_1 = C_2 = 10 \text{ pF}$ . Figure 5 shows the simulated amplitude responses for the BR, LP, BP, and two HP filters of Fig. 2 with  $V_{i2}=V_{i3}=0$ , and  $V_{i1}=V_{in}$ . Figure 6 shows the simulated amplitude and phase responses for the AP filter at the output  $V_{o3}$  of Fig. 2 with  $V_{i3}$ =0, and  $V_{i1}=V_{i2}=V_{in}$ . Figure 7 shows the simulated amplitude responses for the BR, LP, BP, and HP filters in case 2 of Fig. 2. As can be seen, there is a close agreement between theory and simulation.

Fig. 4. CMOS implementation of DVCC.

Fig. 5. Amplitude–frequency responses in case 1 of Fig. 2.

Fig. 6. Amplitude–frequency response and phase–frequency response of Fig. 2 with  $V_{i3}$ = 0 and  $V_{i1}$  =  $V_{i2}$  =  $V_{in}$ .

Fig. 7. Amplitude–frequency responses in case 2 of Fig. 2.

### V. Conclusion

In this paper, a new universal voltage-mode filter was proposed. The proposed circuit can be used as either a three-input two-output universal filter or single-input five-output multifunction filter with the same topology. It is more versatile than the universal one with a single input and multiple outputs or the universal one with multiple inputs and one or two outputs. Moreover, the proposed circuit still offers the following advantages: (i) the employment of two grounded capacitors, (ii) no need to employ inverting-type input signals, (iii) no need to impose component choice, (iv) orthogonal control of  $\omega_{\scriptscriptstyle 0}$  and Q, and (v) low active and passive sensitivity performance. H-Spice simulations with TSMC 0.25  $\mu m$  process and  $\pm 1.25\, V$  supply voltages confirm the theoretical predictions.

## References

- [1] H.O. Elwan and A.M. Soliman, "Novel CMOS Differential Voltage Current Conveyor and Its Applications," *IEE Proc. Circuits Devices Syst.*, vol. 144, no. 3, 1997, pp. 195-200.

- [2] S.S. Gupta and R. Senani, "Grounded-Capacitor Current-Mode SRCO: Novel Application of DVCCC," *Electron. Lett.*, vol. 36, no. 3, 2000, pp. 195-196.

- [3] J.W. Horng, "Current-Mode Quadrature Oscillator with Grounded Capacitors and Resistors Using Two DVCCs," *IEICE Trans. Fundamentals*, vol. E86–A, no. 8, 2003, pp. 2152-2154.

- [4] M.A. Ibrahim, S. Minaei, and H. Kuntman, "A 22.5 MH<sub>Z</sub> Current-Mode KHN-Biquad Using Differential Voltage Current Conveyor and Grounded Passive Elements," *Int. J. Electron. Commun. (AEÜ)*, vol. 59, no. 5, 2005, pp. 311-318.

- [5] M. Incekaraoglu and U. Çam, "Realization of Series and Parallel R-L and C-D Impedances Using Single Differential Voltage Current Conveyor," *Analog Integrated Circuits and Signal Processing*, vol. 43, no. 1, 2005, pp. 101-104.

- [6] S. Minaei and M.A. Ibrahim, "General Configuration for Realizing Current-Mode First-Order All-Pass Filter Using DVCC," Int. J. Electron., vol. 92, no. 6, 2005, pp. 347-356.

- [7] M.A. Ibrahim, S. Minaei, and H. Kuntman, "DVCC Based Differential-Mode All-Pass and Notch Filters with High CMRR," Int. J. Electron., vol. 93, no. 4, 2006, pp. 231-240.

- [8] J.W. Horng, J.R. Lay, C.W. Chang, and M.H. Lee, "High Input Impedance Voltage-Mode Multifunction Filters Using Plus-Type CCIIs," *Electron. Lett.*, vol. 33, no. 6, 1997, pp. 472-473.

- [9] A.M. Soliman, "Kerwin-Huelsman-Newcomb Circuit Using Current Conveyors," *Electron. Lett.*, vol. 30, no. 24, 1994, pp. 2019-2020.

- [10] R. Senani and V.K. Singh, "KHN-Equivalent Biquad Using Current Conveyors," *Electron. Lett.*, vol. 31, no. 8, 1995, pp. 626-628.

- [11] M. Higashimura and Y. Fukui, "Universal Filter Using Plus-Type CCIIs," *Electron. Lett.*, vol. 32, no. 9, 1996, pp. 810-811.

- [12] C.M. Chang, "Multifunction Biquadratic Filters Using Current Conveyors," *IEEE Trans. Circuits Syst.—II: Analog Digital Signal Processing*, vol. 44, no. 11, 1997, pp. 956-958.

- [13] C.M. Chang, B.M. Al-Hashimi, C.L. Wang, and C.W. Hung, "Single Fully Differential Current Conveyor Biquad Filters," *IEE Proc. Circuits Devices Syst.*, vol. 150, no. 5, 2003, pp. 394-398.

- [14] J.W. Horng, W.Y. Chui, and H.Y. Wei, "Voltage-Mode Highpass, Bandpass, and Lowpass Filters Using Two DDCCs," *Int. J. Electron.*, vol. 91, no. 8, 2004, pp. 461-464.

- [15] J.W. Horng, C.L. Hou, C.M. Chang, W.Y, Chung, and H.Y. Wei, "Voltage-Mode Universal Biquadratic Filters with One Input and Five Outputs," *Analog Integr. Circuits and Signal Process.*, vol. 47, no. 1, 2006, pp. 73-83.

- [16] H.P. Chen, "Universal Voltage-Mode Filter Using Only Plus-Type DDCCs," *Analog Integr. Circuits and Signal Process.*, vol. 50, no. 2, 2007, pp.137-139.

- [17] J.W. Homg, C.C. Tsai, and M.H. Lee, "Novel Universal Voltage-Mode Biquad Filter with Three Inputs and One Output Using Only Two Current Conveyors," *Int. J. Electron*, vol. 80, no. 4, 1996, pp. 543-546.

- [18] J.W. Horng, M.H. Lee, H.C. Cheng, and C.W. Chang, "New CCII-Based Voltage-Mode Universal Biquadratic Filter," *Int. J. Electron.*, vol. 82, no. 2, 1997, pp. 151-155.

- [19] S.I. Liu and J.L. Lee, "Voltage-Mode Universal Filters Using Two Current Conveyors," *Int. J. Electron.*, vol. 82, no. 2, 1997, pp. 145-149.

- [20] C.M. Chang and S.H. Tu "Universal Voltage-Mode Filter with Four Inputs and One Output Using Two CCII+s," *Int. J. Electron.*, vol. 86, no. 3, 1999, pp. 305-309.

- [21] J.W. Horng, "Voltage-Mode Universal Biquadratic Filters Using CCIIs," *IEICE Trans. Fundam. Special Section on Analog Circuit Techniques and Related Topics*, vol. E87-A, no. 2, 2004, pp. 406-409.

- [22] J.W. Horng, "High-Input Impedance Voltage-Mode Universal Biquadratic Filter Using Three Plus-Type CCIIs," *IEEE Trans.* on Circuits and Syst.—II: Analog Digital Signal Processing, vol. 48, no. 10, 2001, pp. 996-997.

- [23] J.W. Horng, "High Input Impedance Voltage-Mode Universal Biquadratic Filters with Three Inputs Using Three Plus-Type CCIIs," *Int. J. Electron*, vol. 91, no. 8, 2004, pp. 465-475.

- [24] C.M. Chang and H.P. Chen, "Single FDCCII-Based Tunable Universal Voltage-Mode Filter," *Circuits Syst. Signal Process.*, vol. 24, no. 2, 2005, pp. 221-227.

- [25] C.M. Chang and H.P. Chen, "Universal Capacitor-Grounded Voltage-Mode Filter with Three Inputs and a Single Output," *Int. J. Electron.*, vol. 90, no. 6, 2003, pp. 401-406.

- [26] E. Yuce, S. Minaei, and O. Cicekoglu, "Full-Wave Rectifier Realization Using Only Two CCII+s and NMOS Transistors," *Int. J. Electron.*, vol. 93, no. 8, 2006, pp. 533-541.

**Hua-Pin Chen** was born in Taipei, Taiwan, Republic of China, in 1966. He received the MS and PhD degrees from Chung Yuan Christian University, Chung, Taiwan, in 2001 and 2005, respectively. Since August 2005, he has been affiliated with the Department of Electronic Engineering at the De-Lin Institute of

Technology, Taiwan, as an assistant professor. His teaching and research interests are in the areas of circuits and systems, analog and digital electronics, active filter design, and current-mode signal processing.

Sung-Shiou Shen received the MSEE from the Department of Electronic Engineering, National Taiwan University of Science and Technology, in 1992. From 1992 to 1996 he worked on microwave transmitters and receivers in Chung-Shan Institute of Science and Technology, Taoyuan, Taiwan. From 1997 to 2000, he was

with the Institute of Astronomy and Astrophysics, Academia Sinica, Taipei, Taiwan, where he worked on the development of sub-millimeter astronomical telescopes. Since 2000, he has been a lecturer at the Department of Electronic Engineering, De-Lin Institute of Technology in Taiwan.