**JPE 7-1-4**

# A New PWM-Controlled Quasi-Resonant Converter for a High Efficiency PDP Sustaining Power Module

Woo-Jin Lee<sup>†</sup>, Seong-Wook Choi<sup>\*</sup>, Chong-Eun Kim<sup>\*</sup> and Gun-Woo Moon<sup>\*</sup>

<sup>†\*</sup>Dept. of Electrical Engineering and Computer Science, Korea Advanced Institute of Science and Technology, Korea

#### **ABSTRACT**

A new PWM-controlled quasi-resonant converter for a high efficiency PDP sustaining power module is proposed in this paper. The load regulation of the proposed converter can be achieved by controlling the ripple of the resonant voltage across the resonant capacitor with a bi-directional auxiliary circuit, while the main switches are operating at a fixed duty ratio and fixed switching frequency. Hence, the waveforms of the currents can be expected to be optimized from the view-point of conduction loss. Furthermore, the proposed converter has good ZVS capability, simple control circuits, no high voltage ringing problem of rectifier diodes, no DC offset of the magnetizing current and low voltage stresses of power switches. In this paper, operational principles, features of the proposed converter, and analysis and design considerations are presented. Experimental results demonstrate that the output voltage can be controlled well by the auxiliary circuit using the PWM method.

Keywords: Pulse width modulation, Quasi-resonant converter, PDP

### 1. Introduction

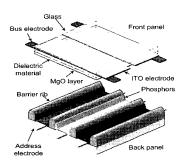

Plasma display panels (PDPs) have been considered as the best candidate for flat panel displays because of their wide viewing angle, high contrast ratio, and long life span. Fig. 1 shows a simplified structure of a PDP with three electrodes. It consists of transparent X and Y sustain electrodes covered with a dielectric layer on the front panel and address electrodes perpendicular to the sustain electrodes on the back panel as shown in Fig. 1. Due to the existence of the dielectric layer, a PDP has a purely capacitive load with respect to circuit operation [1]. Since, it not only features pure capacitive load characteristics but

is also driven by the address display separation (ADS) method, the load variation of the sustaining power module is very wide and abrupt in the case of a full-white screen as shown in Fig. 2. In the ADS method, the operation of a PDP can be divided into three periods known as the resetting, addressing, and sustaining periods. Also, the power dissipated by a PDP is the maximum in this case. However, in real PDP TVs, the load condition is strongly dependent on the average pixel level (APL), a concept that defines the total light output of a given TV image as a percentage of the total light output of a full-white image. Since TV signals typically have an APL of 20% or less [4], the sustaining power module is usually operating under light load conditions. Moreover, all PDPs have an automatic power control (APC) system that limits the power consumption to some maximum level by automatically reducing the luminance of the PDP. Thus,

Manuscript received July. 3, 2006; revised Dec. 1, 2006

<sup>&</sup>lt;sup>†</sup>Corresponding Author: gwmoon@ee.kaist.ac.kr

Tel: +82-42-869-3475, Fax: +82-42-861-3475, KAIST

<sup>\*</sup>Dept. of Electrical Engineering and Computer Science, KAIST

Fig. 1 Simplified structure of PDP with three electrodes

Fig. 2 Load current of sustaining power module

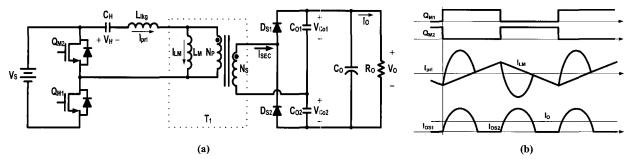

lower power is dissipated even under the full load condition which corresponds to the full-white screen [4]. Although the power dissipated during the sustaining period is less than the maximum power, it is still the highest power driving the PDP compared to that dissipated during the resetting and addressing periods. Therefore, the sustaining power module is mainly responsible for overall system efficiency [1-3]. In addition, when the PDP is operating on TV signals, high efficiency is needed primarily under light load conditions. Up to now, several DC/DC converters which can achieve high efficiency and low cost have been proposed for the sustaining power module of the PDP. Among them, resonant converters have been investigated to achieve the prominent characteristics of miniaturization, high efficiency, and low noise [7-8]. However, since a large variation in switching frequency is needed to control the output voltage, these converters have some difficulties from the view-points of size reduction and noise [9]. To overcome the above problems, recently a half bridge LLC resonant converter has been discussed because it has many unique characteristics and improvements over previous topologies [5-6]. Fig. 3 (a) shows a circuit diagram of a half bridge LLC resonant converter with a voltage doubler rectifier.

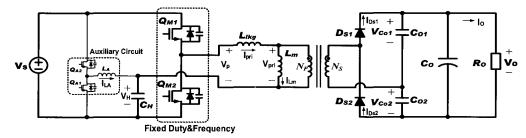

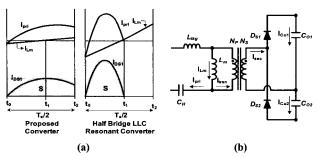

As shown in this figure, it has a simple structure and low voltage stress on primary power switches. Moreover, since there is no secondary filter inductor, the voltage across the secondary rectifier can be effectively clamped to the output voltage. Employing rectifier diodes with a low voltage rating, the conduction loss can be greatly reduced. Also, its zero-voltage-switching (ZVS) capability is excellent from zero to full load condition [6]. These features make the half bridge LLC resonant converter very suitable for use as a PDP sustaining power module. However, this converter has a small magnetizing inductance in order to have a narrow variation in switching frequency. This results in not only considerably higher circulating energy on the primary side of the transformer, but also in more conduction loss especially in the below resonance mode as shown in Fig. 3 (b). In the case of light load conditions, high circulating energy can be a serious problem that reduces the system efficiency. In addition, a variable frequency control method makes the control circuits much more complicated than those using the pulse width modulation (PWM) control method. To resolve these problems effectively, we propose a new PWM-controlled quasi-resonant converter which has simpler control circuits and less conduction loss compared to a half bridge LLC resonant converter under light load conditions. As shown in Fig. 4, the proposed converter is similar to the half bridge LLC resonant converter except for the auxiliary circuit which is needed to control the output voltage. In the proposed converter, the output voltage can be regulated by controlling the voltage across the resonant capacitor while two main switches are operating at a fixed duty ratio and fixed switching frequency. Therefore, the waveforms of both primary and secondary currents can be expected to be optimized from the view-points of conduction loss and current stress. Simultaneously, since the auxiliary circuit controls some portion of the voltage ripple on the resonant capacitor, the output voltage can be regulated well under whole load conditions. Thus, while keeping the good characteristics of a half bridge LLC resonant converter, the proposed converter is expected to sufficiently overcome the above mentioned problems such as the higher current stress and high circulating energy, and can achive high power density, high performance, and high efficiency.

Fig. 3 Half bridge LLC resonant converter with voltage doubler rectifier, (a) Circuit diagram (b) Key waveforms

Fig. 4 Circuit diagram of proposed converter

### 2. Features of the Proposed Converter

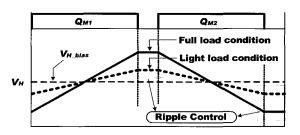

Fig. 5 shows a variation of the voltage ripple across the resonant capacitor, C<sub>H</sub>, according to load conditions in the half bridge LLC resonant converter which is a frequency controlled converter. As the load is changed from a full load to a light load, the variation of the resonant voltage ripple of C<sub>H</sub> gets smaller. This is not only because the change of switching frequency causes the same effect to change the impedance of the resonant tank which is composed of the resonant capacitor and inductor, but also because the amount of the primary current which is reflected to the load current is getting smaller. Thus, in the proposed converter, the bi-directional auxiliary circuit is operating in order to change the resonant voltage ripple using the PWM method while two power switches Q<sub>M1</sub> and Q<sub>M2</sub> are operating with a constant duty ratio (D=0.5) and constant switching frequency. Since the load regulation can be achieved by the auxiliary circuit, the magnetizing inductance of the proposed converter is larger than that of the half bridge LLC resonant converter. Thereby, the circulating energy of the proposed converter is considerably reduced under light load conditions. Additionally, due to the operating of  $Q_{M1}$  and  $Q_{M2}$  with a fixed duty ratio and fixed frequency, the primary current can be optimized from the view-points of conduction loss. Fig. 6 (a) shows the comparison of current waveforms for the proposed converter and the half bridge LLC resonant converter. In each case, the load current is the same as the average value of IDS1 because of the capacitive output filter. Therefore, the peak value of I<sub>DS1</sub> in the proposed converter must be smaller than that of IDS1 in the conventional converter under the same load condition. This can be similarly applied to the primary side of the transformer. Thus, to reduce the conduction loss, the waveforms of the current in the proposed converter are very reasonable. On the other hand, the proposed converter employs a voltage doubler type rectifier which has no output inductor. Due to the lack of an output inductor, there is no high voltage ringing across the rectifier diode. Also, by choosing the proper capacitance

Fig. 5 Variation of voltage ripple across resonant capacitor, C<sub>H</sub> according to load conditions

Fig. 6 Simplified waveforms and circuit (a) Comparison of current waveforms (b) Zero DC offset of magnetizing current

of C<sub>01</sub> and C<sub>02</sub>, the additional resonant voltage ripple of C<sub>01</sub> and C<sub>02</sub> helps the variation of the resonant voltage ripple of C<sub>H</sub>, which is controlled by the auxiliary circuit. Moreover, no DC offsets of the magnetizing current and magnetic flux can be achieved. Considering the DC value of the current through the capacitor is 0A in steady state, the DC values of  $I_{pri}$ ,  $I_{Co1}$ , and  $I_{Co2}$  ( $\langle I_{pri} \rangle$ ,  $\langle I_{Co1} \rangle$ , and  $\langle I_{Co2} \rangle$ , respectively) are all 0A, where  $\langle \bullet \rangle$  means the DC value of '•'. As shown in Fig. 6 (b), I<sub>sec</sub> is equal to  $<I_{sec}>=<I_{Co1}>-<I_{Co2}>=0A.$  $I_{\text{Co1}}$ - $I_{\text{Co2}}$ ,  $<I_{Lm}>=<I_{pri}>+<I_{tran}>=0A$ , because  $<I_{tran}>=<I_{sec}/n>=0A$ . This means that the DC offsets of the transformer magnetizing current and magnetic flux are completely blocked. Therefore, the transformer magnetic core is fully utilized, and its power density can be considerably increased while the heat generation of the transformer can be greatly reduced. Also, the control circuits which generate the gate signals for all power switches, can be easily implemented by using TL494.

#### 3. Operational Principles

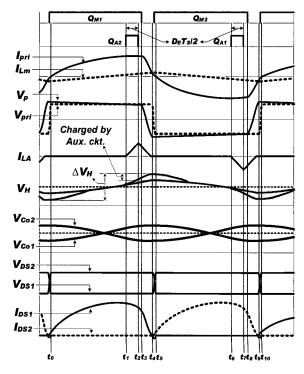

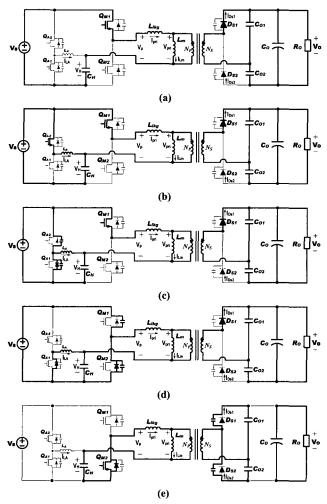

Fig. 7 shows the key waveforms of the proposed converter. The operation of the proposed converter can be divided into ten modes. One switching cycle of the proposed circuit is divided into two half cycles,  $t_0 \sim t_5$  and  $t_5 \sim t_{10}$ . Since the operational principles of two half cycles are symmetric, only the first half cycle is explained. A half cycle can be divided into 5 modes and its equivalent circuits are shown in Fig. 8. The switches of  $Q_{M1}$  and  $Q_{M2}$  are turned on and off alternately with a constant duty ratio (D=0.5) and constant frequency. And the auxiliary switches such as  $Q_{A1}$  and  $Q_{A2}$  are turned on and off in duty

cycle and controlled, where  $D_E T_S$  is the operational conduction time of the auxiliary switches. To illustrate the steady state operation, several assumptions are made as follows:

- The power switches such as  $Q_{M1}$ ,  $Q_{M2}$ ,  $Q_{A1}$ , and  $Q_{A2}$  are ideal except for their internal diodes and output capacitors,  $C_{oss}$ .

- The rectifier diodes  $D_{S1}$  and  $D_{S2}$  are ideal except for their junction capacitors,  $C_i$ .

- The output voltage  $V_0$  is constant during a switching period.

Mode 1 (t₀~t₁): After the ZVS turned on, the Q<sub>M1</sub> is achieved and the commutation between D<sub>S1</sub> and D<sub>S2</sub> is completed, Mode 1 begins. The primary current I<sub>pri</sub>, which rises with resonance between the leakage inductor and resonant capacitor, is given by

$$I_{pri}(t) = \frac{1}{nZ_0} \left[ \frac{V_S}{n} - \frac{V_H(t_0)}{n} - V_{Col}(t_0) \right] \sin \omega_r(t - t_1) + I_{Lm}(t) \quad (1)$$

Concurrently, the magnetizing current,  $I_{Lm}$ , also rises with the resonance between the magnetizing inductor  $L_m$ , and rectifier capacitors  $C_{o1}//C_{o2}$ . On the other hand, since the resonant frequency,  $f_m$ , determined by  $L_m$  and  $C_{o1}//C_{o2}$ , is

Fig. 7 Key waveforms of proposed converter

Fig. 8 Equivalent circuits of proposed converter, (a) Mode 1 (b) Mode 2 (c) Mode 3 (d) Mode 4 (e) Mode 5

much slower than the switching frequency,  $I_{Lm}$  can be linearly approximated as follows:

$$I_{Lm}(t) = I_{Lm}(t_1) + \frac{nV_{Co1}(t)}{L_m}(t - t_1).$$

$$(2)$$

where,  $\omega = \frac{1}{\sqrt{LC}}, Z_0 = \sqrt{\frac{L}{C}}, L = \frac{L_{dig}}{n^2}, C = \frac{n^2C_H \times C_{01}//C_{02}}{n^2C_H + C_{01}//C_{02}}, n = \frac{N_p}{N_s}$

The current of the rectifier diode  $D_{S1}$ ,  $I_{DS1}$ , flows through  $C_{o1}$  and the equivalent load resistor, while the rectifier capacitor  $C_{o1}$  and  $C_{o2}$  is charged and discharged respectively.

Mode 2 (t₁~t₂): When QA2 is turned on, mode 2 begins. During this mode, the resonant capacitor, CH, is additionally charged from the input source, VS, through the auxiliary inductor LA operating in discontinuous

conduction mode (DCM). It is assumed that  $L_A$  is large enough to approximate  $I_{LA}$  which is increased and decreased linearly. The slope of  $I_{LA}$  can be obtained as follows:

$$\frac{dI_{LA}(t)}{dt} = \frac{V_S - V_H(t)}{L_A} \,. \tag{3}$$

The primary and secondary side of the transformer operates similarly to Mode 1.

Mode 3 (t<sub>2</sub>~t<sub>3</sub>): After Q<sub>A2</sub> is turned off, I<sub>LA</sub> starts to charge and discharge the output capacitors, Q<sub>A2</sub> and Q<sub>A1</sub>, respectively. When the voltage across Q<sub>A1</sub> becomes 0V, I<sub>LA</sub> begins to flow through the internal diode of Q<sub>A1</sub>. Since the voltage across the C<sub>H</sub>, V<sub>H</sub> is applied to L<sub>A</sub> oppositely, I<sub>LA</sub> is decreased. During this interval, C<sub>H</sub> is still charged and both of the transformer sides operate similarly to mode 1.

Mode 4 (t<sub>3</sub>~t<sub>4</sub>): When Q<sub>M1</sub> is turned off, mode 4 begins. Since I<sub>pri</sub> starts to charge and discharge the output capacitors of Q<sub>M1</sub> and Q<sub>M2</sub> respectively, the voltage across the primary side of the transformer V<sub>P</sub>, is decreased to −V<sub>S</sub>. Since the rectifier diode D<sub>S1</sub> is still conducting, the voltage across L<sub>m</sub>, V<sub>pri</sub> is maintained to be nV<sub>Co1</sub>. Thus, the negative voltage which is the same as the difference between V<sub>P</sub> and V<sub>pri</sub>, is applied to the leakage inductor, L<sub>lkg</sub>. Thereby, I<sub>pri</sub> is decreased rapidly. Also, in this interval, C<sub>H</sub> is continuously charged until I<sub>LA</sub> becomes 0A. After the voltage across Q<sub>M2</sub> becomes 0V, I<sub>pri</sub> starts to flow through the internal diode of Q<sub>M2</sub>. Thus, the ZVS condition of Q<sub>M2</sub> is satisfied. Mode 4 is finished when I<sub>pri</sub> is equal to I<sub>Lm</sub>.

**Mode 5 (t\_4 \sim t\_5):** When  $I_{pri}$  is smaller than  $I_{Lm}$ , the current of the secondary side of the transformer flows

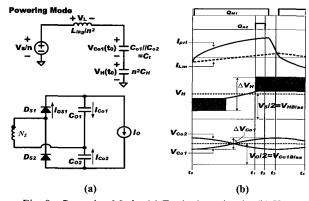

Fig. 9 Powering Mode, (a) Equivalent circuits (b) Key waveforms

oppositely through the junction capacitors,  $D_{S1}$  and  $D_{S2}$ . Since the voltage across each diode is increased and decreased respectively, the commutation between  $D_{S1}$  and  $D_{S2}$  is started. During this mode, the ZVS turned on for the  $Q_{M2}$  can be achieved. After  $D_{S2}$  is fully conducting, mode 5 is finished.

The circuit operation of  $t_5 \sim t_{10}$  is similar to that of  $t_0 \sim t_5$ . Subsequently, the operation from  $t_0$  to  $t_{10}$  is repeated.

### 4. Analysis & Design Considerations

### 4.1 Variations of V<sub>Co1</sub>, V<sub>Co2</sub>, and V<sub>H</sub>

Fig. 9 shows the equivalent circuit and its key waveforms for the analysis. Since both the time duration of  $t_2 \sim t_3$  and the dead time are much smaller than the switching period  $T_S$ , they can be discarded for simplicity of analysis. During the half switching period  $T_S/2$ , the charging current of  $C_{o1}$  is equal to the load current  $I_O$ . This is because  $C_{o1}$  must supply as much as  $I_O$  during the last half of the switching period. In addition, since the sum of  $V_{Co1}$  and  $V_{Co2}$  is always equal to the output voltage  $V_O$ , the

bias voltage of  $V_{\text{Col}}$  and  $V_{\text{Co2}}$  is  $V_{\text{O}}/2$  as shown in Fig. 9 (b). Thus, by using the equation  $I_{\text{C}}$ = $C(dV_{\text{C}}/dt)$ ,  $V_{\text{Col}}(t_0)$  can be obtained as follows:

$$dV_{Col}(t) = \frac{1}{C_{ol}} \int I_{Col}(\tau) d\tau = \frac{T_{sIo}}{2C_{ol}},$$

(4)

where,

$$\frac{2}{T_s} \int I_{Col}(\tau) d\tau = I_0$$

.

$$V_{Col}(t_0) = \frac{V_O}{2} - \frac{T_{SIO}}{4C_{Ol}}.$$

(5)

Similarly  $V_{Co2}(t_0)$  can be obtained as follows:

$$V_{Co2}(t_0) = \frac{V_O}{2} + \frac{T_S I_O}{4C_{o2}}.$$

(6)

As mentioned previously, since both  $Q_{M1}$  and  $Q_{M2}$  are operating with the constant duty ratio (D=0.5), the bias voltage of  $V_H$  is the same as  $V_S/2$ . Thus,  $V_H(t_0)$  can be represented as follows:

$$V_H(t_0) = \frac{V_S}{2} - \frac{\Delta V_H}{2} \,. \tag{7}$$

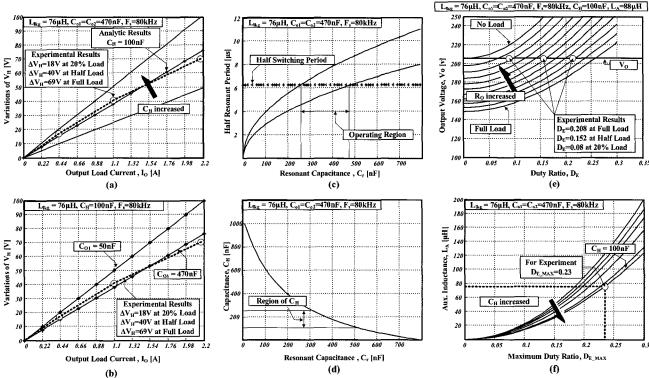

Fig. 10 Figures for analysis,

- (a) V<sub>H</sub> according to load with different C<sub>H</sub>

- (c) Desirable region of resonant frequency

- (e) Output voltage according to duty ratio D<sub>E</sub> with different load

- (b) V<sub>H</sub> according to load with different C<sub>01</sub> and C<sub>02</sub>

- (d) Selection of C<sub>H</sub>

- (f) Selection of  $L_{\text{A}}$  and maximum duty ratio  $D_{\text{E\_MAX}}$

# 4.2 Turns Ratio of the Transformer and Load Current

By using the equations (5) and (7), the current through  $D_{S1}$ ,  $I_{DS1}$  can be easily obtained from the equivalent circuit as shown in Fig. 9 (a) as follows:

$$I_{DSI}(t) = \frac{1}{Z_O} \left[ \frac{V_S}{n} - \frac{1}{n} \left( \frac{V_S}{2} - \frac{\Delta V_H}{2} \right) - \left( \frac{V_O}{2} - \frac{T_{SIO}}{4C_{o1}} \right) \right] \sin \omega_r t \quad (8)$$

The turn ratio of the transformer can be determined under no load in order to maintain  $V_O$  at the desired value without the operation of the auxiliary circuit. Thus, it can be obtained by using the equation (8) with the following conditions  $I_O=0A$ ,  $I_{DS1}=0A$ ,  $\Delta V_H=0V$ , and  $\sin \omega_{rt} \neq 0$ .

$$n = \frac{V_S}{V_O} \,. \tag{9}$$

Since both the charging current of  $C_{o1}$  and the discharging current of  $C_{o2}$  flow through  $D_{S1}$ , the average value of  $I_{DS1}$  during  $T_S/2$  is equal to two times  $I_O$ . From this fact,  $I_O$  can be represented as follows:

$$Io = \left[ \frac{V_S}{n} - \frac{1}{n} \left( \frac{V_S}{2} - \frac{\Delta V_H}{2} \right) - \left( \frac{V_O}{2} - \frac{T_S I_O}{4C_{o1}} \right) \right] \times \frac{1}{Z_O T_S \omega_r} \left[ 1 - \cos \left( \frac{T_S \omega_r}{2} \right) \right]. \tag{10}$$

From the equation (10),  $\Delta V_H$  can be expressed as the following equation.

$$\Delta V_H = 2n \frac{IoZoTs\omega_r}{1 - \cos(Ts\omega_r/2)} - 2n \left(\frac{V_S}{2n} - \frac{V_O}{2} + \frac{T_SI_O}{4C_{o1}}\right) \quad (11)$$

As shown in Fig. 10 (a) and (b),  $\Delta V_H/2$  can be plotted by using the equation (11) according to  $I_O$  under different conditions. Fig. 10 (a) shows  $\Delta V_H/2$  with a fixed value of  $C_{o1}$  and  $C_{o2}$  while  $C_H$  is varied. Similarly, Fig. 10 (b) shows it with a fixed value of  $C_H$  while  $C_{o1}$  and  $C_{o2}$  are varied. As can be seen in these figures, to regulate the output voltage according to load conditions,  $\Delta V_H/2$  gets larger as the load approaches a full load.

### 4.3 Resonant Frequency vs. Switching Frequency

As mentioned above, the waveform of  $I_{pri}$  should be similar to that of the proposed converter as shown in Fig. 6 (a) so as to reduce the conduction loss. Therefore, the

resonant frequency, which is decided by the resonant inductance and capacitance, should be selected according to the switching frequency. Fig. 10 (c) shows the desirable region of resonant frequency when the switching frequency is fixed as 80kHz. To be optimized about the conduction loss, the resonant frequency should be selected within the operating region. After the resonant frequency is selected,  $C_H$  can be decided with the resonant inductance  $76\mu H$ , as shown in Fig. 10 (d). Also, the values of  $C_{o1}$  and  $C_{o2}$  can be obtained properly by using the equation (11) and Fig. 10 (a) and (b).

# 4.4 DC conversion ratio and Maximum duty ratio according to auxiliary inductor, L<sub>A</sub>

$\Delta V_H$ , which is controlled by the auxiliary circuit, can be obtained in a similar way as mentioned in 4.1.

$$\Delta V_H = \frac{1}{C_H L_A} \left[ \frac{V_S}{2} - \frac{T_S I_O}{2nC_H} \right] \left( T_S D_E \right)^2. \tag{12}$$

From equations (10) and (12), the steady state voltage conversion ratio of the overall system can be derived as follows:

$$\frac{V_O}{V_S} = \frac{\frac{1}{2} + \frac{\left(T_S D_E\right)^2}{4C_H L_A}}{\frac{T_S}{R_O} \left[\frac{nZ_O \omega_r}{1 - \cos\left(T_S \omega_r/2\right)} - \frac{n}{4C_{O1}} + \frac{\left(T_S D_E\right)^2}{2C_H L_A}\right] + \frac{n}{2}}$$

(13)

Using equation (13), the output voltage can be plotted as shown in Fig. 10 (e). In this figure, the output voltage can be obtained without the operation of the auxiliary circuit

Table 1 Parameters of prototype circuit

| ltem                        | Symbol                            | Value/Part  |

|-----------------------------|-----------------------------------|-------------|

| Input Voltage               | V <sub>in</sub>                   | 390~410V    |

| Output Voltage              | <b>V</b> o                        | 205V        |

| Max. Power Rating           | P <sub>max</sub>                  | 451W        |

| Switching Frequency         | Fs                                | 80kHz       |

| Turn Ratio                  | n:1                               | 1.96:1      |

| Leakage inductance          | $L_{lkg}$                         | 76uH        |

| Magnetizing inductance      | Lm                                | 1.2mH       |

| Capacitance of half bridge  | Сн                                | 100nF       |

| Capacitance of doubler cell | C <sub>01</sub> ,C <sub>02</sub>  | 470nF       |

| Output Capacitance          | C.                                | 680 uF/250V |

| Main Power Switches         | Q <sub>M1</sub> , Q <sub>M2</sub> | IRFPC60     |

| Auxiliary Power Switches    | Q <sub>A1</sub> , Q <sub>A2</sub> | FQP2N60     |

| Auxiliary Inductor          | LA                                | 88uH        |

| Rectifier Diodes            | D <sub>S1</sub> , D <sub>S2</sub> | 15ETH03     |

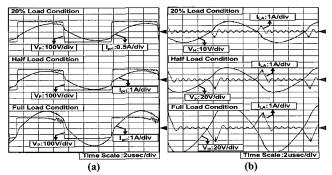

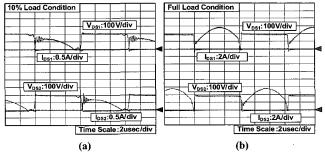

Fig. 11 Experimental waveforms at 20%, half, and full load, (a)  $V_P$  and  $I_{pri}$  (b)  $V_H$  and  $I_{LA}$

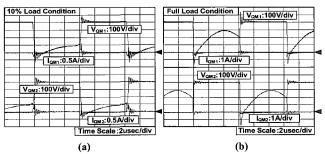

Fig. 12 ZVS of Q<sub>M1</sub> and Q<sub>M2</sub> (a) At 10% load (b) At full load

Fig. 13 ZCS of D<sub>S1</sub> and D<sub>S2</sub>, (a) At 10% load (b) At full load

under no load ( $D_E$ =0). As the load approaches a full load,  $D_E$  is increased to get the desired output voltage. From this figure, the output voltage can be regulated well under a full load condition by the auxiliary circuit. Fig. 10 (f) shows the proper auxiliary inductance needed to achieve the load regulation according to the maximum duty ratio  $D_{E\text{-MAX}}$ . As shown in this figure, when  $L_A$  is selected as the larger value to reduce the peak value of  $I_{LA}$ , the larger maximum duty ratio is needed.

### 5. Experimental Results

A 450W prototype of the proposed converter has been

built for the experiment. The parameters of this prototype circuit are listed in Table 1. Fig. 11 shows the experimental waveforms at 20%, half, and full load. As can be seen in Fig. 11 (a), the waveform of I<sub>pri</sub> is similar to that above resonance mode. This results in less conduction loss and lower peak values of I<sub>pri</sub>, I<sub>DS1</sub>, and I<sub>DS2</sub>. Fig. 11 (b) shows V<sub>H</sub> and I<sub>LA</sub> at each load. As can be seen in this figure, CH is additionally charged or discharged by ILA to regulate the output voltage. The ZVS operation of Q<sub>M1</sub> and Q<sub>M2</sub> at 10% and full load is shown in Fig. 12. In order to have the waveforms of current in BRM, the leakage inductance is rather large compared with that of the half bridge LLC resonant converter. Due to the large leakage inductance, the ZVS operation of Q<sub>M1</sub> and Q<sub>M2</sub> is easily achieved even at 10% load as shown in Fig. 12. Fig. 13 shows the ZCS operation of  $D_{S1}$  and  $D_{S2}$ . Also, in this figure, the voltage across the D<sub>S1</sub> and D<sub>S2</sub> can be clamped to the output voltage without high voltage ringing.

### 6. Conclusions

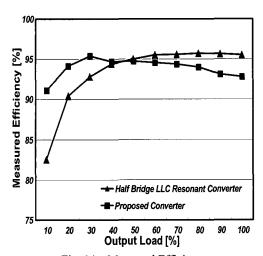

A new PWM-controlled quasi-resonant converter for a high efficiency PDP sustaining power module is proposed in this paper. Since the load regulation of the proposed converter can be achieved by an auxiliary circuit, the waveforms of the current can be optimized from the view-points of the conduction loss especially under light load conditions. Moreover, by employing a voltage doubler type rectifier, additional resonant ripple of the voltage across the rectifier capacitors helps the operation of the auxiliary circuit. Besides, DC offsets of the magnetizing current and magnetic flux can be completely blocked. From the experimental results, good ZVS capability of the power switches Q<sub>M1</sub> and Q<sub>M2</sub> is also proven. A prototype was used in experiments to prove the validity of the proposed converter. Fig. 14 shows the measured efficiency. The measured efficiency within the 10%~40% load range is higher than that of the half bridge LLC resonant converter. As mentioned in the introduction, when the PDP is operating on TV signals, the sustaining power module is usually operating under light load conditions. Thus, the proposed converter is expected to be suitable for the sustaining power module of the PDP. On the other hand, the measured efficiency is decreased as the

Fig. 14 Measured Efficiency

load approaches a full load. This is because the power dissipated by the auxiliary circuit is increased. However, the measured efficiency along wide load ranges shows as high as 94%. Therefore, the proposed converter demonstrates its suitability as a sustaining power module owing to its simple control circuits, low noise, and high efficiency.

### References

- [1] C. W. Roh, H. J. Kim, S. H. Lee, and M. J. Youn, "Multilevel Voltage Wave-Shaping Display Driver for AC Plasma Display Panel Application", *IEEE Journal of Solid-State Circuits*, Vol. 38, No. 6, June 2003, pp.935-947.

- [2] S. K. Han, G. W. Moon, and M. J. Youn, "Current-fed Energy-Recovery Circuit for Plasma Display Panel", *Electronics Letters*, 10<sup>th</sup> July 2003, Vol. 39, No. 14, pp.1035-1036.

- [3] S. K. Han, J. Y. Lee, G. W. Moon, M. J. Youn, C. B. Park, N. S. Jung, and J. P. Park, "A New Energy-Recovery Circuit for Plasma Display Panel", *Electronics Letters*, 18<sup>th</sup> July 2002, Vol. 38, No. 15, pp790-792.

- [4] Larry F. Webber, "Do LCD TVs Really Last Longer than PDP TVs?" *Information Display*, Society for Information Display, Aug. 2004, Vol. 20, No. 8, pp12-17.

- [5] Lazar, J. F.; Martinelli, R., "Steady-state analysis of the LLC series resonant converter" Applied Power Electronics Conference and Exposition, 2001. APEC 2001. Sixteenth Annual IEEE, Volume: 2, 2001 Page(s): 728-735 vol.2.

- [6] Bo Yang; Lee, F. C.; Zhang, A. J.; Guisong Huang, "LLC resonant converter for front end DC/DC conversion,"

- Applied Power Electronics Conference and Exposition, 2002. APEC 2002. Seventeenth Annual IEEE, Volume: 2, 2002 Page(s): 1108-1112 vol.2.

- [7] F. C. Lee: "High-Frequency Quasi-Resonant Converter Technologies", *Proc. of the IEEE*, Vol. 76, No. 4, pp.377-390, April 1988.

- [8] K. Liu and F. C. Lee: "Zero-Voltage Switching Technique in DC/DC Converters", *IEEE PESC'86*, Record, pp.58-70, June 1986.

- [9] Tanaka, H.; Ninomiya, T.; Shoyama, M.; Zaitsu, T.: "Novel PWM-controlled resonant converter" Telecommunications Energy Conference, 1996. INTELEC'96, 18<sup>th</sup> international 6-10 Oct. 1996 Page(s):823-828.

Woo-Jin Lee was born in Taegu, Korea, in 1977. He received his B.S. degree in Electrical Engineering from Kyungpook National University, Taegu, Korea, in 2004. He is currently working toward his M.S. degree in Electrical Engineering from the Korea Advanced Institute of Science and

Technology (KAIST), Daejeon, Korea. His main research interests are high efficiency DC/DC converters, and digital display drivers.

Seong-Wook Choi received his B.S. degree in electrical engineering from Dankook University, Seoul, Korea, 2002, and his M.S. degree in electrical engineering form Korea Advanced Institute of Science and Technology (KAIST), Daejeon, in 2004, where he is currently pursuing his Ph.D.

degree in electrical engineering. His research interests are in the areas of power electronics and digital display driver systems, including analysis, modeling, design, and control of power converters, soft switching power converters, step-up power converters for electric drive systems, multi-level converters and inverters, power factor correction, digital display driver systems, and EEFL back light inverters for LCD TV's. Mr. Choi is a member of the Korean Institute of Power Electronics (KIPE).

Chong-Eun Kim was born in Taegu, Korea, in 1978. He received his B.S. degree in Electrical Engineering from Kyungpook National University, Taegu, Korea, in 2001. In 2003, he received his M.S. degree in Electrical Engineering from the Korea Advanced

Institute of Science and Technology (KAIST), Daejeon, Korea, where he is currently working toward his Ph.D. degree. His main research interests are DC/DC converters, power-factor-correction (PFC) AC/DC converters, soft switching techniques, and digital audio amplifiers.

Gun-Woo Moon was born in Korea in 1966. He received the B.S. degree from Han-Yang University, Seoul, Korea, in 1990, and the M.S. and Ph.D. degrees in Electrical Engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in

1992 and 1996, respectively. He is currently an assistant professor in the department of Electrical Engineering and Computer Science at KAIST. His research interests include modeling, design and control of power converters, soft switching power converters, resonant inverters, distributed power system, power factor corrections, electrical drive systems, driver circuit of PDP and flexible AC transmission systems (FACTS). Dr. Moos is an associate member of IEEE, a member of the Korea Institute of Power Electronics (KIPE), Korea Institute of Electrical Engineering (KIEE), Korea Institute of Telematics and Electronics (KITE), and Korea Institute of Illumination Electronics and Industrial Equipment (KIEEE).