# A New Strained-Si Channel Power MOSFET for High Performance Applications

Young-Kyun Cho, Tae Moon Roh, and Jongdae Kim

ABSTRACT—We propose a novel power metal oxide semiconductor field effect transistor (MOSFET) employing a strained-Si channel structure to improve the current drivability and on-resistance characteristic of the high-voltage MOSFET. A 20 nm thick strained-Si low field channel NMOSFET with a 0.75 µm thick Si<sub>0.8</sub>Ge<sub>0.2</sub> buffer layer improved the drive current by 20% with a 25% reduction in on-resistance compared with a conventional Si channel high-voltage NMOSFET, while suppressing the breakdown voltage and subthreshold slope characteristic degradation by 6% and 8%, respectively. Also, the strained-Si high-voltage NMOSFET improved the transconductance by 28% and 52% at the linear and saturation regimes.

Keywords—High voltage, power device, strained-Si, hot electron, breakdown voltage.

# I. Introduction

High-voltage metal oxide semiconductor field effect transistors (MOSFETs), which have a high switching speed and low on-resistance characteristic compared to other power devices [1]-[3], are recognized to be the most promising power devices. However, these devices have a low transconductance (G<sub>m</sub>), small signal output resistance, and small threshold voltage, which are caused by a hot electron effect due to the large lateral electric field.

To cope with these problems, a lower doping concentrated extension region is formed [4]. The high-voltage capability was achieved through the use of an n-type diffused region outside the gate to sustain most of the drain voltage. The presence of the extension region substantially enhances the breakdown

voltage, but cannot control the low on-resistance precisely and achieve large current drivability. Typically, a 10 to 20% current and transconductance loss is present in extended drain power devices compared with conventional ones.

In this letter, we propose a novel power MOSFET employing a low electric field strained-Si channel structure in order to overcome the disadvantages of the conventional Si channel high-voltage MOSFET, such as a large electric field, high on-resistance, low G<sub>m</sub>, and low current drivability.

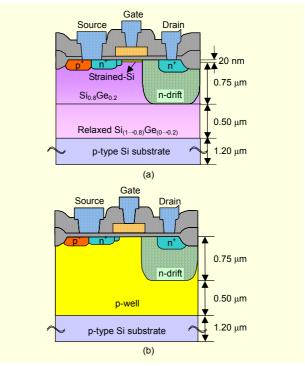

Fig. 1. Schematic figure of (a) the strained-Si channel high-voltage NMOSFET and (b) a conventional Si channel high-voltage NMOSFET.

Manuscript received Aug. 04, 2005; revised Jan. 04, 2006.

Young-Kyun Cho (phone: +82 42 860 6561, email: ykcho@etri.re.kr), Tae Moon Roh (email: tmroh@etri.re.kr), and Jongdae Kim (email: jdkim@etri.re.kr) are with IT Convergence & Components Laboratory, ETRI, Daejeon, Korea.

# II. Device Structure and Simulation

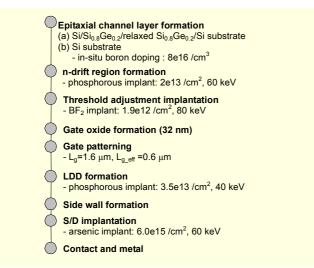

The proposed new high-voltage device and conventional high-voltage device structures are shown in Figs. 1(a) and 1(b), respectively. These devices have the same physical dimension and doping profile. The key structure steps of the proposed device are the following: a) relaxed  $Si_{(1\to 0.8)}Ge_{(0\to 0.2)}$  layer formation on the Si substrate, b) buffer Si<sub>0.8</sub>Ge<sub>0.2</sub> layer formation with uniform doping concentration on the relaxed layer, c) strained-Si layer formation for the Si channel, d) n-drift region formation for higher breakdown voltage, e) threshold adjustment implantation, f) gate oxide formation, LDD formation, side-wall formation, source/drain implantation, and g) final contact and metal. A summary of the fabrication process is represented in Fig. 2. The final Si layer thickness for the strained-Si channel is 20 nm, which can decrease the breakdown voltage but increase current drive capability of the high-voltage NMOSFET (HVNMOS). The uniform Si<sub>08</sub>Ge<sub>02</sub> layer and the relaxed Si<sub>08</sub>Ge<sub>02</sub> layer thicknesses are 0.75 and 0.5 µm, respectively, in order to form a surface strained-Si channel layer.

Fig. 2. Summary of the process sequence.

Table 1. Material properties for device simulation.

|                         | Strained-Si         | Si <sub>0.8</sub> Ge <sub>0.2</sub> |

|-------------------------|---------------------|-------------------------------------|

| Electron affinity       | 4.304 eV            | 4.17 eV                             |

| Band gap energy         | 1.0 eV              | 0.94 eV                             |

| Dielectric constant     | 11.8                | 12.64                               |

| Electron effective mass | 0.19 m <sub>0</sub> |                                     |

#### III. Results and Discussion

In the development of the HVNMOS structure, two dimensional device simulations [5] were performed for the structures of Figs. 1(a) and 1(b) with the strained-Si channel and conventional Si channel to obtain the optimized electrical characteristics and study high-voltage devices. The unstrained energy band model was chosen for SiGe, and the energy band for the strained-Si was generated based on [6] through [9]. The material properties for device simulation are summarized in Table 1.

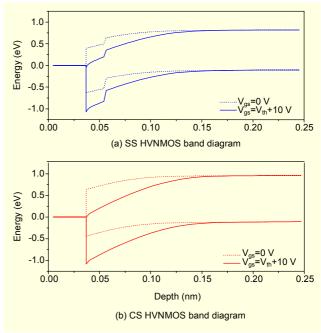

Fig. 3. Calculated energy band diagrams for (a) SS HVNMOS and (b) CS HVNMOS. The solid and dotted lines represent  $V_{gs}$ = $V_{th}$ +10 V and  $V_{gs}$ =0 V, respectively.

Figure 3 shows the calculated electronic energy band diagrams for the strained-Si channel high-voltage NMOSFET (SS HVNMOS) and conventional Si channel high-voltage NMOSFET (CS HVNMOS) at  $V_{\rm gs} = V_{\rm th} + 10~{\rm V}$  and  $V_{\rm gs} = 0~{\rm V}$ , respectively. As illustrated in Fig. 3(a), the conduction band bending due to the heterostructure is helpful to carrier confinement, and the valence band offset fully contributes to the threshold voltage shift. In other words, the negative valence band offset makes the Fermi level closer to the conduction band, and in turn, accumulates more electrons in the inversion layer for the same gate bias. Thus, the band offset lowers the threshold voltage. The simulated threshold voltages of SS HVNMOS and CS HVNMOS are 0.51 V and 0.94 V, respectively.

The modulated band profile in the strained-Si/SiGe layer

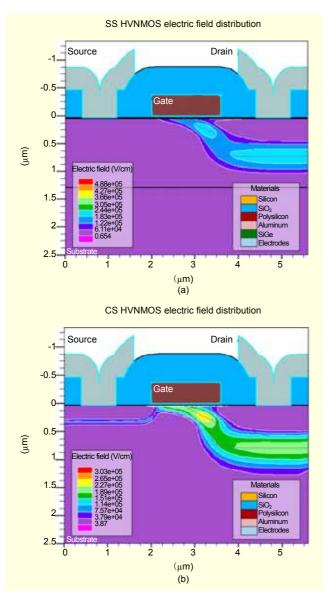

reduces the electronic energy band bending, and thus the electric field in the SS HVNMOS alleviates slightly compared with the CS HVNMOS. The simulated field distribution at the same gate overdrive condition for the devices of Figs. 1(a) and 1(b) are illustrated in Figs. 4(a) and 4(b), respectively. It can clearly be seen that the peak electrical field  $(2.4 \times 10^5 \text{ V/cm})$  at near the drain region of the SS HVNMOS is lower than that  $(2.6 \times 10^5 \text{ V/cm})$  of the CS HVNMOS. These results lead to the higher electron mobility and lower series resistance.

In spite of the smaller electric field, strained-Si devices have higher impact ionization rates compared to bulk-Si devices due to the smaller energy bandgap and longer mean-free-path. This implies that the mean-free-path in strained-Si for high current operation should be reduced from that used in the lower

Fig. 4. Simulated electric field distributions for (a) SS HVNMOS and (b) CS HVNMOS.

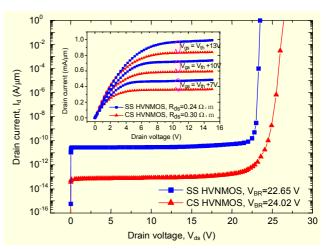

electric field regime. So, the breakdown voltage (VBR) of the SS HVNMOS is slightly lowered. The breakdown voltages of the SS HVMOS and CS HVMOS are 22.7 V and 24.0 V at the critical electric field, as shown in Fig. 5. The inset of Fig. 5 shows the drain current - drain voltage characteristics of highvoltage NMOSFETs with the strained-Si channel and the conventional Si channel. It reveals a significant current gain for the SS HVNMOS. The result could be explained as the repopulation of the energy bands produces an enhancement of the effective electron mobility, and the material properties of SiGe produce a reduction of the channel electric field. Then, the SS HVNMOS exhibited a 20% increase in drive current compared with the CS HVNMOS. The simulated onresistances ( $R_{ds}$ ) of the SS HVNMOS was 0.24  $\Omega \cdot m$ , which is about 25% lower compared with the value of 0.30  $\Omega$ ·m obtained from the CS HVNMOS.

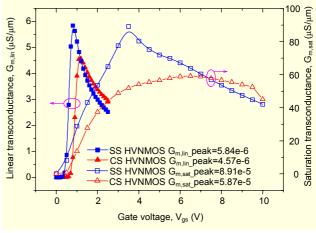

The linear and saturation transconductance characteristics of

Fig. 5. Breakdown voltage characteristics of the SS HVNMOS compared with the CS HVNMOS. The inset shows the drain current - drain voltage characteristics.

ig. 6. Linear and saturation G<sub>m</sub> characteristics of the SS HVNMOS and CS HVNMOS.

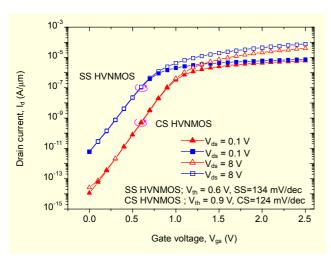

Fig. 7. Simulated subthreshold transfer characteristics of the SS HVNMOS and CS HVNMOS.

the SS HVNMOS and CS HVNMOS are shown in Fig. 6. The gate voltage at which peak transconductance occurs depends on the value of  $V_{\rm ds}$  and the device type, that is, strained-Si or control Si. The transconductance of the SS HVNMOS improved by 28% and 52% at the linear and saturation regimes, respectively, compared to the CS HVNMOS. This is due to the mobility enhancement effect of the SS HVNMOS. The subthreshold slope of the SS HVNMOS is 134 mV/dec, which is higher compared with the 124 mV/dec obtained from the CS HVNMOS as shown in Fig. 7. The thickness of the strained-Si layer is smaller than the depletion depth at zero gate bias, as illustrated in Fig. 3; the subthreshold slope degrades due to the higher depletion capacitance, as a consequence of the higher dielectric constant of SiGe and shallower channel depletion depth.

## IV. Conclusion

In summary, we propose a novel high-voltage NMOSFET structure employing a strained-Si channel structure to improve the current drive capability and on-resistance characteristic. With the slightly lowered breakdown voltage, the current drive capability and on-resistance are improved by 20% and 25%, respectively. These results indicate that the HVNMOS with a strained-Si channel is a promising candidate for a display driver integrated circuit because this device can decrease the chip size by a high current drivability.

### References

[1] A. W. Ludikhuize, "A Versatile 700-1200-V IC Process for Analog and Switching Applications," *IEEE Trans. Electron Devices*, vol.

- 38, 1991, pp. 1582-1589.

- [2] A. Nakagawa, N. Yasuhara, I. Omura, Y. Yamaguchi, T. Ogura, and T. Matsudai, "Prospects of High-Voltage Power ICs on Thin SOI," *IEEE IEDM Tech. Digest*, 1992, pp.229-232.

- [3] J. Kim, T. M. Roh, S-G Kim, I-Y. Park, Y. S. Yang, D-W Lee, J-G Koo, K-I. Cho, and YI Kang, "A Novel Process for Fabricating a High Density Trench MOSFETs for DC-DC Converters," *ETRI* J., vol. 24, 2002, pp. 333-340.

- [4] Y. Tarui et al., "Diffusion Self-Aligned Enhance-Depletion MOS-IC," J. Jpn. Soc. Appl. Phys., vol. 40, 1971, pp. 193.

- [5] Silvaco International, ATLAS User's Manual: Device Simulation Software, 2002.

- [6] R. People, "Physics and Applications of Ge<sub>x</sub>Si<sub>1-x</sub>/Si Strained-Layer Heterostructures," *IEEE Quantum Elec.*, vol. 22, 1986, pp. 1696-1710.

- [7] T. Yamada, J-R. Zhou, H. Miyata, and D. K. Ferry, "In-Plane Transport Properties of Si/Si<sub>1-x</sub>Ge<sub>x</sub> Structure and Its FET Performance by Computer Simulation," *IEEE Trans. Elec. Dev.*, vol. 41, 1994, pp. 1513-1522.

- [8] W. Zhang and J. G. Fossum, "On the Threshold Voltage of Strained-Si-Si<sub>1-x</sub>Ge<sub>x</sub> MOSFETs," *IEEE Trans. Elec. Dev.*, vol. 52, 2005, pp. 263-268.

- [9] B. Mheen, Y.-J. Song, J.-Y. Kang, and S. Hong, "Strained SiGe Complementary MOSFETs Adopting Different Thickness of Silicon Cap Layers for Low Power and High Performance Applications," ETRI J., vol. 27, no. 4, 2005, pp. 439-445.