# A Fast and Robust Approach for Modeling of Nanoscale Compound Semiconductors for High Speed Digital Applications

Anil Ahlawat\*, Manoj Pandey\*\*, and Sujata Pandey\*

Abstract—An artificial neural network model for the microwave characteristics of an InGaAs/InP hemt for 70 nm gate length has been developed. The small-signal microwave parameters have been evaluated to determine the transconductance and drain-conductance. We have further investigated the frequency characteristics of the device. The neural network training have been done using the three layer architecture using Levenberg-Marqaurdt Backpro pagation algorithm. The results have been compared with the experimental data, which shows a close agreement and the validity of our proposed model.

Index Terms—Pseudomorphic high electron mobility transistor, Levenberg-Marqaurdt Backpropagation algorithm, neural network training, drain current, gate length.

# I. Introduction

Recently, pseudomorphic high electron mobility transistors (PHEMTs) have demonstrated superior performance at microwave and millimeter wave frequency ranges [1]. InP HEMTs have higher gain, higher cutoff frequency, lower source resistance, higher maximum current densities, and higher substrate thermal conductivity compared to GaAs-based ones [2]. Improving gain at 94 GHz requires us to decrease the gate

length of HEMTs under  $0.1~\mu m$  to typically reach 70 nm or less. Nevertheless, in order to avoid short-channel effects, it is necessary to maintain an aspect ratio (gate length to gate to channel distance) larger than or equal to 5 [3]. Thus, the reduction of the gate length implies the decrease of the barrier thickness. That leads to the increase of the gate current by a tunneling effect and to the reduction of the current density due to the influence of the surface states which is directly detrimental for power performances. Pseudomorphic high electron mobility transistors with low indium content channels and channel lengths of 0.25- $0.15~\mu m$  are the workhorse of the MMIC industry [4].

The design of active linear circuits for their applications requires a simple and precise simulator model. Several approaches have been followed for modeling of semiconductor device characteristics based on the physics of the device as well as numerical techniques. These methods are limited in their applications because of their extensive computational requirements or due to the lack of accuracy and continuity in the predicted characteristics. These models are also limited in terms of accuracy and input parameter range over which they can be accurate. Neural network computational modules have recently gained recognition as a useful tool for RF and microwave modeling and design. The neural network approach is a new type of modeling approach where the model can be developed by learning from detailed (accurate) data of the RF/microwave component. After training, the neural network becomes a fast and accurate model representing the original component behavior [8].

In the present paper, we have developed a new artificial neural network model for a 70 nm gate length InGaAs/InP HEMT and for a 140 nm gate length InGaAs/GaAs

E-mail: a\_anil2000@yahoo.com, s\_pandey@ieee.org

Manuscript received May 19, 2006; revised Aug. 28, 2006.

<sup>\*</sup> School of Engineering and Technology, Guru Gobind Singh Indraprastha University, New Delhi, India

<sup>\*\*</sup> Institute of Technology and Management Sector 23 A Gurgaon, India

HEMT for its microwave application. The neural network training have been done using a three layer architecture using Levenberg-marquardt Backpropagation algorithm. The main parameters of our study are the drain to source current (I<sub>ds</sub>), transconductance (g<sub>m</sub>), drain conductance (g<sub>d</sub>), and cutoff frequency (ft). The modeling has been implemented using the neural network toolbox of MATLAB software. The data for training has been generated using the simulator MINIMOS-NT. The results have been compared with the experimental data and show a close agreement and prove the validity of our model.

# II. MODELING METHODOLOGY

## 1. Device Structure

The performance of PHEMTs has been investigated based on the experimental results reported by various foundries [5-7].

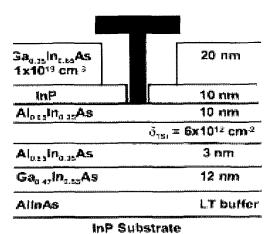

The first structure under study as shown in Fig. 1 consists of AlInAs/GaInAs HEMT on InP substrate with a T gate. An AlInAs buffer is used along with a GaInAs lattice matched channel, a barrier layer and a Ga<sub>0.35</sub>In<sub>0.65</sub>As cap layer. The barrier layer consists of a 20 nm Al<sub>0.65</sub>In<sub>0.35</sub> as strained barrier. The source/drain spacing is of 2 µm. The device has a T gate with a length of 70 nm. To avoid short channel effects we have maintained an aspect ratio equal to 5. This structure fabricated elsewhere [5] was evaluated and implemented for obtaining the device characteristics and small signal

Fig. 1. Schematic cross section of the epitaxial structure of the HEMT containing a 20-nm InP/AlInAs composite barrier.

parameters.

The second device under consideration is an  $Al_{0.25}Ga_{0.75}As/In_{0.3}Ga_{0.7}As$  PHEMT as GaAs substrate with a gate length of 140 nm and 4x40 µm gate width technology [6, 11].

#### 2. Model Formulation

Artificial Neural Network (ANN) based methods have been widely used for modeling various complex and nonlinear processes viz., pattern classification, speech recognition, and signal processing. Once developed, these neural models can be used in place of computationally intensive physics/EM models active/passive devices to speed up microwave design [9-10].

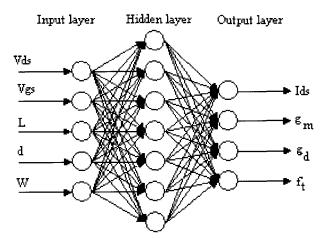

The most popular form of ANN technology is the multilayered perceptron (MLP) model having a feed-forward structure as represented in Fig. 2.

Fig. 2. Three layer Neural Network model.

In our study, inputs and outputs of our PHEMT neural model is given by

$$\begin{aligned} x &= [V_{ds}, V_{gs}, L, d, W]^{T} \\ y &= [I_{ds}, g_{m}, g_{d}, f_{t}]^{T} \end{aligned}$$

(1)

$$y = \left[I_{ds}, g_{m}, g_{d} f_{t}\right]^{T} \tag{2}$$

where x represent a vector contains the external inputs to the neural network, y represent a vector containing the outputs from the output neurons. Vas is the drain voltage, Vgs is gate voltage, L is gate length, d is the gate to channel distance, W is gate width, I<sub>ds</sub> is drain current, g<sub>m</sub> is tranconductance, and gd is drain conductance.

Generally the device parameters are expressed using the following expressions used for developing the analytical model.

Drain-Source current ( $I_{ds}$ ) in the channel is obtained from the current density equation

$$I_{ds} = Wq\mu \left( n(x) \frac{dv_c(x)}{dx} + \frac{KT}{q} \frac{dn(x)}{dx} \right)$$

(3)

where q is the electron charge,  $\mu$  is the mobility, n(x) is the electron concentration in the channel, K is the Boltzmann constant, T is the room temperature and  $\nu_c(x)$  is the channel potential.

The small-signal parameters can be obtained from the drain current model (developed from equation 3) of the device.

The transconductance is evaluated by a procedure in which small changes in the channel current due to small changes in the gate potential with drain potential held constant and is given as

$$g_{\rm m} = \left(\frac{\partial I_{\rm ds}}{\partial V_{\rm gs}}\right) \bigg|_{V_{\rm do}} \tag{4}$$

the output or drain conductance recognized by the change in the drain current with a corresponding change in drain voltage, an important parameter for microwave application is given as

$$g_{d} = \left(\frac{\partial I_{ds}}{\partial V_{ds}}\right) \bigg|_{V_{gs}}$$

(5)

an important figure of merit of a PHEMT is the current-gain cutoff frequency approximately given by

$$ft = \frac{g_m}{2\pi C_g} \tag{6}$$

where  $g_m$  is the device transconductance and  $C_g$  is the gate source capacitance and may include the drain source capacitance and all other parasitic effects.

The present neural model revolves round the basic device parameter on which the device characteristics and small signal parameters depend.

The physics/EM relationship between y (output) and x

(input) of the neural model can be represented as

$$y = y(x) \tag{7}$$

this relationship can be highly nonlinear and multidimensional. The theoretical model for this relationship may not be available or computationally too intensive for online microwave design and repetitive optimization.

We aim to develop a fast and accurate neural model for InGaAs/InP and InGaAs/GaAs PHEMT by training a neural network to learn the problem through a set of training data  $\{(x_p,d_p), p \in T_R\}$ , where  $d_p$  represents the measured/simulated output y for the sample input  $x_p$ , and  $T_R$  represents the index set of training data. The neural network model for PHEMT is given by

$$y = y(x, w). \tag{8}$$

where w be a vector containing all the weight parameters representing various interconnections in the neural network.

The objective of training is to adjust neural network weights w such that neural model outputs best match the training data outputs.

For training purpose, we define an error function E(w) as

$$E(w) = \sum_{p \in T_R} (e_p(w))^q \tag{9}$$

where q represents the  $q^{th}$  norm and  $e_p(w)$  is the error due to  $p^{th}$  sample given by

$$e_{p}(w) = \left[\frac{1}{q} \sum_{k=1}^{N_{y}} |y_{k}(x_{p}, w) - d_{pk}|^{q}\right]^{1/q}$$

(10)

where  $d_{pk}$  is the  $k^{th}$  element of  $d_p$  and  $y(x_p,w)$  is the  $k^{th}$  output of the neural network for input sample  $x_p$ .

The objective of neural network training is to find w such that E(w) is minimized. The output y is computed starting with the input layer  $z_i^0 = x_i$ , then proceeding through the hidden layers,

$$z_{i}^{l} = \sigma \left( \sum_{j=1}^{N_{i-1}} w_{ij}^{l} z_{j}^{l-1} + w_{io}^{l} \right)$$

(11)

and finally  $y_k = z_k^{L+1}$ .

$\sigma(.)$  is the neuron activation function, in our program we have applied the tan sigmoid function between input and hidden layer and pure linear function between hidden and output layer for training using the ANN toolbox available in MATLAB software.

Using the above model, we have obtained the results for the aforementioned device and small signal parameters reported in the next section.

## III. RESULTS AND DISCUSSION

We have developed an ANN model for the device drain current, transconductance, drain-conductance and cut off frequency of the InGaAs/InP and InGaAs/GaAs PHEMT as a function of the drain and gate voltages for the first time. To improve the versatility of the model, three more input parameters, viz., gate length, gate to channel distance and gate width have also been included as the input parameters of the model. The neural network model developed consists of three layers; with five neurons in the input layer corresponding to the five parameters mentioned above, thirty five neurons in the hidden layer and four neurons in the output layer. The output parameters are drain current, transconductance, drain conductance and the cut off frequency. The number of neurons in the hidden layer was optimized so as to obtain a

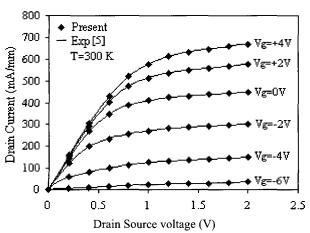

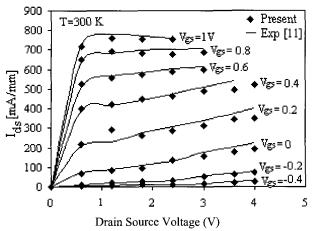

Fig. 3. I<sub>d</sub> (V<sub>ds</sub>) characteristics for 70-nm gate length InP PHEMT.

close agreement with the experimental results with least possible numerical parameters of the model. The proposed ANN model can be used to determine the device currents at various gate voltages for the InGaAs/InP and InGaAs/GaAs HEMTs device. This model can be used as the interface between device modeling and circuit simulation because ANN models are more accurate, more flexible and much faster than the existing other models.

Fig. 3 shows the variation of drain current with drain source voltage for different values of gate source voltage of a 70 nm gate length device. A gradual transition is observed as we go from linear to the saturation region, which confirms a smooth transconductance peak as predicted experimentally for nanoscale devices. A total saturation of drain current is not observed as the gate length is shortened which may be due to the flow of finite leakage current and carrier injection into the substrate, though we have maintained an aspect ratio (gate length to gate to channel distance) equal to 5 to reduce the short channel effects. As in general for all HEMT devices the gate bias controls the two dimensional electron gas density in the channel, the level of drain current is directly determined from the 2-DEG density in the channel. The results of our neural model are compared with the experimental data and show an accuracy of 98%.

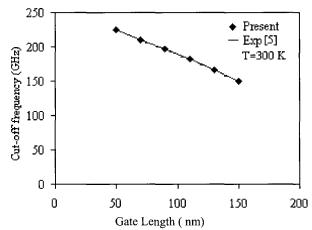

The unity gain cut off frequency that describes the microwave application of the device is plotted as a function of gate length in Fig. 4. A high cut off frequency of about 230 GHz is obtained at a gate length of 70 nm. The increase in cut off frequency is attributed by the increase in transconductance and decrease in the total

Fig. 4. variation of cut off frequency with gate length of InP PHEMT.

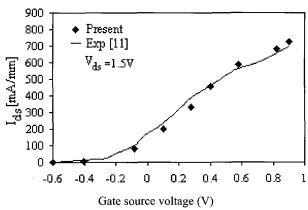

Fig. 5. Variation of drain source current with gate source voltage  $L_g = 140$  nm.

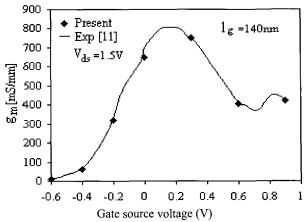

Fig. 6. Drain source current as a function of gate source voltage for Lg = 140nm.

capacitance of the device. As compared in other experimental data we see that  $f_t$  increases with the decrease in gate length.

Fig. 5 shows the current voltage characteristics using our model obtained for a HEMT with  $l_{\rm g}$  = 140 nm and 4x40  $\mu$ m gate width technology and compared with the experimental data.

Fig. 6 shows the modeled and experimental transfer characteristics of the device. I<sub>d</sub>-V<sub>gs</sub> curve shows the usual trend of increase in current with the increase in gate source voltage due to the increase in charge carriers in the channel. The exact determination of the transfer characteristics is important since it determines the device transconductance.

The variation of transconductance with gate source voltage is shown in Fig. 7. In this curve the effect of real space transfer with increasing value of gate source voltage and hence current spreads into the barrier and decreases  $g_m$ .

**Fig. 7.** Variation of Device transconductance with gate source voltage.

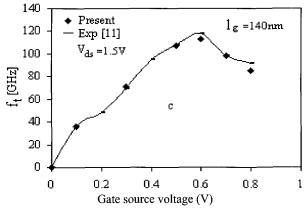

Fig. 8. Current gain cut-off frequency as a function of effective gate voltage.

The cut-off frequency is plotted as a function of gate voltages in Fig. 8.  $f_t$  generally increases with the increase in gate voltage. Fall of  $f_t$  is mainly due to the average carrier velocity that assumes a constant value. Initially as we increase the gate voltage, the sheet carrier concentration increases upto the equilibrium value after that it begins to saturate. Now, the velocity-saturated carriers, moving in a high field region are affected by various scattering mechanism and thereby decreasing the cut-off frequency.

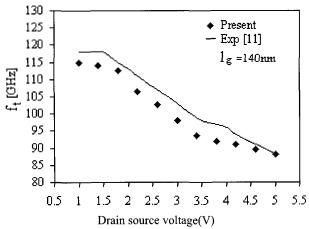

Fig. 9 shows the variation of  $f_t$  with drain voltage. At lower drain voltages normally frequency increases. But for comparison purpose we have studied the frequency behavior ant higher drain voltages. At higher values of  $V_{ds}$ ,  $g_m$  saturates but the capacitance increases so  $f_t$  is degraded.

The model has been tested in our laboratory for implementing digital circuits using compound semiconductors.

Fig. 9. Current gain cut-off frequency as a function of drain source voltage

#### IV. CONCLUSIONS

In our proposed ANN model, we characterize the dc and microwave performance of InGaAs/InP and InGaAs/GaAs PHEMT. The model provides good insight into the device structure optimization and performance prediction. In order to predict the microwave performance of the device, the model is used to analyze the current-voltage characteristics, which shows excellent agreement with the experimental data and the validity of our model. The device has good linear and saturation characteristics. The transconductance and drain-conductance are also measured. The model can be further extended to obtain the microwave characteristics of the device.

# REFERENCES

- [1] See e.g., C. S. Wu, G. L. Lan, C. K. Pao, S. X. Bar, and M. Hu, "Pseudomorphic HEMT devices for microwave and millimeter wave applications," *Mat. Res. Soc. Symp. Proc.*, vol. 300, pp. 41-54, 1993.

- [2] D.C. Streit, K. L. Tan, R. M. Dia, A. C. Han, P. H. Liu, H. C. Yen, and P. D. Chow, "High performance W-band InAlAs-InGaAs-InP HEMT," *Electron. Lett.*, vol. 27, pp. 1149-1150, 1991.

- [3] T. Enoki, M. Tomizawa, Y. Umeda, and Y. Ishii, "0.05-\_m-gate InlAs/GaInAs high electron mobility transistor and reduction of its short-channel

- effects," *Jpn. J. Appl. Phys.*, **vol.** 33, no. 1B, pp. 798–803, 1994.

- [4] Meneghesso G, Grave T, Manfredi M, Pavesi M, Canali C, Zanoni E, "Analysis of hot carrier transport in AlGaAs/InGaAs pseudomorphic HEMT's by means of electroluminescence," *IEEE Trans on Electron Devices*, vol. 47, pp. 2-10, 2000.

- [5] Farid Medjdoub, Mohammed Zaknoune, Xavier Wallart, Christ Gaquiere, Francois Dessenne, Jean-Luc Thobel, and Didier Theron, "InP HEMT downscaling for power applications at W band," *IEEE Transactions on Electron Devics*, vol. 52, no.10, pp. 2136-2143, October 2005.

- [6] M. Schlechtweg et al., "Coplanar millimeter-wave IC's for W-band applications using 0.15 μm pseudomorphic MODFETs," *IEEE J Solid State Circuits*, vol. 31, pp. 1426-1434, Oct. 1996.

- [7] H.Wang et al., "An ultra low noise W-band monolithic three-stage amplifier using 0.1 μm pseudomorphic InGaAs/GaAs HEMT technology," *IEEE-MTT-S Tech. Dig.*, pp. 803-806, 1992.

- [8] Qi-Jun Zhang, K. C. Gupta, and Vijay K. Devabhaktuni,"Artificial Neural Networks for RF and Microwave Design-from theory to practice," *IEEE Transactions on Microwave Theory and Techniques*, vol. 51, no. 4, pp. 1339-1350, April 2003.

- [9] Q.J. Zhang and K.C. Gupta, "Neural networks for RF and microwave design", Artech House, Norwood, MA, 2000.

- [10] K.C. Gupta, "Emerging trends in millimeter-wave CAD, *IEEE Transactions on Microwave Theory and Techniques*, vol. 46, pp. 747-755, 1998.

- [11] Ruediger Quay, Karl Hess, Ralf Reuter, Michael Schlechtweg, Thomas Grave, Vassil Palankovski, and Siegfried Selberherr, "Nonlinear Electronic Transport and Device performance of HEMTs," *IEEE Transactions on Electron devices*, vol. 48, no. 2, Feb. 2001.

Anil Ahlawat was born in Muzaffar Nagar District of Uttar Pradesh, India, in 1975. He has received his M.Sc. degree in Physics (Electronics) from CCS University Meerut, Uttar Pradesh, India, in 1996; M.Phil in

Instrumentation from IIT Roorkee in 1998 and M.Tech in Computer Science and Engineering from Kurukshetra University, Haryana, India in 1999. He is presently working towards his Ph.D. degree from School of Engineering and Technology, GGS Indraprastha University, New Delhi, India. He is an Assistant Professor in Computer Science and Engineering Department of Amity School of Engineering and Technology, Delhi. His present research interests include device modeling and simulation of high electron mobility transistors and Artificial Neural Networks.

Manoj Kumar Pandey He received his M.Sc in Electronics from Kumaon University Nainital in 1994, and the Ph.D degree from Department of Electronics, University of Delhi South Campus in Microelectronics in 1999-

2000. He joined Semiconductor Devices Research Laboratory, University of Delhi in 1996 under the Project of Defense Research and Development Organization (DRDO), Ministry of Defense, Govt. of India. He joined N.C. Corporation Asia Pacific in 1999 and headed many scientific projects. He joined Department of Electronics and Communication Engineering, Institute of Technology and Management in 2002 as Associate Professor. He has 30 papers research published more than International/National Journals/Conferences. His current research interest includes SOI Device modeling and characterization, Noise and integrated circuit design. He has written two books in VLSI design and VLSI technology and one book on multimedia is in press. He is life member of ISTE, and member of IEEE society.

Sujata Pandey She received the Masters degree in electronics (VLSI) from Kurukshetra University in 1994 and the Ph.D degree from Department of Electronics, University of Delhi South Campus in Microelectronics in

1999. She joined Semiconductor Devices Research Laboratory, University of Delhi in 1996 under the Project of CSIR, Ministry of Science and Technology, Govt. of India. She joined Department of Electronics and Communication Engineering, Amity School of Engineering and Technology in 2002 as Assistant Professor. She has published more than 40 research papers in International/National Journals/ Conferences. Her current research interest includes modeling and characterization of HEMTs, SOI Devices and integrated circuit design. She is member of IEEE and Electron Device society.