# DC Characteristics of P-Channel Metal-Oxide-Semiconductor Field Effect Transistors with Si<sub>0.88</sub>Ge<sub>0.12</sub>(C) Heterostructure Channel

Sang Sik Choi\*, Hyun Duk Yang\*, Tae-Hyun Han\*\*, Deok-Ho Cho\*\*, Jea-Yeon Kim\*, and Kyu-Hwan Shim\*

Abstract—Electrical properties of Si<sub>0.88</sub>Ge<sub>0.12</sub>(C) p-MOSFETs have been exploited in an effort to investigate Si<sub>0.88</sub>Ge<sub>0.12</sub>(C) channel structures designed especially to suppress diffusion of dopants during and subsequent fabrication epitaxial growth processes. The incorporation of 0.1 percent of carbon in Si<sub>0.88</sub>Ge<sub>0.12</sub> channel layer could accomodate stress due to lattice mismatch and adjust bandgap energy slightly, but resulted in deteriorated current-voltage properties in a broad range of operation conditions with depressed gain, high subthreshold current level and many weak breakdown electric field in gateoxide. Si<sub>0.88</sub>Ge<sub>0.12</sub>(C) channel structures with boron delta-doping represented increased conductance and feasible use of modulation doped device of Si<sub>0.88</sub>Ge<sub>0.12</sub>(C) heterostructures.

Index Terms—SiGeC Epitaxy, MOSFET, RPCVD, DC characteristics

#### I. Introduction

High level integration density, high speed operation, and low level energy consumption have been accomplished via primarily scaling technology based on the reduction of device dimensions, in accordance with specific ways of circuit design and software controlled optimization [1-4]. SiGe heterostructures, after valuable

success in high performance semiconductors by virtue of advanced BiCMOS technology, expand their applications to CMOS regime focusing on radio frequency integrated circuits as well as sub-100 nm processors [5-9]. Coming years will render interest even more in SiGe heterostructures to CMOS embedded SoC for subsequent evolution of mobile communications.

In SiGe heterostures, using different energy bandgap of Si (1.12 eV) and Ge (0.66 eV), quantum well channels can be fabricated with two-to-eight folds high in carrier mobility compared to conventional silicon bulk channels. Moreover, many researchers reported SiGe devices could achieve much less noise level and expanded linearity in addition to fundamental merit of high speed operation. That is, high density integration and low cost for fabrication, and extremely stable reliability of electrical and thermal treatments provokes uncountable value of SiGe devices. Many previous works on SiGe MOSFETs suggested very promising advantages in terms of extreme enhancement in performance and 1/f noise level [10].

In case of admitting carbon in SiGe layer, the stress developed at the interface of SiGe and Si can be relaxed, and bandgap energy in SiGe(C)/Si heterostrues is to be precisely controlled by the amount of carbon incorporation. Since carbon is known to suppress the diffusion of boron in SiGe, a sharp delta doping of boron in SiGe channel may supply carriers and high performance devices [11, 12]. It is necessary to optimize epi structures for the development of new high performance SiGe MOSFETs [13]. Aggressive trial to adopt carbon in silicon-based devices must surpass technical barrier consisting of unknown problems with defects or segregation related interface states.

Manuscript received Apr. 12, 2006; revised Jun. 5, 2006.

<sup>\*</sup> Department of Semiconductor Science and Technology, Semiconductor Physics Research Center, Chonbuk National University, 664-14 Deokjindong, Deokjinku, Jeonju, 561-756 Korea

<sup>\*\*</sup> Tachyonics, 60-8 Gasandong, Kumchonku, Seoul, 153-801 Korea E-Mail: khshim@chonbuk.ac.kr

In this study, we have exploited Si<sub>0.88</sub>Ge<sub>0.12</sub>(C) MOSFET with 0.1 % of carbon and boron delta doping underneath Si<sub>0.88</sub>Ge<sub>0.12</sub>(C) channel as a first step to expand horizon of silicon-based heterostructure devices targeting high performance and progressive approach toward nano-scale generation. As observed from the first trial to employ carbon and boron doping in SiGe heterostructures, possible considerations and difficult issues regarding fabrication process could have been understood in the practical aspect.

#### II. EXPERIMENTS

In this experiments, Si<sub>0.88</sub>Ge<sub>0.12</sub>(C) p-MOSFET with 0.6 µm gate has been fabricated in a conventional CMOS process. Device isolation was formed by LOCOS and Si/Si<sub>0.88</sub>Ge<sub>0.12</sub>(C)/Si quantum-well channels were grown on Si(100) substrate using RPCVD (Reduced Pressure Chemical Vapor Deposition) using SiH<sub>4</sub>, GeH<sub>4</sub>, SiH<sub>3</sub>CH<sub>3</sub> as Si, Ge, and C source gases. The wafers were chemically ex situ cleaned and inserted into the N<sub>2</sub>

| SG                  | SGC       | SGBD      |

|---------------------|-----------|-----------|

| Si- cap             | Si- cap   | Si- cap   |

| SiGe.               | SIGe:C    | SIGE:C    |

| nuomosani-aanso-aan |           | o doping  |

| Si                  | Si        | Si        |

| Substrate           | Substrate | Substrate |

**Fig. 1.** Epitaxial structures of samples of SG (SiGe), SGC (SiGe:C) and SGBD (SiGe:C with  $\delta$ -doping).

Table 1. Typical process conditions for device fabrication.

| Process         | Process Condition                                                               |  |  |  |

|-----------------|---------------------------------------------------------------------------------|--|--|--|

| N-well          | P, 2.2x10 <sup>13</sup> cm <sup>-2</sup> @120keV, 1150°C, 8 hr anneal           |  |  |  |

| LOCOS           | 5500 Å                                                                          |  |  |  |

| Gate Oxide      | 70 Å                                                                            |  |  |  |

| Gate Poly       | In-situ P-doped Poly-Si (IDP), 3000 Å                                           |  |  |  |

| LDD             | BF <sub>2</sub> , 2.0x10 <sup>13</sup> cm <sup>-2</sup> @65keV                  |  |  |  |

| Sidewall spacer | 1000 Å                                                                          |  |  |  |

| p+ S/D          | BF <sub>2</sub> , 3.0x10 <sup>15</sup> /cm <sup>2</sup> @60keV, RTA @800°C, 30" |  |  |  |

| Polycide        | TiSi2 salicide on the gate, source and drain                                    |  |  |  |

| Dielectric      | UDO and BPSG, 7500 Å                                                            |  |  |  |

| Metallization   | Al-1%Si                                                                         |  |  |  |

**Table 2.** Summary of DC properties ( $L_g=0.6\mu m W_g=25\mu m$ ).

|      |                     |                 |                      | G <sub>m,max</sub> (mS)       |                             |

|------|---------------------|-----------------|----------------------|-------------------------------|-----------------------------|

|      | V <sub>th</sub> (V) | SS<br>(mV/dec.) | I <sub>off</sub> (A) | L(@<br>V <sub>DS</sub> =0.1V) | S(@<br>V <sub>DS</sub> =3V) |

| SG   | -1.1                | 80              | 2.1x10 <sup>-9</sup> | 0.26                          | 2.28                        |

| SGC  | -1.8                | 125             | 6.4x10 <sup>-7</sup> | 0.11                          | 1.66                        |

| SGBD | -1.5                | 165             | 1.3x10 <sup>-7</sup> | 0.14                          | 1.81                        |

purged CVD load-lock chamber. Right after placed on the substrate susceptor, an in situ cleaning was performed by baking the substrate at 100 °C for 1 to 5 min in hydrogen environment. SiGe(C) layers were grown with three typical structures described in the Table 1 at 650 °C and 30 torr.

Major process steps are summarized in the Table 2. For pMOS device, after forming n-well, Si/Si<sub>0.88</sub>Ge<sub>0.12</sub>(C) channel epi layer was grown. The thickness of gate oxide was 7 nm, where the in-situ doped poly silicon holds heavy amount of phosphorous above  $2x10^{20}$  cm<sup>-3</sup> in concentration. Source-drain area implanted with BF2 was annealed at 800 °C using a rapid thermal anneal (RTA) system in nitrogen gas environment. Self-aligned Ti/TiN was deposited to the thickness of 30/30 nm for each layers and silicidation of low sheet resistance of 3-5 ohm/sqr. could be performed via sequential process of annealing and etching in NH<sub>4</sub>OH chemicals. The Fig. 2(a) shows SEM photograph of a SiGe device taken after the metal layer defined, where the body contact could be identified along with other contact pands for source, drain and gate current flow schematic in Fig. 2(a) is discussed below.

Using secondary ion mass spectroscopy (SIMS) the atomic profile was analyzed in various epi structures of  $\mathrm{Si}_{0.88}\mathrm{Ge}_{0.12}$ ,  $\mathrm{Si}_{0.88}\mathrm{Ge}_{0.12}(\mathrm{C})$ , and delta-doped  $\mathrm{Si}_{0.88}\mathrm{Ge}_{0.12}(\mathrm{C})$ . The electrical properties including I-V and C-V were measured using a parameter analyzer of HP4155 assembled with a probe station of Cascade's SUMMIT11741B-6.

**Fig. 2.** (a) SEM pictures taken from SiGe:C p-MOSFETs, and (b) schematic view of current flow under MOS gate, where G, S, D, and B denote gate, source, drain and drain contacts.

los

D

# III. RESULTS AND DISCUSSION

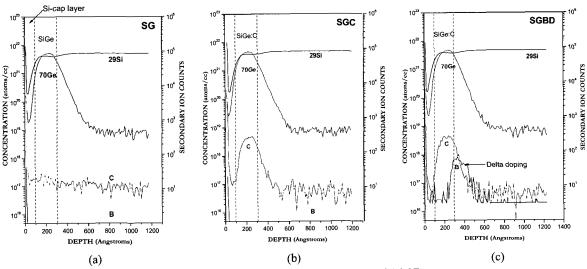

Fig. 3 shows depth profile of Ge, C, B atoms measured from the surface of samples of (a) SG, (b) SGC and (c) SGBD. Fig. 3(a) shows depth profile of Ge and detection limit of carbon concentration of SIMS system that we used for analysis. Figs. 3(b) and 3(c) represent quite normal distribution of Si, Ge, C concentrations as designed structure, but the boron profile reveals significant broadening. In fact, much of the broadening corresponds to artifacts of SIMS measurement with no additional calibration works.

It is necessary to note the sharp profile toward upside for boron concentration inside Si<sub>0.88</sub>Ge<sub>0.12</sub>(C) epi layer. Thermal process could have caused the dispersion of boron atoms in large part, and this problem needs further controlled thermal management in the future. In order to obtain more sharp delta-doped profile, dispersion phenomena will be prohibited through additional experiments to lower substrate temperature during epitaxial growth as well as subsequent process steps.

To evaluate gate oxides grown on Si/SiGe heterostructure, we have measured capacitance (C-V) and current flow as a function of gate voltage as shown in Figs. 4 and 5. Capacitance-voltage curve of MOS gate was measured at the frequency of 10 kHz with 10  $\mu$ m x 25  $\mu$ m gate-oxide MOS structure. The capacitance characteristics changing from accumulation to inversion implies that the SiGe MOS structure formed well for device applications. In Fig. 5, when bias is applied

Fig. 4. Capacitance-voltage curve of MOS gate measured at the frequency of 10 kHz (10  $\mu$ m x 25  $\mu$ m).

**Fig. 5.** Current-voltage curves of gate-to-source&drain (G-S) and gate-to-body (G-B) fro the samples with gate dioxide of 7 nm grown on SG, SGC, and SGBD devices. The gate oxide on silicon bulk is inserted for comparison and oxidation was performed at 700 °C in dry oxidation condition.

Fig. 3. SIMS depth profiles in SiGe channels structures measured from SG, SGC, and SGBD.

between gate and body contact, the electric field causing Fowler-Nordheim tunnel current begins at 6~8.5 MV/cm for SGBD, SGC, SG, and bulk-Si samples, and their corresponding breakdown fields are 10~10.9 MV/cm. When bias is applied between gate and source contact, the electric field causing tunnel current begins at 3~5.2 MV/cm for those and bulk-Si samples. The tunnel current of 7 nm SiO<sub>2</sub> on bulk-silicon implies that normal silicon dioxide films were grown, and their shifts in SiGe channel samples also exist in an appropriate regime.

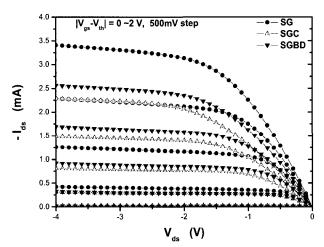

Fig. 6 represents  $I_D$  vs.  $V_D$  curves measured while varying gate bias  $|V_{GS}-V_{TH}|$  from 0 V to 2 V with intervals of 500 mV. In SG sample, the maximum drain current of 3.4 mA was obtained at  $V_{DS}=3$  V and  $|V_{GS}-V_{TH}|=2$  V. As seen in transconductance, SGC resulted in the

Fig. 6. I<sub>DS</sub>-V<sub>DS</sub> curves of SG, SGC, and SGBD devices.

smallest current level of 2.29 mA. On the contrary, SGBD sample shows 2.56 mA, which corresponds to 11 % increase in current level in comparison with SG sample. The degradation measured from SGC sample looks due to the presence of carbon atoms which would deteriorate gate-oxide interface or lower carrier transportation efficiency in channels correspondingly due to impurity scattering. According to current-voltage curves, the severe depression in the transconductance in the samples of SGC and SGBD were associated with the increased external resistance of source and drain. This degradation could be partially amended by the local-doping that supplies carriers in channel layers.

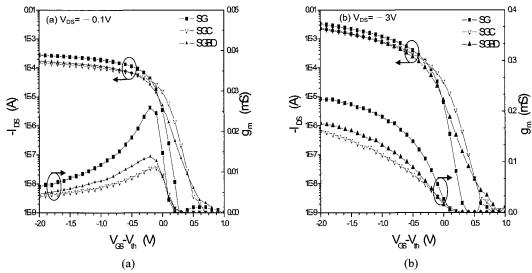

Figs. 7(a) and (b) represent transfer characteristics measured respectively in the linear ( $V_{DS}$ = -0.1 V) and saturation (V<sub>DS</sub>= -3.0 V) regimes, and their corresponding electrical properties are summarized in Table 2. Subthreshold slope (SS) measured from samples of SG, SGC, SGBD represents progressive increase as given 80, 125, 165 mV/dec. in those samples. The maximum transconductance, G<sub>m.max</sub>, was 0.23 mS in SG sample, which was higher than the other two samples. Meanwhile carbon doped SGC sample resulted in the lowest value of 0.17 mS. Small increase in transconductance of SGBD sample as given 0.18 mS compared to that of SGC. Nevertheless these imply that carbons not placed in appropriate sites of Si<sub>0.88</sub>Ge<sub>0.12</sub> channel might cause catastrophic degradation in several ways, as discussed below along with leakage, breakdown, and microscopic crystalline changes.

Fig. 7. Drain current and transconductance curves of SG, SGC and SGBD devices measured at (a) linear ( $V_{DS} = -0.1 \text{ V}$ ) and (b) saturation ( $V_{DS} = -3 \text{ V}$ ) conditions

Fig. 8. Body current of (a) SG, (b) SGC, and (c) SGBD devices, measured in operation conditions of  $V_{GS} = -1 \sim -3$  V with intervals of 500 mV, and the drain bias was scanned from 0 V to -9 V.

Meanwhile, the gate capacitance of MOS structure ( $C_G$ ) measured as a function of gate voltage( $V_{GS}$ ) is expressed as  $1/C_G(V_{GS}) = 1/C_{ox} + 1/C_D(V_{GS})$ , where  $C_{Ox}$  is the effective gate oxide capacitance, and  $C_D$  is assumed to be an ideal junction capacitance for simple calculation. Using this relationship and transconductance  $g_m = dI_{DS}/dV_{GS}$ , the drift mobility of carriers in Si/SiGe channel can be obtained as  $\mu(V_{GS}) = \frac{g_m(V_{GS}) \cdot L_g}{C_D(V_{GS}) \cdot V_{DS}}$ , where Lg and  $V_{DS}$  are the gate length and the drain voltage [14].

The depressed conductance in SGC and SGBD samples is likely due to carbon scattering impurities. although the highest carbon concentration is known to fully substitute lattice sites as high as ~1 at. % for the growth using CVD at 550 °C. We can adopt an appropriate expression between mobility and scattering centers, as found empirically found similarly scattering at interface states,  $\mu/\mu_o = 1/(1+k\cdot N_s)$ , where N<sub>s</sub> (cm<sup>-3</sup>) is the concentration of scattering centers, and k is a constant [15]. Additional precise work will be required to find k constant and the amount of scattering centers for various carbon embedded SiGe:C films.

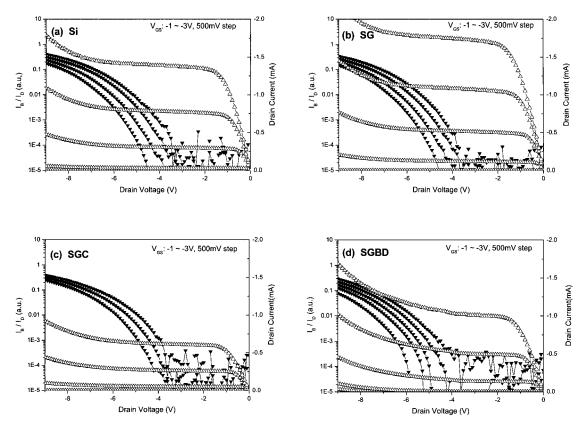

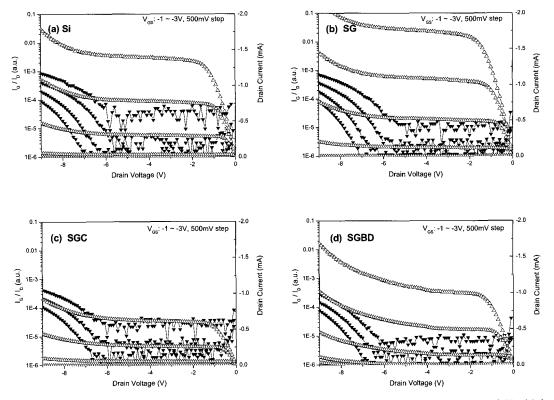

Fig. 8 displays current-voltage curves of gate dioxide

grown on the samples of SG, SGC, and SGBD samples with 70 Å thickness, where gate oxide on silicon bulk is inserted for comparison and oxidation was performed at 700 °C in dry oxidation condition. Figure 8 shows body current for (a) SG, (b) SGC, and (c) SGBD samples, which were measured under various bias conditions: V<sub>GS</sub> = -1~-3 V with 500 mV step, and  $V_{DS}$  = 0~-9 V. As the drain current increases, the body current becomes prominent through the impact ionization generating electron-hole-pairs (EHPs). The ratio of current, I<sub>B</sub>/I<sub>DS</sub> implies that the carriers in the channel of SGC sample generates large amount of electron-hole pairs (EHPs) through significant scattering of charged carriers. This degraded performance is believed primarily due to the presence of carbons placed improper positions in channel. The current flow of gate-to-body in Si and SG sample is observed almost same level, but substantial increase is recognized in both SGC and SGBD due to the carbon incorporation.

Fig. 9 shows gate current for the samples of (a) SG, (b) SGC, and (c) SGBD, which were measured in various bias operation conditions of  $V_{GS} = -1 \sim 3$  V with 500mv step, and  $V_{DS} = 0 \sim 9$  V. Unlike the body current,

Fig. 9. Gate current of (a) SG, (b) SGC, and (c) SGBD devices, measured in operation conditions of  $V_{GS}$ = -1~-3 V with intervals of 500mV, and the drain bias was scanned from 0 V to -9 V.

the gate leakage current looks more dependent on electrical properties of gate oxide than any contribution from EPHs generated in channels. Among gate leakage components as described in the Fig. 2(b), two possible contributions may come from electron tunneling: one is from gate to channel( $I_{LGS}$ ), and the other is the hole conduction from channel to gate  $I_{GC}$  and  $I_{LGD}$ . According to Fig. 7 and Fig. 8, and as notified in Fig. 5, most of excess carriers dissipate through body contact and the degree of current flow by excess carrier became dominant in carbon doped channel.

As discussed above, it is clear that the delta doping of boron could increase transconductance, however we also need to mention that carbon doping must be separated from carrier conduction and the spacer between channel and delta-doped layer should be adjusted properly. Also it is suggested that the delta-doping needs to be more sharp and narrow to reduce subthreshold current.

As explained above, three different shape of samples were fabricated to analyze the influence of carbon and boron playing a role of diffusion barrier and carrier supply in channels. Electrical properties obtained from SG presented the best properties with high transconductance

and straight forward device parameters. Si<sub>0.88</sub>Ge<sub>0.12</sub>(C) layers were known to be stable for remarkably high annealing temperature due to the presence of carbon retarding phase transformation and stress compensation [16]. Therefore controlled process is necessary to utilize feasible merits of additional considerations using carbon and boron in Si<sub>0.88</sub>Ge<sub>0.12</sub> channels. Carbon looks predominantly related to the depressed transport properties in Si<sub>0.88</sub>Ge<sub>0.12</sub> channel and the increase in transconductance by boron were limited in this experiment.

From experimental results, it is concluded that Si<sub>0.88</sub>Ge<sub>0.12</sub>(C) layer must be separated from channels being made of either silicon or SiGe is desirable, so a certain shape of silicon cap layer can be placed between channel and the delta-doped layer. In addition, it is likely that scales or three dimensional CMOS will try to adopt SiGe, SiGeC in daca-nao technology generations. Problems associated with auto-doping and out-diffusion, additional process steps are necessary during epitaxial growth and subsequent fabrication process.

## IV. CONCLUSIONS

Si<sub>0.88</sub>Ge<sub>0.12</sub>(C)/Si heterostructure channels grown by RPCVD were employed to p-type MOSFETs, and their electrical properties were analyzed using I-V and C-V measurements. In a wide range of scope, samples with carbon and boron presented favorable breakdown voltage and leakage levels as compared to conventional Si device. The incorporation of carbon resulted in a shift of threshold voltage -0.7 V, and even significantly decreased transconductance. The delta doping of boron could have increased the transconductance by 11 % in the device using Si<sub>0.88</sub>Ge<sub>0.12</sub>(C) channel but not sufficient to recover up to that of Si<sub>0.88</sub>Ge<sub>0.12</sub> channel device. It is suggested that low temperature epitaxial growth and subsequent thermal process need to unfavorable phenomena associated with dispersed profile of carbon and boron in channels.

#### **ACKNOWLEDGMENTS**

This work was supported by the Korea Research Foundation Grant(KRF-2005-005-J07502) funded by the Korean Government (MOEHRD).

## REFERENCES

- [1] J. D. Plummer and P. B. Griffin, "Material and process limits in silicon VLSI technology," *Proceedings of the IEEE*, Vol.89, issue 3, pp.240-258, March 2001.

- [2] T. Ohmi, S. Sugawa, K. Kotani, M. Hirayama and A. Morimoto, "New paradigm of silicon technology," *Proceedings of the IEEE*, Vol.89, issue 3, pp.394-412, March 2001.

- [3] T. Sugii, "High-performance bulk CMOS technology for 65/45 nm nodes," *Solid-State Electronics*, Vol.50, issue 1, pp.2-9, January 2006.

- [4] D. K. Schroder and J. A. Babcock, "Negative bias temperature instability: Road to cross in deep submicron silicon semiconductor manufacturing," *Journal of Applied Physics*, Vol.94, pp.1-18, July 2003.

- [5] K. H. Shim, Y. J. Song and J. Y. Kang, "High-Performance SiGe pHMOS usin reduced-pressure CVD," Solid State Technology, pp.51-58, March 2004.

- [6] S. H. Olsen, K. S. K. Kwa, S. Chattopadhyay and A. G. ONeill, "Design, fabrication and characterisation of strained Si/SiGe MOS transistors," *IEE Proceedings Circuits, Devices & System*, Vol.151, issue 5, pp.431-437, October 2004.

- [7] T. Mizuno, N. Sugiyama, T. Tezuka, Y. Moriyama, S. Nakaharai and S. Takagi, "High-speed sourceheterojunction-MOS-transistor (SHOT) utilizing high-velocity electron injection," *IEEE Transactions* on *Electron Devices*, Vol 52, issue 12, pp.2690-2696, December 2005.

- [8] H. C. Lee, G. Y. Yeom, Y. J. Lee, J. K. Shim, S. I. Baik and Y. W. Kim, "Structural and Electrical Analysis of Silicon Thin Films Deposited by Transformer-Coupled-Plasma Chemical-Vapor Deposition," *Journal of the Korean Physical Society*, Vol 47, issue 2, pp.277-282, August 2005.

- [9] S. Watanabe, "Multi-Lorentzian Model and 1/f noise spectra," *Journal of the Korean Physical Society*, Vol.46, issue 3, pp.646-650, March 2005.

- [10] Y. J. Song, J. W. Lim, B. Mheen, S. H. Kim, H. C. Bae, J. Y. Kang, J. H. Kim, J. I. Song, K. W. Park and K. H. Shim, "1/f noise in Si/sub 0.8/Ge/sub 0.2/ pMOSFETs under Fowler-Nordheim stress," *IEEE Transactions on Electron Devices*, Vol.50, issue 4, pp.1152-1156, April 2003.

- [11] E. J. Quinones, S. John, S. K. Ray and S. K. Banerjee, "Design, fabrication, and analysis of SiGeC heterojunction PMOSFETs," *IEEE Transactions on Electron Devices*, Vol.47, issue 9, pp.1715-1725, September 2000.

- [12] Y. J. Song, S. H. Kim, N. E. Lee, J. Y. Kang, J. I. Song and K. H. Shim, "A low-temperature and high-quality radical-assisted oxidation process utilizing a remote ultraviolet ozone source for high-performance SiGe/Si MOSFETs," *Semiconductor Science and Technology*, Vol.19, issue 7, pp.792-797, July 2004.

- [13] S. Ariyoshi, S. Takeuchi, O. Nakatsuka, A. Sakai, S. Zaima and Y. Yasuda, "Influence of Si<sub>1-x</sub> Ge<sub>x</sub> interlayer on the initial growth of SiGeC on Si(1 0 0)," *Applied Surface Science*, Vol.224, pp.117-121,

March 2004.

- [14] R. A. Pucel and C. F. Krumm, "Simple method of measuring drift mobility in thin semiconductor films," *Electronics Letters*, Vol.12, issue 10, pp.240-242, May 1976.

- [15] S. C. Sun and J. D. Plummer, "Electron mobility in inversion and accumulation layers on thermally oxidized silicon surfaces," *IEEE Trans. Electron Devices*, Vol.27, issue 8, pp.1497-1508, August 1999.

- [16] J. Hallstedt, M. Blomqvist, P. O. A. Persson, L. Hultman, and H. H. Radamson, "The effect of carbon and germanium on phase transformation of nickel on Si<sub>1-x-y</sub>Ge<sub>x</sub>C<sub>y</sub> epitaxial layers," *Journal of Applied Physics*, Vol.95, issue 5, pp.2397-2402, March 2002.

Sang Sik Choi received the B.S. degree in the department of physics form Chonbuk National University, Jeonju, Korea, in 2005. He currently pursuing a M.S. degree in the department of semiconductor science

and technology at same university. His current research interests include the simulation, fabrication and charac terization of SiGe MOSFET and HBT

Hyun Duk Yang recived the B.S. degree in the department of physics from Chonbuk National University, Jeonju, Korea, in 2002 and the M.S. degree in the department of semicon ductor science and technology at same

university, in 2004, where he is currently pursuing the Ph.D. degree. His current research interests include the simulation, fabrication and characterization of SiGe MOSFET and HBT.

**Kyu-Hwan Shim** received his B.S. and M.S. degrees in 1984 and 1986, respectively, in materials science and engineering from Korea University, and his PhD degree in 1997 from the University of Illinois at Urbana-Champaign (UIUC). Meanwhile, he

joined Electronics and Telecommunications Research Institute (ETRI) in 1986, where his major activities were focused on compound semiconductor processes and devices, GaAs MESFETs until 1992. Thanks to ETRI's program, he could study at UIUC (1992-1997) to specialize in GaN-based heterostructures utilizing plasma-assisted molecular beam epitaxy technology. For the past nine years, his efforts have been devoted to SiGe HBTs, BiCMOS integrated circuits, and strained silicon heterostructure MOSFETs (SS-HMOS) evolving into the sub-100 nm generation. At present, he is a professor at Chonbuk National University, and devotes on R&Ds in his research group, Intelligent Semiconductor Research Laboratory.