**JPE 6-2-3**

# Comparison of FPGA-based Direct Torque Controllers for Permanent Magnet Synchronous Motors

Yoshiharu Utsumi\*, Nobukazu Hoshi†\*\* and Kuniomi Oguchi\*\*

\*LSI Module Business Promotion Department, NEC Access Technica, Ltd., Japan

## **ABSTRACT**

This paper compares two types of direct torque controllers for permanent magnet synchronous motors(PMSMs). These controllers both use a single-chip FPGA(Field Programmable Gate Array) but have differing hardware configurations. One of the controllers was constructed by programming a soft-core CPU and hardware logic circuits written in VHDL(Very high speed IC Hardware Description Language), while the other was constructed of only hardware logic circuits.

The characteristics of these two controllers were compared in this paper. The results show the controller constructed of only hardware logic circuits was able to shorten the control period and it was able to suppress the low torque ripple.

Keywords: Permanent Magnet Synchronous Motor, Field Programmable Gate Array, Direct Torque Control

#### 1. Introduction

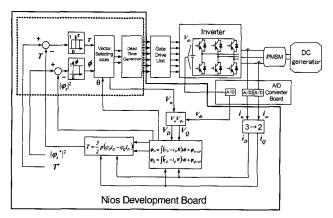

Direct torque control (DTC) was proposed by Takahashi for induction machines in the mid-1980s<sup>[1]</sup>. DTC is an applicable control scheme for all AC motors<sup>[2]</sup>. In recent years, a significant body of research on DTC has been performed all over the world<sup>[3-8]</sup>. Fig. 1 shows a block diagram of DTC. As shown in this figure, the controller configuration for DTC is simpler than that of conventional current control based vector controls, since the coordinate transformation from a stationary reference frame to a synchronously rotating reference frame or the inverse transformation is not required in DTC. On the

other hand, torque- and flux-ripples grow larger when the control period is longer. In order to reduce those ripples, many schemes have been proposed<sup>[9-13]</sup>. Obviously, the ripples can be reduced by shortening the control period. The authors described a PMSM (Permanent Magnet Synchronous Motor) controller using an FPGA (Field Programmable Gate Array) in which the control period of the DTC can be advantageously shortened in an easy control scheme using logic circuits<sup>[15]</sup>. The controller was constructed by programming hardware logic circuits written in VHDL (Very high speed IC Hardware Description Language) and a soft-core CPU onto a FPGA. This controller is called "*Type A controller*" in this paper.

In recent years, the progress of FPGA-related technologies has been remarkable. Under current conditions, large-scale FPGAs decreases in price year by year, and can be obtained easily. In this paper, a direct torque controller is newly constructed of only hardware

<sup>\*\*</sup>Department of Electrical and Electronic Engineering, Ibaraki University, Japan

Manuscript received January 27, 2005; revised Feb. 2, 2006

<sup>&</sup>lt;sup>†</sup>Corresponding Author: hoshi@ieee.org

Tel: +81-294-38-5095, Fax: +81-294-38-5275, Ibaraki Univ.

<sup>\*</sup>NEC Access Technica, Ltd

<sup>\*\*</sup>Ibaraki University

Fig. 1 Block diagram of DTC for PMSM

and called "*Type B controller*". In order to compare the control characteristics of *Type A* and *Type B controllers*, an IPMSM(Interior PMSM) was driven with each controller.

#### 2. Principle of Direct Torque Control

In DTC, torque T, stator flux-linkage amplitude  $|\varphi_s|$  and stator flux-linkage position  $\theta_n$  are estimated from stator currents  $i_u$ ,  $i_w$  and voltage-vector  $V_n$  is determined by the conduction state of the inverter switching devices shown in Fig. 1. Torque T and stator flux-linkage amplitude  $|\varphi_s|$  are compared with each reference value by hysteresis comparators. The voltage-vector is selected by using these comparator outputs  $\tau$ ,  $\phi$  and the stator flux-linkage position  $\theta_n$  according to Table 1. Torque T, stator flux-linkage amplitude  $|\varphi_s|$  and stator flux-linkage position  $\theta_n$  is obtained as follows. The instantaneous values of the direct- and quadrature-axis on a stationary reference frame were used in the following calculations; and the values are expressed by subscript D and Q, respectively. In DTC,  $i_n$  and  $i_w$  are converted into  $i_D$  and  $i_Q$  by

$$i_D = i_u \tag{1}$$

$$i_{Q} = -\frac{1}{\sqrt{3}} (i_{u} + 2i_{w}). \tag{2}$$

Moreover,  $V_D$  and  $V_Q$  are calculated by the following equations using the inverter DC-link voltage  $V_{dc}$  and coefficients  $k_D$ ,  $k_Q$ . The coefficients are related to the output voltage-vector  $V_n$  and are shown in Table 2.

Table 1 Inverter output voltage-vector selecting table for DTC

| φ   | τ   | $	heta_n \left( D_2 D_1 D_0  ight)$ |                      |                      |                      |                      |                      |

|-----|-----|-------------------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

|     |     | $\theta_1(001)$                     | $\theta_{2}(010)$    | θ <sub>3</sub> (011) | $\theta_4(100)$      | θ <sub>5</sub> (101) | θ <sub>6</sub> (110) |

| φ=1 | τ=I | V <sub>2</sub> (110)                | V <sub>3</sub> (010) | V <sub>4</sub> (011) | V <sub>5</sub> (001) | V <sub>6</sub> (101) | V <sub>1</sub> (100) |

|     | τ=0 | V <sub>6</sub> (101)                | V <sub>1</sub> (100) | V <sub>2</sub> (110) | V <sub>3</sub> (010) | V <sub>4</sub> (011) | V <sub>5</sub> (001) |

| φ=0 | τ=1 | V <sub>3</sub> (010)                | V <sub>4</sub> (011) | V <sub>5</sub> (001) | V <sub>6</sub> (101) | V <sub>1</sub> (100) | V <sub>2</sub> (110) |

|     | τ=0 | V <sub>5</sub> (001)                | V <sub>6</sub> (101) | V <sub>1</sub> (100) | V <sub>2</sub> (110) | V <sub>3</sub> (010) | V <sub>4</sub> (011) |

Table 2 The coefficients for determining D-Q axis voltage

| $\overline{V}_n$ | $k_D$        | $k_{Q}$                         |

|------------------|--------------|---------------------------------|

| $V_1$            | $k_D = 1$    | $k_Q = 0$                       |

| $V_2$            | $k_D = 1/2$  | $k_{Q} = \sqrt{3}/2$            |

| $V_3$            | $k_D = -1/2$ | $k_Q = \sqrt{3}/2$              |

| $V_{_4}$         | $k_D = 1$    | $k_{Q} = 0$                     |

| $V_{5}$          | $k_D = -1/2$ | $k_{\mathcal{Q}} = -\sqrt{3}/2$ |

| $V_6$            | $k_D = 1/2$  | $k_{Q} = -\sqrt{3}/2$           |

$$V_D = \frac{2}{3} k_D V_{dc} \tag{3}$$

$$V_{\mathcal{Q}} = \frac{2}{3} k_{\mathcal{Q}} V_{dc} \tag{4}$$

From  $i_u$ ,  $i_w$ ,  $V_D$  and  $V_Q$  obtained by the above calculations, stator flux-linkage  $\varphi_D$ ,  $\varphi_Q$  are estimated by (5) and (6).

$$\varphi_D = \int (V_D - Ri_D) dt + \varphi_{D|t=0}$$

(5)

$$\varphi_{Q} = \int (V_{Q} - Ri_{Q}) dt + \varphi_{Q|_{t=0}}$$

(6)

From  $\varphi_D$ ,  $\varphi_Q$ ,  $i_u$  and  $i_w$ , the square of the estimated stator flux-linkage  $|\varphi_s|^2$  and estimated torque T are calculated by the following equations:

$$\left|\varphi_{s}\right|^{2} = \varphi_{D}^{2} + \varphi_{Q}^{2} \tag{7}$$

$$T = \frac{2}{3} p(\varphi_D i_Q - \varphi_Q i_D), \qquad (8)$$

where p is the number of pole-pairs. In addition, stator flux-linkage position  $\theta_n$  is obtained from  $\varphi_D$  and  $\varphi_O$ .

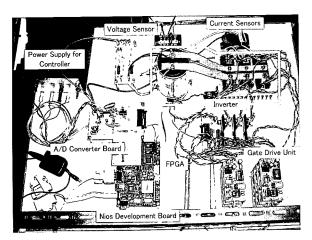

Fig. 2 Photo of the constructed control system

# 3. Controller Configurations

The control system in this paper was constructed by connecting a gate drive unit and an A/D converter board that acquires the information from current and voltage sensors, to an *Altera Nios Development board, Stratix Edition*<sup>[16]</sup>. In the A/D converter board, three A/D converters with serial transmission(*National Semiconductor ADC10731*<sup>[17]</sup>) were used for the acquisition of the measurement data  $i_u$ ,  $i_w$  and  $V_{dc}$  from current sensors and a voltage sensor.

The appearance of the constructed control system is shown in Fig. 2. Two types of controllers in this paper shared this system in Fig. 2, because these are realizable only by changing the hardware logic circuits' structure programmed on the FPGA. The performance and the resource utilization of the two controllers(*Type A controller* and *Type B controller*) were compared using this system.

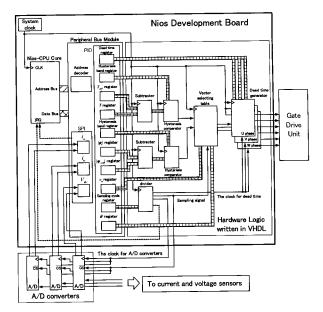

#### 3.1 Type A controller

A functional block diagram of the *Type A controller* is shown in Fig. 3. The *Type A controller* was constructed by programming hardware logic circuits written in VHDL and a soft-core CPU. Two hysteresis comparators, an inverter output voltage-vector selecting table, dead time generators, and subtracters for reference values and estimated values were implemented by hardware logic circuits (the part surrounded by the dotted line in Fig. 1). On the other hand, the following functions are executed on the CPU.

Fig. 3 Functional block diagram of Type A controller

- Initializing of the hardware logic circuits written in VHDL (setting bandwidth for the hysteresis comparators, control period and dead time),

- Conversion to parallel data from serial data that are from A/D converters,

- Calculation of torque T, the square of stator flux-linkage amplitude  $|\varphi_s|^2$  and stator flux-linkage position  $\theta_n$  from current values  $i_u$ ,  $i_w$  and inverter output voltage-vector  $V_n$ ,

- Output of the calculation results to the hardware logic circuits.

In order to shorten the arithmetic processing cost, 16 bits fixed-point arithmetic was carried out in most parts of the above calculations, and 32 bits fixed-point arithmetic was carried out only at integral computation parts which required high accuracy. In addition, estimated flux-linkage  $|\varphi_s|$  was compared with reference  $|\varphi_s^*|$  at the square value because it reduced the arithmetic processing time. The processing time of the *Type A controller* for the DTC is 50 $\mu$ s.

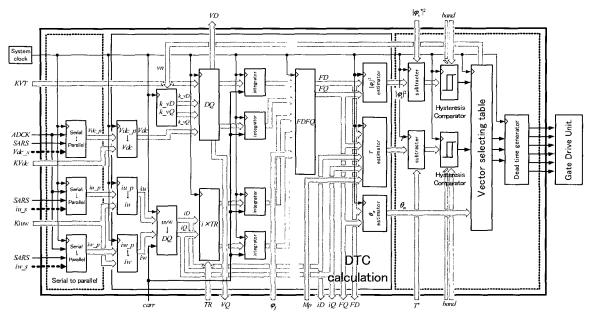

# 3.2 Type B controller

In this controller, the following functions which were realized by software in the *Type A controller* were changed to hardware implementation.

Conversion to parallel data from serial data that were from the A/D converters,

Fig. 4 Functional block diagram of Type B controller

#### • All the calculations for the DTC,

A functional block diagram of the *Type B controller* is shown in Fig. 4. In addition, an explanation of the signals in Fig. 4 is shown in Table 3. As in the *Type A controller*, 32 bits fixed-point arithmetic was carried out only at integral computation parts; and 16 bits fixed-point arithmetic was carried out in the rest of the calculations. Also, a parallel operation was carried out to reduce the arithmetic processing time as shown in Fig. 4.

The CPU performed the following functions:

- initializing of the hardware logic circuits described in VHDL,

- data acquisition of the operation results  $(V_D, V_Q, i_D, i_Q, \varphi_D, \varphi_Q, |\varphi_s|^2, T, \theta_n)$  for verification in the experiments.

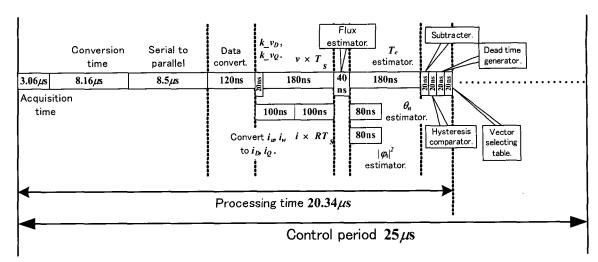

The time-line diagram of the *Type B controller* is shown in Fig. 5. The processing time of the *Type B controller* is 20.34µs as shown in Fig. 5. However, most of this time is occupied by acquisition, analog-to-digital conversion and serial-to-parallel conversion. These depend on the performance of the A/D converters; the calculation of the DTC hardly requires time. Therefore, when the A/D converters used in this paper are changed to high-speed A/D converters, a shorter control period is expected.

Table 3 Explanation of the signals in Fig. 4

| ADCK                | Clock for A/D converters.                              |  |  |

|---------------------|--------------------------------------------------------|--|--|

| SARS                | Successive approximation register status of            |  |  |

| SAKS                | A/D converter.                                         |  |  |

| Vdc s               | Serial data of A/D conversion result of dc link        |  |  |

|                     | voltage.                                               |  |  |

| iu_s, iw_s          | Serial data of A/D conversion result of <i>u</i> - and |  |  |

|                     | w-phase stator current.                                |  |  |

| KVT                 | $2/3 \times T_s$ ( $T_s$ : Sampling period.)           |  |  |

| vn                  | Voltage vector selected by inverter output             |  |  |

|                     | voltage-vector selecting table.                        |  |  |

| KVdc, Kiuw          | Conversion coefficients for A/D converter.             |  |  |

| carr                | Synchronization signal for latch circuits.             |  |  |

| TR                  | $T_s \times R$ (R: Stator resistance.)                 |  |  |

| $arphi_f$           | Magnet flux-linkage.                                   |  |  |

| Мр                  | $3/2 \times p$ (p: Number of pole-pairs.)              |  |  |

| VD, VQ              | Voltages on the D-Q coordinate.                        |  |  |

| iD, iQ              | Stator currents on the D-Q coordinate.                 |  |  |

| FD, FQ              | Flux-linkages on the D-Q coordinate.                   |  |  |

| $ \varphi_{s} ^{2}$ | Square of estimated stator flux-linkage.               |  |  |

| T                   | Estimated torque.                                      |  |  |

| $\theta_n$          | Estimated stator flux-linkage position.                |  |  |

| $ \varphi_s^* ^2$   | Square of reference stator flux-linkage.               |  |  |

| $T^*$               | Reference torque.                                      |  |  |

| band                | Hysteresis band.                                       |  |  |

Fig. 5 Time-line diagram of Type B controller

# 4. Characteristics comparison of two controllers

Tables 4 and 5 are the FPGA resource utilization for the *Type A* and *Type B controllers*, respectively. By changing the controller configuration, the rate of total logic elements increased from 35% to 53%.

In order to compare the control characteristics of *Type A* and *Type B controllers*, IPMSM was driven with each controller. The motor parameters of the IPMSM used for the experiments are shown in Table 6. Torque reference  $T^*$ , flux-linkage reference  $|\varphi_s^*|$  and inverter DC-link voltage  $V_{dc}$  were set up as 8N-m, 0.289035Wb and 100V, respectively. Besides, the base clock of both systems is 50MHz.

Table 4 FPGA resource utilization of Type A controller

| Total logic elements     | 3,737 / 10,570 (35%)  |  |  |

|--------------------------|-----------------------|--|--|

| Total pins               | 123 / 426 (28%)       |  |  |

| Total memory bits        | 34,688 / 920,448 (3%) |  |  |

| DSP block 9-bit elements | 2 / 48 (4%)           |  |  |

| total PLLs               | 0 / 6 (0%)            |  |  |

| Total DLLs               | 0 / 2 (0%)            |  |  |

Table 5 FPGA resource utilization of Type B controller

| Total logic elements     | 5,622 / 10,570 (53%)  |  |  |

|--------------------------|-----------------------|--|--|

| Total pins               | 123 / 426 (28%)       |  |  |

| Total memory bits        | 34,688 / 920,448 (3%) |  |  |

| DSP block 9-bit elements | 30 / 48 (62%)         |  |  |

| total PLLs               | 0 / 6 (0%)            |  |  |

| Total DLLs               | 0 / 2 (0%)            |  |  |

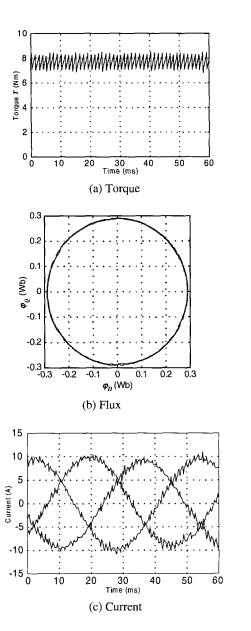

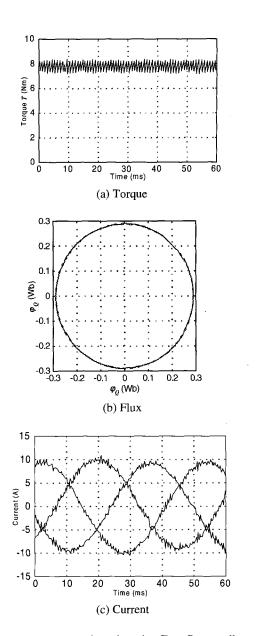

Figs. 6 and 7 show the experimental results for the *Type A* and *Type B controllers*, respectively. The minimum control period of the *Type A controller* is  $50\mu$ s. On the other hand, the period of the *Type B controller* could be  $25\mu$ s (Processing time was  $20.34\mu$ s; however the control period was set as  $25\mu$ s because of the limitations of the gate drive unit.). As a result, the torque ripple width of the *Type A controller* is 1.2N-m, and that of the *Type B controller* is 0.8N-m.

Table 6 Motor parameters

| Rated speed          | $\overline{N_R}$ | 1800 [rpm]   |

|----------------------|------------------|--------------|

| Number of pole-pairs | p                | 2            |

| Stator resistance    | R                | 0.5919 [Ω]   |

| d axis inductance    | $L_d$            | 10.54 [mH]   |

| q axis inductance    | $L_q$            | 26.56 [mH]   |

| Magnet flux-linkage  | $\varphi_f$      | 0.19129 [Wb] |

|                      |                  |              |

#### 5. Conclusions

If all control functions are constructed from only hardware, processing time can be decreased; on the other hand, the number of logic elements increases. By changing the controller configuration from the *Type A controller* to the *Type B controller*, processing time is decreased from 50 µs to 20.34 µs. On the other hand, the rate of total logic elements increased from 35% to 53%. Since large-scale FPGAs can be obtained at low-cost in recent years; it is therefore possible to construct a

Fig. 6 Experimental results using *Type A controller* at  $T_s$ =50 $\mu$ s.

controller by using only hardware. A hardware configured controller using an FPGA is effective in the reduction of torque- and flux-ripples.

## **Acknowledgement**

This research was supported financially in part by Grant-in-Aid for Encouragement of Young Scientists of the Ministry of Education, Culture, Sports, Science and Technology in Japan.

Fig. 7 Experimental results using *Type B controller* at  $T_s$ =25 $\mu$ s.

#### References

- [1] I. Takahashi and T. Noguchi: "Quick response torque control of as Induction motor by using instantaneous slip frequency control", *Transactions on IEE Japan*, 106–B, 1, pp. 9–16, (1986) (in Japanese).

- [2] I. Takahashi: "Direct torque control for all ac motor", 1999 National Convention Record I.E.E Japan, vol. 4, p. 424, (1999) (in Japanese).

- [3] Hao Yun Zhong, Henry P. Messinger and Muhammad H. Rashad: "A new microcomputer-based direct torque control system for three-phase induction motor", *IEEE*

- Transactions on Industry Applications, Vol. 27, No. 2, pp. 294-298, (1991).

- [4] Thomas G. Habetler, Francesco Profumo, Michele Pastorelli and Leon M. Tolbert: "Direct torque control of induction machines using space vector modulation", *IEEE Transactions on Industry Applications*, Vol. 28, No. 5, pp. 1045-1053, (1992).

- [5] L. Zhong, M. F. Rahman, W. Y. Hu, and K. W. Lim: "Analysis of Direct Torque Control in Permanent Magnet Synchronous Motor Drives", *IEEE Transactions on Power Electronics*, Vol. 12, No. 3, pp. 528-536, (1997).

- [6] M. R. Zolghadri, D. Diallo, D. Roye: "Direct Torque Control System for Synchronous Machine", Proc. on 7th European Conference on Power Electronics and Applications EPE'97, Trondheim, pp.3.694-3.699, (1997).

- [7] F. Aubépart, P. Poure, C. Girerd, Y. A. Chapuis and F. Braun: "Design and simulation of ASIC-based system control: Application to Direct Torque Control of Induction Machine", Proc. on 1999 IEEE International Symposium on Industrial Electronics, Vol. 3, pp. 1250–1255, (1999).

- [8] G. S. Buja and M. P. Kazmierkowski: "Direct Torque Control of PWM Inverter-Fed AC Motors-A Survey", *IEEE Transactions on Industrial Electronics*, vol. 51, No. 4, pp. 744-757, (2004).

- [9] K. B. Lee, J. H. Song, I. Choy and J. Y. Yoo: "Torque ripple reduction in DTC of induction motor driven by three-level inverter with low switching frequency", *IEEE Transactions on Power Electronics*, vol. 17, No. 2, pp. 255–264, (2002).

- [10] J. K. Kang and S. K. Sul: "New direct torque control of induction motor for minimum torque ripple and constant switching frequency", *IEEE Transactions on Industry Applications*, vol. 35, No. 5, pp. 1076–1082, (1999).

- [11] Arias Pujol, Antoni: "Improvements in direct torque control of induction motors", Doctoral thesis, Technical University of Catalonia, pp. 60–62, (2001).

- [12] C. A. Martins, X. Roboam, T. A. Meynard and A. S. Carvalho: "Switching Frequency Imposition and Ripple Reduction in DTC Drives by Using a Multilevel converter", *Proc on 2002 IEEE Transactions on Power Electronics*, vol. 17, No. 2, pp. 286–297, (2002).

- [13] L. Tang, L. Zhong, M. F. Rahman and Y. Hu: "A Novel Direct Torque Control for Interior Permanent Synchronous Machine Drive With Low Ripple in Torque and Flux – A Speed-Sensorless Approach", *IEEE Transactions on Industry* Applications, VOL39, No. 6, pp.1748–1756, (2003).

- [14] L. Romeral, A. Arias, E. Aldabas and M. G. Jayne: "Novel direct torque control (DTC) scheme with fuzzy adaptive torque-ripple reduction", *IEEE Transactions on Industrial Electronics*, vol. 50, No. 3, pp. 487-492, (2003).

- [15] N. Hoshi, Y. Utsumi and K. Oguchi: "Rapid Prototyping of a Direct Torque Controller for Permanent Magnet Synchronous Motors using Complex Programmable Logic Device with Soft-CPU Core", 2003 National Convention Record I.E.E. JAPAN, Vol. 4, p. 234, (2003) (in Japanese).

- [16] Altera Corporation, Nios Embedded Processor Development Board Data Sheet, (2002).

- [17] ADC10731/ADC10732/ADC10734/ADC10738, National Semiconductor, (1995).

Yoshiharu Utsumi: he received the B. S. and M.S. degrees in Electrical Engineering from Ibaraki University, Ibaraki, Japan in 2003 and 2005, respectively. He joined LSI Module Business Promotion Department, NEC Access Technica, Ltd, Japan in April,

2005. His research interests are motor control and logic circuits design. Mr. Utsumi is a member of the Institute of Electrical Engineers of Japan.

Nobukazu Hoshi: he received the B.S., M.S., and Ph.D. degrees in Electrical Engineering from Yokohama National University, Yokohama, Japan, in 1992, 1994, and 1997, respectively. He joined the Department of Electrical and Electronic Engineering,

Ibaraki University, Hitachi, Japan as a research associate in 1997. Since 2005, he has been an assistant professor. He was a Research Fellow of the Japan Society for the promotion of Science from 1994 to 1997. His research interests are power electronics, ultrasonic actuators, and electric vehicles. Dr. Hoshi is a senior member of the Institute of Electrical Engineers of Japan, a member of the Japan Institute of Power Electronics, and a member of IEEE. He was a co-recipient of the 1998 Committee Prize Paper Awards of the Industrial Power Converter Committee of the IEEE Industry Applications Society, and a recipient of the 2000 Conference Paper Awards of IEE of Japan.

Kuniomi Oguchi: he received the B. E. and Dr. Engineering degrees in Electrical Engineering from Kyusyu University, Fukuoka, Japan in 1963 and 1977, respectively. He is currently a Professor in the Department of Electrical and Electronic

Engineering, Ibaraki University, Hitachi, Japan. His research interests include high-power converter topologies and control, soft-switching converters, and motor drives. Prof. Oguchi is a member of the Institute of Electrical Engineers of Japan, a senior member of IEEE, and was co-recipient of the 1983, 1993, 1997, and 1998 Committee Prize Paper Award from the Industrial Power Converter Committee of the IEEE Industry Applications Society.