**JPE 6-1-10**

# A New High Efficiency and Low Profile On-Board DC/DC Converter for Digital Car Audio Amplifiers

Chong-Eun Kim\*, Sang-Kyoo Han\*\* and Gun-Woo Moon†

<sup>\*\*</sup>Dept. of Electrical Engineering, KAIST, Daejeon, Korea \*\*School of Electrical Engineering, Kookmin University, Korea

#### **ABSTRACT**

A new high efficiency and low profile on-board DC/DC converter for digital car audio amplifiers is proposed. The proposed converter shows low conduction loss due to the low voltage stress of the secondary diodes, a lack of DC magnetizing current for the transformer, and a lack of stored energy in the transformer. Moreover, since the primary MOSFETs are turned-on under zero-voltage-switching (ZVS) conditions and the secondary diodes are turned-off under zero-current-switching (ZCS) conditions, the proposed converter has minimized switching losses. In addition, the input filter can be minimized due to a continuous input current, and an output inductor is absent in the proposed converter. Therefore, the proposed converter has the desired features, high efficiency and low profile, for a viable power supply for digital car audio amplifiers. A 60W industrial sample of the proposed converter has been implemented for digital car audio amplifiers with a measured efficiency of 88.3% at nominal input voltage.

Keywords: digital car audio amplifier, DC/DC converter, zero-voltage-switching, zero-current-switching

## 1. Introduction

Generally, analog audio amplifiers have excellent distortion characteristics, but show considerably low efficiency and require bulky heat sinks for cooling. On the other hand, digital audio amplifiers have high efficiency and a compact size, but relatively poor fidelity. Nowadays, since new technologies for digital audio amplifiers have been developed and their fidelity characteristics have been improved, as reported in [1-3], they are being applied to compact car audio systems. Therefore, a high efficiency

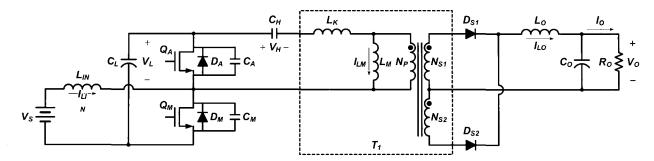

and low profile on-board DC/DC converter is required for digital car audio amplifiers. Among previously proposed DC/DC converters, the boost integrated half bridge (BHB) converter shown in Fig. 1 is suitable for low voltage battery input applications, because the converter has a continuous input current, I<sub>LIN</sub>, and a boosted link voltage, V<sub>L</sub>. In addition, the primary MOSFETs are turned-on under zero-voltage-switching (ZVS) conditions<sup>[4-5]</sup>. However, the main disadvantages of the BHB converter are the high DC magnetizing current of the transformer, high voltage stress and large turn-off voltage oscillation of the secondary rectifier diodes, increased magnetic components count, and considerable freewheeling energy in the transformer.

In this paper, to overcome these disadvantages of the BHB converter, a new high efficiency and low profile

Manuscript received June 30, 2005; revised Dec. 15, 2005 †Corresponding Author: gwmoon@ee.kaist.ac.kr

Tel: +82-42-869-3475, Fax: +82-42-861-3475, KAIST

<sup>\*</sup>Dept. of Electrical Engineering and Computer Science, KAIST

<sup>\*\*</sup>School of Electrical Engineering, Kookmin University

Fig. 1 Conventional BHB converter

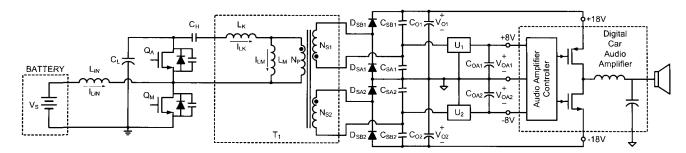

Fig. 2 Circuit diagram of the proposed converter

on-board DC/DC converter is proposed. The operational principles of the proposed converter are analyzed and the advantages are described. A 60W industrial sample for digital car audio amplifier has been implemented to verify the operational principles and the advantages of the proposed converter.

## 2. Principles of Operation

As shown in Fig. 2, the proposed converter is an asymmetrically controlled half bridge converter integrated with a boost converter in the output stage and a voltage doubling rectifier in the output stage. To simplify the analysis of the proposed converter, the following statements are assumed.

- All components are ideal except the primary MOSFETs which include the anti-parallel body diode and the parasitic output capacitor. The transformer is composed of an ideal transformer, a leakage inductor, and a magnetizing inductor.

- The proposed converter is operating in steady-state.

- The capacitances of C<sub>L</sub>, C<sub>H</sub>, C<sub>SA</sub>, and C<sub>SB</sub> are large enough to be considered as constant voltage sources.

#### 2.1 Modal Analysis

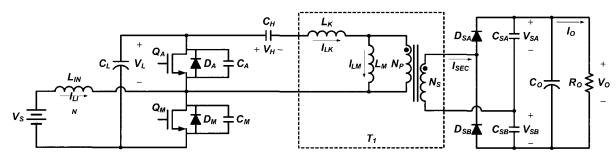

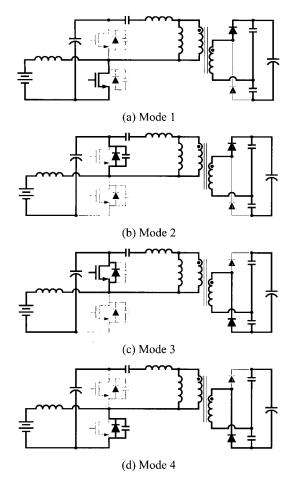

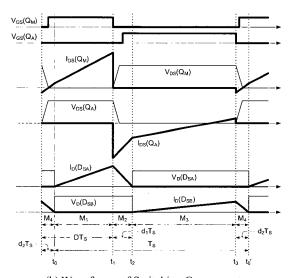

The proposed converter operates in four modes according to the switching states of the primary MOSFETs and the secondary diodes. The operational modes and the key waveforms are presented in Fig. 3 and Fig. 4, respectively. Before  $t_0$ ,  $I_{LIN}$  flows through  $Q_M$ , and  $I_{LK}$  flows through  $D_M$ . In addition,  $I_{SEC}$  flows through  $D_{SB}$  and abruptly increases toward zero.

**Mode 1** ( $M_1$ ,  $t_0 \sim t_1$ ): When  $I_{SEC}$  is increased to zero and  $D_{SB}$  is turned-off at  $t_0$ , Mode 1 begins and  $D_{SA}$  is turned-on as shown in Fig. 3(a). The boost inductor current,  $I_{LIN}$  and the transformer primary current,  $I_{LK}$  flows through  $Q_M$ , and linearly increases. The slopes of these currents are given by

$$\frac{d}{dt}I_{L_{IN}} = \frac{V_S}{L_{IN}} \tag{1}$$

$$\frac{d}{dt}I_{L_K} = \frac{1}{L_K} \left[ \left( V_L - V_H \right) - \frac{N_{P}}{N_S} V_{SA} \right] \tag{2}$$

The transformer's secondary current,  $I_{SEC}$  flows through  $D_{SA}$ , and linearly increases, while  $C_{SA}$  is charged and  $C_{SB}$  is discharged.

Fig. 3 Operational modes of the proposed converter

**Mode 2** ( $M_2$ ,  $t_1 \sim t_2$ ): When  $Q_M$  is turned-off at  $t_1$ , Mode 2 begins, as shown in Fig. 3 (b).  $I_{LIN}$  and  $I_{LK}$  flow through the parasitic output capacitors,  $C_M$  and  $C_A$ . Provided that the gating signal of  $Q_A$ ,  $V_{GS}(Q_A)$  becomes actively high when  $C_M$  is charged to  $V_L$  and  $C_A$  is discharged to zero, ZVS turn-on of  $Q_A$  is obtained. After,  $I_{LIN}$  and  $I_{LK}$  flow through the anti-parallel body diode,  $D_A$ , and decrease linearly with the current slopes of the following equations.

$$\frac{d}{dt}I_{L_{IN}} = \frac{V_S - V_L}{L_{IN}} \tag{3}$$

$$\frac{d}{dt}I_{L_K} = \frac{1}{L_K} \left[ \left( -V_H \right) - \frac{N_P}{N_S} V_{SA} \right] \tag{4}$$

$I_{SEC}$  flows through  $D_{SA}$  and abruptly decreases, while  $C_{SA}$  is charged and  $C_{SB}$  is discharged.

(a) Waveforms of Magnetic Components

(b) Waveforms of Switching Components

Fig. 4 Key waveforms of the proposed converter

**Mode 3** (M<sub>3</sub>,  $t_2\sim t_3$ ): When  $I_{SEC}$  is decreased to zero and  $D_{SA}$  is turned-off at  $t_2$ , Mode 3 begins and  $D_{SB}$  is turned-on as shown in Fig. 3 (c).  $I_{LIN}$  flows through  $D_A$ , charging  $C_L$ , and decreases linearly with the slope of the equation (3).  $I_{LK}$  flows through  $Q_A$  and decreases linearly with the following slope.

$$\frac{d}{dt}I_{L_K} = \frac{1}{L_K} \left[ \left( -V_H \right) + \frac{N_P}{N_S} V_{SB} \right] \tag{5}$$

$I_{SEC}$  flows through  $D_{SB}$  and linearly decreases, while  $C_{SA}$  is discharged and  $C_{SB}$  is charged.

**Mode 4 (M<sub>4</sub>, t<sub>3</sub>~t<sub>0</sub>')**: When  $Q_A$  is turned-off at t<sub>3</sub>, Mode 4 begins, as shown in Fig. 3 (d).  $I_{LIN}$  and  $I_{LK}$  flow through the parasitic capacitors, discharging  $C_M$  and charging  $C_A$ . By firing  $Q_M$  after the full discharge of  $C_M$ , we can achieve ZVS turn-on of  $Q_M$ . And then  $I_{LIN}$  flows through  $Q_M$ , increasing with the slope of the equation (1), and  $I_{LK}$  flows through  $D_M$ , increasing with the slope given by

$$\frac{d}{dt}I_{L_K} = \frac{1}{L_K} \left[ \left( V_L - V_H \right) + \frac{N_P}{N_S} V_{SB} \right] \tag{6}$$

$I_{SEC}$  flows through  $D_{SB}$  and abruptly decreases, while  $C_{SA}$  is discharged and  $C_{SB}$  is charged.

# 2.2 Input-Output Voltage Conversion Ratio

In order to derive the output voltage equation, it is assumed that  $V_L$ ,  $V_H$ ,  $V_{SA}$ ,  $V_{SB}$ , and  $V_O$  are constant during the switching period and the current of  $L_M$  is zero. By applying the voltage•second product equations on  $L_{IN}$ ,  $L_K$ , and  $L_M$  during one switching period, the following equations can be easily obtained.

$$V_L = \frac{1}{1-D}V_S \tag{7}$$

$$V_H = DV_I \tag{8}$$

$$V_{SA} = (1 - D - d_1 + d_2)V_Q = (1 - D)V_Q - \alpha \tag{9}$$

$$V_{SB} = (D + d_1 - d_2)V_Q = DV_Q + \alpha$$

(10)

where D is the duty ratio of  $Q_M$ , and  $\alpha$  is the correction factor. From the above equations, the peak currents of the secondary diodes are derived as follows:

$$I_{D,peak}(D_{SA}) = \frac{N_p}{N_s} \frac{DT_s}{L_K} \left[ (1 - D) \left( V_L - \frac{N_p}{N_s} V_O \right) + \frac{N_p}{N_s} \alpha \right]$$

(11)

$$I_{D,peak}(D_{SB}) = \frac{N_P}{N_S} \frac{(1-D)T_S}{L_K} \left[ D\left(V_L - \frac{N_P}{N_S}V_O\right) - \frac{N_P}{N_S}\alpha \right]$$

(12)

By applying the current-second product equations on  $C_{SA}$  and  $C_{SB}$  during one switching period, the equation of  $\alpha$  can be obtained as

$$\alpha = \frac{D(1-D)(1-2D)}{D^2 + (1-D)^2} \frac{N_S}{N_P} \left( V_L - \frac{N_P}{N_S} V_O \right)$$

(13)

Therefore, the peak currents of the secondary diodes are

arranged by substituting equation (13) into (11) and (12) as the following equations.

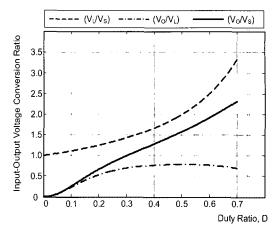

Fig. 5 Input-output voltage conversion ratio

$$I_{D,peak}(D_{SA}) = \frac{N_P}{N_S} \frac{DT_S}{L_K} \frac{(1-D)^2}{D^2 + (1-D)^2} \left( V_L - \frac{N_P}{N_S} V_O \right)$$

(14)

$$I_{D,peak}(D_{SB}) = \frac{N_P}{N_S} \frac{(1-D)T_S}{L_K} \frac{D^2}{D^2 + (1-D)^2} \left( V_L - \frac{N_P}{N_S} V_O \right)$$

(15)

Since the output load current equals the average current of  $D_{SA}$  or  $D_{SB}$ , it is given by

$$I_{O} = \frac{V_{O}}{R_{O}} = \frac{1}{2} \times DT_{S} \times I_{D,peak}(D_{SA}) \times \frac{1}{T_{S}}$$

$$= \frac{1}{2} \times (1 - D)T_{S} \times I_{D,peak}(D_{SB}) \times \frac{1}{T_{S}}$$

(16)

Therefore, by substituting equations (14) or (15) into (16), the ratio of  $V_0$  to  $V_L$  is derived as

$$\frac{V_o}{V_L} = \frac{\frac{N_s}{N_p} D^2 (1 - D)^2}{D^2 (1 - D)^2 + \left(\frac{N_s}{N_p}\right)^2 \frac{2L_K F_s}{R_O} \left[D^2 + (1 - D)^2\right]}$$

(17)

where  $F_S$  is the switching frequency and it equals  $1/T_S$ . Finally, by substituting equation (7) into (17), we can obtain the input-output voltage conversion ratio of the proposed converter as the following equation.

$$M = \frac{V_O}{V_S} = \frac{\frac{N_S}{N_P} D^2 (1 - D)}{D^2 (1 - D)^2 + \left(\frac{N_S}{N_P}\right)^2 \frac{2L_K F_S}{R_O} \left[D^2 + (1 - D)^2\right]}$$

(18)

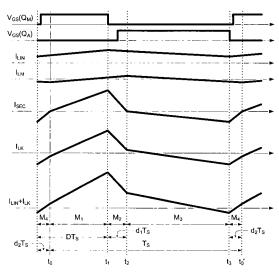

The input-output voltage conversion ratio is plotted as a function of duty ratio D in Fig. 5 under the conditions of  $N_P/N_S=1$ ,  $L_K=2\mu H$ ,  $F_S=100kHz$ , and  $R_O=12\Omega$ .

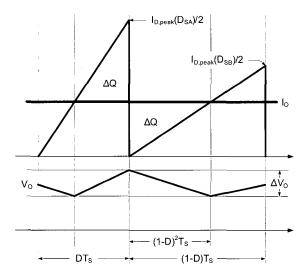

Fig. 6 Simplified output voltage and current waveforms

# 2.3 Output Voltage Ripple Ratio

In order to derive the output voltage ripple ratio of the proposed converter with the condition of D < 0.5, an increased charge or a decreased charge of the output capacitor is needed, as shown in Fig. 6. Moreover, the decreased charge can be obtained more easily as follows.

$$\Delta Q = C_O \Delta V_O = \frac{1}{2} \times I_O \times (1 - D)^2 T_S$$

(19)

Therefore, by arranging the equation (19), the output voltage ripple ratio of the proposed converter can be obtained as

$$\frac{\Delta V_o}{V_O} = \frac{(1 - D)^2}{2C_o R_o F_s}, \quad D < 0.5$$

(20)

In addition, the output voltage ripple ratio with the condition of D > 0.5 can be derived similarly and it is given by

$$\frac{\Delta V_o}{V_o} = \frac{D^2}{2C_o R_o F_s}, \quad D > 0.5$$

(21)

On the other hand, the output voltage ripple ratio of the conventional BHB converter is given by these equations.

$$\frac{\Delta V_o}{V_o} = \frac{\left| 1 - 2D \right|}{16L_o C_o F_s^2} \tag{22}$$

As can be seen in equations (20) and (21), the proposed converter shows relatively larger output voltage ripples than the conventional BHB converter. Since there is no need for an output inductor in the proposed converter, the properly sized output capacitor can be available without an increase in size.

# 2.4 ZVS Characteristics of Primary MOSFETs

ZVS of the primary MOSFETs is related to input current  $I_{LIN}$  and the transformer primary current  $I_{LK}$  at the switching instant. The current to achieve ZVS turn-on of  $Q_A$  at  $t_1$  can be expressed by the sum of  $I_{LK}(t_1)$  and  $I_{LIN}(t_1)$  as follows.

$$I_{ZVS,Q_1} = I_{L_V}(t_1) + I_{L_{DV}}(t_1)$$

(23)

where

$$I_{L_{K}}(t_{1}) = \frac{1}{L_{K}F_{S}} \frac{D(1-D)^{2}}{D^{2} + (1-D)^{2}} \left(\frac{1}{1-D}V_{S} - \frac{N_{P}}{N_{S}}V_{O}\right)$$

(24)

$$I_{L_{IN}}(t_1) = \frac{1}{\eta} \frac{V_O^2}{V_S R_O} + \frac{V_S}{2L_{IN} F_S} D$$

(25)

and  $\eta$  is the efficiency of the proposed converter. Therefore, ZVS condition of  $Q_A$  is obtained as

$$\frac{1}{2}L_{K}I_{ZVS,Q_{A}}^{2} \ge \frac{1}{2(1-D)^{2}}(C_{M} + C_{A})V_{S}^{2}$$

(26)

where  $C_M$  and  $C_A$  are the output capacitances of  $Q_M$  and  $Q_A$ , respectively. On the other hand, the current to obtain ZVS turn-on of  $Q_M$  at  $t_3$  can be expressed by the difference of  $|I_{LK}(t_3)|$  and  $I_{LIN}(t_3)$  as follows.

$$I_{ZVS,O_{M}} = \left| I_{L_{K}}(t_{3}) \right| - I_{L_{M}}(t_{3}) \tag{27}$$

where

$$\left|I_{L_{\kappa}}(t_{3})\right| = \frac{1}{L_{\kappa}F_{s}} \frac{D^{2}(1-D)}{D^{2}+(1-D)^{2}} \left(\frac{1}{1-D}V_{s} - \frac{N_{p}}{N_{s}}V_{o}\right)$$

(28)

$$I_{L_{IN}}(t_3) = \frac{1}{\eta} \frac{V_o^2}{V_c R_O} - \frac{V_S}{2L_{IN} F_c} D$$

(29)

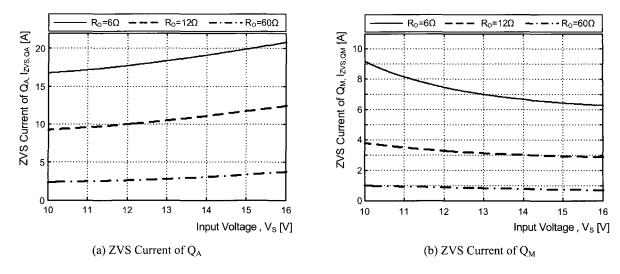

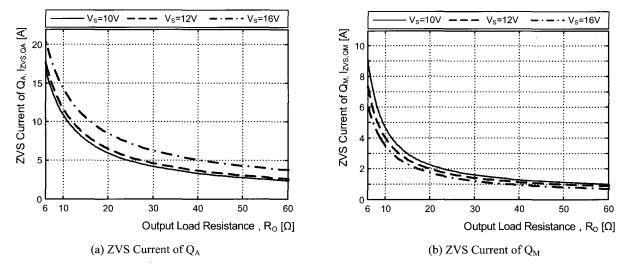

Fig. 7 ZVS current of primary MOSFETs as the function of the input voltage

Fig. 8 ZVS current of primary MOSFETs as the function of the load resistance

Thus, the ZVS condition of Q<sub>M</sub> is obtained as

$$\frac{1}{2}L_{K}I_{ZVS,Q_{M}}^{2} \ge \frac{1}{2(1-D)^{2}}(C_{M} + C_{A})V_{S}^{2}$$

(30)

With the condition of  $N_P:N_S=1:1$ ,  $L_{IN}=50\mu H$ ,  $L_K=2\mu H$ , and  $F_S=100kHz$ , ZVS currents of the primary MOSFETs are plotted as functions of the input voltage and the load resistance in Fig. 7 and Fig. 8, respectively. In this case, ZVS turn-on of  $Q_M$ , as well as  $Q_A$ , can be obtained from 10% to 100% output load in the overall input voltage range, provided that the primary MOSFETs are selected to satisfy the following equation.

$$C_M + C_A \le 1.862 \text{nF}$$

(31)

# 2.5 Advantages of Proposed Converter

The advantages of the proposed converter are as follows:

i) The BHB converter has a DC offset of the transformer magnetizing current given by

DC Magnetizing Current =

$$I_{L_M,DC} = \frac{N_S}{N_P} (1 - 2D) \frac{V_O}{R_O}$$

(32)

where  $N_S = N_{S1} = N_{S2}$ . On the other hand, the proposed converter has no DC offset of the transformer's

magnetizing current due to the series-connected DC blocking capacitors, C<sub>H</sub>, C<sub>SA</sub>, and C<sub>SB</sub>. That is, since the average currents of both the primary and the secondary sides of the transformer are zero, the average current of the magnetizing inductor is also zero. As a result, since optimal design of the transformer is possible, the size of the transformer can be minimized and the radiated heat of the transformer can be greatly reduced.

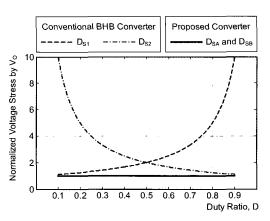

ii) The voltage stress of secondary diodes,  $D_{S1}$  and  $D_{S2}$  in the BHB converter is given by

Voltage Stress of

$$D_{S1} = V_{D_{S1}} = 2\frac{N_S}{N_P}V_H = V_O/(1-D)$$

(33)

Voltage Stress of

$$D_{S2} = V_{D_{S2}} = 2\frac{N_S}{N_D}(V_L - V_H) = V_O/D$$

(34)

where  $N_S = N_{S1} = N_{S2}$ . Therefore, the voltage stress of  $D_{S2}$  increases at high input voltage and light load conditions. However, in the proposed converter, the voltage stresses of the secondary rectifier diodes,  $D_{SA}$  and  $D_{SB}$  are always clamped to the output voltage  $V_O$  regardless of the duty ratio D as follows.

Voltage Stress of

$$D_{SA} = V_{D_{SJ}} = V_{O}$$

(35)

Voltage Stress of

$$D_{SB} = V_{D_{CB}} = V_{O}$$

(36)

The voltage stresses, normalized by  $V_{\rm O}$ , of the secondary diodes in both converters as the functions of the duty ratio, D are shown in Fig. 9.

- iii) In the conventional BHB converter, a serious voltage ringing exists in the secondary diodes. Thus, an RC snubber or transient-voltage-suppressor (TVS) has to be used, which deteriorates efficiency. Conversely, since the secondary diodes of the proposed converter are turned-off under ZCS condition, the turn-off voltage oscillation is very small. Therefore, since the use of the snubbers is not necessary, the proposed converter can achieve high efficiency.

- iv) Since the proposed converter has no output inductor, conduction loss can be greatly reduced, and this is desirable for a low profile and lower cost.

- v) In the BHB converter, the non-power-transfer time interval exits due to the commutation of  $D_{S1}$  and  $D_{S2}$ . Thus, the effective duty ratio,  $D_{eff}$ , is decreased in the BHB converter as in the following equation.

Fig. 9 Normalized voltage stress of the secondary diodes

$$D_{eff} = D - 2L_K I_{L_0} F_S \frac{N_S}{N_P} \left( \frac{1}{V_H} + \frac{1}{V_L - V_H} \right)$$

(37)

On the other hand, the proposed converter always transfers the power of the primary stage to the secondary stage in the overall switching period and has no freewheeling energy. Thus, high efficiency can be obtained without large circulating energy loss in the proposed converter.

- vi) Since the primary MOSFETs,  $Q_M$  and  $Q_A$ , of the proposed converter are turned-on under the ZVS condition, switching loss can be minimized.

- vii) Since the input current is continuous, the proposed converter has a the minimized input filter.

Although the current stresses of the secondary diodes in the proposed converter are rather large compared with those in the conventional BHB converter, the proposed converter has high efficiency due to minimized conduction and switching losses. Furthermore, the proposed converter shows desirable features such as high power density and low profile due to the reduced count and size of magnetic components. In addition, the proposed converter is expected to have a low EMI due to the wide ZVS range of the primary MOSFETs, and ZCS turn-off of the secondary diodes.

## 3. Experimental Results

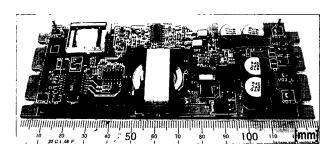

To verify the operational principles and the feasibility of the proposed converter, the 60W industrial sample of the proposed converter is implemented by employing the metal printed-circuit-board (PCB) for digital car audio

Fig. 10 Circuit diagram of 60W sample for digital car audio amplifiers

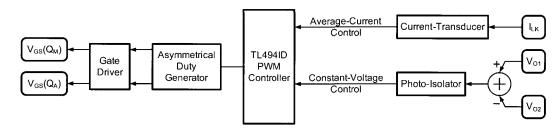

Fig. 11 Control scheme of 60W sample for digital car audio amplifiers

amplifiers. The circuit diagram and the control scheme of the proposed system are shown in Fig. 10 and Fig. 11, respectively. As can be seen in Fig. 10, the proposed converter produces  $\pm 18V$  and  $\pm 8V$  as a power supply for the power stage and the controller stage of digital car audio amplifiers, respectively. The dimension of the industrial sample is  $129(L)\times48(W)\times13(H)$  [mm] and its photograph is presented in Fig. 12.

Fig. 12 Photograph of 60W industrial sample for digital car audio amplifiers

Table 1 Design Specification for Digital Audio Amplifiers

| Input Voltage, V <sub>S</sub>            | 10V ~ 16V, 12V Nominal    |

|------------------------------------------|---------------------------|

| Output Voltage, Vo                       | +18V(1.5A) and -18V(1.5A) |

| Auxiliary Output Voltage, VOA            | +8V(0.4A) and -8V(0.4A)   |

| Maximum Output Power, P <sub>O,max</sub> | 60W                       |

| Switching Frequency, F <sub>S</sub>      | 100kHz                    |

Table 2 Circuit Parameters for Digital Audio Amplifiers

| L <sub>IN</sub>                               | 50μH, EPC17 (TDK)                            |

|-----------------------------------------------|----------------------------------------------|

| C <sub>L</sub>                                | 100μF, 35V, Electrolytic, 2EA                |

| Сн                                            | 22μF, 25V, MLCC, 2EA                         |

| $C_{SA1}$ , $C_{SB1}$ , $C_{SA2}$ , $C_{SB2}$ | 22uF, 25V, MLCC                              |

|                                               | 22uF, 25V, Tantal                            |

| C <sub>01</sub> , C <sub>02</sub>             | 470uF, 35V, Electrolytic, 2EA                |

| T <sub>1</sub>                                | PQ2610 (Magnetics)                           |

|                                               | $L_{M} = 100 \mu H, L_{K} = 2 \mu H$         |

|                                               | $N_P = 3, N_{S1} = 3, N_{S2} = 3$            |

| $Q_{M}$                                       | IRF1104S, D2-Pak (C <sub>OSS</sub> = 1.10nF) |

| QA                                            | IRFR3504, D-Pak (C <sub>OSS</sub> = 0.58nF)  |

| $D_{SA1}$ , $D_{SB1}$ , $D_{SA2}$ , $D_{SB2}$ | 12CWQ03FN, D-Pak                             |

| U <sub>1</sub>                                | UA78M08C, D-Pak                              |

| $U_2$                                         | UA79M08C, D-Pak                              |

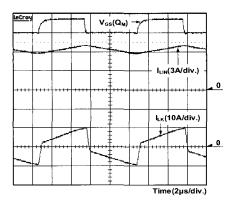

The design specifications of the sample are shown in Table 1. While the circuit parameters and the selected components are shown in Table 2. Moreover, the primary MOSFETs are chosen by the ZVS condition of  $Q_M$ , as presented in the equation (31). The input current,  $I_{LIN}$  and the transformer primary current,  $I_{LK}$ , at the nominal input voltage, is presented in Fig. 13. The input current is continuous and it has the small current ripple of 1.3A. The

Fig. 13 Experimental waveform of  $I_{LIN}$  and  $I_{LK}$  at  $V_S = 12V$

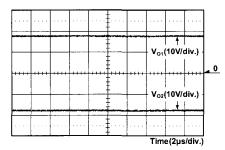

Fig. 14 Experimental waveforms of output voltages at  $V_S = 12V$

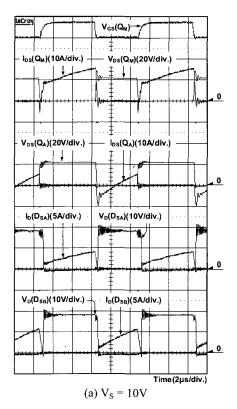

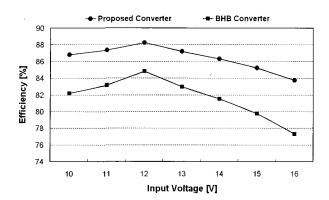

waveform of I<sub>LK</sub> agrees well with the theoretical waveform, as shown in Fig. 4, and it is balanced around zero for maximum efficiency at the nominal input voltage. Fig. 14 shows the output voltages of +18V and -18V with greatly reduced output voltage ripples and switching noises. The switching waveforms of the proposed converter at both the minimum and the maximum input voltages are presented in Fig. 15. As can be seen in this figure, the primary MOSFETs, Q<sub>M</sub> and Q<sub>A</sub> are turned-on under the ZVS condition and the secondary rectifier diodes are turned-off under ZCS condition at both the input voltages. In addition, the voltage stress of the secondary rectifier diodes is clamped to the output voltage, 18V, and the voltage oscillation is considerably small without the snubbers. The measured efficiencies of the proposed converter and the BHB converter are compared in Fig. 16. At nominal input voltage, the efficiency of the proposed converter is 88.3% and that of the BHB converter 84.8%. As can be seen in Fig. 16, the proposed converter shows higher efficiency than the conventional BHB converter in the overall input voltage range.

Fig. 15 Experimental waveforms of switching components

Fig. 16 Measured efficiencies

#### 4. Conclusions

In this paper, a new high efficiency and low profile on-board DC/DC converter for digital car audio amplifiers is proposed. The proposed converter shows a lack of DC magnetizing current for the transformer, low voltage stress of the overall active components, ZCS turn-off of the secondary diodes and no output inductor. Furthermore, the proposed converter has a wide ZVS range for the primary MOSFETs and a continuous input current.

The operational principles of the proposed converter were analyzed and the advantages were described. A 60W industrial sample of the proposed converter was implemented for digital car audio amplifiers to confirm the advantages of the proposed converter. The measured efficiency of the proposed converter was 88.3% at the nominal input voltage which is higher than that of the BHB converter at the overall input voltage range. The proposed converter demonstrates suitability for high efficiency and low profile on-board DC/DC converters for digital car audio amplifiers and other low input voltage applications.

#### Acknowledgment

This work was supported through research funds by NGVtek, Hyundai Motor Company, and Hyundai Autonet, Korea.

## References

[1] B-H. Gwee, J. S. Chang, H. Li, "A micropower low-

- distortion digital pulse width modulator for a digital class D amplifier," IEEE Trans. Circuits and Systems II: Analog and Digital Signal Processing, Vol. 49, Issue 4, pp. 245 256, April, 2002.

- [2] N.-S. Jung, N.-I. Kim; G.-H. Cho, "A new high-efficiency and super-fidelity analog audio amplifier with the aid of digital switching amplifier: class K amplifier," in Proc. IEEE PESC 1998, Vol. 1, pp. 457 – 463, May, 1998.

- [3] N.-I. Kim, S.-H. Jung, J.-Y. Ryoo, G.-H. Cho, "Ripple feedback filter suitable for analog/digital mixed-mode audio amplifier for improved efficiency and stability," in Proc. IEEE PESC 2002, Vol. 1, pp. 45 49, June, 2002.

- [4] J. Zeng, J. Ying, Q. Zhang, "A novel DC/DC ZVS converter for battery input application," in Proc. IEEE APEC 2002, Vol. 2, pp. 892 –896, March, 2002.

- [5] H. Watanabe, H. Matsuo, "A novel high-efficient DC-DC converter with 1V/20A DC output," in Proc. IEEE INTELEC 2002, pp. 34 –39, Sept.-Oct., 2002.

Chong-Eun Kim was born in Daegu, Korea in 1978. He received the B.S. degree in the Electrical Engineering from Kyungpook National University, Daegu, Korea, in 2001. In 2003, he received the M.S. degree in the Electrical Engineering from the Korea

Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, where he is currently working toward the Ph.D. degree.

His main research interests are DC/DC converters, power-factor-correction (PFC) AC/DC converters, soft switching technique, digital audio amplifiers, and plasma display panel.

Sang-Kyoo Han received the M.S. and Ph.D degrees in Electrical Engineering and Computer Science from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 2001 and 2005, respectively. For six months after that, he

worked as a post-doctoral fellow in KAIST where he developed digital display power circuits and preformed several research activities. Since September 2005. He has been with the Kookmin University, Seoul, Korea, as a professor of electrical engineering and worked for the Samsung Power Electronics Center (SPEC) as a research fellow. His research interests are in the areas of power electronics and digital display driver system, including analysis, modeling, design, and control of power converter, soft switching power converters, step-up power converters for electric drive system, multi-level converters and inverters, power

factor correction, Plasma Display Panel (PDP) driver, digital display driving circuit, and back light inverters for LCD TV. Mr. Han is a member of the Korean Institute of Power Electronics (KIPE).

Gun-Woo Moon was born in Korea in 1966. He received the B.S. degree from Han-Yang University, Seoul, Korea, and the M.S. and Ph.D. degrees in Electrical Engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, in 1990,

1992, and 1996, respectively. He is currently an Associate Professor in the department of Electrical Engineering and Computer Science, KAIST. His research interests include modeling, design and control of power converters, soft-switching power converters, resonant inverters, distributed power systems, power-factor correction, electric drive systems, driver circuits of plasma display panels, and flexible ac transmission systems. Dr. Moon is a member of the Korean Institute of Power Electronics (KIPE), Korean Institute of Electrical Engineers (KIEE), Korea Institute of Telematics and Electronics (KITE), and Korea Institute of Illumination Electronics and Industrial Equipment (KIIEIE).