**IPE 5-3-6**

# A Novel Boost-Input Full-Bridge Converter

Takahiro Sonoda\*, Tamotsu Ninomiya†, Satoshi Tomioka\*\*, Kei Sato\*\* and Hiroto Terashi\*\*

<sup>†\*</sup>Dept.of EESE, Kyushu University, 6-10-1 Hakozaki, Higashi-ku, Fukuoka, 812-8581, Japan <sup>\*\*</sup>Densei-Lambda K.K., 2701 Togawa, Settaya, Nagaoka, Niigata, 940-1195, Japan

#### **ABSTRACT**

In order to correct the power boost topology has been used for easy control. But conventional boost topology has the following drawbacks: switching voltage surge, cross conduction current and right-half-plane zero of its control transfer function. Furthermore, in this topology the output voltage is always higher than the input voltage. As a result, a first-stage boost PFC converter needs to be connected with a second-stage DC-DC converter. A new topology which can be used as single stage PFC converter is proposed in this paper.

Keywords: Single-Stage, PFC, ZVS

#### 1. Introduction

The conventional boost topology has the following drawbacks: high output voltage, cross conduction current, and a right-half-plane zero of the control transfer function.

This paper proposes a new topology to overcome these drawbacks. Two boost converters operating in an interleaving manner are connected in parallel, and four switches used in these boost converters with synchronous rectification derive an equivalent full- bridge converter by combining a transformer. This novel converter provides the following prominent features: small current ripple in both the input and the output sides, disappearance of right-half-plane zero under a certain parameter value, and availability of an arbitrary low voltage output. The

steady-state and the dynamic characteristics are analyzed in this paper. The analysis confirms that the novel converter provides ZVS operation, small input current ripple, and high efficiency.

# 2. Drawbacks of a Conventional Boost Converter

In a conventional boost converter, the output voltage is always higher than the input voltage. When the output voltage is required to be lower than the input voltage, it is necessary to use a buck, forward, half-bridge, or full-bridge converter as the second stage. As the result, the power efficiency is decreased. Furthermore, these two converters operating at different switching frequencies cause a beat-frequency phenomenon which cannot be suppressed by the output filter. To overcome these above drawbacks, this paper proposes a boost-input-type full-bridge converter topology.

Manuscript received January 14, 2005; revised May 17, 2005.

<sup>&</sup>lt;sup>†</sup>Corresponding Author: ninomiya@ees.kyushu-u.ac.jp

Tel: +81-92-642-3901, Fax: +81-92-642-3957, Kyushu Univ.

<sup>\*</sup>Dept.of EESE, Kyushu University

<sup>\*\*</sup>Densei-Lambda K.K.

# 3. Boost-Input Type Full-Bridge Converter

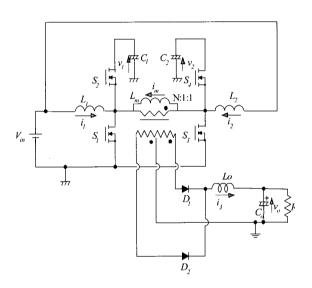

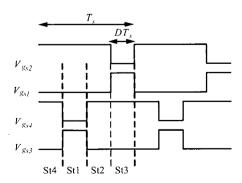

Figure 1 shows the circuit configuration of the proposed boost-full-bridge converter composed of two boost converters operating in an interleaving manner, where MOSFET switches are utilized instead of rectifying diodes and a transformer is used to build a full-bridge converter. Figure 2 illustrates the time chart of four switches  $S_1$ ,  $S_2$ ,  $S_3$ , and  $S_4$ .  $S_1$  and  $S_3$  are driven in a complimentary, interleaving manner, as are  $S_2$  and  $S_4$ . In this topology, the ZVS operations of all switches are achieved. The steady-state and the dynamic characteristics of this converter are derived by applying the state-space-averaging method<sup>[1,2]</sup>.

Fig. 1 Proposd Boost-Input Full-Bridge Converter

Fig. 2 Time Chart of Gate-Drive Signals for Four MOSFET Switches

# 4. State-Space Averaged Analysis

# 4.1 Basic Differential Equations

(a) In the case of D < 0.5:

First, the division of circuit states is shown in Fig. 2. Second, the state variables are selected as shown by eq.(1). Then, a state-space differential equation and an output equation are derived correspondingly to each state as shown by eqs.(2) and (3), respectively.

$$\vec{x} = (i_1 \quad i_3 \quad v_{c1} \quad v_{c2})^T \qquad \vec{y} = (i_1 \quad i_3 \quad v_1 \quad v_2)^T \tag{1}$$

$$\frac{d\vec{x}}{dt} = A_k \vec{x} + \overrightarrow{b_k} V in \tag{2}$$

$$\vec{y} = g_{\nu} \vec{x} \tag{3}$$

$$A_{1} = \begin{pmatrix} -\frac{r_{s} + r_{1}}{L} & -\frac{r_{s}}{NL} & 0 & 0\\ \frac{r_{c} - r_{s}}{NL_{o}} & -\frac{r_{\beta}}{L_{o}} & \frac{1}{NL_{o}} & -\frac{R_{o}}{L_{o}r_{a}}\\ 0 & 0 & 0 & 0\\ 0 & \frac{R_{o}}{C_{o}r_{a}} & 0 & -\frac{1}{C_{o}r_{a}} \end{pmatrix}$$

$$(4)$$

$$A_{2} = \begin{pmatrix} -\frac{r_{c} + r_{1}}{L} & -\frac{r_{c}}{NL} & -\frac{1}{L} & 0\\ 0 & -\frac{r_{\gamma}}{L_{o}} & 0 & -\frac{R_{o}}{L_{o}r_{a}}\\ \frac{1}{C} & \frac{1}{NC} & 0 & 0\\ 0 & \frac{R_{o}}{C} & 0 & \frac{-1}{C} r_{c} \end{pmatrix}$$

(5)

$$A_{3} = \begin{pmatrix} -\frac{r_{c} + r_{1}}{L} & \frac{r_{c}}{NL} & -\frac{1}{L} & 0\\ \frac{r_{c} - r_{s}}{NL_{o}} & -\frac{r_{\theta}}{L_{o}} & \frac{1}{NL_{o}} & -\frac{R_{o}}{L_{o}r_{a}}\\ \frac{1}{C} & -\frac{1}{NC} & 0 & 0\\ 0 & \frac{R_{o}}{C_{o}r_{o}} & 0 & -\frac{1}{C_{o}r_{a}} \end{pmatrix}$$

$$(6)$$

$$A_{4} = \begin{pmatrix} -\frac{r_{c} + r_{1}}{L} & \frac{r_{c}}{NL} & -\frac{1}{L} & 0\\ 0 & -\frac{r_{r}}{L_{o}} & 0 & -\frac{R_{o}}{L_{o}r_{a}}\\ \frac{1}{C} & -\frac{1}{NC} & 0 & 0\\ 0 & \frac{R_{o}}{C_{o}r_{a}} & 0 & -\frac{1}{C_{o}r_{a}} \end{pmatrix}$$

$$(7)$$

$$b_1 = b_2 = b_3 = b_4 = \begin{pmatrix} 1 & 0 & 0 & 0 \end{pmatrix}^T$$

(8)

$$g_{1} = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & \frac{R_{o}r_{co}}{r_{\alpha}} & 0 & \frac{R_{o}}{r_{\alpha}} \end{pmatrix}$$

$$(9)$$

$$g_{2} = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ r_{c} & \frac{r_{c}}{N} & 1 & 0 \\ 0 & \frac{R_{o}r_{co}}{r_{a}} & 0 & \frac{R_{o}}{r_{a}} \end{pmatrix}$$

(10)

$$g_{3} = g_{4} = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ r_{c} & -\frac{r_{c}}{N} & 1 & 0 \\ 0 & \frac{R_{o}r_{co}}{r_{a}} & 0 & \frac{R_{o}}{r_{a}} \end{pmatrix}$$

(11)

$$r_{\alpha} = R_{o} + r_{co}$$

$$r_{\beta} = \frac{r_{c} + r_{m} + r_{s}}{N^{2}} + r_{Lo} + \frac{R_{o}r_{co}}{r_{a}}.$$

$$r_{\gamma} = \frac{2r_{c} + r_{m}}{N^{2}} + r_{Lo} + \frac{R_{o}r_{co}}{r_{a}}$$

(12)

Applying the state-space-averaging method to the above-mentioned equations, a state-space averaged equation and an averaged output equation are obtained as shown by eqs.(13) and (14), respectively.

$$\frac{d\overline{x}}{dt} = A\overline{x} + bV_{in} \tag{13}$$

$$\overline{y} = g\overline{x} \tag{14}$$

$$A = DA_1 + (0.5 - D)A_2 + DA_3 + (0.5 - D)A_4$$

(15)

$$b = Db_1 + (0.5 - D)b_2 + Db_3 + (0.5 - D)b_4$$

(16)

$$g = Dg_1 + (0.5 - D)g_2 + Dg_3 + (0.5 - D)g_4$$

(17)

where,

$i_l$ ,  $i_3$ ,  $v_l$ , and  $v_o$ : as shown in Fig.1,

$v_{cl}$  and  $v_{co}$ : Capacitance voltage without ESR,

k: 1, 2, 3 and 4,

$r_{rl}$ : Parasitic resistance of primary stage inductor,

$r_{Lo}$ : Parasitic resistance of secondary stage inductor,

$r_m$ : Parasitic resistance of transformer,

$r_c$ : ESR of primary stage capacitor,

$r_{co}$ : ESR of secondary stage capacitor,

$r_s$ : ON resistance of MOSFET

D: Duty ratio of the switches  $S_1$  and  $S_3$

N: Turns ratio of transformer windings.

# 4.2 Steady-State Characteristics

Assuming that the derivative of (13) is zero, the steady-state characteristics are obtained. As a result, the voltage conversion ratio is expressed as eq.(18), where parasitic resistances associated with switches, inductors, transformer, and capacitors are neglected for simplicity.

$$\frac{V_o}{V_{in}} = \frac{2D}{N(1-D)} \tag{18}$$

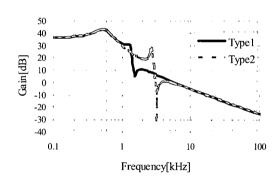

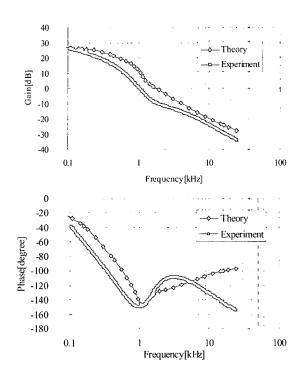

Fig.3 Bode Diagram for Two Cases of Transer Function with Different Parameters.

Type 1 :  $r_c$ =0.2[ $\Omega$ ] and C=44[ $\mu$ F]

Type 2 :  $r_c$ =0.01[ $\Omega$ ] and C=10[ $\mu$ F]

Common parameters for both cases:  $r_s$ =0.4[ $\Omega$ ],  $r_I$ = $r_m$ = $r_{Lo}$ =0.01[ $\Omega$ ],  $r_{co}$ =0.05[ $\Omega$ ], L=160[ $\mu$ H],  $L_o$ =60[ $\mu$ H],  $C_o$ =1200[ $\mu$ F],  $R_o$ =12[ $\Omega$ ], N=4, D=0.35 and  $V_{in}$ =140[V]

#### (b) In the case of D>0.5:

The voltage conversion ratio in this case is derived by the same procedure as the previous one, and is expressed

$$\frac{V_o}{V_{in}} = \frac{2}{N} \tag{19}$$

Hence the conversion ratio does not depend on the duty ratio when D>0.5. Therefore, the duty ratio is required to be smaller than 0.5 for the output regulation.

### 4.3 Dynamic Characteristics

Applying the perturbations to the variables around their steady-state values such as  $\overline{x} \to X + \Delta X$ ,  $\overline{y} \to Y + \Delta Y$ , and  $D \to D + \Delta D$ , a linearized small-signal model for D < 0.5 is obtained as follows:

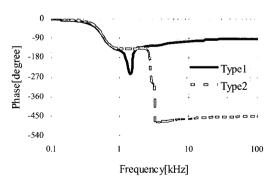

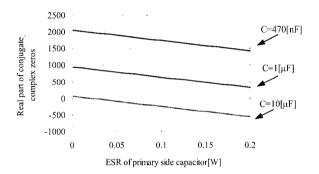

Fig. 4 Effect of ESR of Primary-side Capacitor on the Real Part of Conjugate Complex Zeros

$$\Delta X(s) = (s - A)^{-1} \left(\frac{\partial A}{\partial D} X + \frac{\partial b}{\partial D} V_{in}\right) \Delta D(s)$$

(20)

$$\Delta Y(s) = g\Delta X(s) + \frac{\partial g}{\partial D} X \Delta D(s)$$

(21)

$$\frac{\partial A}{\partial D} = A_1 - A_2 + A_3 - A_4 \tag{22}$$

$$\frac{\partial b}{\partial D} = b_1 - b_2 + b_3 - b_4 \tag{23}$$

$$\frac{\partial g}{\partial D} = g_1 - g_2 + g_3 - g_4 \tag{24}$$

Furthermore, the control transfer function of this converter is derived as follows:

$$\frac{\Delta Vo(s)}{\Delta D(s)} = \frac{K(s^3 + \alpha s^2 + \beta s + \gamma)}{\{1 + 2\xi_1(\frac{s}{\omega_1}) + (\frac{s}{\omega_1})^2\}\{1 + 2\xi_2(\frac{s}{\omega_2}) + (\frac{s}{\omega_2})^2\}}$$

(25)

where

$\omega_1$ : First peak frequency,

$\omega_2$ : Second peak frequency,

$\xi_1$ : Damping factor of first peak,

$\xi_2$ : Damping factor of second peak,

$K, \alpha, \beta, \gamma$ : Constant value.

The converter stability can be estimated by examining whether one of three zeros represented by this control transfer function is located in the right-half plane or not. Figure 3 compares two cases of the frequency characteristics: Type 1 is the transfer function without any right-half-plane zeros, and Type 2 is with a right-half-plane zero. The location of these zeros strongly depends on parasitic resistances. The effect of ESR of the primary-side capacitors on the location of zeros is shown in Fig.4, where the real part of the conjugate complex zeros of the transfer function is examined. It shows that the decrease of the ESR of the primary-side capacitors causes converter instability, and that a larger capacitance is needed to assure converter stability.

#### 5. Experiment

In order to evaluate the performance of this converter experimentally, a breadboard was implemented using the following specifications and parameters:

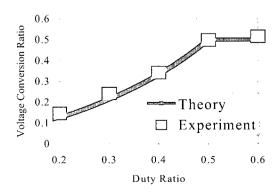

Fig. 5 Voltage Conversion Ratio vs. Duty Ratio

Fig. 6 Bode Diagrams of the Control Transfer Function

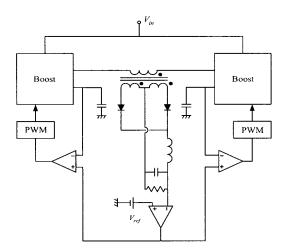

Fig. 7 Block Diagram of Double Feedback loops

$$V_{in}$$

=140[V],  $f_s$ =200[kHz],  $L_I$ = $L_2$ =160[ $\mu$ H],  $C_I$ = $C_2$ =44[ $\mu$ F],  $L_o$ =60[ $\mu$ H],  $C_o$ =1200[ $\mu$ F], N=4.

Figure 5 shows the relation of the voltage conversion ratio and the duty ratio, and Figure 6 illustrates Bode plots of the control transfer function. The analytical and experimental results are compared, respectively, and a good agreement is obtained.

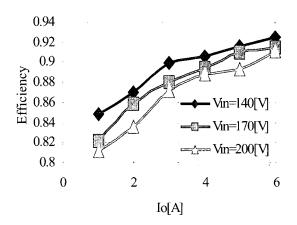

Fig. 8 Power Efficiency (Vo=48[V])

In practical applications, a transformer should be protected from the asymmetrical magnetization, so the voltage across the primary-side capacitor is regulated to be equal to each other as shown in Fig.7, where double feedback loops are used for the output voltage and the voltage across the primary-side capacitors. The experimental results measuring power efficiency are shown in Fig.8, where Vin =140 to 200V, Vout=48V, and Io= 1 to 6A. A high efficiency of over 90% was obtained for the output power of 300W.

# 6. Conclusion

A novel topology of boost-input full-bridge converters has been proposed. The steady-state and dynamic characteristics were analyzed by using the state-space averaging method and were experimentally confirmed. It is predicted that the application of this converter to a power-factor-correction converter derives some prominent features. This work will be pursued in the future.

#### References

- [1] R.D.Middlebrook, S.Cuk: "General Unified Approach to Modeling Switching-Converter Power Stages," IEEE PESC'76 Record, pp. 18-34.

- [2] T.Ninomiya, M.Nakahara, T.Higashi, K.Harada: "Unified Analysis of Resonant Converters," IEEE Trans. on Power Electro., Vol. 6, No.2, pp.260-270, April 1991.

**Takahiro Sonoda** was born in Oita Prefecture, Japan in 1979. He received the B.E. degree in electrical engineering from Kyushu University, Japan, in 2003. And he has been a M.E. student in electrical engineering since 2003. His interests include

developing and designing PFC switched-mode power converter topologies. He is an IEEE students member.

Tamotsu Ninomiya received the B.E., M.E., and Dr. Eng. degrees in electronics from Kyushu University, Japan. Since 1969, he has been associated with the Department of Electronics, Kyushu University, first as a Research Assistant and since 1988 as a

Professor. Since the re-organization in 1996, he has been a Professor in the Department of Electrical and Electronic Systems Engineering of the Graduate School of Information Science and Electrical Engineering. He is a specialist in the field of power electronics, including the analysis of switching power converters their electromagnetic interference problems, and development of noise suppression techniques, piezoelectric-transformer converters. He has served as a member of Program Committees for PESC and APEC, as Program Vice Chairman for 1988 PESC, and General Chairman for 1998 PESC. He was a member of the Administrative Committee of IEEE PELS from 1993 through 1998. In January 2001, he was awarded as IEEE Fellow.

Satoshi Tomioka was born in Niigata Prefecture, Japan in 1961. He received the B.S. degrees in electrical engineering from Tokyo Denki University, Japan, in 1984. Since 1984, he has been working with NEMIC-LAMBDA K.K. (presently

DENSEI-LAMBDA K.K.). He is currently a manager of Power Module development department. He is a Member of the Institute of Electronics, Information and Communication Engineers of Japan.

**Kei Satoh** was born in Fukuoka Prefecture, Japan in 1972. He received the B.S. and M.S. degrees in electrical engineering from Kumamoto Institute of Technology (presently Sojo University), Japan, in 1995 and 1997, respectively. Since 1997, he has

been working with NEMIC-LAMBDA K.K. (presently DENSEI-LAMBDA K.K.). He is currently working on Power Module development department.

Hiroto Terashi received the B.E. degree in clectronics from Shibaura Institute of Technology in 1975. During 1975-1989, he worked in Kenwood Corp. and Asahi-Pentax Corp. to develop Audio and Video equipment and the control of CD-RW drive.

Since 1989 he has been associated with Densei-Lambda Corp. to develop DC-DC converters. He is now with the graduate school of Kyushu University to obtain the Ph.D. degree.