# Sensitivity Analysis of Plasma Charge-up Monitoring Sensor

Sung Joon Lee, Dea-Wha Soh, and Sang Jeen Hong, Member, KIMICS

Abstract—High aspect ratio via-hole etching process has emerged as one of the most crucial means to increase component density for ULSI devices. Because of charge accumulation in via-hole, this sophisticated and important process still hold several problems, such as etching stop and loading effects during fabrication of integrated circuits. Indeed, the concern actually depends on accumulated charge. For monitoring accumulated charge during plasma etching process, charge-up monitoring sensor was fabricated and tested under some plasma conditions. This paper presents a neural network-based technique for analyzing and modeling several electrical performance of plasma charge-up monitoring sensor.

*Index Terms*—Charge-up monitoring sensor, Neural networks, Plasma, *SiO*<sub>2</sub> etching

#### I. INTRODUCTION

Over the past few years, a device size in modern semiconductor manufacturing has continuously decreasing as component density increase. And shifting towards the next generation ultra large scale integrated-circuits (ULSI), SiO<sub>2</sub> via-holes etching with a high aspect ratio is a key process for fabrication of multilayer interconnect. Via etching for dual-damascene process with 0.18µm node or less requires high aspect ratio inter-metal dielectric (IMD) etching consisting of intermediate nitride and oxide layers or low-k dielectrics. As the gate oxide thickness dramatically decreases to improve device performance, charging damage is becoming more of a concern. The damage can degrade all the electrical properties of a gate oxide. With the advent of high density plasma technology, deep-via etching has become feasible and continuously developed. However, this etching process still holds some unresolved difficulties: etching stop [1], micro-loading effect [2], and charge-up damage [3-5]. One of the most crucial problems is charge-up damage in via holes. Etching stop can be caused by a reduced transport of reactive species in deep and narrow structures, and the micro-loading effect by a local depletion

of reactive species. Thus, it is expected that as the aspect ratio of via holes increase, the much more accumulated charge is significant in ULSI.

In  $SiO_2$  etching process using fluorocarbon gas plasmas, a fluorocarbon film is deposited on the underlayer surface and sidewall of via holes. In fact, the deposited fluorocarbon polymer has influenced upon the etching characteristics and charge accumulation in  $SiO_2$  via-hole etching process [6]. To accomplish an optimal high aspect ratio etching process for next generation device fabrication, it will be very significant work to monitor and control the amount of charge accumulated in  $SiO_2$  layer.

In Section II, charge-up monitoring sensor to finally measure accumulated charge in high aspect ratio via holes and measurement are introduced. To make firm the functionality of the sensor, charging potential between two electrodes is measured during Ar plasma discharge. The general concept of neural networks is discussed in Section III, followed by an analysis of experiment with neural networks and response surface plots. Finally, in Section IV, the results and discussion are presented, followed by conclusion in Section V.

#### II. EXPERIMENT AND MEASUREMENT

According to experienced bowing of high aspect ratio via holes etching in  $SiO_2$  dielectrics, a major reason for the viahole bowing was converged to the charge accumulation on the sidewall due to fluorocarbon polymer. When  $SiO_2$  film is etched under fluorinated plasma, such as  $C_4F_8$  or  $C_2F_4$ , it generates many high molecular weight radicals ( $C_xF_y$  radicals) that contribute to the fluorocarbon polymer deposition. Recently, it has been reported that the deposited fluorocarbon on sidewall of via-hole patterns is conductive, and this can cause mitigation of accumulated electric charge [7].

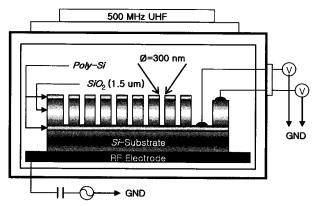

An intention of developing the charge-up damage sensor is to monitor  $SiO_2$  etching process in real-time as regards accumulated charge. On a 2" Si <100> wafer, 300nm of silicon dioxide layer was thermally deposited. On the top electrode, a great number of 300nm vias in their diameters were formed to perform high aspect ratio (1:5) via hole etching process. For more high aspect ratio either/both thinner IMD SiO<sub>2</sub> and/or smaller via size was desired, but this was the critical fabrication capability under the university research environment. However, 1:5 aspect ratio was high enough to performing sidewall conductivity measurement. Figure 1 shows a schematic of the structure of fabricated charge-up sensor. To verify the performance of the fabricated damage sensor, the charging potential of two polycrystalline silicon electrodes was measured after via-etching is completed.

Manuscript received November 29, 2005.

Sung Joon Lee is currently a graduate student in the Department of Electronic Engineering at Myongji University.

Dae-Wha Soh is a professor in the Department of Electronic Engineering and director of semiconductor technology center at Myongji University.

Sang Jeen Hong is a with the Department of Electronic Engineering & NBRC at Myongji University, 38-2 San, Nam-dong, Yongin, Gyeonggi-do, Korea, 449-728 (Tel: +82-31-335-6374, Email: samhong@mju.ac.kr)

Fig. 1 A schematic of charge-up damage sensor

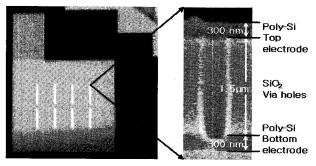

Fig. 2 A cross section SEM photo of fabricated sensor with 300nm via holes

A cross sectional SEM photograph is presented in Figure 2. In this exercise, a home-made UHF (500MHz) plasma reactor was employed. This etching system provides the mean electron energy was about 2-3eV, and the electron density was about  $10^{11}cm^{-3}$ .

The charge-up sensor was located on the RF electrode in the plasma reactor (see Figure 1). While Ar plasma was irradiated, DC potential between the top and the bottom electrodes was measured.

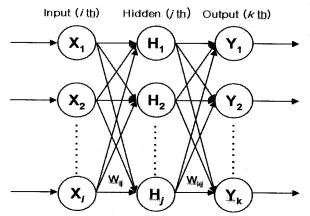

Fig. 3 Typical feed-forward NN structure

## III. SENSITIVITY ANALYSIS

Neural network is a structured interconnection of computational nodes called "neurons" that contribute to parallel computation in a manner similar to the human brain. Each neuron contains the weighted sum of its

inputs filtered by a neuron activation function, providing NNs with the ability to generalize with an added degree of freedom that is not available in traditional regression techniques [8]. General feed-forward NN structure consists of multiple neurons in one input layer, one or more hidden layers, and one output layer. Figure 3 depicts such a structure with a single hidden layer. The neurons in the input and output layers corresponded to the input factors and the process responses, respectively. The number of neurons in the hidden layer(s) is varied to give the best modeling results for the input/output mapping. Due to their inherent ability to learn complex nonlinear mappings from limited data, NNs offer an efficient, fast, and accurate method of process modeling. NNs have been successfully applied to semiconductor process modeling, optimization, and control [9].

In this study, to build the NN models, we employed one simulation machine which can create, train, and test NN models. Three input factors with three levels of each were considered: pressure, source power, and bias power. The response of interest was the potential difference measured (refer to Table 1).

Table 1 Process parameters, unit, and their ranges

| Name                 | Abbry.   | Range          | Unit  |

|----------------------|----------|----------------|-------|

| Pressure             | PRES     | 5, 15, 25      | mTorr |

| Bias Power           | Bias_PWR | 1, 25, 50      | watts |

| Source Power         | Src_PWR  | 500, 750, 1000 | watts |

|                      |          |                |       |

| Name                 |          | Abbry.         | Unit  |

| Potential Difference |          | V_Dif          | V     |

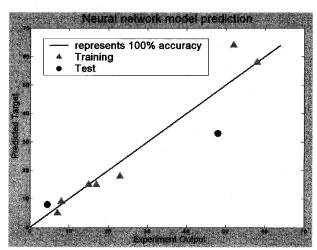

Fig. 4 Performance evaluation of process

After setting up percentage used for training and test, there are randomizations of network weights. And then NNs were trained with the data. Several networks with different numbers of hidden neurons were performed until RMSE (root-mean-square-error) reached stopping conditions (target RMSE and maximum iterations). Model performance is depicted in Figure 4.

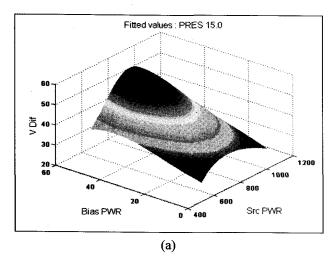

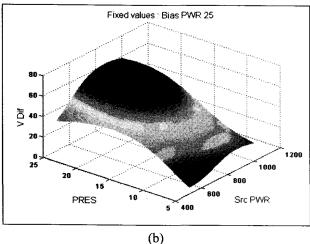

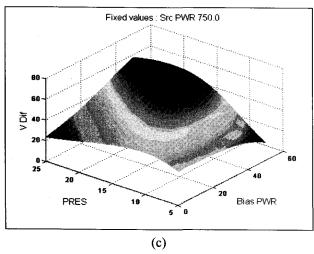

Fig. 5 Response surface plots for V\_Difference at fixed values; (a) Pressure:15, (b) Bias Power:25, and (c) Source Power:750

## IV. RESULTS AND DISCUSSION

Under higher pressure with Ar plasma irradiation, dissociated reactive ions are tend to more like to get directed vertically rather than a condition of lower pressure plasma. Thus, charging potential under higher pressure can be less than others.

Once the neural process model is established, response surfaces are generated to explain on the relationships between any two process parameters of three and an interesting response. On the other hand, the remaining factor is set to its mid-range level.

Response surface plots shown as Figure 5 present the relationship between two factors and a response while the rest of input factors is fixed at its mid-range.

Figure 5(a) presents the effect of bias and source power on the degree of the potential difference when the pressure is hold to 15mTorr. At a given bias and source power, the accumulated charge slightly increases. The graph presents very low curvature near the middle range of source power. This means low degree of correlation between process parameters and the response. However, as bias power increases and source power is in the middle of the range, the accumulation charge distribution is somewhat notable. An observed pattern in Figure 5(b) is similar to Figure 5(a). There are little point in Figure 5(c). But, high bias power and pressure are worthy of notice about the aspect of accumulated charge. This needs to be further investigation.

#### V. CONCLUSION

To summarize, a sensor fabrication and a measurement of charging potential under Ar plasma discharge as a method of accumulated charge in via holes patterns. An useful method for measuring accumulated charge using the fabricated charge-up damage sensor has generated and the response surface plots were also shown to identify suitable process conditions to avoid plasma charge damage, which is one of the most crucial problems.

#### REFERENCES

- [1] Ogawa E.T, Lee K.D, Matsuhashi H, Ko K.S, Justison P.R, Ramamurthi A.N, Bierwag A.J, Ho P.S. Blaschke V.A, and Havemann R.H, "Statistics of electromigration early failures in Cu/Oxide dual-damascene interconnects," *in Proc. Reliability Physics Symposium*, 2001, pp. 341-349.

- [2] S. Samukawa and T. Mukai, "High-performance of process-induced charging in scaled-down devices and reliability improvement using time-modulated plasma," *J. Vac. Sci. Tech. B*, vol. 18, no. 1, 2000, pp.166-171.

- [3] C. Hedlund and S. Berg, "Microloading effect in reactive ion etching," *J. Vac. Sci. Tech. A*, vol. 12, no. 42, 1994, pp. 1962-1965.

- [4] T. Nozawa and T. Kinoshita, "The electron charging effects of plasma on notch profile defects", *Jpn. J. Appl. Phys.*, part I. vol. 34, no. 4B, 1995, pp. 2107-2113.

- [5] T. Kinoshita, M. Hane, and J. P. McVittie, "Notching as an example of charging in uniform high density plasmas", *J. Vac. Sci. Tech. B*, vol. 14, no. 1, 1996, pp. 560.

- [6] K. Hashimoto, "New phenomena of charge damage in plasma etching: heavy damage only through dense-line

- antenna", *Jpn. J. Appl. Phys.*, part I, vol. 32, no. 12B, 1993, pp. 6109-6113.

- [7] T. Simmura, S. Soda, S. Samukawa, M. Koyanagi, and K. Hane, "electrical conductivity of sidewall deposited fluorocarbon polymer in *SiO*<sub>2</sub> etching processes", *J. Vac. Sci. Tech. B*, vol. 20, no. 6, 2003, pp. 2346-2350.

- [8] T. Simmura, S. Soda, S. Samukawa, K. Hane, "Mitigation of Accumulated electric Charge by Deposited Flurocarbon Film during SiO<sub>2</sub> Etching", J. Vac. Sci. Tech. A. vol. 22, no. 2, 2004, pp. 433-436.

- [9] C. himmel and G. May, "Advantages of plasma etch modeling using neural networks over statistical techniques", *IEEE Trans. Semiconductor Manufacturing*, vol. 6, no. 2, 1993, pp. 103-111.

#### **Sung Joon Lee**

He received B.S. degree in electronic engineering from Myongji University, Korea, in 2005.

He is currently working on a master's degree in Electronic Engineering, Myongji University, Yongin, Korea. His research interest is plasma induced

damage and statistical process control (SPC) in semiconductor manufacturing.

#### Dea-Wha Soh

He received the B.S. degree in electrical engineering from Hanyang University, Korea, in 1972 and the M.S. degree in electrical engineering from Myongji University, Korea, in 1975 and Ph.D. degree in electrical engineering from Kyunghee University, Korea, in 1987.

Currently, he is a professor in the Department of Electronic Engineering at Myongji University, Yongin, Korea. His research interest is semiconductor material and device fundamentals.

## Sang Jeen Hong

He received the B.S. degree in electrical engineering from Myongji University, Korea in 1999 and the M.S. and Ph.D. degree in electrical and computer engineering from the Georgia Institute of Technology, Atlanta, in 2001 and 2003, respectively.

Currently, he is an assistant professor in the Department of Electronic Engineering at Myongji University, Yongin, Korea, and he also serves as an editorial board of *KIMICS* and *KIEEME*. His research interest is statistical process control (SPC) and advanced process control (APC), real-time fault detection and classification, and plasma induced damage in plasma etch process focused on high volume semiconductor manufacturing environment.