## 비정질실리콘 박막 트랜지스터

허창우\*

### Hydrogenated a-Si TFT Using Ferroelectrics

Chang-Wu Hur\*

요 약

강유전체(SrTiO<sub>3</sub>) 박막을 게이트 절연층으로 하여 수소화 된 비정질 실리콘 박막 트랜지스터를 유리 기판 위에 제조하였다. 강유전체는 기존의  $SiO_2$ , SiN 등과 같은 게이트 절연체에 비하여 유전특성이 매우 뛰어나 TFT의 ON 전류를 증가시키고 문턱전압을 낮추며 항복특성을 개선하여 준다. PECVD에 의하여 증착된 a-Si:H는 FTIR 측정 결과 2,000 cm<sup>-1</sup>과 635 cm<sup>-1</sup> 및 876 cm<sup>-1</sup>에서 흡수 밴드가 나타났으며, 2,000 cm<sup>-1</sup>과 635 cm<sup>-1</sup>은  $SiH_1$ 의 stretching과 rocking 모드에 기인한 것이며 876 cm<sup>-1</sup>의 weak 밴드는  $SiH_2$  vibration 모드에 의한 것이다. a-SiN:H는 optical bandgap이 2.61 eV이고 굴절률은  $1.8 \sim 2.0$ , 저항률은  $10^{11} \sim 10^{15}$  Q-cm 정도로 실험 조건에 따라 약간 다르게 나타난다. 강유전체(SrTiO<sub>3</sub>) 박막의 유전상수는  $60 \sim 100$  정도이고 항복전계는 1MV/cm 이상으로 우수한 절연특성을 갖고 있다. 강유전체를 이용한 TFT의 채널 길이는  $8 \sim 20~\mu$ m, 채널 넓이는  $80 \sim 200~\mu$ m로서 드레인 전류가 게이트 전압 20V에서  $3.4~\mu$ A이고  $I_{on}/I_{off}$  비는  $10^5 \sim 10^8$ ,  $V_{th}$ 는  $4 \sim 5~volts$ 이다.

#### **ABSTRACT**

In this paper, the a-Si:H TFT using ferroelectric of SrTiO<sub>3</sub> as a gate insulator is fabricated on glass. High k gate dielectric is required for on-current, threshold voltage and breakdown characteristics of TFT. Dielectric characteristics of ferroelectric are superior to SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub>. Ferroelectric increases on-current and decreases threshold voltage of TFT and also can improve breakdown characteristics. SrTiO<sub>3</sub> thin film is deposited by e-beam evaporation. Deposited films are annealed for 1 hour in N2 ambient at 150°C ~ 600°C. Dielectric constant of ferroelectric is about 60~100 and breakdown field is about 1MV/cm. In this paper, the TFT using ferroelectric consisted of double layer gate insulator to minimize the leakage current. a-SiN:H, a-Si:H (n-type a-Si:H) are deposited onto SrTiO<sub>3</sub> film to make MFNS(Metal/ferroelectric/a-SiN:H/a-Si:H) by PECVD. In this paper, TFT using ferroelectric has channel length of 8 ~ 20  $\mu$ m and channel width of 80 ~ 200  $\mu$ m. And it shows that drain current is 3.4 $\mu$ A at 20 gate voltage, I<sub>on</sub>/I<sub>off</sub> is a ratio of 10<sup>5</sup> ~ 10<sup>8</sup> and V<sub>th</sub> is 4 ~ 5 volts, respectively. In the case of TFT without having ferroelectric, it indicates that the drain current is 1.5  $\mu$ A at 20 gate voltage and V<sub>th</sub> is 5 ~ 6 volts. If properties of the ferroelectric thin film are improved, the performance of TFT using this ferroelectric thin film can be advanced.

#### 키워드

a-Si:H Thin Film Transistor, Ferroelctric (SrTiO3), Double Layer Gate Insulator

### Introduction

Today, amorphous silicon is widely used in

optical to electrical conversion device and wide area film device. Especially, it is used such as a switching device for active matrix LCD, contact

\*목원대학교 전자정보보호공학부

접수일자: 2005, 4, 14

image sensor for a-Si:H TFT and Fax, and a-Si:H solar cell. Usually, amorphous silicon TFT uses a-SiN:H as a gate insulator [1],[2]. Induced dielectric constant of a-SiN:H is 7.5. To increase a driving current of TFT, an insulator with a large of induced dielectric constant is needed. Recently, much works have advanced on TFT gate insulating layer. High k gate dielectrics are required for a-Si:H TFT structure because the conventional a-SiN:H film is too thin to minimize the threshold voltage and the leakage current. A thick layer can be used with the high k material to lower the parasitic capacitance between the gate and the source (and drain). A thick layer is used to prevent the top-to-bottom metal shortage, which is a killing factor for the yield. The high k dielectric material is usually used in combination with a high quality dielectric interface layer to lower the interface density of states. Ferroelectric thin film is suitable as gate insulator because of large dielectric constant. In this paper, we have fabricated a-Si:H TFT using gate insulator with ferrodielectric and compared their electrical characteristics with gate insulator a-SiN:H TFT used as commonly.

# II. Fabrication and Characteristics of Thin Films

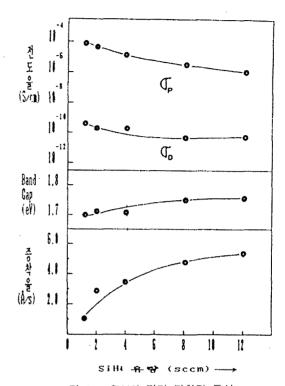

Amorphous silicon is deposited using plasma enhanced chemical vapor deposition (PECVD). At this time, electrical and optical characteristics of amorphous silicon such as conductivity, optical band gap and deposition rate are changed under deposition condition such as SiH<sub>4</sub>, flux, chamber pressure, RF power and substrate temperature. Figure 1 shows the characteristics of experimental results according to amorphous deposition condition. From the results shown in Figure 1, photo and dark conductivity are diminished according to SiH4 flux, dark conductivity is changed 10-9 ~ 10-11(S/cm), in the case of photo conductivity is varied range from 10<sup>-4</sup> to 10<sup>-6</sup> (S/cm). Also, optical band gap shows 1.7 ~ 1.8eV, as a flux of SiH<sub>4</sub> is increased, it is deposited from 1.0 to 6.9 (Å/sec). As shown in Figure 1, we can estimate the trade-off relation between conductivity and

그림 1. a-Si:H의 전기 광학적 특성 Fig 1. Electrical and optical characteristics of a-Si:H (a-Si:H properties as SiH4 flow rate).

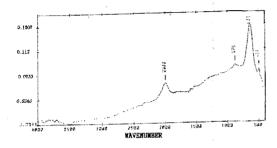

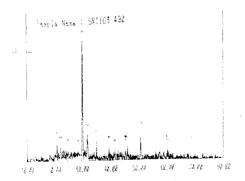

optical band gap according to a flux of SiH4 and control the optical band gap by adjusting a flux of SiH4. But, the change of conductivityand optical band gap is little according to chamber pressure condition. The deposition rate is ranged from 1.0 to 3.0 (Å/sec). Also, the change of electrical and optical characteristics is a little according to RF power. Figure 2 shows the IR spectrum result. It represents a relation between Si of a hydrogenated amorphous silicon film and bonding of H. Frequency of fundamental infrared absorption modes depends on a mass of oscillation dipole and amount of bond between elements including dipole. The a-Si:H film shows type of vibration mode, it shows SiH4 stretching mode at wave number 2000 cm<sup>-1</sup>. Also, it represents a rocking mode at wave number 635 cm<sup>-1</sup>. The bond represented at weaker bond range 800 ~ 900 cm<sup>-1</sup> depends on the vibrational mode of SiH<sub>2</sub>. Therefore, the fabricated a-SiH film in this experimental setup shows that Si-H bonding of stretching/rocking mode exists [3],[4]. The gate insulator layer and a-SiN:H film of passivation film are fabricated using PECVD by mixing SiH<sub>4</sub> gas and NH<sub>3</sub> gas. Etching rate of a-SiN:H increases and refraction diminishes as NH<sub>3</sub>/SiH<sub>4</sub> increases. Also, their characteristics are not related with RF power. The Eopt value is around 2.4 Ev [5],[6].

그림 2. a-Si:H의 FTIR 특성 Fig 2. FTIR characteristics of a-Si:H.

그림 3. SrTiO<sub>3</sub> 박막의 X-RD 측정 Fig. 3. X-RD analysis of SrTiO<sub>3</sub> thin film.

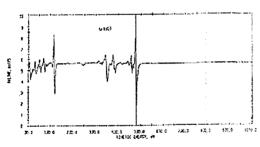

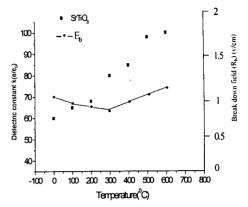

Ferroelectrics (SrTiO<sub>3</sub>) film is fabricated by E-beam evaporator. Figure 3 shows X-RD analysis of SrTiO<sub>3</sub>. The used ferroelectrics target forms ceramic type with high pressed PELLET. Dielectric constant of ferroelectric thin film is 60 ~ 100 and has high value compared with another insulator. It has a high breakdown field about 1 MV and an excellent characteristic as an insulator. Figure 4 shows dielectric constant and breakdown field of ferroelectrics (SrTiO<sub>3</sub>) as annealing temperature.

## III. Characteristics and Structure of Thin Film Transistor

그림 4. 강유전체의 유전상수와 항복 특성 Fig 4. Dielectric constant and breakdown field of ferroelectrics (SrTiO<sub>3</sub>) as annealing temperature.

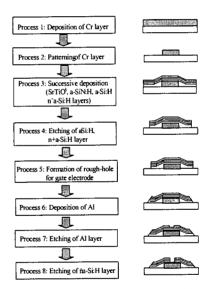

그림 5. a-Si:H TFT의 제조공정 Fig 5. Fabrication process of a-Si:H TFT.

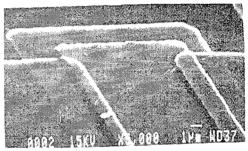

Figure 5 shows a cross-section and fabrication process of thin film transistor fabricated in this experimental setup. Figure 6 shows microscope picture of a-Si:H TFT. The gate electrode is formed by patterning with length of 8 μm~16 μm and width of 80~200 μm after depositing with gate electrode (Cr) 1000 Å under corning 7059 glass substrate. We have fabricated a-Si:H, a-Si:H and n<sup>†</sup>a-Si:H samples on gate electrode in sequence and ferroelectric (SrTiO<sub>3</sub>), a-Si:H and n<sup>†</sup>a-Si:H samples, respectively. The thickness of these thin films is formed with SrTiO<sub>3</sub> (2000 Å),

그림 6. a-Si:H TFT의 공정별 현미경 사진 Fig 6. Microscope picture of a-Si:H TFT.

a-SiN:H (3000 Å), a-Si:H(2000 Å) and n<sup>+</sup>a-Si:H (500 Å). We have used a RIE (Reactive Ion Etching) method to etch after forming a-Si:H pattern of channel layer. RIE equipment is used RI mode of PECVD. After hole pattern is formed, a-Si:N:H is conducted RIE and the used gas is used by mixing CHF<sub>3</sub> and O<sub>3</sub>. Ferroelectric (SrTiO<sub>3</sub>) is mixed with HF:DI at a rate of 1:5 and etched by dipping with 17 seconds. To form a source drain electrode, the film is patterned after depositioning 4000 Å of Al by

그림 7. 강유전체의 X-RD Fig 7. X-RD analysis of ferroelectrics (SrTiO<sub>3</sub>).

E-beam evaporator. Finally,  $n^{\dagger}a$ -Si:H is conducted by RIE using CF +  $O_2$  and gas for S/D metal pattern. To compensate a damage by RIE process, the  $n^{\dagger}a$ -Si:H is annealed at temperature 200 °C in vacuum state. To test characteristics of fabricated sample, we have gained an I-V,  $V_{th}$  and  $I_{on}/I_{off}$  characteristics by using probe station and HP4145B parameter analyzer. Figure 7 shows X-RD analysis of ferroelectrics(SrTiO<sub>3</sub>). Figure 8 shows SEM picture of a-Si:H TFT.

그림 8 a-Si:H TFT의 SEM 사진 Fig 8. SEM picture of a-Si:H TFT.

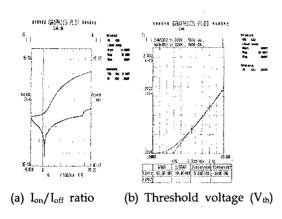

We have annealed for 1 hour at a temperature 200 ℃ to compensate damage by RIE process. To measure the electrical characteristics of the fabricated samples, we obtained characteristics of I-V, Vth and Ion/Ioff by using probe station and 4145A parameter measurement equipment. As shown in Figure 9, the saturation current at gate voltage 20 volts without having ferroelectric TFT is 1.4  $\mu$ A,  $I_{on}/I_{off}$  is  $10^3$  and  $V_{th}$  is 5.6 volts. In the case of TFT with ferroelectric gate insulator layer as shown in Figure 10, saturation current at gate voltage 20 volts is 3.4µA, Vth is 4.5 volts and I<sub>on</sub>/I<sub>off</sub> gives a values range from 10<sup>5</sup> to 10<sup>6</sup>. We have estimated that the leakage current of TFT with ferroelectric layer is smaller than that of without ferroelectric layer. That is to say, the Vth of the TFT with two layers using ferroelectric and a-SiN:H compared with TFT of gate insulator with a-SiN:H layer shows a small value and has 1 volts.  $I_{on}/I_{off}$  has  $10^2 \sim 10^3$  order value. Its I-V current has a 1.5µA times in the same gate and drain volts. From the results, we can estimate that the ferroelectric layer employing two layers gate insulator has good quality insulator characteristics. It enhanced good elec-

(c) I-V curve 그림 9. a-Si:H TFT의 전기적 특성 Fig 9. Electrical Characteristics of a Si:H TFT Without Ferroelectric.

trical characteristics. Also, the leakage current can be diminished using two layers insulator.

### IV. Conclusions

From the experimental results, the TFT with ferroelectric has a higher value of I<sub>on</sub>/I<sub>off</sub> compared with TFT having a gate insulator employing a-SiN:H. In the case of I<sub>off</sub> current, leakage current between source and gate by using two layers gate insulator (SrTiO<sub>3</sub>/a-SiN:H) reduces, pin hole employing gate insulator with one layer is more larger than two layer gate insulator. The probability of generation of pinhole by using two layer is more smaller. Also, I<sub>on</sub> current increases as dielectric constant of gate insulator increases. This effect gives the increase of I<sub>on</sub>/I<sub>off</sub>. As dielectric constant increases, V<sub>th</sub> get smaller 1 volts value. The channel is formed in

(c) I-V curve 그림 10. a~Si:H TFT의 전기적 특성 Fig 10. Electrical Characteristics of a Si:H TFT With Ferroelectric.

small gate voltage. From the I-V curve, we can estimate that drain current of TFT with  $SrTiO_3$  at same gate voltage increases over  $1.5~\mu A$ . And, leakage current between gate and source is much smaller. Under the voltage stress condition, TFT with ferroelectric compared to thin film has no influence on the voltage stress condition. From the results, we can estimate that TFT with ferroelectric has no interface trap. These phenomena give good results. Ferroelectric thin film can be applicable to TFT application such as HDTV display device.

### References

- [1] Michael Hack, "Physical models for amorphous-silicon TFT and their implementation in a circuit simulation program", IEEE ED., pp.2764-2769, Dec, 1989.

- [2] M. J. Powell, "The physics of a-Si TFT", IEEE Trans. El. Dev. 36(12) 1989, pp.2753-2763.

- [3] R. A. Street, "HDOS model a-Si and alloys",

- MRS Symp. Proc. 219, 1991, pp.253-258.

- [4] S. J. Jones, R. Crucet, X. Deng, J. Doehler, R. Kopf, A. Myatt and M. Izu, "Use of a gas jet technique to prepare microcrystalline silicon based solar cells at high i-layer deposition rates", in Amorphous and Heterogeneous Silicon Thin Films—Fundamentals to Devices, ed. By H. Branz, R. W. Collins, H. Okamoto, S. Guha, and R. Schropp, MRS Symp. Proc. 557, 567 (1999).

- [5] X. Liao, H. Povolny, S. Han and X. Deng, "Raman and IR study of narrow bandgap a-SiGe and mc-SiGe films deposited under different hydrogen dilution" to be submitted to J. of Non-Cryst. Solids, 2001.

- [6] X. Liao, H. Povolny, P. Agarwal and X. Deng," Raman and IR Study of Narrow Bandgap a-SiGe and mc-SiGe Films Deposited Using Different Hydrogen Dilution", to be published in Proc. of IEEE 29th Pho-

tovoltaic Specialist Conference, 2002.

## 저자소개 허창우(Change-Wu Hur)

received his B.S.degree in Electronic Engineering from Kwangwoon University in 1982 and M.S. and Ph.D.

degrees in Electrical and Electronic Engineering from the Yonsei University in 1984 and 1991, respectively. From 1986 to 1994, he joined at LG Research Center, where he worked as Senior Member of Technical Staff. In 1994, he joined the department of Electronic and Information security Engineering, Mokwon University, Korea, where he is presently a professor. His research interest is in the area of VLSI and Display that includes ASIC design, Display technology and Wireless Communication design.