# The jitter and phase noise caused by 1/f noise of MOSFET in 2.75 GHz CMOS ring oscillator

#### Se Hoon Park<sup>†</sup>

#### Abstract

It has been known that 1/f noise of MOSFET is generated by superposition of random telelgraph signals (RTS). In this study, jitters and phase noise caused by 1/f noise of MOSFET are analysed with RTS supplied to all of the nodes of the CMOS ring oscillator under investigation. Through the analysis of jitters and jitter ratios with varying values of the amplitude of RTS, it is found that the jitters and the jitter ratios are proportional to the amplitude of RTS. And the analysis of FFT of the output of the ring oscillator reveals that the jitters are closely related to the phase noise of the high order harmonics of the ring oscillator outputs.

Key Words: 1/f nose, jitter, phase noise, random telegraph signal, ring oscillator

#### 1. Introduction

As CMOS technology develops to deep submicron gate length regime of 90 nm these days, 1/f noise is getting attentions in the applications of the image sensors and RF circuits. These circuits have been known to be very sensitive to 1/f noise.

1/f noise is a generic noise of MOSFET and its effect on systems is getting serious as more systems are integrated into a chip. 1/f noise in analog systems, for example, causes the phase noise in the oscillation circuits and the jitters in the high frequency digital circuits. This paper analyses the jitter and phase noise caused by 1/f noise in the CMOS ring oscillator.

Section II explains the origin of 1/f noise in MOS-FET's, the random telegraph signal (RTS) and the superposition of RTS to make 1/f noise. Section III explains how RTS is added into the ring oscillator to simulate 1/f noise in the devices. Section IV discusses the definition of the jitters and the simulation results revealing the close relationship of the jitter with the phase noise on the high order harmonics. Section V concludes this study.

Electronic Engineering. Andong National University

<sup>†</sup>Corresponding author: separk@andong.ac.kr

(Received: November 17, 2004, Accepted: December 1, 2004)

#### 2. 1/f Noise of MOSFET

The interface between the gate oxide and the substrate is the most important part for the performance of MOSFET. The density of the interface states between the gate oxide and the substrate is directly related to the threshold voltage of MOSFET. The density of the interface states today is in the range of  $10^8 \sim 10^{10}$  cm<sup>2</sup> eV<sup>-1</sup> which is low enough to minimize any effects on device but is still the cause of generic 1/f noise.

It is known that 1/f noise of MOSFET is generated as results of the generation and recombination between the channel carriers and the energy states close to the interface of the gate oxide and Si<sup>[1]</sup>. The change of the number of carriers in the channel due to the generation and recombination causes the fluctuation of the channel conductivity resulting in the generation of 1/f noise. The 1/f noise is named after the property that the power spectral density of noise due to the change of the number of carriers is inversely proportional to the frequency.

Ralls and coworkers investigated the variation of drain current due to the change of occupancy of the interface states between the gate oxide and the substrate in a MOSFET of size of  $0.1 \, \mu m \times 1.0 \, \mu m$  by adjusting the gate voltage<sup>[2]</sup>. This variation of the drain current is called the random telegraph signal (RTS)<sup>[2]</sup>. In other words, the variation of the drain current resulting from

the recombination and generation between single interface energy state and single carrier becomes RTS in time domain.

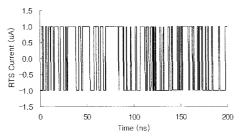

Uren and coworkers showed that 1/f noise is a result of the superposition of RTS's generated by the recombination and generation between single interface energy state and single carrier<sup>[3]</sup>. The RTS of MOSFET is the result of a sequential occurrence of capture of a carrier by an interface energy state and emission of a carrier from the energy state. The capture time constant corresponds to the time constant for the decrease of a carrier and the emission time constant corresponds to that for the increase of a carrier in the channel. In Fig. 1, the time interval of the high value corresponds to the capture time constant and the time interval of the low value does to the emission time. It is known that the time constants of the capture and the emission have the exponential distribution<sup>[1]</sup>.

Fig. 1. A piece wise linear model of the RTS signal with the pulse width of the exponential distribution.

In this study, the jitter and phase noise due to 1/f noise are analysed in the ring oscillator with 10 RTS's at each node. The exponentially distributed random numbers for the time constants are generated first and then they are used in the expression of a piece wise linear (PWL) current source of SPICE. The amplitudes of RTS are in the range of 2 to  $10\,\mu\text{A}$  and the average pulse width is  $10\,\text{nsec}$ .

# 3. Ring Oscillator

The ring oscillator is used as a basic oscillator in many digital and telecommunication systems. In the clock recovery circuits<sup>[4-6]</sup>, the disc drivers<sup>[7,8]</sup>, and the frequency synthesizers<sup>[9,10]</sup>, the ring oscillator is used as a voltage controlled oscillator (VCO). The digital systems operating in high frequencies above 1 GHz require

the quite rigorous specification for jitters. It is, therefore, important to have a good insight into the mechanism of jitter generation.

There are many sources for jitters, Among them, the power supply noise is the most dominant one<sup>[11]</sup>. Other than that, the thermal and 1/f noises contribute the jitters. The thermal noise is also called the white noise. Although the thermal noise affects a quite broad range of frequencies covering the entire operating frequencies, the power spectral density (PSD) is not so high that the thermal noise is not considered seriously compared with 1/f noise. The 1/f noise, however, has a relatively high PSD compared to the thermal noise in the low frequency ranges. As a result, the 1/f noise is considered as an important source of the jitter or the phase noise.

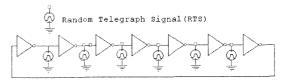

Fig. 2. shows the 7-stage CMOS ring oscillator used in this study. To model the RTS's of MOSFET, every node has 10 RTS's connected in parallel. TSMC 0.18 μm CMOS technology is used and the fundamental frequency of the ring oscillator is 2.75 GHz.

Fig. 2. Ring oscillator with 10 parallel RTS current noise sources at each of 7 nodes.

#### 4. Simulation Results and Discussion

The jitter is the time deviation of the transition time of a signal from a reference time. Jitters make the speed of systems slow by the increased setup time for timing security. In this study, the jitters caused solely by the 1/f noise is investigated with other sources of jitter eliminated.

There are two jitters depending on how to define them, such as the cycle jitter and the cycle to cycle jitter [11]. The cycle jitter is the root mean square (RMS) of the difference between the average period and the individual period over a specified time interval. The second jitter, the cycle to cycle jitter, is the RMS of the difference between two neighboring periods. The cycle jitter represents the period deviation in a long time interval but the cycle to cycle jitter represents that in a short time interval.

44 Se Hoon Park

The cycle jitter is defined as follows. The nth transition time of the output of the ring oscillator crossing  $V_{DD}/2$  is defined as  $t_n$  where  $V_{DD}$  is the power supply voltage. Then the period,  $T_n$ , is defined as follows.

$$T_n = t_{n+1} - t_n \tag{1}$$

Defining the reference period,  $\overline{T}$ , as the average of periods over an interval, the difference between  $T_n$  and  $\overline{T}$  becomes an individual jitter. As the average of individual periods over the interval becomes null, it is not used for estimating the amount of jitters. For more meaningful definition, the RMS of individual jitters is used. As a result, the first jitter, cycle jitter,  $\Delta T_c$ , is defined as follows.

$$\Delta T_c = \lim_{N \to \infty} \sqrt{\frac{1}{N} \sum_{n=1}^{N} \Delta T_n^2}$$

(2)

where N is the number of periods.

The second jitter, cycle to cycle jitter,  $\Delta T_{cc}$ , is the RMS of the difference of neighboring periods as following.

$$\Delta T_{cc} = \lim_{N \to \infty} \sqrt{\frac{1}{N} \sum_{n=1}^{N} (T_{n+1} - T_n)^2}$$

(3)

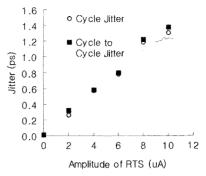

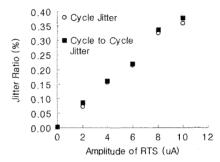

Fig. 3 shows the jitters and the jitter ratios as the amplitude of RTS varies from 0 to  $10 \,\mu\text{A}$ . The jitter ratio is the relative value of the jitter with respect to the average period as given by

Jitter Ratio =

$$\frac{\Delta T_c (\text{or } \Delta T_{\infty})}{\overline{T}}$$

(4)

As shown in Fig. 3, the jitter and the jitter ratio are proportional to the RTS amplitude as expected. And the difference between the values of the cycle jitter and the cycle to cycle jitter is small enough to be neglected. Table 1 lists the slopes of graphs of Fig. 3 calculated by the interpolation method. In the case of the cycle jitter, the jitter increases at the rate of  $1.36 \times 10^{-13}$  sec per unit  $\mu A$  of the RTS amplitude while the jitter ratio increases at the rate of  $3.72 \times 10^{-4}$  sec/sec per unit  $\mu A$  of the RTS. For the cycle to cycle jitter, similar results are obtained.

The analyses of Fig. 3 and Table 1 show that as the RTS amplitude increases, the fluctuation of charges at a corresponding node results in the linearly increased jitter and jitter ratio. Another thing to note is that the jitter increases 240 times while the change of the oscilla-

(a) Jitter vs. RTS amplitude

(b) Jitter Ratio vs. RTS amplitude

Fig. 3. Variations of (a) jitter and (b) jitter ratio as a function of amplitude of RTS.

Table 1. The slopes of the jitter and the jitter ratio graphs (Fig. 3)

|   | -   | Cycle Jitter           |                       | Cycle to Cycle Jitter  |                       |

|---|-----|------------------------|-----------------------|------------------------|-----------------------|

| - |     | Jitter                 | Jitter Ratio          | Jitter                 | Jitter Ratio          |

|   |     | (s/µA)                 | (1/μA)                | (s/µA)                 | (1/μA)                |

|   | 기울기 | 1.36×10 <sup>-13</sup> | 3.72×10 <sup>-4</sup> | $1.39 \times 10^{-13}$ | $3.83 \times 10^{-4}$ |

tion frequency of the ring oscillator is only 0.24 % of the fundamental frequency, 2.75 GHz, over the variation of RTS amplitudes from 0 to 10  $\mu$ A. These observations summerize that the jitters are directly related to RTS amplitude with the fundamental frequency of the ring oscillator at a fixed value.

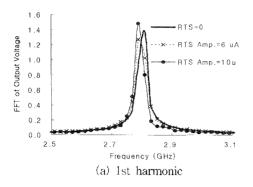

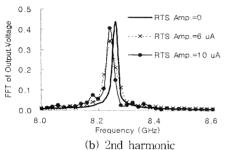

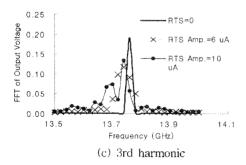

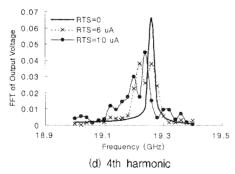

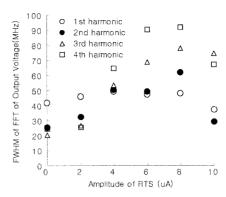

Fast Fourier Transform (FFT) is performed to analyze the effects of RTS in the frequency domain. Fig. 4 shows the phase noises of first four harmonics with the amplitude of RTS as a parameter.

The phase noises of harmonics except the first harmonic increase as the amplitude of RTS increases. In Fig. 4(a), the first harmonic shows little increase of phase noise with increasing amplitude of RTS. On the

Fig. 4. The variation of phase noises of the output of the ring oscillator as a function of the amplitude of RTS.

second, third, and forth harmonics, however, the bandwidths of FFT of the output signals increase with increase of the amplitude of RTS as shown in Fig. 4(b),

Fig. 5. The variation of the FWHM in FFT of the output of the ring oscillator as a function of the amplitude of RTS with each harmonic as a parameter.

(c), and (d). Above  $6\,\mu A$  of the amplitude of RTS, the peak frequencies of all of the harmonics except the first one break into two peak frequencies.

The full width of half maximum(FWHM) of the phase noise well represents the amount of the phase noise. Fig. 5 shows that FWHM of harmonics increases with the increase of the amplitude of RTS until the peak frequencies of harmonics break into two peak frequencies. It has been already observed that in the time domain, the jitters increase linearly with the increase of the amplitude of RTS. It is noteworthy that the linearly increased jitters correspond to the increase of FWHM of the phase noises or the split of the peak frequency of a harmonic into two frequencies. These facts confirm that the jitter of the ring oscillator in the time domain is caused by the increased phase noise of high order harmonics or the split of frequencies of high order harmonics.

## 5. Conclusions

Jitters and phase noise have been analysed using the 2.75 GHz CMOS ring oscillator each node of which is supplied with 10 RTS's that model 1/f noise by superposition. The amplitude of RTS, which has the exponentially distributed pulse width, ranges from 0 to 10  $\mu$ A. As the amplitude of RTS increases, the cycle jitter increases linearly at the rate of  $1.36 \times 10^{-13}$  s/ $\mu$ A and the cycle to cycle jitter at the rate of  $1.39 \times 10^{-13}$  s/ $\mu$ A. FFT analysis confirms that the jitter due to the 1/f noise is closely related to the broadened bandwidth of high order harmonics and the split of the peaks of the high

46 Se Hoon Park

order harmonics as the amplitude of RTS increases up to  $10\,\mu\text{A}$ .

## Acknowledgments

This study was supported in part by 2003 Research Fund of the Andong National University.

### References

- [1] M. J. Kirton, M. J. Uren, S. Collins, M. Schulz, A. Karmann, and K. Scheffer, "Individual defects at the Si:SiO<sub>2</sub> interface", *Semicond. Sci. Technol.*, vol. 4, pp. 1116, 1989.

- [2] K. S. Ralls, W. J. Skocpol, L. D. Jackel, R. E. Howard, L. A. Fetter, R. W. Epworth, and D. M. Tennant, "Discrete Resistance Switching in Submicrometer Silicon Inversion Layers: Individual Interface Traps and Low-Frequency (1/f) Noise", Phys. Rev. Lett., vol. 52, pp. 228, Jan. 1984.

- [3] M. J. Uren, D. J. Day, and M. J. Kirton, "1/f and random telegraph noise in silicon metal-oxide-semiconductor field-effect transistors", *Apply. Phys. Lett.*, vol. 47, pp. 1195, Dec. 1985.

- [4] L. DeVito, J. Newton, R. Croughwell, J. Bulzacchelli, and F. Benkley, "A 52 and 155 MHz clock-recovery PLL", ISSCC Dig. Tech. Papers, p. 142, Feb. 1991.

- [5] A. W. Buchwald, K. W. Martin, A. K. Oki, and K. W. Kobayashi, "A 6 GHz integrated phase-locked loop using AlCaAs/Ga/As heterojunction bipolar transistors", *IEEE J. Solid-State Circuits*, vol. 27, pp. 1752, Dec. 1992.

- [6] B. Lai and R. C. Walker, "A monolithic 622 Mb/s clock extraction data retiming circuits", *ISSCC Dig. Tech. Papers*, pp. 144, Feb. 1993.

- [7] W. D. Llewellyn, M. M. H. Wong, G. W. Tiets, and P. A. Tucci, "A 33 Mbit/s data synchronizing phaselocked loop circuit", *ISSCC Dig. Tech. Papers*, pp. 12, Feb. 1988.

- [8] M. Negahban, R. Behrasi, G. Tsang, H. Abouhossein, and G. Bouchays, "A two-chip CMOS read channel for hard-disk drives", ISSCC Dig. Tech. Papers, pp. 216, Feb. 1993.

- [9] I. A. Young, J. K. Greason, J. E. Smith, and K. L. Wong, "A PLL clock generator with 5-110 MHz lock range for microprocessors", *ISSCC Dig. Tech. Papers*, pp. 50, Feb. 1992.

- [10] M. Horowitz, A. Chen, J. Cobrunson, J. Gasbarro, T. Lee, W. Leung, W. Richardson, T. Thrush, and Y. Fujii, "PLL design for a 500 Mb/s interface", ISSCC Dig. Tech. Papers, pp. 160, Feb. 1993.

- [11] F. Herezel and Behzad Razavi, "A Study of Oscillator Jitter Due to Supply and Substrate Noise", *IEEE Trans. Circuits and Systems*, vol. 46, no. 1, pp. 56, Jan. 1999.

#### 박 세 훈 (차 世 熏)

- 1980년 경북대학교 전자공학 학사

- 1982년 경북대학교 전자공학 석사

- 1983 ~ 1986년 현대전자 반도체 사업부

- 1992 미국 아리조나 주립대학 공학박사

- 1993 ~ 1995년 한국 전자 통신 연구원 반도체 연구소

- 2004년 현재 안동대학교 전자공학과 부교수