# 3-레벨 반브리지 인버터로 구성된 새로운 UPFC의 동특성 분석

論文

53P-3-3

# Dynamic Characteristic Analysis of Novel Unified Power Flow Controller Using 3-Level Half-Bridge Inverter Modules

白承澤<sup>†</sup>・蘇龍哲<sup>\*</sup>・韓炳文<sup>\*\*</sup> (Seung-Taek Baek・Yong-Chul Soh・Byung-Moon Han)

**Abstract** - This paper proposes a novel UPFC based on 3-level Half-bridge modules, isolated through single-phase multi-winding transformers. The dynamic performance of proposed system was analyzed by simulation with EMTDC, assuming that the UPFC is connected with the 138-kV transmission line of one-machine-infinite-bus power system. The proposed system can be directly connected to the transmission line without series injection transformers. It has flexibility in expanding the operation voltage by increasing the number of 3-level Half-bridge modules.

Key Words: UPFC, H-bridge modules, Multi-bridge, STATCOM, SSSC

#### 1. 서 론

GTO를 이용한 전압원인버터식 FACTS 기기인 UPFC는 전력계통의 조류제어, 과도안정도, 저주파공진감쇠등에 탁월한 효과가 기대되어 선진국에서 많은 연구가 진행되고 있다.[1] 현재 개발된 UPFC의 직류전압은 대략 20kV이고 이 것은 전력계통의 동작전압보다 훨씬 낮은 전압이다. 이는 전력용 반도체 기술의 제약 때문이다. 실제 적용 가능한 GTO의 최대정격은 약 6000V이다.

UPFC의 직류링크전압을 증가시키기 위해서 GTO 소자의 직렬운용 기법이 개발되었다. 하지만 GTO 소자의 직렬운용 은 대단히 난이하고 직렬운용이 가능한 소자 수에도 많은 제약이 따른다. 따라서 전력계통과 원만한 결합을 위해 강 압변압기를 사용하는 것이 보편적이다.[2]

소자의 직렬운용을 피하고 시스템의 동작전압을 높이기위해서 다중레벨 인버터가 제안되었다.[3] 그러나 다중레벨인버터는 출력전압의 형성이 복잡하고 많은 역결합 다이오드를 필요로 한다. 이러한 단점을 보완하고자 Peng은 한 상당 5개의 단상 풀브리지로 구성한 다중브리지 STATCOM을 제안하고 그 동작과 성능을 축소모형을 통한 실험으로 분석하였다.[4,5] 한 상당 6개의 단상 풀브리지와 3개의 3레벨 풀브리지로 구성된 두 가지 형태의 SSSC를 저자가 제안한 바 있다.[6,7] 이 시스템은 직렬주입변압기 없이 동작이가능하고 인버터 모듈의 수를 추가함으로써 동작전압을 유연하게 확장할 수 있다.

본 논문은 단상 다중변압기로 절연된 3-레벨 반브리지를

이용한 새로운 UPFC를 제안하고 제안한 시스템의 동특성을 EMTDC 시뮬레이션을 통해서 검증하였다. 제안하는 시스템은 직렬 주입용 변압기 없이 선로에 직접결합이 가능하다.

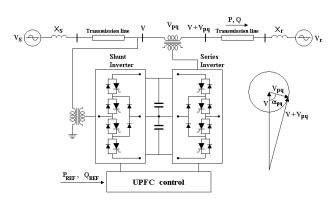

#### 2. UPFC

UPFC는 그림 1에 나타낸 것처럼 두 개의 3-레벨 인버터가 직류링크 캐패시터를 통해서 병렬로 연결된 구조로 되어 있다. 네 개의 모듈로 구성된 3-레벨 인버터가 위상 제어 변압기를 통해서 병렬로 연결되어 있다. 출력전압은 저차고조파를 제거하기 위해서 다중펄스 형태로 형성이 된다. 각 모듈은 12개의 GTO 스위치로 구성되어 있고 또한 각스위치들은 반도체 스위치의 낮은 내압으로 인해서 여러 개의 GTO 스위치가 직렬로 연결된 구조로 되어 있다. UPFC의 구조는 STATCOM과 SSSC가 직류링크 캐패시터를 공유한 형태로 구성된다. 따라서 UPFC는 선로의 유·무효전력을 직접 제어하는 기능이 있다.

UPFC의 병렬인버터는 두 가지 기능을 가지고 있다. 하나는 직류링크 캐패시터를 통해서 직렬인버터에서 요구되는 유효전력을 공급하는 것이다. 이것은 직렬인버터 출력전압의 변동을 최소화하기 위해서 직류링크전압을 일정하게 유지하는 기능이다. 다른 기능은 무효전류를 제어함으로써 연결점의 전압안정도를 향상시키는 것이다.

직렬인버터의 기능은 임의의 크기와 위상을 갖는 전압을 선로에 주입함으로써 독립적으로 유·무효전력을 제어하는 것이다. 직렬인버터의 주입전압은 전력계통에 대해 주파수는 같고 적절한 크기와 위상각을 가진다. 직렬인버터의 주입전압의 위상각은 인버터의 점호각  $\alpha_{pq}$ 에 의해 결정되는데  $0<\alpha_{pq}<2\pi$ 인 범위 내에서 임의로 조정 가능하다. 또한 주입전압의 크기  $V_{pq}$ 는 DC 링크전압의 크기를 제어하거나  $V_{pq}$ 의 최대치 범위 내에서 직렬인버터의 출력전압의 소호각  $\gamma$

接受日字: 2004年 3月 17日 最終完了: 2004年 8月 4日

<sup>\*</sup> 교신저자, 正會員: 明知大 차세대전력기술연구센터 연구원・工博

E-mail: inverter@mju.ac.kr

<sup>\*</sup> 正 會 員:京畿工業大 컴퓨터응용제어과 教授・工博

<sup>\*\*\*</sup> 正 會 員:明知大 工大 電氣工學科 教授・工博

를 제어함으로써 조절된다. 계산된 주입전압  $V_{pq}$ 는 직렬로 결합된 변압기에 의해 송전단 전압 V에 벡터적으로 합해져 수전단 전압  $V+V_{pq}$ 를 생성한다.

그림 1 UPFC의 시스템 구성

Fig. 1 System configuration of UPFC

#### 3. 제안하는 UPFC

여러 개의 3-레벨 인버터를 병렬로 연결한 구조를 갖는 기존의 UPFC는 저차 고조파를 제거하기 위해서 PAM(Pulse Amplitude Modulation) 방식으로 동작한다. 인버터는 각각 12개의 GTO 소자로 구성되어 있고 스위치는 여러 개의 GTO를 직렬로 연결한 구조로 되어 있다. GTO 소자의 직렬운용은 이미 알려진 방식이지만 허용가능한 소자수에는 아직도 제약이 따른다. 이러한 제약으로 인해서 UPFC의 직류링크 전압을 20kV 이상 높일 수가 없다.

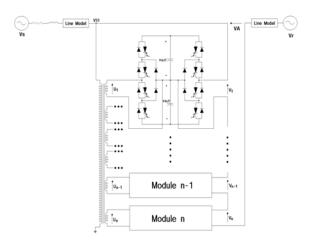

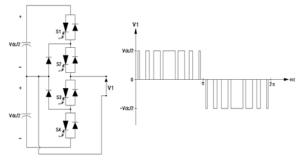

본 논문에서는 그림 2에 나타낸 것처럼 상당 여러 쌍의 3-레벨 반브리지 모듈로 구성되어 있는 새로운 UPFC를 제안한다. 각 쌍은 직류링크 캐패시터를 통해서 두개의 3-레벨 반브리지 모듈이 병렬로 연결된 구조로 되어 있다. 병렬측의 3-레벨 반브리지 모듈은 절연을 목적으로 하는 단상다중권선 변압기를 통해서 직렬로 연결되어 있다. 또한 직렬측의 3-레벨 반브리지 모듈은 선로에 직접 연결되어 있다.

그림 2 제안하는 UPFC의 단상회로도

Fig. 2 Configuration of novel UPFC

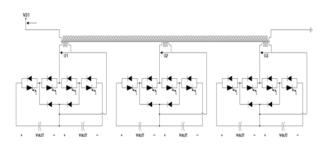

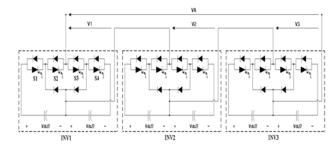

본 논문에서 제안하는 UPFC구조는 그림 2와 같이 N개의 3-레벨 반브리지 인버터로 구성되어 있는 형태이지만 시뮬레이션에서는 편의상 한 상당 세 쌍의 인버터 모듈로 구성하여 동특성을 분석하였다. 그림 3(c)와 표 1은 다중브리지인버터의 정확한 동작을 위해서 각각의 3-레벨 반브리지 인버터의 스위치가 어떠한 방식으로 동작을 해야 하는지를 보여준다. 그림 3(c)의 오른쪽 그림과 같은 출력을 발생하기위한 인버터 스위치 S1~S4의 동작은 출력전압의 크기가  $V_{cc}/2$ , 0,  $-V_{cc}/2$  인 경우로 나누어서 설명할 수 있으며 각각의 상태에 대한 스위치 동작을 표 1에 나타내었다.

표 1 다중브리지의 스위칭 방식

Table 1 Switching pattern of multi-bridge inverter

| V1        | Switching State            |  |  |  |  |

|-----------|----------------------------|--|--|--|--|

| $V_{dc}$  | S1, S2: on and S3, S4: off |  |  |  |  |

| 0         | S2, S3: on and S1, S4: off |  |  |  |  |

| $-V_{dc}$ | S3, S4: on and S1, S2: off |  |  |  |  |

(a) 병렬측 인버터

(b) 직렬측 인버터

(c) 출력전압 형성

그림 3 인버터 구조 및 스위칭 방식

Fig. 3 Inverter structure and switching pattern

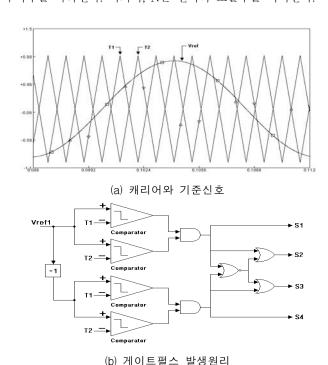

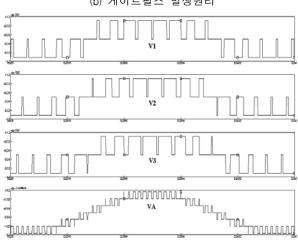

그림 4는 제안하는 UPFC의 PWM 게이트 펄스 발생원리를 나타낸 것이다. 그림 4(a)는 3-레벨 반브리지 인버터의게이트 펄스를 만들기 위한 캐리어와 기준 신호를 보여준다. 캐리어 T1, T2의 주파수는 480[Hz]이며, 서로 180°의 위상차를 가지고 있다. 그리고 기준 신호  $V_{ref}$ 의 주파수는 60[Hz]인 정현파이다. 그림 4(b)는 그림 4(a)의 신호를 가지고 어떻게 Gate 펄스를 만드는 가를 나타낸다. 그림 4(b)의원리에 의해 생성된 3-레벨 반브리지 인버터의 출력전압은절연변압기를 통해 합성된다. 다른 상의 인버터 게이트 펄스는 그림 4(a)의 기준신호가 120°의 위상차가 있는 정현파로 바뀌는 것만 빼고 모두 동일하다. 그림 4(c)는 각 인버터모듈의 출력전압과 다중브리지 인버터의 출력전압을 보여주고 있다. 각각의 인버터 모듈의 캐리어 주파수가 480Hz이므로 다중브리지 인버터의 출력전압 VA는 N\*480Hz의 스위칭주파수를 나타낸다. 여기서, N은 인버터 모듈수를 의미한다.

(c) 인버터 출력전압

그림 4 게이트 펄스 생성원리

Fig. 4 Principle of gate pulse generation

제안하는 UPFC는 각 상당 여러 개의 직류링크 캐패시터를 가지고 있다. 동일한 상에서 각 캐패시터는 서로 절연이되어 있기 때문에 평균전압보다 전압편차가 있게 된다. 직류 캐패시터의 불균등한 누설전류, 인버터의 데드타임, 과도와 외란시의 비대칭동작 등과 같은 다양한 원인에 의해 직류전압의 불평형이 발생하게 된다. 직류전압을 평형하게 제어하므로써 인버터 출력전압의 고조파 레벨을 감소시킬 수가 있다.

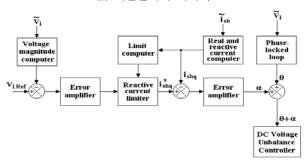

그림 5는 직류 캐패시터의 직류전압 불평형제어기를 나타 낸 것이다. 각 상을 분리제어하기 때문에 시뮬레이션 편의 상 제안하는 UPFC는 세 개의 직류전압 불평형제어기로 구 성된다.

그림 5 직류전압 불평형 제어기 Fig. 5 DC voltage unbalance controller

#### 4. EMTDC 시뮬레이션

제안하는 UPFC의 동특성을 분석하기 위해서 EMTDC 시뮬레이션을 실시하였다. 시뮬레이션에서 사용된 회로정수를 표 2에 나타내었다.

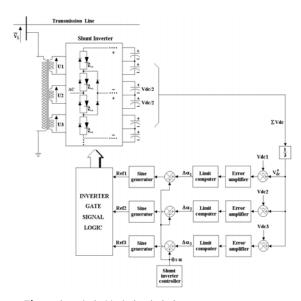

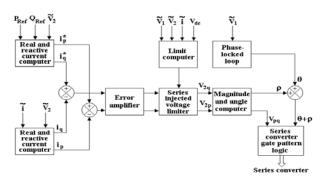

그림 6은 시뮬레이션에서 사용된 UPFC 제어기의 구조를 보여주고 있다. 그림 6(a)와 6(b)는 자동조류제어를 수행하는 직렬인버터와 병렬인버터의 제어기를 나타낸 것이다. 정상 대시 직류 신호로 나타나는 제어량을 이용하여 선로전류를 조절하는 벡터제어로 자동조류제어를 수행한다. 기준유・무효전력 성분인 iq\*와 ix\*는 유구되는 유・무효전력인 Pref와 Qref로 결정이 된다. 이 기준 성분은 측정된 선로전류의 ip와 iq 성분과 비교되고 직렬인버터 출력전압의 크기와위상각을 결정하는  $V_{pq}$ 와 ρ를 생성한다. 병렬인버터의 제어기에서 출력전압의 크기는 직류전압의 크기에 의존하고 출력전압의 위상각만을 제어한다. 제어기의 외부제어루프는 선로측 모선단 전압을 조절하고 또한 직류전압을 제어한다. 요구되는 무효분을 보상하는데 필요한 값으로 직류전압이 형성될 때까지 외부제어기는 선로측 모선단 전압에 대해서인버터 출력전압의 위상각 α를 가변한다.

#### 표 2 시뮬레이션 회로정수

Table 2 Simulation parameter

| Base 전압 | 112.676kV      |  |  |

|---------|----------------|--|--|

| Base 전류 | 946A           |  |  |

| 송수전단 전압 | 138kV          |  |  |

| 위상각     | 20°            |  |  |

| 선로모형 1  | 1.0053Ω        |  |  |

| 인도도명 I  | 19.73mH        |  |  |

| 선로모형 2  | $3.0159\Omega$ |  |  |

| 신도도정 2  | 59.19mH        |  |  |

| 직류캐패시터  | 1000μF         |  |  |

(a) 직렬인버터 제어기

(b) 병렬인버터 제어기

그림 6 UPFC 제어기

Fig. 6 Block diagram of UPFC controller

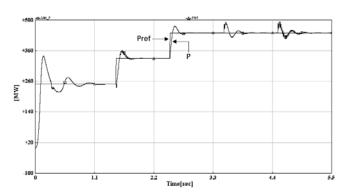

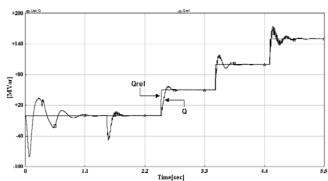

시뮬레이션에서 고려된 시나리오를 표 3에 나타내었다. 총 시뮬레이션 진행시간은 5.5초로 설정하였다. 유효전력 P의 기준값은 초기에 250[MW]로 설정하였고, 표 3에 나타낸 것처럼 1.5초, 2.5초, 3.5초에 기준값을 변경하였다. 무효전력 Q의 기준값은 초기에 0[MVar]로 설정하였고, 표 3에 나타낸 것처럼 2.5초, 3.5초, 4.5초에 기준값을 변경하였다. 유효전력과 무효전력의 기준값인  $P_{ref}$ 와  $Q_{ref}$ 를 스텝 변화시킴으로써 제안하는 UPFC의 동특성을 확인하였다.

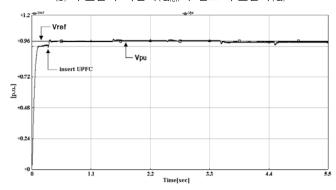

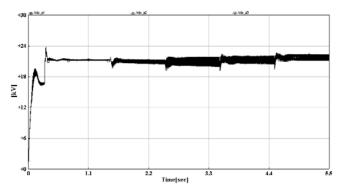

그림 7은 제안하는 UPFC의 시뮬레이션 결과를 나타낸 것이다. 그림 7(a)와 7(b)는 선로 P와 Q의 기준값을 스텝변화 시켰을 때 UPFC의 추종성능을 보여주고 있다. 기준값 Pref와 Qref에 따라 송전선로에 직렬인버터가 적정한 전압을 주입하므로써 선로의 P, Q가 변화됨을 알 수가 있다. 그림 7(c)는 병렬인버터의 동작에 의해 모선단 전압이 일정하게 유지되고 있음을 보여주고 있다. 그림 7(d)는 A상의 직류링크전압을 나타낸 것이다. 인버터의 PWM 동작으로 인한 직

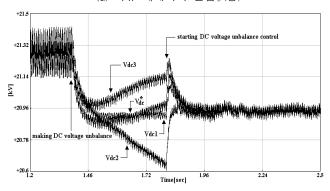

류전압의 편차 존재하기는 하지만 각 캐페시터의 전압이 평형을 이루고 있음을 알 수가 있다. 그림 7(e)는 불평형제어기가 동작이 될 때 직류링크전압 Vdc1, Vdc2, Vdc3와 평균직류링크전압  $V_{dc}^*$ 의 변화를 나타낸 것이다. 각 캐페시터가초기에 평형을 이룬다고 가정하고 1.4초에 갑자기 불평형을 발생시킨다. 전압 불평형제어기가 1.8초에 동작이 되면 각 캐페시터의 전압이 평형을 이루고 있음을 알 수가 있다.

#### 표 3 시뮬레이션 시나리오

Table 3 Simulation Scenario

| 시간(초)                   | 0~1.5 | 1.5~2.5 | 2.5~3.5 | $3.5 \sim 4.5$ | $4.5 \sim 5.5$ |

|-------------------------|-------|---------|---------|----------------|----------------|

| V <sub>ref</sub> [p.u.] | 1.0   | 1.0     | 1.0     | 1.0            | 1.0            |

| P <sub>ref</sub> [MW]   | 250   | 350     | 450     | 450            | 450            |

| Q <sub>ref</sub> [MVar] | 0     | 0       | 50      | 100            | 150            |

(a) 유효전력 기준치(P<sub>refl</sub>와 선로 유효전력(P)

(b) 무효전력 기준치(Q<sub>ref</sub>)와 선로 무효전력(Q)

(c) 모선전압 기준치(V<sub>ref</sub>)와 모선전압(V<sub>DII</sub>)

(d) 직류 캐패시터 전압(A상)

(e) 직류 캐패시터 전압(전압불평형제어)

그림 7 시뮬레이션 결과

Fig. 7 Simulation results

#### 5. 결 론

본 논문에서는 직렬주입변압기가 없는 새로운 UPFC 의 토폴로지를 제안하고 시뮬레이션을 통하여 시스템의 동특성 을 검증하였다. 제안하는 UPFC는 직렬주입변압기가 없기 때문에 시스템 규모가 작고 가격이 저렴하며 송전전압에 따라 이에 적합하도록 브리지의 수를 가감하여 융통성 있는 시스템 운용이 가능하다는 장점이 있다.

본 논문의 목적은 직렬주입변압기가 없이 송전선로에 직접 연결이 가능한 새로운 UPFC를 제안하는 것이다. 직렬변압기는 UPFC에 있어서 낮은 포화영역과 낮은 누설 임피던스를 가져야 하므로 중요한 부분을 차지한다.

본 논문에서 개발한 시뮬레이션 모델의 동특성 분석의 결과를 토대로 실 규모의 시스템 개발에 활용 가능한 기본기술을 확보할 수 있다.

### 감사의 글

본 연구는 과학기술부 및 한국과학재단의 ERC프로그램을 통한 지원으로 이루어졌으며 이에 감사를 드립니다.

#### 참 고 문 헌

[1] C. D. Schauder, L. Gyugyi, M. R. Lund, D. M.

- Hamai, T. R. Rietman, D. R. Torgerson, A. Edris, "Operation of the Unified Power Flow Controller (UPFC) under Practical Constraints," IEEE Trans. on Power Delivery, Vol. 13, No. 2, pp.630–639, April 1998.

- [2] Renz, B. A., Gyugyi, L., "AEP Unified Power Flow Controller Performance," IEEE Trans. on Power Delivery, Vol. 14, No. 4, pp.1374–1381, October 1999.

- [3] Yiqiang Chen, Mwinyiwiwa, B, Z. Wolanski, Boon-Teck Ooi, "Regulating and Equalizing DC Capacitance Voltages in Multi-level STATCOM," IEEE Trans. on Power Delivery, Vol 12, No.2, pp. 901–907, April 1997.

- [4] F. Z. Peng, J. S. Lai, "A Multilevel Voltage-Source Inverter with Separate DC Sources for Static Var Generation," IEEE/IAS Annual Meeting. pp. 2541–2548, Orlando, FL, Oct. 8–12, 1995.

- [5] F. Z. Peng, J. S. Lai, "Dynamic performance and control of a static var compensator using cascade multilevel inverter," IEEE/IAS Annual Meeting. pp.1009–1015, San Diego, CA, Oct. 6–10, 1996.

- [6] B. Han, S. Baek, H. Kim, G. Karady, "Dynamic Characteristic Analysis of SSSC Based on Multibridge Inverter", IEEE Trans. on Power Delivery, Vol. 17, No. 2, April 2002.

- [7] B. Han, S. Baek, H. Kim, "Performance analysis of SSSC based on three-level multi-bridge PWM inverter", Elsevier Science, Electric Power System Research, Vol. 61, No. 3, pp.195-202, June 2002.

# 저 자 소 개

#### 백 승 택 (白 承 澤)

1971년 11월 24일생. 1997년 명지대학교 전기공학과 졸업. 1999년 동 대학원 전기공학과 졸업(석사). 2004년 동대학원 전기공학과 졸업(공박). 현재명지대 차세대전력기술연구센터 전임연구원

Tel: 031-333-1542 Fax: 031-321-0271

E-mail: <u>inverter@mju.ac.kr</u>

#### 소 용 철 (蘇 龍 哲)

1959년 12월 12일생. 1985년 명지대 전 기공학과 졸업(학사). 1996년 동 대학원 전기공학과 졸업(공박). 현재 경기공업대 컴퓨터응용제어과 교수.

Tel: 031-4964-715 Fax: 031-4964-625

E-mail: <a href="mailto:ycsoh@kinst.ac.kr">ycsoh@kinst.ac.kr</a>

## 한 병 문 (韓 炳 文)

1953년 7월 5일생. 1976년 서울대 전기공학과 졸업. 1988년 미 아리조나주립대 대학원 전기공학과 졸업(석사). 1992년 동대학원 전기공학과 졸업(공박). 미 Westinghouse 중앙연구소 선임연구원. 현재 명지대 전기공학과 교수

Tel: 031-330-6366 Fax: 031-321-0271

E-mail: erichan@mju.ac.kr