# Optimization of Gate Stack MOSFETs with Quantization Effects

Tina Mangla\*, Amit Sehgal\*, Manoj Saxena\*\*, Subhasis Haldar\*\*\*, Mridula Gupta\*, and R. S. Gupta\*

Abstract—In this paper, an analytical model accounting for the quantum effects in MOSFETs has been developed to study the behaviour of high-k dielectrics and to calculate the threshold voltage of the device considering two dielectrics gate stack. The effect of variation in gate stack thickness and permittivity on surface potential, inversion layer charge density, threshold voltage, and  $I_D$ - $V_D$ characteristics have also been studied. This work aims at presenting a relation between the physical gate dielectric thickness, dielectric constant and substrate doping concentration to achieve targeted threshold voltage, together with minimizing the effect of gate tunneling current. The results so obtained are compared with the available simulated data and the other models available in the literature and show good agreement.

Index Terms—Quantization effects (QEs), Triangular Potential Well (TPW), Gate stack, Equivalent oxide thickness (EOT)

#### I. Introduction

The continued growth of silicon-based VLSI technology over time has led to orders of magnitude of improvement in performance, device density and cost.

Manuscript received June 28, 2004; revised September 7, 2004.

- \*Semiconductor Device Research Laboratory, Department of Electronic Science, University of Delhi South Campus, New Delhi – 110 021, India

- \*\*Department of Physics & Electronics, Deen Dayal Upadhayaya College, University of Delhi, New Delhi 110 015, India

- \*\*\*Department of Physics, Motilal Nehru College, University of Delhi, New Delhi 110 021, India E-mail: rsgu@bol.net.in

The successful scaling of MOSFETs toward shorter channel lengths requires thinner gate oxides and higher doping levels in order to achieve high drive currents and minimized short-channel effects [1-2]. Currently, for MOSFET applications, traditional SiO2 gate oxide is quickly approaching its physical scaling limit due to severe direct tunnelling leakage and poor reliability [3]. To overcome these problems, it is necessary that a suitable alternative gate oxide be developed having similar properties and could act as a replacement to traditional  $SiO_2$ . Some studies have shown that the gate tunnelling current is significantly reduced with the use of the high-k#gate dielectrics even though the barrier height decreases with the increase of gate dielectric constant [4-5]. Much effort is currently underway on alternative high-k gate dielectrics such as  $Ta_2O_5$ ,  $TiO_2$ ,  $ZrO_2$ ,  $HfO_2$ , and  $HfSi_xO_y$  [6-10]. However, most of the work so far has been mainly concentrated on material issues such as achieving a stable interface with silicon as well as the gate contact material. Very few detailed analysis of the effect of high-k dielectrics on sub-micron MOSFET performance has so far been undertaken [11], but analytical modeling is still lacking.

For these state-of-the art devices, it was demonstrated a long time ago, that as the gate oxide thickness is scaled down to 10nm and below, it can result in very large transverse electric fields (of the order of  $10^7$  - $10^8$  V/m) at the Si- $SiO_2$  interface leading to significant bending of the energy bands at the Si- $SiO_2$  interface. With that sufficient band bending, the potential well can become sufficiently narrow to quantize the motion of inversion layer carriers in the direction perpendicular to the interface and the electrons confined in the narrow potential well of an inversion layer would not behave classically [12-14]. This gives rise to a splitting of the

once continuous energy bands into discrete bands (2-D Density of states), such that the lowest of the allowed energy levels for electrons does not coincide with the bottom of the conduction band, and a shifting of the charge centroid away from the  $Si\text{-}SiO_2$  interface occurs [15-16]. Since then quantization effects (QEs) have significant influence on threshold voltage [14, 17], gate capacitance attenuation [18], current driving capability and transconductance degradation [19-20]. Extensive investigations on this issue have been carried out with both experiments and numerical calculations [21-23].

As QEs comes into picture, it is necessary to obtain self-consistent results of coupled Schrödinger's and Poisson's equations to estimate quantum inversion space charge density [13, 24]. The troublesome, fully self-consistent treatment [25, 26, 30] of the system accounts for the quantum-mechanical aspects of the MOS physics. But involves demanding numerical effort and the results, once obtained, are hard to transfer to different experimental situations, due to implicit and complex interrelation of the results to the input parameters. So, it is important to develop simple and convenient model to predict QEs on MOSFET characteristics [16, 21].

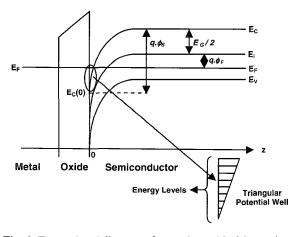

We have assumed the triangular-potential well (TPW) approximation as shown in Fig. 1; a simplest approximation, so that Schrödinger equation has an analytical solution [21, 22, 26] which is a good approximation when the device is in strong inversion.

**Fig. 1.** Energy band diagram of an n-channel MOS transistor in strong inversion. Splitting of energy levels is shown in Triangular Potential well Approximation (TPW). Energy levels  $E_{ij}$  are measured with respect to conduction band edge (Ec(0)).

Using this TPW approximation, the formulation of

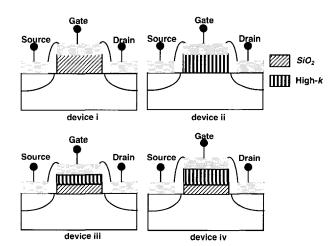

charge density is extended to develop a surface potential based model accounting for QEs using Fermi-Dirac statistics in order to offer a suitable basis for MOSFET modeling. The model can be applied to analyze QEs on inversion layer carrier density  $(N_{Inv})$  as well as on surface potential  $(\phi_S)$ . Using the analytical model, the effect of variation in gate stack (using high-k dielectric) thickness and permittivity on surface potential, inversion layer charge density, threshold voltage, and drain current; with the extension into saturation regime along with the variation of substrate doping and oxide thickness are studied. We have studied the impact of high-k dielectric using the different dielectric structured MOSFETs shown in Fig. 2. The results so obtained are compared with the available simulated data and the other models available in literature and show good agreement.

Fig. 2. Various MOSFET device structures used for analysis. *device i*: conventional  $SiO_2$  with oxide thickness of 1.5nm. *device ii*: high-k gate dielectric (k=10) with thickness 1.5nm *device iii*: Gate Stack structure with upper dielectric (k=10) and lower dielectric  $SiO_2$  (k=3.9) physical thickness of both layers 0.75nm. *device iv*: Gate Stack structure same as device iii but with an equivalent oxide thickness (EOT) of 0.75nm  $SiO_2$  for upper dielectric.

# II. QUANTUM INVERSION SPACE CHARGE DENSITY

In the effective mass approximation, if the Bloch waves are constrained to travel parallel to the interface, the three-dimensional Schrödinger's equation can be decoupled into a one-dimensional Schrödinger's equation. The envelope function normal to the interface (z

direction) is  $\xi_{ij}(z)$  for  $i^{th}$  valley and  $j^{th}$  subband and satisfies Schrödinger's equation

$$\frac{d^2 \xi_{ij}(z)}{dz^2} + \frac{2 \cdot m_{zi}}{\hbar^2} \cdot \left[ E_{ij} + q \cdot \phi(z) \right] \cdot \xi_{ij}(z) = 0 \tag{1}$$

where  $m_{zi}$  is the effective mass perpendicular to the surface,  $E_{ij}$  is the energy state of  $i^{th}$  valley (the lower and the higher) and  $j^{th}$  subband (j = 1,2,...), q is the electronic charge,  $\hbar$  is the reduced Planck constant and  $\phi(z)$  is the electrostatic potential representing the band bending at oxide-semiconductor surface satisfying the Poisson equation

$$\frac{d^2\phi(z)}{dz^2} = -\frac{\rho(z)}{\varepsilon_{si}} \tag{2}$$

where  $\varepsilon_{Si}$  is the silicon permittivity and  $\rho(z)$  is total space charge concentration given by

$$\rho(z) = q \cdot \left[ N_D^+ - N_A^- + p(z) - n(z) \right] \tag{3}$$

in which  $N_D^+$  and  $N_A^-$  are the concentrations of the ionized donors and acceptors, respectively, p(z) is the density of holes and n(z) is the density of electrons. Although in the classical calculation, electron density is given as the Boltzmann distribution, while in the quantum mechanical model, it can be expressed in terms of wave functions and energy levels determined by solving Schrödinger's equation. Summing the electron density of all the sub-bands, n(z) is given as [26]

$$n(z) = \sum_{i,j} N_{ij} \cdot \left| \xi_{ij}(z) \right|^2 = \left( \frac{k_B \cdot T}{\pi \cdot \hbar^2} \right) \cdot \sum_i n_{vi} \cdot m_{di} \sum_j \ln \left[ 1 + \exp \left( \frac{E_F - E_{ij}}{k_B \cdot T} \right) \right] \cdot \left| \xi_{ij}(z)^2 \right|$$

(4)

where  $n_{vi}$  is the degeneracy of the energy subbands,  $m_{di}$  is the density-of-states mass per valley,  $k_B$  is the Boltzmann's constant, T is the temperature,  $E_F$  is the Fermi energy and  $N_{ij}$  is the induced 2-D inversion sheet electron density for the  $j^{th}$  sub band from the  $i^{th}$  valley. The values of  $m_{zi}$ ,  $n_{vi}$ , and  $m_{di}$  are the same as those used by Stern [26] for a <100> surface and are given in Table-I.

# III. SURFACE POTENTIAL BASED MODEL

The set of equations given in the section II can be solved by the various numerical techniques, but it is complicated by the mutual dependence and the implicit coupling of the charge and potential distributions via the

Poisson and Schrödinger equations. Also it is very time consuming. And from circuit simulation point of view, together with accuracy and efficiency, model used should be as simple as possible in order to limit simulation time. As a good approximation, a triangular potential distribution at the oxide-semiconductor surface is assumed to decouple Schrödinger's equation from Poisson equation. Using triangular potential well (TPW) approximation, we replace the potential  $\phi(z)$  in equation (2) by  $-F_{S}$ .z (where  $F_{S}$  is the surface electric field) for z>0 and by an infinite barrier for z<0; [26]. Under this approximation, solution of Schrödinger's equation is represented by Eigen-functions as an Airy function solution

$$\xi_{ij}(z) = Ai \left( \left( \frac{2 \cdot m_i^{\perp} \cdot q \cdot F_s}{\hbar^2} \right)^{\frac{1}{3}} \cdot \left( z - \left( \frac{E_{ij}^0}{q \cdot F_s} \right) \right) \right)$$

(5)

and the corresponding Eigen-energy values are:

$$E_{ij}^{0} = \left(\frac{\hbar^{2}}{2 \cdot m_{i}^{\perp}}\right)^{\frac{1}{3}} \cdot \left[\frac{3}{2} \cdot \pi \cdot q \cdot F_{s} \cdot \left(j + \frac{3}{4}\right)\right]^{\frac{2}{3}} \tag{6}$$

where  $F_s = \frac{q}{\varepsilon_{si}} \cdot [N_{brv} + N_{Dep}]$  is the surface electric field (7a)

$$N_{Dep} = \sqrt{\frac{2 \cdot \varepsilon_{Si} \cdot \varepsilon_0 \cdot \phi_S \cdot N_A}{q}}$$

is the depletion charge density (7b)

and

$$N_{Inv} = \sum_{i,j} N_{i,j}$$

is the inversion charge density. (7c)

Since the depletion layer charge is due to ions, not the carriers, no quantum calculation is required for its analysis. The energy levels  $E_{ij}^0$  forming the 2-DEG inversion layer are expressed with reference to energy value Ec(0) of conduction-band edge at the  $Si\text{-}SiO_2$  interface.

i.e.

$$E_{ii} = E_{ii}^0 + Ec(0)$$

(8)

where Ec(0) is given by the relation  $Ec(0) - E_F = q \cdot \left(\frac{E_G}{2} - \phi_S + \phi_F\right)$  and is shown in Fig. 1 in

which  $E_G$  is the energy band-gap of silicon, and  $\phi_S$  is the surface potential determined by

$$V_G = V_{fb} + V_{ox} + \phi_S \tag{9}$$

where

$$V_{ox} = \frac{\varepsilon_{Si}}{C_{ox}} \cdot F_{S}$$

$V_{fb}$  is the flat-band voltage of the device.

In our work, we have analyzed the device for  $V_{fb} = n + \text{poly-}Si$  gate with substrate chosen to be uniformly doped. The poly-Si gate chosen is so heavily doped that the fermi energy level in gate is same as the conduction band.

Thus, solving equations (6) – (9) iteratively, the relation between  $N_{Inv}$  and Ec(0) -  $E_F$  is determined i.e. one can express  $N_{Inv}$  as a function of gate-to-source voltage  $(V_G)$  for a given oxide thickness  $(t_{ox})$  and substrate doping  $(N_A)$ . Furthermore this  $\phi_S$  - based model can be extended to evaluate threshold voltage  $(V_{Th})$  and drain current  $(I_D)$  of the device.

# 1. Threshold Voltage

The threshold voltage  $V_{Th}$  in MOS transistor is one of the most important parameter for circuit, device and process characterization. By definition, the conventional strong inversion condition is the surface potential  $\phi_{STh} = 2.\phi_F$ , which we say is the classical definition of threshold voltage. However, due to the inversion layer quantization effect, the electron distribution is pushed away from the surface; the conventional strong inversion condition will not be valid then. For this reason, we use the following strong inversion condition [17]:

$$\left| \frac{dQ_{lnv}}{d\phi_S} \right|_{\phi_S = \phi_{STh}} = \left| \frac{dQ_{Dep}}{d\phi_S} \right|_{\phi_S = \phi_{STh}}$$

(10a)

which in turn is equivalent to equation

$$\left| \frac{dQ_{Inv}}{dV_G} \right|_{V_G = V_{Th}} = \left| \frac{dQ_{Dep}}{dV_G} \right|_{V_G = V_{Th}}$$

(10b)

where  $Q_{Inv}$  and  $Q_{Dep}$  are the inversion layer charge and depletion layer charge; equals to product of electronic charge with  $N_{Inv}$  and  $N_{Dep}$  respectively, and  $V_{Th}$  is the threshold voltage. Appendix A provides the system of equations used in determining threshold voltage of the device based on the condition described by equation (10b).

# 2. Drain Current

A major advantage of surface potential ( $\phi_s$ ) based – model is the drain current ( $I_D$ ) calculation, which uses a single equation for the whole operation range. The approach of the charge-sheet model [27], which is based upon the drift-diffusion equation and Gauss's Law, is

used in our analysis. Under the assumptions of gradual channel and charge-sheet approximations, and if the mobility  $\mu$  is assumed to be constant along the channel [27], the drain current can be written as

$$I_D = I_{Drift} + I_{Diffusion} \tag{11}$$

where.

$$I_{Drift} = \mu \cdot C_{av} \cdot \frac{W}{L} \cdot \left[ \left( V_{a} - V_{pb} \right) \cdot \left( \phi_{SL} - \phi_{S0} \right) - 0.5 \cdot \left( \phi_{SL}^{2} - \phi_{S0}^{2} \right) - \frac{2}{3} \cdot \gamma \cdot \left( \phi_{SL}^{1.5} - \phi_{S0}^{1.5} \right) \right]$$

(12)

$\gamma$  is the body-effect coefficient given by  $\gamma = \frac{\sqrt{2 \cdot \varepsilon_{s_i} \cdot \varepsilon_0 \cdot q \cdot N_A}}{C_{or}}$

and

$$I_{Diffusion} = \mu \cdot C_{ox} \cdot \frac{W}{L} \cdot V_{t} \left[ (\phi_{SL} - \phi_{S0}) + \gamma \cdot (\phi_{SL}^{0.5} - \phi_{S0}^{0.5}) \right] (13)$$

where  $V_t$  is the thermal voltage;  $V_t = \frac{k_B \cdot T}{q}$

In the above equations,  $\phi_{SL}$  and  $\phi_{S0}$  denote the surface potential at the drain end and source end respectively. W is the width of the device, L is the channel length and  $C_{ox}$  is the oxide capacitance per unit area. The above equations do not depend on whether a classical or a quantum formulation based surface potential is used. It is a result of the very basic drift-diffusion equation and Gauss's Law, which have the same form in terms of charge and gradients of charge for both quantum and classical approaches. However, it differs in the way, in which surface potential is calculated.

For the classical approach, surface potential  $\phi_S$  is found from the following expression:

$$\phi_{S}^{CL} = V_{G} - V_{fb} + \frac{Q_{S}^{CL}}{C_{ox}}$$

(14)

in which

$$Q_s^{CL} = -\gamma \cdot C_{\alpha s} \cdot \sqrt{V_t \cdot \left[\alpha + \exp\left(\frac{-2 \cdot \phi_F - V_{cb}}{V_t}\right) \cdot \left(\exp(\alpha) - 1 - \alpha \cdot \exp\left(\frac{V_{cb}}{V_t}\right)\right) + \exp(-\alpha) - 1\right]}$$

(15

where  $V_{cb}$  varies from  $V_S$  at the source end to the  $V_D$  at the drain end, and  $\alpha = \frac{\phi_S^{CL}}{V_c}$ .

For the quantum drain current calculation, once  $\phi_{S0}^{QM}$ , quantum approach based surface potential at the source end (x=0) is determined using equation (9) for a given substrate doping, oxide thickness and gate bias, we have determined  $\phi_{SL}^{QM}$ , surface potential at the drain end

(x=L) by inputting incremental values of  $V_D[20]$ .

The same equation for drain current  $(I_D)$  is extended for the saturation region by replacing the drain bias voltage with the saturation drain voltage  $(V_D = V_{Dsat})$  at the particular applied gate voltage without taking into account the effects of channel length modulation (CLM) and kink effect. The value of saturation voltage  $V_{Dsat}$  is extracted by setting the derivative of drain current with respect to drain bias to zero (pinch-off condition) i.e.

$$\left. \frac{\partial I_D}{\partial V_D} \right|_{V_D = V_{Dsat}} = 0.$$

# IV. Introduction Of High-k Gate Dielectrics

The sub-100 nm MOSFETs face a scaling limit, when a  $SiO_2$  gate dielectric is used, and it requires alternative gate-dielectric materials with higher permittivity and greater physical thickness which prevents tunneling. However, the use of a high-k#gate material may result in dielectric thickness comparable to the device gate length, resulting in increased fringing fields [28] from the gate to the source/drain regions and compromised shortchannel performance. Thus, understanding the impact of dielectric materials different high-k on performance is important. Essentially the key idea in high-k design is to produce the same drain current performance in using  $SiO_2$ , but replacing the  $SiO_2$ dielectric thickness with a thicker high-k that suppresses tunneling effect.

A high-k film will be physically thicker than a pure  $SiO_2$  layer by the ratio of its dielectric constant to that of  $SiO_2$ , and still provide the same gate capacitance, as

$$C_{ox} = \frac{k_{ox} \cdot \mathcal{E}_0}{t_{ox}} = C_{high-k} = \frac{k_{high-k} \cdot \mathcal{E}_0}{t_{high-k}}$$

(16)

implying

$$t_{high-k} = \left(\frac{k_{high-k}}{k_{ox}}\right) \cdot t_{ox} \tag{17}$$

thus potentially reducing direct tunneling current substantially.

In the context of high-k dielectrics, we express eqn (17) in terms of the equivalent oxide thickness (EOT)

defined as the thickness of a pure  $SiO_2$  layer which provides the same gate capacitance as a high-k layer,

$$EOT = \left(\frac{k_{ox}}{k_{high-k}}\right) \cdot t_{high-k} \tag{18}$$

At first glance, it would seem that an arbitrarily high-k value would allow a substantially thick dielectric film to meet very small EOT targets. In practice, the extreme gate dielectric thickness-length aspect ratio that would result from a very high-k value and hence a very thick insulator leads to fringing field effects which undermine the gate electrode's ability to maintain control of the channel [11]. Also, it is known that silicon-single high-k material systems might suffer from unacceptable levels of bulk fixed charge, high density of interface trap states, and low silicon interface carrier mobility [29]. An extremely thin interfacial oxide is used to passivate the interface and minimize interface states when high-k gate materials are deposited. Also, using the low-k gate dielectric one can well confine the electric-fields within the channel region thereby significantly reducing the fringing fields from gate-to-source/drain regions. Thus, use of multiple material layers is a good approach to the gate dielectric for scaled MOSFETs with gate lengths less than 100nm.

In order to model gate stack structure, we have analyzed dielectric thickness (physical/equivalent) of 1.5nm in our cases with n+ poly-Si gate. In the modeling section,  $V_{ox}$  given in equation (9) is replaced by  $V_{ox} + V_{ox} + V_{ox}$  with the introduction of gate stack architecture in which

$$V_{ox1} = \frac{Q_s}{C_{ox1}} \text{ and } V_{ox2} = \frac{Q_s}{C_{ox2}}$$

(19)

for different dielectric layers  $\mathcal{C}_1$  and  $\mathcal{C}_2$ . The EOT of the dielectric stack can be obtained by the above equation in terms of dielectric constants and thicknesses as

$$EOT_{Stack} = t_{SiO_2} + \left(\frac{k_{SiO_2}}{k_{high-k}}\right) \cdot t_{high-k}$$

(20)

# V. RESULTS AND DISCUSSION

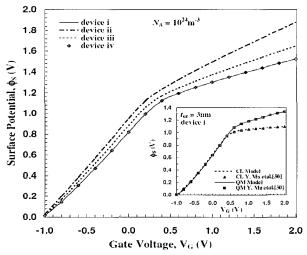

All calculations were made for temperature T = 300 K. Fig 3 shows the variation of surface potential  $(\phi_S)$

versus gate voltage  $(V_G)$  with flat band voltage  $V_{fb} = n + poly-Si$  gate for both classical and quantum-mechanical cases. The inset of the figure proves the validity of model by matching the results with the available fully self-consistent results of Y. Ma etal. [30]. It is clear that in quantum-mechanical case, surface potential does not become constant in strong inversion regime, and rather follows a gradual increase. This happens due to confinement of inversion carriers, which results in a peak of inversion charge density separated from the interface and an increased width of inversion layer.

**Fig. 3.** Surface potential variation with gate voltage for the system shown in Fig. 2 for n+ poly gate. **Inset** shows  $\phi_S$  vs.  $V_G$  for classical (CL) and quantum approach (QM) together with self-consistent results of Ma Y etal.

Thus, the same charge density would result in a higher surface potential in comparison to classical case. The figure also shows surface potential for the four devices under consideration as shown in Fig. 2. An increase in surface potential is seen, as the dielectric permittivity of dielectric increases. It is due to the fact that the capacitance of dielectric is directly proportional to its permittivity, and high capacitance influences more charge thereby increasing surface potential of the device. But, in order to optimize the device characteristics i.e. to obtain the same surface potential, a gate stack system is analyzed to retain the same surface charge density allowing the gate dielectric permittivity to change and in turn corresponding thickness of the high-k gate dielectric is calculated using equation (20). One can thus obtain the same EOT for the stack, but with greater physical thickness, in order to have low gate tunneling currents. Thus, the variation of surface potential for the fourth device is found to be same as that of using single dielectric  $SiO_2$ .

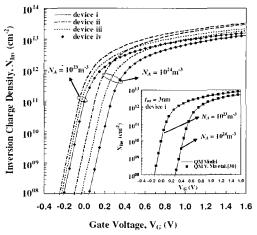

Fig. 4. Variation of Inversion charge density with gate voltage for Fig. 2 devices for different doping densities. Inversion charge density together with Ma Y et al. results are shown in inset.

The inversion charge density ( $N_{Inv}$ ) variation with gate bias together with Y. Ma etal. results [30] at different doping concentrations are shown in Fig. 4. The results so obtained coincide well with the reported self-consistent solution (Y. Ma etal.) as shown in inset of the figure. It can be clearly understood from the graph, that due to carrier energy quantization the total inversion charge induced at a given gate voltage is decreased with increase in doping. Furthermore comparison for the four devices under consideration is done in the drawn figure. As can be interpreted, with increase in the dielectric permittivity of the gate dielectric, the same charge density is achieved at earlier gate voltages. Also the device (iv) in Fig. 2 is found to be analogous to single dielectric  $SiO_2$ .

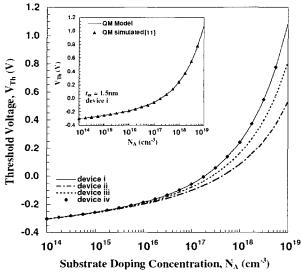

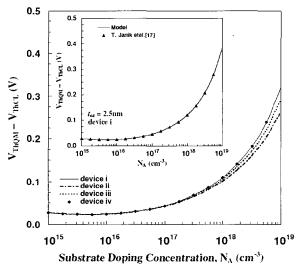

Fig. 5 and its inset show the variation of device threshold voltage with doping concentration for the Fig. 2 devices along with simulated results [11]. The parameters used in our calculations are taken from [11]. One of the well known consequences of the energy quantization in the inversion layer is the increase of the threshold voltage. The values of threshold voltage extracted are found to be in good agreement with the data justifying the analysis. Also a shift in the value of threshold voltage is found while obtaining the results from classical approach to quantum theory i.e. QEs lead

to increase in threshold voltage. This shift in threshold voltage with doping concentration is plotted in Fig. 6 and agrees well with T. Janik etal. results [17]. The shift in  $V_{Th}$  value from classical to quantum approach is due to over-estimation of the inversion charge carrier density in classical case.

**Fig. 5.** Threshold voltage variation with doping concentration with simulated data is shown in **inset**. Fig. 2 system is analyzed for the variation of threshold voltage with doping concentration.

**Fig. 6.** Threshold voltage shift variation with doping concentration due to CL and QM approach with Janik T etal. results.

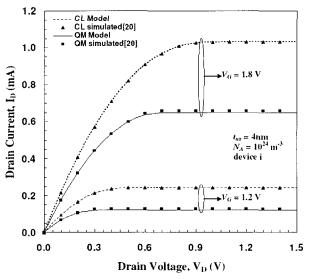

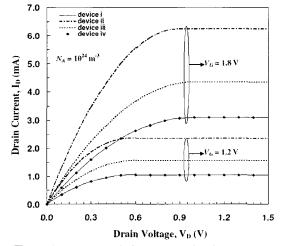

Using the developed surface potential based model, drain characteristics of the devices illustrated in Fig. 2 are obtained for two gate voltages 1.2V and 1.8V in Figs. 7a and 7b. Curves show comparison of classical and quantum approach together with simulated data [20]

for the same set of parameters as shown in Fig. 7a. The developed results are in fair agreement with the available simulated results. One infers from the graphs that an increase in the value of permittivity results in higher value of drain current at the same gate bias. It is found that with the increase in the dielectric permittivity of gate dielectric saturation voltage decreases as high-k influences more charge and hence more channel potential at same gate bias. Also the pinch-off approach adopted in our analysis for calculating the saturation voltage of the device and thus obtaining saturation current is more promising and is free from any fitting parameters.

**Fig. 7a.** Drain characteristics with drain bias at  $V_G = 1.2 \text{V}$  and 1.8V for CL and QM models together with available simulated results for n+ poly gate for device i. W/L = 10,  $\mu = 250 \text{ cm}^2/\text{V.sec}$  (constant)

Fig. 7b. Drain current variation with drain bias at  $V_G = 1.2$ V and 1.8V for Fig. 2 devices.

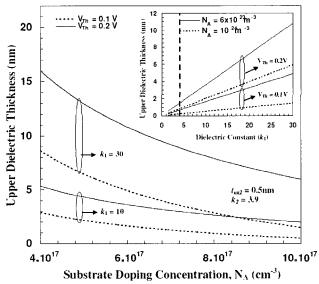

Variation of physical dielectric thickness of upper dielectric  $(k_l)$  with doping concentration is plotted in Fig. 8 to achieve targeted threshold voltage keeping configuration of lower dielectric layer adjoining to substrate to be fixed  $(t_{ox2} = 0.5 \text{nm} \text{ and } k_2 \text{ for } SiO_2)$ . Curves show that with the increase in substrate doping, the dielectric thickness decreases whereas on increasing the dielectric constant for the same set of parameters yields in the increase in dielectric thickness. Also the change in dielectric thickness with dielectric constant  $k_1$ can be seen in inset. The demarcation line shown in the inset resembles the device with single dielectric configuration i.e. SiO2 only. Figure shows that at constant threshold voltage, on comparison with single structure, increase in dielectric dielectric gate permittivity increases the physical thickness of the dielectric sandwiched between gate electrode substrate resulting in greater distance between the gate electrode and the substrate thus reducing the gate leakage current. Thus the formulation in turn gives the relation between different parameters such as gate dielectric thickness, gate dielectric constant and doping density required for device fabrication for the given threshold voltage.

**Fig. 8.** Upper physical dielectric thickness variation with doping density for obtaining targeted threshold voltages at different dielectric permittivity keeping lower dielectric thickness and permittivity fixed and equals to 0.5nm and 3.9  $(SiO_2)$ . **Inset** shows variation of Upper dielectric thickness with dielectric thickness for same device threshold at different doping concentration.

# VI. CONCLUSION

The surface potential based model is developed and is used to determine the characteristics of the device. This model considers the decoupling of Poisson's and Schrödinger's equations using triangular potential well (TPW) approximation instead of fully self-consistent approach by Y. Ma et al. [30]. The characteristics obtained by the model matches well with available data. The threshold voltage analysis is based on a definition more applicable for the quantum approach and on more realistic assumptions. A compact analytical model quantitatively describes the threshold voltage shifts due to quantum effects as a function of the doping concentration. The gate voltage dependence of the inversion layer charge is thus modeled quite accurately by the use of the triangular potential well approximation. Consequently, this approximation is found to be both an accurate and efficient method for modeling the I-V characteristics of the MOS transistor. Also introduction of gate stack architecture improves the characteristics of the device. One can interpret that with the increase in gate dielectric thickness tunneling current in the channel decreases. This allows one to use physically thicker films thereby reducing the tunnelling current while maintaining the same gate capacitance needed for scaled device operation. So downscaling of dielectric thickness is possible without compromising the reduction in physical thickness of gate dielectric, and this has become possible due to the introduction of gate stack architecture. An optimization of gate dielectric thickness yields as a helping aid in device fabrication with targeted threshold voltages.

## ACKNOWLEDGEMENT

The authors are grateful to the Department of Science and Technology (DST), Government of India, for providing the necessary financial assistance to carry out this research work.

# APPENDIX A

$$\frac{dQ_{lnv}}{dV_{G}} = q \cdot \left(\frac{k_{B} \cdot T}{\pi \cdot \hbar^{2}}\right) \cdot \sum_{i} n_{vi} \cdot m_{di} \cdot \sum_{j} \frac{-\exp\left(\frac{E_{F} - E_{ij}}{k_{B} \cdot T}\right)}{1 + \exp\left(\frac{E_{F} - E_{ij}}{k_{B} \cdot T}\right)} \cdot \frac{1}{k_{B} \cdot T} \cdot \frac{dE_{ij}}{dV_{G}}$$

(A1)

$$\frac{dQ_{Dep}}{dV_G} = \sqrt{\frac{q \cdot \varepsilon_{Si} \cdot \varepsilon_0 \cdot N_A}{2 \cdot \phi_S}} \cdot \frac{d\phi_S}{dV_G}$$

(A2)

$$\frac{dE_{ij}}{dV_{G}} = \left(\frac{\hbar^{2}}{2 \cdot m_{i}^{\perp}}\right)^{\frac{1}{3}} \cdot \left[\frac{3}{2} \cdot \pi \cdot q \cdot \left(j + \frac{3}{4}\right)\right]^{\frac{2}{3}} \cdot \frac{2}{3} \cdot F_{S}^{\frac{-1}{3}} \cdot \frac{dF_{S}}{dV_{G}} - q \cdot \frac{d\phi_{S}}{dV_{G}}$$

(A3)

$$\frac{d\phi_S}{dV_G} = 1 - \frac{\varepsilon_{Si}}{C_{ox}} \cdot \frac{dF_S}{dV_G}$$

(A4)

$$\frac{dF_S}{dV_G} = \frac{1}{\varepsilon_{Si}} \cdot \left[ \frac{dQ_{Inv}}{dV_G} + \frac{dQ_{Dep}}{dV_G} \right]$$

(A5)

The above system of equations is solved iteratively to get the threshold voltage of the device using condition given by equation (10b).

**Table 1.** Physical quantities used in the calculations. All effective masses are in units of the free electron mass.

| Surface<br>Valleys  | < 100 >              |             |

|---------------------|----------------------|-------------|

|                     | Lower                | Higher      |

| i                   | 1                    | 2           |

| $\overline{n_{vi}}$ | 2                    | 4           |

| $m_{zi}$            | 0.916.m <sub>0</sub> | $0.190.m_0$ |

| $m_{di}$            | $0.190.m_0$          | $0.417.m_0$ |

$m_0 = 9.1 \times 10^{-31} \text{ Kg} = \text{free electron mass}$

# REFERENCES

- [ 1 ] M. Ono, M. Saito, T. Yoshitomi, C. Fiegna, T. Ohguro and H. Iwai, "A 40 nm gate length nMOSFETs", *IEEE Trans. Electron Devices*, Vol. 42, p.1822-30,1995.

- [2] Y. Taur, D. A. Buchanan, W. Chen, D. J. Frank, K. E. Ismail, S. H. Lo, G. A. Sai-Halasz, R. G.

- Viswanathan, H. J. C. Warn, S. J. Wind, H. S. Wong, "CMOS scaling into the nanometre regime", *Proceeding IEEE*, Vol. 85, p. 486-504, 1997.

- [ 3 ] S. H. Lo, D. A. Buchanan, Y. Taur, W. Wang, "Quantum-Mechanical Modeling of Electron Tunneling Current from the Inversion Layer of Ultra-Thin-Oxide nMOSFETs", *IEEE Trans. Electron Device Letter*, Vol. 18, p.209-11, 1997.

- [4] E. M. Vogel, K. Z. Ahmed, B. Hornug, W. K. Henson, P. K. McLarty, G. Lucovsky, J. R. Hauser, J. J. Wortman, "Modeled tunnel currents for high dielectric constant dielectrics", *IEEE Trans. Electron Devices*, Vol. 45, p. 1350-4, 1998.

- [ 5 ] Q. Lu, D. Park, A. Kalnitsky, C. Chang, C. C. Cheng, S. P. Tay, T. J. King and C. Hu, "Leakage current comparison between ultra-thin Ta<sub>2</sub>O<sub>5</sub> films and conventional gate dielectrics", *IEEE Trans. Electron Devices Letter*, Vol. 19, p.341-2, 1998.

- [ 6 ] D. Park, Y. King, Q. Lu, T. J. King, C. Hu, A. Kalnitsky, S. P. Tay, C. C. Cheng, "Transistor characteristics with Ta<sub>2</sub>O<sub>5</sub> gate dielectric", IEEE Trans. Electron Devices Letter, Vol. 19, p. 441-3, 1998.

- [7] X. Guo, X. Wang, Z. Juo, T. P. Ma, T. Tamagawa, "High-quality ultrathin (1.5nm)  $TiO_2/Si_3N_4$  gate dielectric for deep sub-micron CMOS technology", *IEDM Technical* Digest, p.137-140, 1999.

- [8] W. J. Qi, R. Nieh, B. H. Lee, L. Kang, Y. Jeon, K. Onishi, T. Ngai, S. Banerjee, J. C. Lee, "MOSCAP and MOSFET characteristics using  $ZrO_2$  gate dielectric deposited directly on Si", IEDM Technical Digest, p.145-81, 1999.

- [9] B. H. Lee, L. Kang, W. J. Qi, R. Nieh, Y. Jeon, K. Onishi, J. C. Lee, "Ultrathin hafnium oxide with low leakage and excellent reliability for gate dielectric application", *IEDM Technical Digest*, p.133-6, 1999.

- [10] G. D. Wilk, R. M. Wallace, J. M. Anthony, "Hafnium and zirconium silicates for advanced gate dielectrics", *J. Appl. Phys.*, Vol. 87, p. 484-92, 2000.

- [11] B. Chenng, Min Cao, R. Rao, A. Inani, P. V. Voorde, W. M. Greene, J. M. C. Stork, Z. Yu, P. M. Zeitzoff, J. C. S. Woo, "The impact of High-k gate dielectrics and metal gate electrode on sub-100nm MOSFETs", *IEEE Trans. Electron Devices*, Vol. 46, p. 1537-42, 1999.

- [12] F. Stern and W. E. Howard, "Properties of semiconductor surface inversion layers in the electric quantum limit", *Phys Rev.*, Vol. 163, p. 816-35, 1967.

- [13] T. Ando, A. B. Fowler, F. Stern, "Electronic properties of two-dimensional systems", *Rev. Mod. Phys.*, Vol. 54, p. 437-672, 1982.

- [14] M. J. Van Dort, P. H. Woerlee, A. J. Walker, C. A. H. Juffermans and H. Lifka, "Influence of high substrate doping levels on the threshold voltage and the mobility of deep-sub micrometer MOSFETs", *IEEE Trans. Electron Devices*, Vol. 39, p. 932–8, 1992.

- [15] A. Hartstein and N. F. Albert, "Determination of the inversion-layer thickness from capacitance measurements of metal-oxide-semiconductor field-effect transistors with ultra thin oxide layers", *Phys. Rev. B*, Vol. 38, p. 1235–40, 1988.

- [16] Y. Ohkura, "Quantum effects in Si n-MOS inversion layer at high substrate concentration", Solid-State Electron, Vol. 33, p. 1581-5, 1990.

- [17] T. Janik and B. Majkusiak, "Influence of carrier energy quantization on threshold voltage of metaloxide-semiconductor transistor", J. Appl. Phys., Vol. 75, p. 5186-90, 1994.

- [18] R. Versari and B. Ricco, "Scaling of maximum capacitance of MOSFET with ultra-thin oxide", *Electronic letters*, Vol. 34, p. 2175-6, 1998.

- [19] G. Baccarani and M. R. Worderman, "Transconductance degradation in thin-oxide MOSFETs", *IEEE Trans. Electron Devices*, Vol. 30, p. 1295-1304, 1983.

- [20] K. Ip. Brian and R. Brews Johnn, "Quantum effects upon drain current in a biased MOSFET", *IEEE Trans. Electron Devices*, Vol. 45, p. 2213-21, 1998.

- [21] M. J. Van Dort, P. H. Woerlee, A. J Walker, "A simple model for quantisation effects in heavilydoped silicon MOSFETs at inversion conditions", *Solid-State Electron*, Vol. 37, p. 411-4, 1994.

- [22] T. Janik and B. Majkusiak, "Analysis of the MOS transistor based on the self-consistent solution to the Schrödinger and Poisson equations and on the local mobility model", *IEEE Trans. Electron Devices*, Vol. 45, p. 1263-71, 1998.

- [23] G. Chindalore, S. A. Hareland, S. Jallepalli, A. F.

- Tasch, C. M. Maziar, V. K. F. Chia and S. Smith, "Experimental determination of threshold voltage shifts due to quantum mechanical effects in MOS electron and hole inversion layers", *IEEE Trans. Electron Devices Letter*, Vol. 18, p. 206-8, 1997.

- [24] S. Jallepalli, J. Bude, W. K. Shih, M. R. Pinto, C. M. Maziar, A. F. Tasch, "Electron and hole quantization and their impact on deep submicron silicon p-and n-MOSFET characteristics", *IEEE Trans. Electron Devices*, Vol. 44, p. 297-302, 1997.

- [25] C. Moglestue, "Self-consistent calculation of electron and hole inversion charges at siliconsilicon dioxide interfaces", *J. Appl. Phys.*, Vol. 59, p. 3175-83, 1986.

- [26] F. Stern, "Self-consistent results for n-Type Si inversion layers", *Phys Rev B.*, Vol. 5, p. 4891-9, 1972.

- [27] N. Arora, MOSFET models for VLSI circuit simulation. Theory and practice. New York: Springer-Verlag, 1993.

- [28] C. H. Choi, P. R. Chidambaram, R. Khamankar, C. F. Machala, Z. Yu and R. W. Dutton, "Dopant profile and gate geometric effects on polysilicon gate depletion in scaled MOS", *IEEE Trans. Electron Devices*, Vol. 49, p. 1227-31, 2002.

- [29] S. A. Campbell, D. C. Gilmer, X. C. Wang, M. T. Hsieh, H. S. Kim, W. L. Gladfelter and J. Yan, "MOSFETs transistors fabricated with high permittivity *TiO*<sub>2</sub> dielectrics", *IEEE Trans. Electron Devices*, Vol. 44, p. 104-9, 1997.

- [30] Y. Ma, L. Liu, Z. Yu and Z. Li, "On the degeneracy of quantized inversion layer in MOS structures", *Solid-State Electron*, Vol. 44, p. 1925-9, 2000.

Tina Mangla was born in Delhi, India on September 06, 1980. She received the B.Sc.(special) degree in electronics from Gujarat University, Gujarat, India in 2000 and M.Sc. degree in electronics from University of Delhi, Delhi, India in 2002. She

is currently pursuing the Ph. D. degree at the Delhi University, Delhi, India. She joined semiconductor devices research laboraling, department of Electronic Science University & Delhi South Campus in 2002.

Her research interests are in the modeling, simulation and characterization of silicon based devices especially MOSFETs with quantization effects and poly-crystalline TFT.

Amit Sehgal was born in Delhi, India on December 01, 1979. He received the B.Sc.(Honor) and M.Sc. degrees in electronics from University of Delhi, Delhi, India in 2000 and 2002 respectively. He is currently pursuing the Ph. D. degree at the

Delhi University, Delhi, India. He joined Semiconductor Device Research Laboratory Department of Electronic Science, University of Delhi South Campus in year 2002. His research interests are in the modeling, simulation and characterization of silicon based devices especially poly-crystalline TFT and MOSFETs with quantization effects.

Manoj Saxena was born in New Delhi, India, on August 14, 1977. He received the B.Sc (Hons.) and M.Sc. degrees in electronics from the University of Delhi, New Delhi, in 1998 and 2000, respectively. Since 2000, he has been pursuing the Ph.D.

degree in electronics at Semiconductor Device Research Laboratory, Department of Electronic Science, University of Delhi. He joined Deen Dayal Upadhyaya College, University of Delhi, in 2000, as a Lecturer. Presently, he is working on modeling and simulation of gateengineered structure for deep sub-micrometer MOSFETs. He is the Joint Secretary of 16<sup>th</sup> Asia Pacific Microwave Conference to be held 15<sup>th</sup>-18<sup>th</sup> December, 2004 in New Delhi, India. He has published 10 papers in international journals and conferences. He has contributed one chapter entitled *MOSFET Modeling* in Encyclopedia on RF and Microwave Engineering, John Wiley to appear in January 2005.

Subhasis Haldar was born in India in 1967. He received the B.Sc. (Hon.) and M.Sc. degrees, both in physics, and the Ph.D. degree in Electronics from the University of Delhi, India, in 1988, 1990, and

1995, respectively He joined the Semiconductor Device Research Laboratory, Department of Electronic Science, University of Delhi South Campus in 1991, and developed analytical models for both MOSFET and MESFET devices. He joined Motilal Nehru College, University of Delhi, in 1993, as a Lecturer, and is now Reader. Currently, his field of interest is miniaturization of devices, study and suppression of hot carrier effect considering LDD and FOLD structures, single and double gate MOSFET, surrounding gate/cylindrical devices and Polysilicon TFT. He has around 110 technical papers published in international journals and conference proceedings. Dr. Haldar was member of ISRAMT'93, Joint Secretary of APMC'96.

Mridula Gupta received the B.Sc. (Physics) in 1984, M.Sc. (Electronics) in 1986, M Tech (Microwave Electronics) in 1988, and PhD (Optoelectronics) in 1998, all from the University of Delhi. She joined

the Department of Electronic Science, University of Delhi in 1989, as a lecturer and is currently a reader there. She is fellow of the Institution of Electronics and Telecommunication Engineers, (India), Member IEEE and life member of Semiconductor Society of India Her current research interests include modeling and simulation of MOSFETs, MESFETs, and HEMTs for microwave-frequency applications. She has around 67 publications in international and national journals and conferences. She is a Secretary of Asia Pacific Microwave Conference (APMC-2004) to be held in New Delhi, India in December 2004. She has contributed one chapter entitled *MOSFET Modeling* in Encyclopedia on RF and Microwave Engineering, John Wiley to appear in January 2005.

**R.S.** Gupta received the B.Sc. and M.Sc. degree from Agra University, India, in 1963 and 1966, respectively, and the PhD degree in electronic engineering form the Institute of Technology, Banaras Hindu University, in 1970. He joined Ramjas College,

University of Delhi, India in 1971, and then joined the Department of Electronic Science, University of Delhi in

1987, where he is a professor. His present interests and activities cover modeling of SOI submicrometer MOSFET and LDD MOSFETs, modeling and design of high electron-mobility transistors, hot-carrier effects in MOSFETs and modeling of GaAs MESFETs for highperformance microwave and millimeter-wave circuits and Quantum effect devices. He heads several major research projects sponsored by the Ministry of Defence, Department of Science and Technology, Council of Science and Industrial Research and University Grants Commission. He has published more than 293 papers in various international and national journals and conferences. 25 students have already got Ph.D. under his guidance and 10 students are working under him for their Ph.D. He was a visitor at the University of Sheffield, UK, in 1988, under the ALIS Link exchange program and also visited several U.S. Universities in 1995 and Spain in 1999. He has been a senior member of the IEEE since 1981. He was an executive member of the IEEE-ED/MTT Chapter India council. He is listed in Who's Who in the World. His name also appeared in the Golden list of IEEE Transactions on Electron Devices in December 1998 and December 2002. He is a fellow of the Institution of Electronics and Telecommunication Engineers (India), life member of the Indian Chapter of the International Centre for Theoretical Physics (ICTP) and life member semiconductor society of India. He was the secretary of the both ISRAMT'93 and APMC'96 and the Chairman of the Technical programme committee of APMC'96, and has edited the proceedings of the both international conferences. Prof. Gupta is a Chairman of Asia Pacific Microwave Conference (APMC-2004) to be held in New Delhi, India in December 2004. He has contributed one chapter entitled MOSFET Modeling in Encyclopedia on RF and Microwave Engineering, John Wiley to appear in January 2005.