# High $f_T$ 30nm Triple-Gate $In_{0.7}$ GaAs HEMTs with Damage-Free $SiO_2/SiN_x$ Sidewall Process and BCB Planarization

Dae-Hyun Kim, Seong-Jin Yeon, Saegm-Sub Song, Jae-Hak Lee\*, and Kwang-Seok Seo

Abstract—A 30 nm In<sub>0.7</sub>GaAs High Electron Mobility Transistor (HEMT) with triple-gate has successfully fabricated using the SiO2/SiNx sidewall process and BCB planarization. The sidewall gate process was used to obtain finer lines, and the width of the initial line could be lessened to half by this process. To fill the Schottky metal effectively to a narrow gate line after applying the developed sidewall process, the sputtered tungsten (W) metal was utilized instead of conventional e-beam evaporated metal. To reduce the parasitic capacitance through dielectric layers and the gate metal resistance (Rg), the etchedback BCB with a low dielectric constant was used as the supporting layer of a wide gate head, which also offered extremely low R<sub>g</sub> of 1.7 Ohm for a total gate width (Wg) of 2x100 m. The fabricated 30nm In<sub>0.7</sub>GaAs HEMTs showed V<sub>th</sub> of -0.4V, G<sub>m.max</sub> of 1.7S/mm, and  $f_T$  of 421GHz. These results indicate that InGaAs nano-HEMT with excellent device performance could be successfully fabricated through a reproducible and damage-free sidewall process without the aid of state-of-the-art lithography equipment. We also believe that the developed process will be directly applicable to the fabrication of deep sub-50nm InGaAs HEMTs if the initial lime length can be reduced to below 50nm order.

Index Terms—InP, HEMT, InGaAs/InAlAs, nanometer, sidewall, triple-gate, BCB,  $f_T$

#### I. Introduction

An InGaAs/InAlAs high electron mobility transistor (HEMT) on an InP substrate has shown excellent frequency characteristics due to enhanced electron mobility and an increased conduction band discontinuity  $(\Delta E_c)^{1-3}$ . Recently, the device microwave characteristics have been improved considerably by reducing the gate length (L<sub>g</sub>) to the nanometer scale, by adopting a highly strained In<sub>x</sub>GaAs channel (x>0.53) and two-step recess etching technology <sup>4,5</sup>. According to the recent work by the Fusitsu group, the current gain cut-off frequency (f<sub>T</sub>) of 562GHz with L<sub>g</sub> of 25nm and the strained In<sub>x</sub>Ga<sub>1-x</sub>As (X=0.7) channel was reported <sup>6</sup>).

The conventional e-beam lithography equipment with an acceleration voltage of 30 kV and a Tungsten (W) or LaB<sub>6</sub> filament would offer a minimum feature scale of about 100nm. To reduce the device gate length (Lg) to the sub-100nm scale, the state-of-the-art e-beam lithography equipment with high resolution will be needed. The side-wall process has been widely used to overcome these lithography limitations, particularly in CMOS device fabrications<sup>7)</sup>. The fine pattern is obtained by the formation of a side-wall spacer through the sequence of dielectric etching, dielectric redeposition and dielectric etch-back. Among the various process parameters, the percentage of overetching in the etchback step predominantly affects the shape of the final side-wall spacer. Due to the step coverage problem in dielectric redeposition, precise control of the overetching time is impossible, and thus the ambiguity of the shape of the final side-wall spacer would be problematic in this process.

Manuscript received May 30, 2004; revised June 15, 2004. ISRC & School of Electrical and Computer Engineering, Seoul National University

<sup>\*</sup> WAVICS, Co., Ltd.

In this study, a highly reproducible side-wall gate process was developed in order to overcome the lithography limitation. The ambiguity of the shape of the final side-wall spacer was resolved by using SiN<sub>x</sub>/SiO<sub>2</sub> dual dielectric layers and appropriate etching gas <sup>8)</sup>. Using the developed sidewall gate process, a 30nm gate could be obtained reproducibly. To fill the Schottky gate metal effectively in the narrow line opening having a high aspect ratio of above 3, sputtered tungsten (W) metal was used instead of conventional e-beam evaporated metal. With the newly developed process features, 30nm In<sub>0.7</sub>GaAs HEMT's were successfully fabricated and characterized.

# II. DAMAGE-FREE AND REPRODUCIBLE S102/SINX SIDEWALL GATE PROCESS

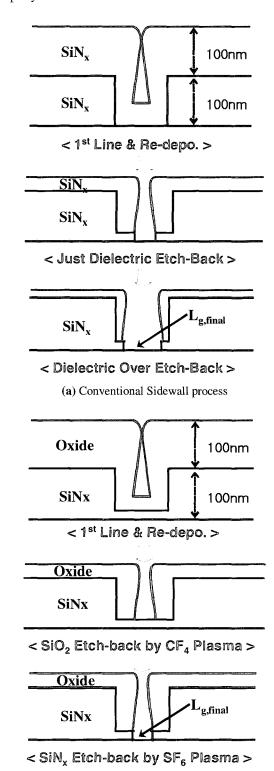

Figure 1(a) shows the procedure of the conventional sidewall gate process which includes first line definition, dielectric redeposition and dielectric etch-back. The final gate length ( $L_g$ ) is reduced according to the dimensions of the two sidewall spacers. Because the shape of the final sidewall spacer easily changes with the duration time of dielectric etch-back, the fine control of the final gate length ( $L_g$ ) is very difficult.

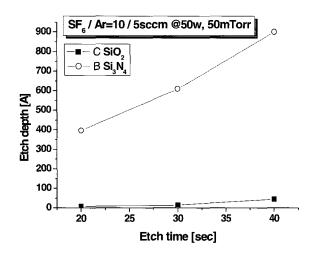

**Figure 1(b)** represents our new sidewall process, which utilizes two dielectric layers of SiN<sub>x</sub> and SiO<sub>2</sub>, and two plasma gas sources for the purpose of dielectric dry etching. After the redeposited SiO<sub>2</sub> was etched by CF<sub>4</sub>-based plasma, the residual SiN<sub>x</sub> was etched by SF<sub>6</sub>-based plasma. **Figure 2** shows typical SF<sub>6</sub> based plasma etching characteristics for PECVD grown SiO<sub>2</sub> and SiN<sub>x</sub>. Here, the SF<sub>6</sub>-based plasma has a high etching selectivity for the SiO<sub>2</sub> layer, which prevents the shape of the final side-wall spacer from being reduced during overetching. This feature does ensure the reproducibility of the proposed side-wall gate process. The actual etch selectivity for the oxide layer by the SF<sub>6</sub> plasma was over 20 in this process.

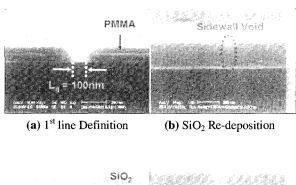

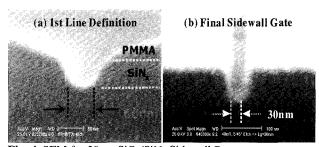

**Figure 3** shows the over-all SEM images of the proposed side-wall gate process in detail. After applying the newly developed sidewall process, the initial line could be reduced to a half scale. In addition, SF<sub>6</sub> gas has the advantage of little plasma-induced damage during

the etching process, which can allow enough overetching time without any degradation of the carrier transport property <sup>8)</sup>.

(b) Newly developed sidewall Process **Fig. 1.** Procedure of Sidewall process

Fig. 2. SiO<sub>2</sub> and SiN<sub>x</sub> etch results by SF<sub>6</sub> based plasma

Fig. 3. The over-all SEM Photograph of Sidewall process

### III. NOVEL 30NM TRIPLE-GATE TECHNOLOGY

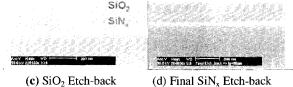

To reduce the final line length after the sidewall process, it is much more effective to lessen the initial line length. To achieve this goal, thin PMMA with the thickness of 500Å was used. In accordance with the reduction of the e-beam resist thickness, it is possible to reduce the quantity of e-beam dose, which results in the resolution of finer line length through dose optimization. **Figure 4** shows the over-all SEM images for the 30nm sidewall gate process in detail. Using thin PMMA and the dose optimization method, the initial line length with the thickness of 60 to 70nm could be obtained. In addition to the decrease of the initial line length, a sloped

etching profile with anisotropy of 75 degrees also aids in conformal second oxide deposition, which resulted in more greatly reduced final line length after etch-back of the re-deposited dielectric layer. With the above sidewall gate process, the obtained final gate length after dielectric etch-back was 30nm.

Fig. 4. SEM for 30nm SiO<sub>2</sub>/SiN<sub>x</sub> Sidewall Process

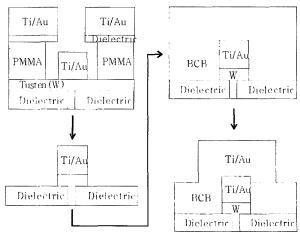

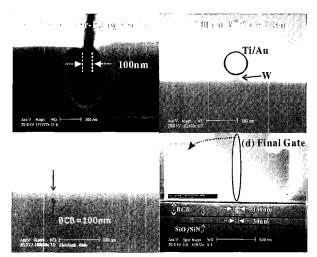

The procedure for the fabrication of the triple-gate structure is shown in **Fig. 5**. After filling the sputtered tungsten (W) metal in the narrow gate line, a second gate metal (Ti/Au) with the thickness of 1500Å was evaporated and lifted off, and then unnecessary tungsten metal was removed by SF<sub>6</sub>-based RIE. Here, SF<sub>6</sub>-based RIE also has etching selectivity for oxide over tungsten, thus it is possible to do some degree of overetching. Next, planarization using a BCB layer with a low dielectric constant ( $\varepsilon_r$ ) of 2.75 was carried out. Finally, the third gate layer, typically wide gate head, was defined using a bilayer of PMMA and copolymer, and then Ti/Au with a metal thickness of 5000Å was evaporated and lifted off. **Figure 6** shows the SEM images of the fabricated 30nm triple-gate structure.

Fig. 5. Schematic procedures for BCB-assisted triple-gate process

Fig. 6. SEM images for triple-gate metal process

# IV. FABRICATION OF 30NM IN0.7GAAs HEMTS

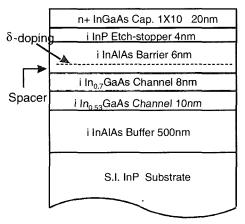

Pseudomorphic InGaAs/InAlAs HEMT epitaxial layers with an InP etch-stopper were grown by solid-source molecular beam epitaxy on 3-inch semi-insulating InP substrates. The detailed structures are shown in **Fig.** 7. An 8nm strained In<sub>0.7</sub>GaAs channel was adopted to enhance the carrier transport property, and a 4nm undoped InP layer acted as an etch-stopper in the selective gate recess etching process. The results of Hall measurement indicated a 2-DEG (two dimensional electron gas) density of  $3 \times 10^{12}$  /cm<sup>2</sup> with a low field Hall mobility of 11,000 cm<sup>2</sup>/V-s at room temperature.

Fig. 7. Cross Section of InGaAs/InAlAs HEMTs

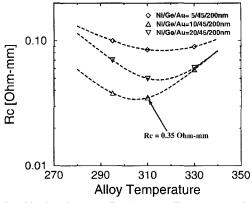

Device fabrication began with mesa isolation down to the InAlAs buffer layer by wet chemical etching using a  $H_3PO_4: H_2O_2: H_2O$  mixture. For the S/D ohmic contacts, an image reversal photoresist was used to achieve a well-defined overhang profile for lift-off, and then ohmic contacts were formed by Ni/Ge/Au metallization through e-beam evaporation and alloyed in  $H_2$  ambient after passivation of the remote PECVD (R-PECVD) grown 70nm  $SiN_x$  pre-passivation.

Fig. 8. Ohmic Contact Resistance  $(R_c)$  versus the ally temperature for various Ni/Ge/Au metal systems

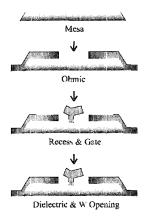

**Figure 8** shows the optimization results of S/D ohmic contact for various metal systems. The ohmic metal system of Ni/Ge/Au(10/45/160nm) had a significantly reduced contact resistance (R<sub>c</sub>) of below  $0.035\Omega$ -mm, which is acceptable for the sub-50nm gate device. The developed SiN<sub>x</sub>/SiO<sub>2</sub> side-wall process was applied to define a 30nm gate foot, and then selective gate recess etching using a mixture of citric acid and H<sub>2</sub>O<sub>2</sub> was performed. The developed BCB-assisted triple-gate process was applied to form a 30nm gate structure. The overall device fabrication procedures are summarized in **Fig. 9** <sup>9)</sup>.

Fig. 9. The over-all HEMT fabrication procedures

# V. Dc And Microwave Characteristics

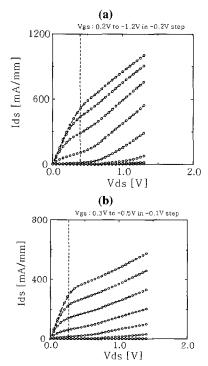

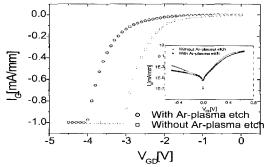

Two types of 30nm InGaAs HEMT devices such as an InP-Schottky barrier device and an InAlAs-Schottky barrier device by means of Ar-based RIE etching with low plasma-induced damage characteristics were fabricated. The fabricated 30 nm HEMTs were characterized by onwafer measurement for their DC and microwave performances. The output I-V transfer curves for the two HEMT devices were plotted in Fig. 10. The 30nm HEMTs with an InP-Schottky barrier exhibit V<sub>th</sub> of -0.85V and  $G_{m,max}$  of 1.75S/mm. The 40nm HEMTs with an InAlAs-Schottky barrier show somewhat higher  $G_{m,max}$ of 1.69S/mm and lower V<sub>th</sub> of -0.3V due to the etching of the InP etch-stopper by Ar plasma. On comparing the performance of these two devices, the short channel effect was found to be considerably suppressed for the InAlAs-Schottky barrier device. This was due to the improvement of the aspect ratio, namely, the ratio of the device gate length to the distance between the channel and the Schottky contact. Quantitatively, 40% improvement of the aspect ratio led to an approximately 2.7-fold increase of voltage gain (G<sub>m</sub>/G<sub>o</sub>).

**Fig. 10.** (a) *I-V* transfer curve for a device with InP-Schottky gate and (b) *I-V* transfer curve for a device with InAlAs-Schottky gate.

**Figure 11** shows the reverse and forward Schottky-gate characteristics for the two types of HEMT devices. Because the InP layer has a low Schottky barrier height (SBH) of typically 0.35 eV compared with the In<sub>0.52</sub>AlAs layer which has SBH of about 0.6 eV, a similar behavior of the off-state breakdown characteristics was appeared. These can also be explained by the increase of the forward turn-on voltage (V<sub>on</sub>) of the InAlAs-Schottky device.

Fig. 11. The Schottky Gate Characteristics. A device with InAlAs schottky shows  $BV_{GD}$  of – 4.0V and gate turn-on voltage  $(V_{on})$  of + 0.45V

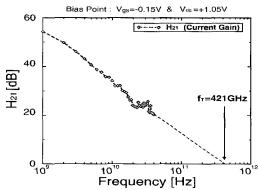

The small signal scattering parameters (S-parameters) of  $2\times50\mu m$  InGaAs HEMTs were measured using on-wafer probing and the 8510C network analyzer (1~40GHz). Shown in **Fig. 12** was the plot of H<sub>21</sub> versus the frequency biased near the maximum transconductance ( $G_{m,max}$ ) region. Extrapolating H<sub>21</sub> to zero gain with a -6 dB/octave slope, an estimation of 421 GHz was obtained for  $f_T$ . We believe that this result indicates an excellent sub-100nm InGaAs HEMTs with little short channel effects without the aid of state-of-the-art e-beam lithography equipment.

**Fig. 12.** Typical Current gain  $H_{21}$  versus measured frequency for the 30nm InGaAs HEMT's biased near the peak transconductance ( $G_{m,max}$ )

## VI. CONCLUSION

We have fabricated a 30nm  $In_{0.7}GaAs$  HEMT with triple-gate metal using the sidewall process and BCB planarization. Fine lines measuring 30nm could be obtained by the dual  $SiO_2/SiN_x$  sidewall processes and the triple-gate metal process assisted by the BCB layer with low dielectric constant ( $\varepsilon_r$ ) did result in a good metal-filling property in the narrow gate line with a high aspect ratio, a stable metal structure stability and a reduced gate fringing parasitic effect. The developed process was applied to fabricate 30nm InGaAs HEMTs which exhibited  $G_{m,max}$  of 1.7S/mm and  $f_T$  of 421GHz. We demonstrated that 30nm InGaAs HEMTs could be successfully fabricated reproducibly through our damage-free sidewall process without the aid of state-of-the-art lithography equipment.

#### REFERENCES

- [1] P. C. Chao, A. J. Tessmer, K. G. Duh, P. Ho, M. Kao, P. M. Smith, J. M. Ballingall, S. M. J. Liu and A. A. Jabra, "W-Band Low-Noise InAlAs/InGaAs Latticematched HEMT's," *IEEE Electron Device Lett.*, vol. 11, pp. 59-62, Jan., 1990.

- [2] P. M. Smith, "InP-based HEMTs for microwave and millimeter-wave applications", in *Proc. Indium Phosphide and related Conf.*, Sapporo, Japan, pp. 9-13, 1995

- [3] G. -W. Wang, Y. -K. Chen, W. J. Schaff, and L. F. Eastman, "A 0.1μm Al<sub>0.5</sub>In<sub>0.5</sub>As/Ga<sub>0.5</sub>In<sub>0.5</sub>As MODFET fabricated on GaAs substrate," *IEEE Trans. Electron Devices*, vol. 35, pp. 818-823, 1988.

- [4] K. Shinohara, Y. Yamashta, A. Endoh, K. Hikosaka, T. Matsui, T. Mimura and S. Hiyamizu, "Extremely High-Speed Lattice-Matched InGaAs/InAlAs High Electron Mobility Transistors with 472GHz Cutoff frequency," *Japanese Journal of Applied Physics*, vol. 41, pp. L437-L439, 2002

- [5] T. Suemitsu, H. Yokoyama, T. Ishii, T. Enoki, G. Meneghesso and E. Zanoni, "30-nm Two-Step Recess Gate InP-Based InAlAs/InGaAs HEMTs", IEEE Trans. Electron Devices, vol. 49, No. 10, pp.

- 1694-1700, 2002

- [6] Y. Yamashita, A. Endoh, K. Shinohara, M. Higashiwaki, K. Hikosaka and T. Mimura, "Ultra-Short 25nm-Gate Lattice-Matched InAlAs/InGaAs HEMTs within the Range of 400GHz Cutoff frequency," *IEEE Trans. Electron Device Letters*, vol. 22, no. 8, pp. 367-369, 2001

- [7] M. Ono, M. Saito, T. Yoshitomi, C. Fiegna, T. Ohguro, H. Iwai, "Sub-50nm gate length n-MOSFETs with 10nm phoshorus source and drain junctions" *IEEE Electron Devices Meeting (IEDM)*, pp. 5-8, Dec. 1993

- [8] D. H. Kim, S. J. Kim, Y. H. Kim and K. S. Seok, "Damage-Free SiO2/SiNx Side-wall Gate Process and its application to 40nm InGaAs/InAlAs HEMT's with 65% InGaAs Channel", Proc. Int. Indium Phosphide and Related Materials (IPRM), pp. 61-64, Santa Barbara, USA, 2003

- [9] D. H. Kim, S. W. Kim, S. C. Hong, S. W. Paek, J. H. Lee, K. W. Jung and K. S. Seo, "Fabrication and Characterization of 0.2μm InAlAs/InGaAs M-HEMT's with Inverse Step-Graded InAlAs Buffer on GaAs substrate," *Journal of Semiconductor Technology and Science*, vol. 1, no. 2, pp. 111-115, 2001

#### **ACKNOWLEDGMENTS**

This work was financially supported by the National Program for Tera-level Nano-devices of the Ministry of Science & Technology of Korea as one of the 21-Century Frontier Programs. The authors would like to thank Dr. Jiang Jian at MBE Technology for the epitaxial-layer growth of InGaAs/InAlAs HEMTs

**Dae-Hyun Kim** was born in Korea on November 13, 1974. He received the B.S. degree in Electrical Engineering and Computer Science at Kyungpook National University, Taegu, Korea, in 1997, the M.S. degree from Electrical Engineering at Seoul

National University, Seoul, Korea, in 2000, and Ph.D degree on Electrical Engineering and Computer Science at Seoul National University, Seoul, Korea, in 2004. Now he is in Post-Doctorate position on Electrical Engineering and Computer Science at Seoul National University, Korea. He also worked at the Inter-university Semiconductor Research Center (ISRC), Seoul, Korea, from 1999 to 2001, where he engaged in the development of 0.5µm CMOS fabrication as a research assistant for the dry etching. His current interests include the development for the III-V Nano-InGaAs-HEMT's device and its application for high speed digital and analog ICs.

Seong-Jin Yeon was born in Korea on September 13, 1975. He received the B.S. degree in Electronics Engineering at Kwangwoon University, Seoul, Korea in 2002. Now he pursuits the M.S. degree in Electrical Engineering and Computer Science at Seoul

National University, Seoul, Korea. His current research activities include the development for the III-V Nano-InGaAs-HEMT's device.

Sang-Sub Song was born in Korea on Mar. 5, 1979. He received the B.S. degree in Electronics Engineering at University of Seoul, Seoul, Korea, in 2002, the M.S. degree from Electrical Engineering at Seoul National University, Seoul, Korea,

in 2004. Now he pursuits the Ph.D degree in Electrical Engineering and Computer Science at Seoul National University, Seoul, Korea. His current research activities include the design and fabrication of MMICs and MMIC modules using Flip-Chip technology.

Jae-Hak Lee received the B.S. degree in Electrical Engineering from Seoul National University, Seoul, Korea in 1988, the M. S. degree in Electronic and Electrical Engineering from Pohang University of Science and Technology, Pohang,

Korea in 1990 and the Ph. D. degree in Electrical Engineering and Computer Science from Seoul National University, Seoul, Korea in 2001, respectively. He worked at LG Electronics Institute of Technology, Seoul, Korea, from 1990 to 2001, where he engaged in the development of GaAs MESFET and HEMT MMIC processes. Currently, he is at Wavics Inc., Seoul, Korea. His present interests include III-V microwave and millimeter-wave device designs and process developments, and MMIC designs.

**Kwang-Seok Seo** received the B.S. degree from Seoul National University in 1976, and the M.S. degree from the Korea Advanced Institute of Science and Technology in 1978, and the Ph.D. degree on electrical engineering from the

University of Michigan, Ann Arbor in 1987. From 1978 to 1982, he was a senior research engineering at the korea Institute of electronics Technology. From 1987 to 1988, he was a postdoctoral fellow at the IBM T.J. Watson Research Center. Since 1989, he has been with Seoul National University, where he is now a Professor in the School of Electrical engineering and Computer science. His current interests include high speed device physics and technology, compound semiconductor materials, and high frequency circuit design.