# A New Reference Cell for 1T-1MTJ MRAM

S. Y. Lee, H. J. Kim, S. J. Lee, and H. S. Shin

Abstract—We propose a novel sensing scheme, which operates by sensing the difference in voltage between a memory cell and a reference cell for a magnetoresistive random access memory (MRAM). A new midpoint-reference generation circuit is adopted for the reference cell to improve the sensing margin and to guarantee correct operation of sensing circuit for wide range of tunnel magneto resistance (TMR) voltages. In this scheme, the output voltage of the reference cell becomes nearly the midpoint between the cell voltages of high and low states even if the voltage across the magnetic tunnel junction (MTJ) varies.

### I. Introduction

A recent advancement in memory devices involves spintronics, which combines semiconductor technology of electronics and spin technology of magnetics. The spin of an electron, rather than the electron charge, is used to indicate the logic '0' or logic '1'. One such spintronic device is a MRAM, which has several advantages including nonvolatile storage, unlimited read and write endurance, low power, high density and high speed. [1-5] MRAM basically includes giant magnetoresistive (GMR) element or magnetic tunneling junction (MTJ) element, bit line, digit line, and word line. The MRAM employs the magnetic vectors to store memory states. Magnetic vectors in the layers of GMR or MTJ are switched very quickly from one direction to an opposite direction when a magnetic field is applied to the

magnetic material over a certain threshold or intensity. But, less current is required to switch the magnetic vectors in free layer of MTJ that has more large cell resistance in comparison with GMR. Also, a MTJ element is more sensitive to the applied field and has better magneto-resistance (MR) ratio than a GMR element. [6]

1T-1MTJ structure and 2T-2MTJ structure are representative cell structures in MRAM, the former requires less area than the latter. However, MRAM based on 1T-1MTJ structure needs to have a reference cell so that the stored information can be sensed. Since the magneto resistance (MR) ratio depends strongly on the voltage applied to the MTJ and is reduced considerably when the voltage across the MTJ reaches a critical voltage, it is important to improve the reliability and stability of memory operations. This is especially true in a MRAM architecture that has a reference voltage generation circuit for read data decision. In this work, we propose a new reference cell-sensing scheme for 1T-1MTJ MRAM and present simulation results based on a HSPICE macro-model of MTJ that we have developed. [7]

# II. A NEW REFERENCE CELL FOR 1T-1MTJ MRAM

A typical MRAM device includes word lines and digit lines extended along rows of the memory cells, and bit lines extended along columns of the memory cells. Each memory cell is located at a cross point of a digit line and a bit line and is connected to a pass transistor. Also, a typical MRAM device based on IT-1MTJ structures includes an array of memory cell block, and an array of reference cell block and a comparator. A reference cell block generates a reference signal that can

Manuscript received May 30, 2004; revised June 19, 2004.

Ewha Womans University, Seoul 120-750

PACS numbers: 85.30.De FAX: 02-3277-3494 E-mail: slee@ewha.ac.kr be used to determine the resistance states of each memory cell in the array, despite the variations in resistance due to manufacturing tolerances and other factors such as temperature gradients across the array, electromagnetic interference and bias voltages across the MTJ memory cell. It is especially important characteristics in MRAM that the MTJ resistance varies with the voltage applied to the MTJ, and the MR ratio is reduced considerably when the voltage across the MTJ reaches a critical voltage.

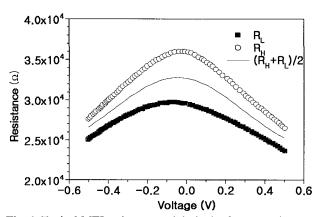

In order to read an MRAM cell based on 1T-1MTJ structure, it is necessary to have a reference cell so that the stored information can be sensed. Therefore, in recent technology MRAM cells, the reference cell is located therein of the memory cell array area, includes the same structure as a memory cell based on 1T-1MTJ so that more accurate sensing operation is possible. However it is still far from perfect because the tunneling magneto resistance (TMR) varies with the voltage applied to the MTJ. Figure 1 shows an above-mentioned characteristic that is about varied magneto-resistances with the bias voltage across the MTJ. The MR ratio depends strongly on the voltage applied to the MTJ and is reduced by half when the applied voltage reaches 400mV, as shown in the figure. Therefore, the reference resistance is required to be maintained at (R<sub>L</sub>+R<sub>H</sub>)/2 even if the applied bias voltage changes (solid line).

Fig. 1. Typical MTJ resistance and desired reference resistance as a function of bias voltage.

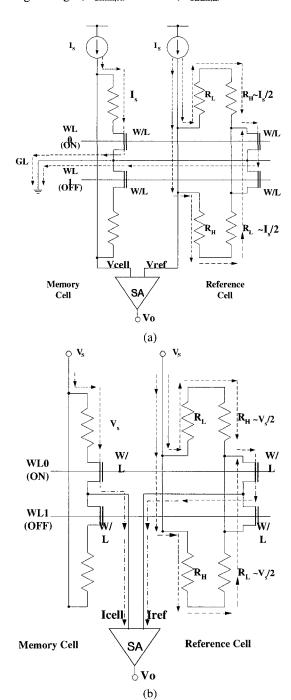

Figure 2(a) shows a schematic of conventional reference cell and current forcing sensing scheme in MRAM. [8] The stored cell data, either  $R_H$  or  $R_L$ , is read by detecting the voltage difference between a memory cell and a reference cell. In this scheme,  $I_S$  supplied by the current source of reference part is divided into two equal

parts and the voltage across each MTJ of reference cell is almost half compared with that across a memory cell. Accordingly,  $V_{\text{REF}}$  differs from the midpoint between cell voltage of high ( $V_{\text{CELL,H}}$ ) and low ( $V_{\text{CELL,L}}$ ) states.

Fig. 2. (a) Schematics of the conventional reference cell and current forcing sensing scheme and (b) schematics of the conventional reference cell and voltage forcing sensing scheme.

Figure 2(b) shows another schematic of conventional reference cell and voltage forcing sensing scheme in

MRAM. The stored cell data, either R<sub>H</sub> or R<sub>L</sub>, is read by detecting the current difference between a memory cell and a reference cell. In this scheme, V<sub>S</sub> supplied by the voltage source of reference part is divided into two resistors connected serially and the voltage across each MTJ of reference cell is almost half compared with that across a memory cell. Accordingly, I<sub>REF</sub> differs from the midpoint between cell current of high (I<sub>CELL,H</sub>) and low (I<sub>CELL,L</sub>) states. As a result, the reference resistances of these conventional reference cells deviate from the medium value, and the sensing margin is reduced. [9] That may even result in incorrect sensing.

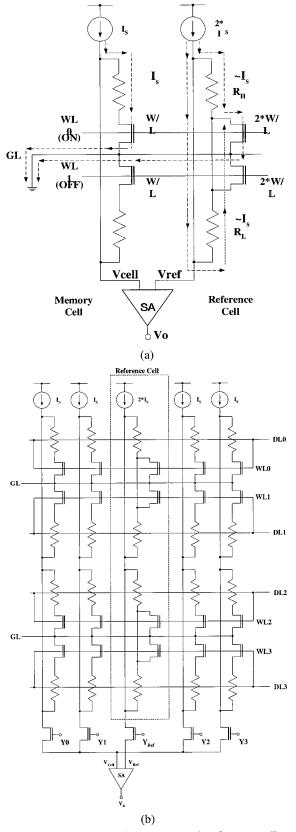

In this work, we propose a new midpoint referencecell sensing scheme for 1T-1MTJ MRAM. As shown in Fig. 3(a), the reference cell consists of a pair of MTJ element connected in parallel each of which has a value of R<sub>H</sub> and R<sub>L</sub>, respectively. The current source applied to the reference cell draws twice of the current flowing into the memory cell and the current driving capability of reference cell pass-TR is twice as large as that of memory cell pass-TR. In this case, the reference resistance remains very close to (R<sub>L</sub>+R<sub>H</sub>)/2 even when the applied bias voltage varies since the voltage applied to the MTJ of reference cell is about the same with the voltage applied to that of the memory cell. Therefore, V<sub>REF</sub> becomes nearly (V<sub>CELL,H</sub>+ V<sub>CELL,L</sub>)/2, which improves sensing margin and makes a stable sensing possible. Figure 3(b) shows an array example of proposed reference cell. A reference cell column is placed per memory cell block and belongs to both memory cells. A certain column of memory cell block is selected by column select-TR positioned at the underside of circuit and compares with the reference cell column.

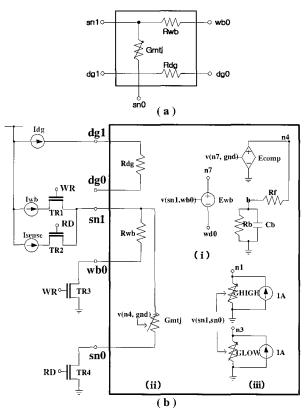

We have developed the macro-model for MTJ applicable to HSPICE circuit simulator. [7] As shown in Fig. 4(a), the macro-model is realized as a five-terminal sub-circuit that reproduces MTJ characteristics including hysteresis, asteroids with thermal variation, and R-V characteristics. This model includes the nodes of sn1, sn0, wb0, dg1, dg0 and the resistors of Rwb, Rdg, and Gmtj. Rwb is the bit line resistance per cell and Rdg is the digit line resistance per cell. Gmtj is the voltage-controlled resistor and it corresponds to the effective TMR value. Sn1~wb0 is the bit line located above the MTJ cell, through which write bit line current (Iwb) flows and dg1~dg0 is the digit line located below the

**Fig. 3.** (a) Schematics of the proposed reference cell and current forcing sensing scheme and (b) an array example of the proposed reference cell.

MTJ cell, through which digit line current (Idg) flows for writing operation. Sense current (Isense) flows through MTJ from sn1 to sn0 for reading operation and the pass transistor is connected to the node sn0.

Fig. 4. (a) Block diagram and (b) schematic of macro-model for MTI

- Embodiments of the hysteresis and the asteroid curve dependent on the operating temperature of MTJ.

- (ii) Actual TMR values of MTJ having hysteresis, asteroid curve and R-V characteristics.

- (iii) Embodiments of R-V characteristics for MTJ.

Figure 4(b) shows the schematics of the entire subcircuits contained in the macro-model. The sub-circuits can be divided into three parts: (i) comparator circuit, (ii) effective MTJ corresponding circuit, and (iii) gaussian fitting circuit. TR1 and TR3 outside the box are turned-on, whereas, TR2 and TR4 outside the box are turned-off by WR signals for writing operation. In case of reading operation, TR2 and TR4 are turned-on, whereas, TR1 and TR3 are turned-off by RD signals. The active Gmtj of part (ii) reproduces the hysteretic and the asteroid characteristics, shrinking with the increase of operating temperature, by part (i) during the writing operation.

And Gmtj reproduces the R-V characteristic by part (iii) during the reading operation. A plot of the hysteresis with varying Idg, simulated with HSPICE, is shown in Fig. 5(a). The left-hand waveform shows the results simulated while Idg flows from dg1 to dg0, and the right-hand one shows the results simulated while Idg flows from dg0 to dg1. The hysteresis shrinks as the magnitude of Idg increases. Similarly, we confirmed that the hysteresis shrinks as the operating temperature increases. Figure 5(b) shows the asteroid curve, which is simulated with various Idgs, while the operating temperature of the cell varies. As shown in Fig. 5(c), the circuit macro-model accurately emulates the R-V characteristic of an actual MTJ. The simulation was done with varying Isense. It can be observed how well the macro-model reproduces the MTJ characteristics including hysteresis, asteroids dependent operating temperature, and R-V characteristics.

(a) Hysteresis with varying Idg, when the cell operates at 25°C.

- (b) Temperature dependencies of asteroid curve for MTJ.

- (c) TMR resistance of MTJ as a function of bias voltage.

# III. SIMULATION RESULTS

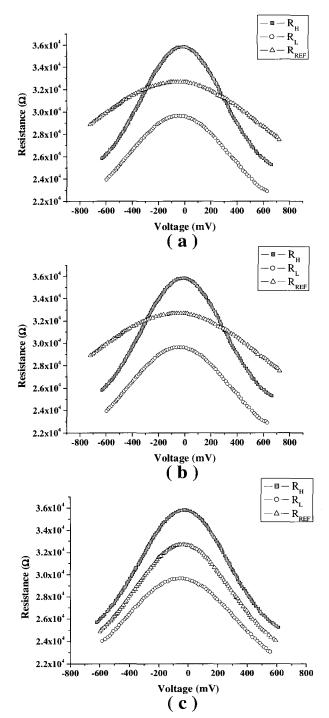

HSPICE simulations of the new reference cell for 1T-1MTJ MRAM are performed using a macro-model that is able to reproduce the hysteresis, the asteroids dependent on the operating temperature of the cell, and the R-V characteristics of MTJ. [7] Figure 6(a), (b) show reference cell resistances as a function of bias voltages in the conventional reference cells for current forcing scheme and voltage forcing scheme, respectively. The reference cell resistance doesn't stay at the middle of high and low resistance. It becomes even greater than the high resistance when the voltage across MTJ exceeds 300mv, which makes MR ratio worse and even produces incorrect sensing.

Figure 6(c) shows a reference cell resistance as a function of bias voltage for the proposed reference cell scheme. In comparison to the conventional reference cell schemes, the reference cell resistance of proposed scheme always maintains at the near of midpoint between R<sub>H</sub> and R<sub>L</sub> for a wide range of applied voltage. It is because the similar amount of voltage is applied to the memory cell and the reference cell. Table 1 shows the deviation of reference resistances for conventional and proposed reference cells from the  $(R_L+R_H)/2$ . Conventional reference cell shows deviations over 16.33%, which increase with the bias voltage across the MTJ. However, in proposed reference cell, the maximum deviation is 0.92% when the bias voltage is zero. The reference resistance of the proposed reference cell approaches to the (R<sub>L</sub>+R<sub>H</sub>)/2 when the bias voltage across the MTJ increases. This nearly accurate midpoint reference resistance improves the sensing margin and robust sensing operation is possible for wide range of voltages.

**Table 1.** The deviations of reference resistances for conventional reference cell and proposed reference cell from the  $(R_L+R_H)/2$ .

| V(m)                                    | -500  | -400  | -300  | -200  | -100  | 0     | 100   | 200   | 300   | 400   | 500   |

|-----------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| (R <sub>H</sub> +R <sub>.</sub> )/2(kΩ) | 26.55 | 28.27 | 30.09 | 31.64 | 32.57 | 3264  | 31.82 | 30.32 | 28.50 | 26.72 | 25.23 |

| R <sub>p</sub> (kΩ)                     | 26.49 | 28.19 | 29.94 | 31.43 | 32.30 | 32.34 | 31.55 | 30.11 | 28.35 | 26.61 | 25.14 |

| R <sub>cow</sub> (kΩ)                   | 30.82 | 31.56 | 32.14 | 32.54 | 32.71 | 32.64 | 3232  | 31.79 | 31.08 | 30.25 | 29.35 |

| Proposed (%)                            | 0.23  | 0.28  | 0.50  | 0.66  | 0.83  | 0.92  | 0.85  | 0.69  | 0.53  | 0.41  | 0.36  |

| Conventional (%)                        | 16.08 | 11.64 | 6.81  | 2.85  | 0.43  | 0.00  | 1.57  | 485   | 9.05  | 13.21 | 16.33 |

**Fig. 6.** Simulation results of the midpoint-reference generation circuits.

- (a) Reference cell resistance as a function of bias voltage in the conventional reference cell for current forcing scheme

- (b) Reference cell resistance as a function of bias voltage in the conventional reference cell for voltage forcing scheme

- (c) Reference cell resistance as a function of bias voltage in the proposed reference cell

## IV. CONCLUSIONS

In this paper, a new midpoint reference generation circuit for 1T-1MTJ MRAM utilizing a pair of MTJ connected in parallel and a current source is proposed. In comparison to the existing reference cell schemes, the proposed architecture requires much less area and is more accurate. In this scheme, the reference resistance remains very close to  $(R_L+R_H)/2$  even when the applied bias voltage varies since the voltage applied to the MTJ of reference cell is about the same with the voltage applied to that of the memory cell. Therefore,  $V_{REF}$  becomes nearly  $(V_{CELL,H}+V_{CELL,L})/2$ , which improves the sensing margin and makes a stable sensing possible. Consequently, new reference-cell circuit improves the sensing margin and guarantees correct operation of the sensing circuit for wide range of TMR voltages.

#### ACKNOWLEDGEMENT

This work was supported by the National program for Tera-Level Nanodevices of the Ministry of Science and Technology as one of the 21 century Frontier Programs.

# REFERENCES

- [1] T. Fang and J. Zhu, *IEEE Trans. Magnetics*, **37**, 1964 (2001).

- [2] G. B. Granley and A. T. Hurst, *Proc. of Nonvolatile Memory Tech. Conference* (Albuquerque, June, 1996), p. 138.

- [3] K. Lee, Y. Park, H. Min, C. Lee, and H. Shin, *J. of Korean Phys. Soc.*, **44**, 73 (2004).

- [4] H. Lee and H. Shin, *J. of Korean Phys. Soc.*, **44**, 56 (2004).

- [5] J. Lee and H. Shin, *J. of Korean Phys. Soc.*, **44**, 50 (2004).

- [6] D. Wang, M. Tondra, C. Nordman and J. M. Daughton, *IEEE Trans. magnetics*, **35**, 2886 (1999).

- [7] S. Lee et al., submitted to 2004 Symp. on VLSI Circuits.

- [8] M. Durlam et al., *Tech. Dig. of Symp. on VLSI Circuits* (Hawai, June, 2002), p.158.

- [9] H. S. Jeong et al., *Tech. Dig. of IEDM* (San Francisco, Dec., 2002), p.551.

Seung-Yeon Lee was born in Korea on May 18, 1979. She received the B.S. and the M.S. degree in Information Electronics Engineering at Ewha Womans University, Seoul, Korea in 2002 and in 2004, respectively. Now she pursues the

Ph.D degree in Information Electronics Engineering at Ewha Womans University, Seoul, Korea. Her current interests include the design of high speed and high density MRAM.

Seungjun Lee received B.S. degree in electronics engineering from Seoul National University in 1986, and M.S. and Ph.D degrees in electrical engineering and computer from the University of California at Berkeley, in 1989 and 1993,

respectively. From 1993 to 1998 he was with Hyundai Electronics Industries, where he worked on the development of 256Mb synchronous DRAM and QPSK demodulator for DVB receiver. Since 1999, he has been an Assistant Professor of Information Electronics Department at Ewha Womans University, Seoul. His research interests include the design of digital circuits, wireless communication systems, and system level design methodology. He is a member of the IEEE and the IEEK.

Hye-Jin Kim was born in Korea on April 4, 1979. She received the B.S.degree and the M.S. degree from Information Electronics Engineering at Ewha Womans University, Seoul, Koea in 2002 and 2004, respectively. Now she works at Samsung

Electronics, Hwasung, Gyeonggi-Do, Korea. Her current interests include the design of new type of non-volitile memory like MRAM and PRAM.

Hyungsoon Shin was born in Seoul, Korea, in 1959. He received B.S. in electronics engineering from the Seoul National University in 1982, M.S. and Ph.D. in electrical engineering from the University of Texas at Austin in 1984 and 1990,

respectively. From 1990 to 1994, he was with LG Semicon Co., Ltd., in Korea, where he worked on the development of 64M DRAM, 256M DRAM, 4M SRAM, and 4M FLASH memory. Since 1995, he has been a faculty member of the department of information electronics engineering at Ewha Womans University, Seoul, Korea. His present research areas include new processes, devices, and circuit developments and modeling based on Si, both for high density memory and RF IC. He has published numerous journal articles on implant profile models, mobility models, deepsubmicron MOSFET structure analysis, current crowding effect in diagonal MOSFET, hot-carrier degradation, alpha-particle-induced soft error and MRAM. He is a senior member of the Institute of Electrical and Electronics Engineers and the Institute of Electronics Engineers of Korea. He received the Technical Excellence Award from the Semiconductor Research Corporation (SRC) in 1991.