# A New SOI LDMOSFET Structure with a Trench in the Drift Region for a PDP Scan Driver IC

Won-So Son, Sang-Gi Kim, Young-Ho Sohn, and Sie-Young Choi

To improve the characteristics of breakdown voltage and specific on-resistance, we propose a new structure for a LDMOSFET for a PDP scan driver IC based on silicon-oninsulator with a trench under the gate in the drift region. The trench reduces the electric field at the silicon surface under the gate edge in the drift region when the concentration of the drift region is high, and thereby increases the breakdown voltage and reduces the specific onresistance. The breakdown voltage and the specific onresistance of the fabricated device is 352 V and 18.8 m $\Omega$ cm² with a threshold voltage of 1.0 V. The breakdown voltage of the device in the on-state is over 200 V and the saturation current at  $V_{\rm gs}$ =5 V and  $V_{\rm ds}$ =20 V is 16 mA with a gate width of 150  $\mu$ m.

Keywords: lateral double-diffused MOSFET (LDMOSFET), trench, silicon-on-insulator (SOI), power integrated circuit (PIC).

## I. Introduction

Intelligent power integrated circuits have become increasingly popular for implementing system functions with improved performance, reduced size, low cost, and low power consumption. For example the flat panel display industry has made effective use of power integrated circuits (PICs) to offer improved features. In particular, a plasma display panel requires power devices with a breakdown voltage above 100 V in the data driver IC or 250 V in the scan driver IC [1]. Currently, a lateral double-diffused MOSFET (LDMOSFET) structure is commonly used in such circuits. Yet, in the case of LDMOSFET, the use of fine lithography cannot reduce the size imposed by the drift region, as the breakdown voltage of an LDMOSFET is a function of the doping and length of the drift region [2]. Many studies have reported on the specific onresistance (R<sub>on</sub>) and breakdown voltage improvement of LDMOSFET devices [3]-[7]. The silicon-on-insulator (SOI) has emerged as the technology of choice for fabricating PICs, because the buried oxide provides an effective way of isolating the low-power CMOS from the high-side and low-side power devices, thereby preventing such problems as induced overvoltages and latch-up, without having to resort to using expensive deep wells. This advantage has spawned a great interest in fabricating PICs with an SOI [8]-[10].

Accordingly, the current study proposes a new type of LDMOSFET, called a trench LDMOSFET, based on an SOI in which a trench is applied under the gate in the drift region, and the electric characteristics are investigated using a process simulation program, ATHENA, and a 2-D device simulation program, ATLAS. By including a trench in the device, the electric field under the gate edge is alleviated and the doping concentration of the n-drift region can be increased, thereby

Manuscript received Sept. 9, 2003; revised Nov. 7, 2003.

Won-So Son (phone: +82 53 950 6837, email:ogong999@palgong.knu.ac.kr) and Sie-Young Choi (email:sychoi@ee.knu.ac.kr) are with School of Electrical Engineering and Computer Science, Kyungpook National University, Daegu, Korea.

Sang-Gi Kim (email: sgkim@etri.re.kr) is with Basic Research Laborotory, ETRI, Daejeon, Korea.

Young-Ho Sohn (email: ysohn1@hanmail.net) is with School of Electrical Engineering and Computer Science, Yeungnam University, Gyongbuk, Korea.

increasing the breakdown voltage and reducing the specific onresistance. As a result, the trade-off between the breakdown voltage and the  $R_{\text{on}}$  is improved.

### II. Device Structures and Simulation Results

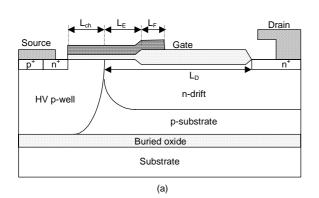

Schematic cross sections of the conventional LOCOS LDMOSFET and the proposed trench LDMOSFET are shown in Fig. 1. Generally, the breakdown voltage of the conventional SOI LDMOSFET is limited by the buried oxide thickness, SOI thickness, the drift region length and the drift region concentration. To compare the characteristics of the proposed trench LDMOSFET with the conventional LOCOS LDMOSFET, the basic parameters of the structure, except the drift region dose and the trench depth, were fixed as follows.

We used an SOI silicon wafer with an 8  $\mu$ m active layer on 3.0  $\mu$ m buried oxide and a p-substrate with a concentration of  $1 \times 10^{15}$  cm<sup>-3</sup>. Boron was doped with a dose of  $5 \times 10^{12}$  cm<sup>-2</sup> for the high voltage (HV) p-well and the phosphorus was doped with the various doses for the n-drift region to achieve a maximum breakdown voltage. The channel length ( $L_{ch}$ ) and gate extension ( $L_{E}$ ) were 3  $\mu$ m, the gate extension over the field ( $L_{F}$ ) was 2  $\mu$ m, the gate oxide thickness was 500 Å, and the drift region length ( $L_{D}$ ) was 16  $\mu$ m. The thickness of LOCOS

Fig. 1. The cross sections of (a) the conventional LOCOS LDMOSFET and (b) the proposed trench LDMOSFET.

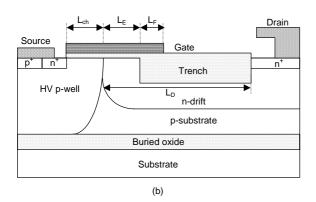

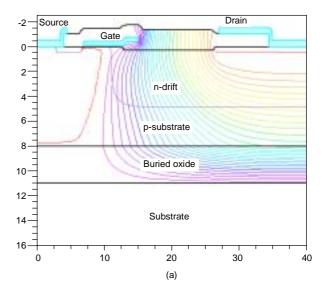

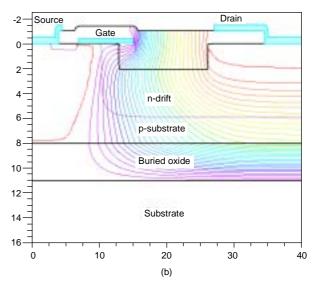

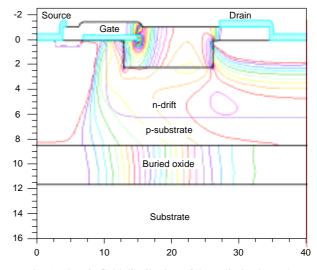

Fig. 2. Potential distribution of (a) the conventional LOCOS LDMOSFET and (b) the proposed trench LDMOSFET at 305 V.

for the conventional LOCOS LDMOSFET was 6000 Å, while the trench depth was the key parameter for the proposed trench LDMOSFET when the trench width was fixed at 13  $\mu m$ .

The main performance parameters for smart power devices are  $R_{on}$  and the breakdown voltage, which are inversely related to each other. As such, the optimum design between the breakdown voltage and the  $R_{on}$  is the main issue for high voltage LDMOSFET devices. A trench under the gate edge in the drift region can increase the breakdown voltage by reducing the electric field there, while slightly reducing the  $R_{on}$  by increasing the doping concentration of the drift region. Figure 2 shows the potential distribution of the conventional LOCOS LDMOSFET and the proposed trench LDMOSFET at 305 V, which is the breakdown voltage of the conventional LOCOS

LDMOSFET. In the conventional LOCOS LDMOSFET, the potential was crowded at the gate edge, resulting in a high electric field under the gate edge; however, the thickness of the LOCOS under the gate could not sufficiently reduce the electric field. Thus, to improve the breakdown voltage characteristics, the oxide thickness under the gate needed to be thicker than the LOCOS to reduce the electric field under the gate edge. One way to increase the oxide thickness would be to apply a trench. As in the conventional LOCOS LDMOSFET, the potential was crowded at the gate edge; however, the oxide thickness under the gate edge in the proposed trench LDMOSFET was thicker than that in the conventional LOCOS LDMOSFET so the potential crowding was reduced (Fig. 2 (b)) and the electric filed was reduced under the gate edge.

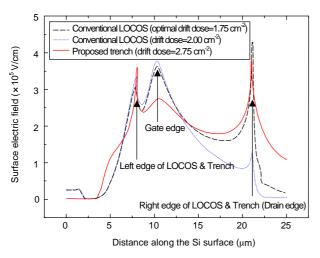

In the conventional LOCOS LDMOSFET, the breakdown voltage was 305 V with an optimized drift dose of  $1.75 \times 10^{12}$ cm<sup>-2</sup> when the drift region length was 16 µm and the peak electric field was located at the edge of the drain. Yet, when the drift dose was increased to  $2.0 \times 10^{12}$  cm<sup>-2</sup> to reduce the R<sub>on</sub>, because the Ron for high voltage devices with a breakdown voltage over 100 V was mainly determined by the drift region resistance [11], the peak electric field position was changed to the gate edge and the breakdown voltage was drastically reduced to 258 V. Therefore, to increase the breakdown voltage with a higher dose than the optimal dose by alleviating the electric field at the gate edge, we created a trench under the gate in the drift region because oxide in a trench can withstand a higher voltage than silicon. In the proposed trench LDMOSFET, the optimized drift dose was  $2.75 \times 10^{12}$  cm<sup>-2</sup> when the depth and the width of the trench were 1.25 and 13 µm, respectively, the total gate length was  $8\,\mu m$ , and the field plate on the trench was 2 µm. The peaks of the electric field within the trench

Fig. 3. Electric field distributions at the silicon surface of the conventional LOCOS LDMOSFET and the proposed trench LDMOSFET with trench depth of 1.25 µm.

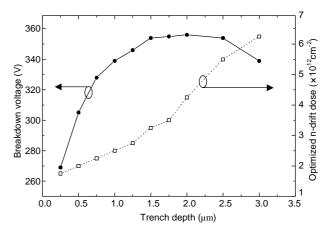

Fig. 4. Effects of the trench depth on the drift dose and the breakdown voltage.

Fig. 5. Electric field distribution of the optimized trench LDMOSFET at breakdown.

LDMOSFET at breakdown were located at the right and left edges of the trench (Fig. 3). As a result, the breakdown voltage increased from 305 V for the conventional LOCOS device to 346 V for the trench device.

Figure 4 shows the effects of the trench depth and the drift dose on the breakdown voltage, both of which had a significant impact on the device characteristics. With the same doping concentration of the drift region, when the trench became deeper, the electric field at the right edge of the trench increased due to the potential crowding, and breakdown occurred. Therefore, to alleviate the electric field at the right edge of the trench, we needed to increase the drift doping concentration. With the same trench depth, when the drift dose was higher than the optimal dose, the breakdown occurred at the left edge of the trench, yet when the drift dose was lower than the optimal dose, breakdown occurred at the right edge of the

trench. The maximum breakdown voltage of 356 V was obtained when the trench depth was 2  $\mu$ m and the drift dose was  $4.25 \times 10^{12}$  cm<sup>-2</sup>, which was three times the drift dose of the optimized conventional LOCOS LDMOSFET. Under these conditions, the peak electric field moved to the bulk (Fig. 5). However, when the trench depth was over 2  $\mu$ m, the breakdown voltage began to decrease; since the higher dose could not catch the trench depth, the electric field at the right edge increased due to the potential crowding.

The simulated breakdown voltages and the specific onresistances of the LDMOSFET devices with the conventional LOCOS field oxide and the trench filled with oxide were 305 V,  $356 \, \text{V}$  and  $17.1 \, \text{m}\Omega \cdot \text{cm}^2$ ,  $16.6 \, \text{m}\Omega \cdot \text{cm}^2$ , respectively.

### III. Device Fabrication and Results

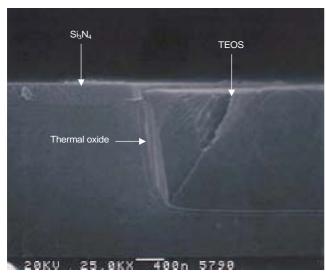

We designed and implemented a new device for a 350 V SOI LDMOSFET for a PDP scan driver IC. We used a 2-D simulator ATHENA to design the various processing steps [12]. The starting SOI substrates had an 8 µm-thick silicon layer and 3 µm-thick buried oxide. The background doping concentration of the silicon layer was  $1 \times 10^{15}$  cm<sup>-3</sup>. We used the standard CMOS process except for the trench formation process. The process began with ion implantation for the p-well and the ndrift region. The doses for the p-well and n-drift regions were  $5 \times 10^{12}$  cm<sup>-2</sup> and  $3.5 \times 10^{12}$  cm<sup>-2</sup>, respectively. The drive-in step was performed in an inert ambient at 1200 °C for a uniform drift region with a junction depth of 5.5 µm from the result of ATHENA. After that, we formed a trench by silicon etching using HBr/He-O<sub>2</sub>/SiF<sub>4</sub> by MERIE (P-5000, AMK) [13]. To make the surface of the trench smooth, we performed wet oxidation for 10 min at 1000 °C. We used chemical mechanical

Fig. 6. Cross section of the trench after CMP process. The trench depth is  $1.5 \mu m$ .

polishing (CMP) for the planar process. The depth of the trench was 1.5  $\mu$ m. We used silicon nitride of 4000 — as the barrier during the CMP process. Figure 6 shows a cross section view of the trench after CMP.

The gate oxide of 500 was thermally grown and the poly-silicon of 5000 was deposited by LPCVD and doped with POCl<sub>3</sub>. We then carried out a phosphorous implantation to dope the drain and the source regions with a dose of  $3 \times 10^{15}$  cm<sup>-2</sup> and an energy of 80 keV. After this, we implanted boron to form the contact to the high voltage p-well next to the source with a dose of  $5 \times 10^{15}$  cm<sup>-2</sup> and energy of 50 keV. Finally, metallization was followed by sputtering of Al to form metal electrodes. The wafer was then sintered for 30 min at 400 °C.

We used an HP4155A precision semiconductor parameter analyzer to measure the breakdown voltage, the threshold voltage, and the specific on-resistance, and a Tektronix programmable curve tracer 370A to evaluate the electrical characteristics.

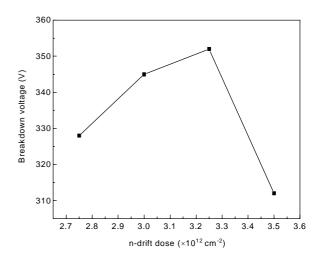

Figure 7 shows the breakdown voltage characteristics according to the n-drift dose for the proposed trench LDMOSFET. The optimized dose was  $3.25 \times 10^{12}$  cm<sup>-2</sup> with a breakdown voltage of 352 V.

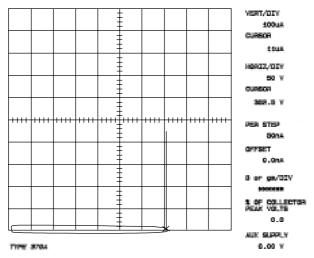

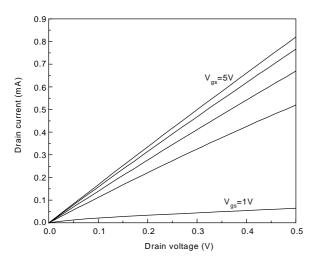

Figure 8 shows the breakdown characteristics of the proposed trench LDMOSFET, and Fig. 9 shows the on-state characteristics. At  $V_{ds}=0.1$  V the threshold voltage was 1.0 V. At  $V_{gs}=5$  V, based on the current-voltage characteristics in Fig. 8, the calculated specific on-resistance for the device was 18.8 m $\Omega$ ·cm<sup>2</sup> with the drain current of 168  $\mu$ A at  $V_{ds}=0.1$  V when the area of the device was  $3.15 \times 10^{-5}$  cm<sup>2</sup>.

$$R_{on} = 0.1 \text{ V} / 168 \,\mu\text{A} \times 3.15 \times 10^{-5} \,\text{cm}^2 = 18.8 \,\text{m}\Omega \cdot \text{cm}^2$$

The specific on-resistance of  $18.8 \text{ m}\Omega\text{-cm}^2$  was lower than any other published work for SOI LDMOSFET devices [14]-[15].

Fig. 7. Breakdown voltage characteristics of the proposed trench LDMOSFET based on the n-drift dose.

Fig. 8. Breakdown characteristics of the proposed trench LDMOSFET.

Fig. 9. Forward on-resistance characteristics of the proposed trench LDMOSFET.

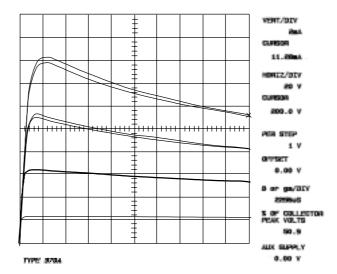

Figure 10 shows the forward conduction characteristics of the proposed trench LDMOSFET. The saturation drain current at  $V_{gs}$ =5 V and  $V_{ds}$ =20 V was 16 mA with a gate width of 150  $\mu$ m. The breakdown voltage of the proposed trench LDMOSFET in the on-state was over 200 V, which demonstrates that the device of the proposed trench LDMOSFET is good for a device in the output stage of a PDP scan driver IC.

# IV. Conclusion

We proposed a new high voltage LDMOSFET structure for a PDP scan driver IC and developed it so as to increase the breakdown and on-resistance characteristics. The proposed structure has a trench under the gate in the drift region; with this structure the electric field at the silicon surface under the gate

Fig. 10. Forward conduction characteristics of the proposed trench LDMOSFET.

edge was reduced so the breakdown voltage could be increased, and drift dose could be increased so the specific on-resistance could be reduced. The breakdown voltage and the specific on-resistance of the fabricated device was 352 V and  $18.8~\mathrm{m}\Omega\mathrm{\cdot cm}^2$  with a threshold voltage of 1.0 V. The breakdown voltage of the device in the on-state was over 200 V and the saturation current at  $V_{\rm gs}\!\!=\!\!5$  V and  $V_{\rm ds}\!\!=\!\!20$  V was 16 mA with a gate width of 150  $\mu\mathrm{m}$ .

### References

- [1] Kenya Kobayashi, Hiroshi Yanagigawa, Kazuhisa Mori, Suichi Yamanaka, and Akira Fujiwara, "High Voltage SOI CMOS IC Technology for Driving Plasma Display Panels," Proc. ISPSD '98, 1998, pp. 141-144.

- [2] S. Merchant, E. Arnold, H. Baumgart, R. Egloff, T. Letavic, S. Mukherjee, and H. Pein, "Dependence of Breakdown Voltage on Drift Length and Buried Oxide Thickness in SOI RESURF LDMOS Transistor," *Proc. ISPSD '93*, 1993, pp. 124-128.

- [3] P.G.Y. Tsui, P.V. Gilbert, and S.W. Sun, "Integration of Power LDMOS into a Low-Voltage 0.5 mm BiCMOS Technology," *IEEE IEDM Digest*, 1992, pp. 27-30.

- [4] L. Vestling, B. Edhholm, J. Olsson, S. Tiensuu, and A. Soderbrag, "A Novel High-Frequency LDMOS Transistor Using an Extended Gate RESURF Technology," *Proc. ISPSD '97*, 1997, pp. 45-48.

- [5] Jongdae Kim, Sang-Gi Kim, Tae Moon Roh, Hoon Soo Park, Jin-Gun Koo, and Dae Yong Kim, "Characteristics of P-Channel SOI LDMOS Transistor with Tapered Field Oxides," *ETRI J.*, vol. 21, no. 3, 1999, pp. 22-27.

- [6] Cheon Soo Kim, Sung Do Kim, Mun-Yang Park, and Hyun-Kyu Yu, "Trenched-Sinker LDMOSFET (TS-LDMOS) Structure for 2 GHz Power Amplifiers," ETRI J., vol. 25, no. 3, 2003, pp. 195-202.

- [7] Tae Moon Roh, Dae Woo Lee, Yil Suk Yang, Jin Gun Koo, and Jongdae Kim, "Breakdown Voltage Improvement of p-LDMOSFET with an Uneven Racetrack Source for PDP Driver IC Applications," ETRI J., vol. 24, no. 4, Aug. 2002, pp. 328-331.

- [8]T. Letavic, E. Arnold, M. Simpson, E. Peters, R. Aquino, R. Egloff, S. Wong, and S. Mukherjee, "600 V Single-Chip Power Conversion System Based on Thin Layer Silicon-on-Insulator," *Proc.* 1998 IEEE Int'l SOI Conf., 1998, pp. 133-134.

- [9] A. Nakagawa, N. Yasuhara, I. Omura, Y. Yamaguchie, T. Ogura, and T. Matsudai, "Prospects of High Voltage Power ICs on Thin SOI" (invited paper), *IEDM Tech. Dig.*, 1992, pp. 229-232.

- [10] M. Stoisiek, K.G. Oppermaun, U. Schwalke, D. Takacs, "A Dielectric Isolated High-Voltage IC-Technology for Off-Line Applications," *Proc. ISPSD* '95, 1995, pp. 325-329.

- [11] B. J. Baliga, *Power Semiconductor Devices*, PWS, Boston, 1996.

- [12] ATHENA User's Manual, SILVACO Int'l, Santa Clara, CA, 2000.

- [13] Jongdae Kim, Tae Moon Roh, Sang-Gi Kim, Il-Yong Park, Yil Suk Yang, Dae-Woo Lee, Jin-Gun Koo, Kyoung-Ik Cho, and Young Il Kang, "A Novel Process for Fabricating High Density Trench MOSFETs for DC-DC Converters," *ETRI J.*, vol. 24, no. 5, 2002, pp. 333-340.

- [14] D.M. Garner, F. Udrea, H.T. Lim, G. Ensell, A.E. Popescu, K. Sheng, and W.I. Milne, "Silicon-on-Insulator Power Integrated Circuits," *Microelectronics J.*, vol. 32, 2001, pp. 517-526.

- [15] A.K. Paul, Y.K. Leung, J.D. Plummer, S.S. Wong, S.C. Kuehne, V.S.K. Huang, and C.T. Nguyen, "High Voltage LDMOS Transistors in Sub-Micron SOI Films," *Proc. ISPSD* '96, 1996, pp. 89-92.

Won-So Son is a final year PhD student and received MS degree in electronics from Kyungpook National University, Daegu, Korea in 1997. From 1997 to 2000, he had joined LG Semicon Corporation, Chungju, Korea, where he had been working on the analysis of the device and product failure from 64M SDRAM

to 256M SDRAM. He is studying on the power MOSFET for flat panel display, especially LDMOSFET using SOI. His interests are in FPD driver, power devices, and SOI-based technology.

Sang-Gi Kim received the MS and PhD degrees, all in department of physics from Yeungnam University, Gyongbuk, Korea, in 1989 and 1996, respectively. In 1981, he joined Electronics and Telecommunications Research Institute, Daejeon, Korea, where he has been working on materials science and device

characterization in advanced LDMOS and power devices technologies. His work also includes a development of oxide, silicon, and metal dry etching process, and a development of CMP process, and the development of trench etching and trench gate device technologies.

of Electronics from Kyungpook National University, Daegu, Korea, in 1989, and the PhD in electrical engineering from Texas A&M, Texas, USA, in 2002. In 2002, he joined the School of Electrical Engineering and Computer Science of Yeungnam University as a Visiting

Young-Ho Sohn received the BS in Department

Professor (BK21).

**Sie-Young Choi** received the BS and MS degree in electronics from Kyungpook National University, Daegu, Korea, in 1972 and 1974, respectively, and the PhD degree from Tohoku University, Sendai, Japan, in 1986. He was a Visiting Professor at Department of Electrical and Computer Engineering, Louisiana

University, LA, USA during the period of December 1989 to December 1990. He is currently a Professor in the School of Electronic and Electrical Engineering, Kyungpook National University, Daegu, Korea. He has served as Director of the Institute of Electronic Technology in Kyungpook National University, since 1999. He has performed research on semiconductor devices, semiconductor process technology, display device, and physical sensors, since 1974.