# Comparison of retention characteristics of ferroelectric capacitors with Pb(Zr, Ti)O<sub>3</sub> films deposited by various methods for high-density non-volatile memory.

Sangmin Shin, Mirko Hofmann, Yong Kyun Lee, June Mo Koo, Choong Rae Cho, June Key Lee, Youngsoo Park, Kyu Mann Lee, and Yoon Jong Song

Abstract—We investigated the polarization retention characteristics of ferroelectric capacitors with Pb(Zr,Ti)O<sub>3</sub> (PZT) thin films which were fabricated by different deposition methods. In thermally-accelerated retention tests, PZT films which were prepared by a chemical solution deposition (CSD) method showed rapid decay of retained polarization charges as the thickness of the films decreased down to 100 nm, while the films which were grown by metal organic chemical vapor deposition (MOCVD) retained relatively large nonvolatile charges at the corresponding thickness. We concluded that in the CSD-grown films, the thicker interfacial passive layer compared with the MOCVDgrown films had an unfavorable effect on retention behavior. We observed the existence of such interfacial layers by extrapolation of the total capacitance with thickness of the films and the capacitance of these layers was larger in MOCVDgrown films than in CSD-grown films. Due to incomplete compensation of surface polarization charges by the free charges in the metal electrodes, the interfacial field activated the space charges inside the interfacial layers and deposited them at the boundary between the ferroelectric layer and the interfacial layer. Such space charges built up an internal field inside the films, which interfered with domain wall motion, so that retention property at last became degraded. We observed less imprint which was a result of less internal field in MOCVD-grown films while large imprint was observed in CSD-grown films.

*Index Terms*—PZT, MOCVD, CSD(sol-gel), FRAM, retention, ferroelectric, thin film.

### I. Introduction

Due to a few benefits such as low power, non-volatility of data and fast access, some kinds of non-volatile memories with smart, electric or magnetic materials have been studied and developed to new prototypes during past decades. Among them, ferroelectric random access memory (FRAM) is a promising candidate for future memory device because of its compatibility with the structure of dynamic random access memory (DRAM)[1]. However, there are some crucial issues on the reliability of FRAM such as thermal stability, fatigue, and retention. In a real application field of using PbZr<sub>x</sub>Ti<sub>1-x</sub>O<sub>3</sub> (PZT) as a material inside the ferroelectric capacitor of FRAM, fatigue, the reduction of the remnant polarization with the numerous cycles of polarity switching in the capacitor, could be much

Manuscript received August 13, 2003; revised August 28, 2003. Sangmin Shin, Mirko Hofmann, Yong Kyun Lee, June Mo Koo, Choong Rae Cho, June Key Lee, Youngsoo Park are with Materials & Devices Laboratory, Samsung Advanced Institute of Technology, Suwon 440-600, Korea

Kyu Mann Lee and Yoon Jong Song are with Process development team, Samsung Electronics, Yongin 449-900, Korea

alleviated by using oxide electrodes like  $IrO_2$ ,  $RuO_2$  and  $La_{1-x}Sr_xCoO_3$  [2,3]. But, when a ferroelectric capacitor is kept at a high temperature for a long time in a specific polarization state, the remnant polarization charge tends to decrease and it is still quite a hard problem [4,5,6] - much severer in thin ferroelectric films whose thickness is less than 100 nm.

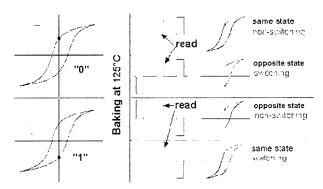

If an electrical pulse goes into a ferroelectric capacitor, the difference of charges from different remnant polarization states can distinguish one logic state, i.e. "0" from the other, i.e. "1". So, the non-volatility of data stored in ferroelectric capacitors may be defined as such charge difference between "0" and "1" states. Here, the charge difference can be termed as the non-volatile charge and its decrease in time can be called retention loss. In order to see long-time behavior of retention loss, thermal acceleration in retention test is used. One first writes the data bit of "0" or "1" in a capacitor with the electrical pulses of the corresponding polarities, bakes the capacitor at a higher temperature, and reads the data again after some time. If the poling state of the capacitor does not change before one tries to read the state, it is named as 'same-state' retention test. When one changes the state by a precedent pulse and reads the new-written state with a following pulse, then it can be 'oppositestate' retention test. And, if the capacitor jumps into an opposite polarization state during the reading pulse, we call it 'switching' test. If not, it can be termed as 'nonswitching' test. The pulse sequences are shown in Figure 1. In order to distinguish between "0" and "1" logic bits in the capacitor, the difference between switching and non-switching charges must be larger than the minimum margin of a sense amplifier. In our cumulative work so far, retention problem in the opposite state has been much severer than in the same state. Therefore, we define the non-volatile charge in our capacitor as the difference between opposite-state switching charge  $Q_{osm}$ and opposite-state non-switching charge  $Q_{osns}$ , i.e.  $P_{nv}$  =  $Q_{ossw}$  -  $Q_{osns}$ .

In our experiment, a variety of ferroelectric capacitors were tested for their retention characteristics. Ferroelectric films inside those capacitors were deposited by different methods. We revealed that the films (less than 100 nm in their thickness) grown by our chemical solution deposition (CSD) method did not guarantee a finite amount of non-volatile charge over the

**Fig. 1.** 4 kinds of retention tests and corresponding pulse sequences.

testing time, while the films grown by a metal-organic-chemical-vapor-deposition (MOCVD) method seemed to be more robust during retention test. We chose the proper width and voltage of applied pulses in order to make capacitors undergo switching saturation, and baked all the samples at the same temperature and for the same retention period.

### II. EXPERIMENTS AND RESULTS

We prepared the PZT films with thickness of 100 nm to 250 nm which were spin-coated on Pt/IrO<sub>2</sub>/Ir substrates by sol-gel method. The PZT solutions were composites of lead acetate trihydrate, titanium tetra-isopropoxide, zirconium tetra-n-propoxide, acetic acid and n-propanol. The concentration of the solution was  $0.1 \sim$ 0.4 Mole of Pb<sub>1.13</sub>Zr<sub>0.35</sub>Ti<sub>0.65</sub>O<sub>3</sub>, whose composition was abbreviated as PZT(113/35/65). Since the solution was very stable, any precipitation or gelation has not been observed during the experiment. A PbTiO3 (PTO) seed layer was used to enhance the crystallization of PZT films and the films were deposited onto Pt(100 nm)/IrO<sub>2</sub>(30 nm)/Ir(70 nm) substrate with an automatic spin-coater. And, the films were baked at 205 ~ 300 °C for 5 minutes in air on a temperature-fixed hotplate and annealed at 650 °C in N2 atmosphere incorporated with oxygen furnace for 10 minutes. Top Ir(70 nm) and IrO<sub>2</sub>(30 nm) electrodes were deposited by sputtering to improve fatigue behavior and annealed again at 550 °C for 15 minutes. Then, Ir/IrO2/PZT/Pt/IrO2/Ir structures were etched by high-density plasma etcher such as ICP (Inductively Coupled Plasma) into final capacitors with

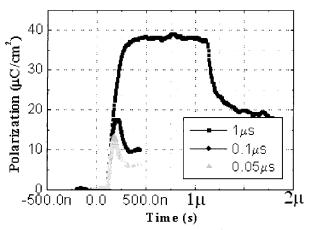

Fig. 2. Switching test on a  $50\times50~\mu\text{m}^2$  capacitor with various widths and 3 V of pulses. The PS module of TF analyzer 2000 (aixACCT Corp.) was used for the measurement.

size of  $0.45 \sim 10^4~\mu\text{m}^2$ . Those PZT films showed dominant crystallographic orientations of (111) from X-ray diffraction.

We chose  $50\times50~\mu\text{m}^2$  capacitors for our retention measurement. Figure 2 shows that those capacitors reach the saturation level of switching under pulses of 1  $\mu$ s width and 3 V height for 100 nm thick films. For comparison under the constant electric field, we increased the voltage of pulses to 5.7 V and 7.5 V on 190 nm and 250 nm thick films, respectively. Leakage current was always less than  $10^{-9}$  A even at such biases. After obtaining the normal P-V hysteresis curves for defining the initial state of the capacitors, we applied the packet of pulses onto the capacitors and baked the samples at 125 °C, and repeated pulse measurement-baking to get retained charges at each moment as depicted in Fig. 1.

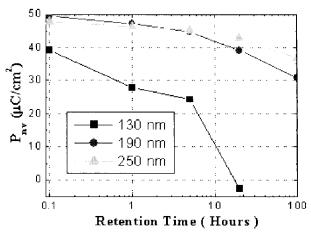

Figure 3 shows retention characteristics of capacitors with different film thickness. The non-volatile charge vanished before 20 hours in case of 100 nm thick film, while 190 nm and 250 nm thick films still showed a certain amount of non-volatile charge even after 100 hours. It could be inferred that the rearrangement of space charges along the polarization axis might occur faster in thinner films than in thicker films. The resultant internal field by space charges could reverse some domains during the delay time between the precedent pulse and the reading pulse (Fig. 1), so that it decreased  $Q_{ossis}$  and increased  $Q_{ossis}$ , finally reducing the non-

**Fig. 3.** Retention characteristics of the CSD-grown films of different thickness.

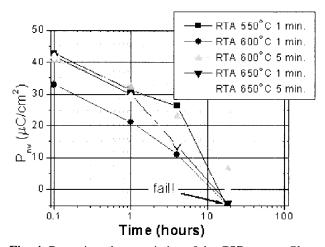

**Fig. 4.** Retention characteristics of the CSD-grown films which were annealed at different conditions.

volatile charge  $P_{nv}$ . The role of the internal field on retention loss has been published in the recent work of B. S. Kang *et al.*[7].

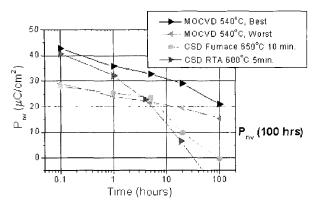

Retention loss was highly dependent on the condition of film fabrication. In Figure 4, one can see different trends of retention characteristics from capacitors made by different annealing steps. A rapid thermal annealing (RTA) step was used because it was more favorable in a real integration process. There was a little enhancement when we increased annealing time and temperature. As shown in Figure 5, annealing in a furnace for a longer time seemed to be better in retention than RTA. But, all CSD-grown films of thickness 100 nm did not retain a finite amount of non-volatile charge  $P_{nv}$  over 100 hours at 125 °C.

In order to increase capacitor density inside a memory

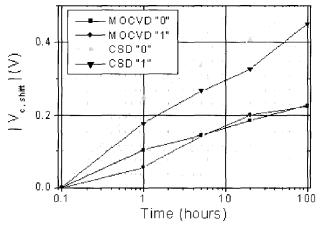

**Fig. 5.** Retention characteristics of the MOCVD-grown films and comparison with the CSD-grown films.

cell, shrinking thickness of films becomes unavoidable, especially in a planar type of FRAM devices. Due to reduction of the non-volatile charge before and after retention period, CSD did not seem to be recommendable for the films of thickness of 100 nm or less. Aside from retention issue, metal organic chemical vapor deposition (MOCVD) method has been tested for the fabrication of PZT capacitors as a future candidate of conformal deposition on a 3 dimensional capacitor structure. And, we observed much enhanced retention in the MOCVD-grown films of thickness of 100 nm.

We prepared the test capacitors by metal organic chemical vapor deposition (MOCVD). Our MOCVD apparatus was designed for uniform deposition of 6-inch wafer using showerhead technique, and liquid delivery system was utilized in order to control the input amount of the precursor solutions with ±1 % accuracy [8]. Tmhd-based organometallic compounds, such as Pb(tmhd)<sub>2</sub>, Zr(tmhd)<sub>2</sub>(O<sup>i</sup>Pr)<sub>2</sub> and Ti(tmhd)<sub>2</sub>(O<sup>i</sup>Pr)<sub>2</sub>, were used for metal-organic precursors, dissolved in octane solvent with a concentration of 0.05 Mole, respectively, and reserved separately in each ampule. Precursor solution was turned into the vapor state in the vaporizer heated at 235°C, and then delivered into the reactor. PZT films were grown on Ir/Ti (150/10nm) electrode, which is deposited at 200°C on 200 nm oxidized Si(100) wafer by DC magnetron sputtering. Growth rate was 5.5 ~ 6.0 nm/min within the Pb source supply ranges, resulting in a PZT film thickness of about 100 nm after the deposition of 18 minutes. For the measurement of electrical properties, top Ir/IrO<sub>2</sub>(70/30 nm) electrode was deposited by sputtering. Final etching process was identical with the previous case of CSD.

Figure 5 showed the distinctive retention properties obtained from MOCVD-grown films. For comparison with the cases of CSD, the best result from CSD films was given in the graph. Even the worst case in MOCVD which had the initial non-volatile charge less than 30  $\mu\text{C/cm}^2$ , remained over 50 % of non-volatile charge compared to the initial value after 100 hours. We are now optimizing the deposition condition in order to keep such a large non-volatile charge even after we complete the whole integration process. This dramatic change in retention between CSD and MOCVD in thin films of about 100 nm thickness suggests strongly to us that we should select another way of fabricating high-density FRAM, discarding a cheap and conventional deposition method.

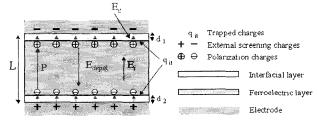

The inborn difference between CSD and MOCVD may come from the creation of the interfacial layer between the ferroelectric film and the metal electrode (Figure 6) as well as the defect density of the bulk film which was determined during the deposition-annealingcooling cycle. While the nucleation initiated from the bottom interface and the grains grew upward abruptly in the crystallization in CSD, MOCVD deposited atoms in vapor phase layer by layer and made the complete film slowly with the consistent heat supply. As a result, the films grown by CSD may have thicker interfacial passive layer with a lot of charge-trapped sites near the electrodes than the films grown by MOCVD. It should be noted that ozone-treated capacitors after a CSD process showed better retention characteristics because the treatment promoted enhanced surface oxidation to reduce the amount of oxygen-vacancies at the PZT-metal interfaces [9]. But, such post-treatment on the capacitors with thin films(< 100 nm) and thin electrodes(< 100 nm) can affect or even change the back-end processes and leave many factors in those processes to be optimized. So, it is still a hard problem to enhance retention properties with CSD-grown films.

Fig. 6. The schematic diagram of the interfacial layer inside the PZT films.

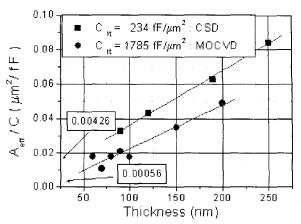

In order to confirm the existence of interfacial passive layer in our capacitors, we plotted the reciprocal of total capacitance with the thickness of the films as shown in Fig. 7. If there is an interfacial layer inside the capacitor, the total capacitance of the capacitor is,

$$1/C = 1/C_{it} + 1/C_{fe}$$

(1)

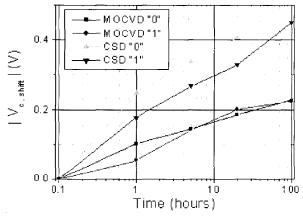

where Cit is the capacitance of the interfacial layer and C<sub>fe</sub> is the capacitance of the ferroelectric layer and depends on the thickness of the film. In Fig. 7, the extrapolation gave us the result that Cit was nearly 7.6 times larger in MOCVD-grown films than in CSDgrown films. There was an interesting report that if Cit is large, the induced field Eit inside the interfacial layer becomes small, so that either the injection of charges from the electrodes or the separation of positive and negative charges within the passive layer can be much reduced [10,11]. If the accumulated charges at the boundary between the ferroelectric layer and the passive layer, are small, the resultant internal field inside the ferroelectric layer becomes weak. In the opposite-state retention test, a precedent pulse reverses domains and set their polarization vectors opposite to the direction of the internal field, then some of reversed domains could switch back to the original state driven by the internal field during the delay time. This mechanism is explained explicitly in our former work [7]. In this manner, the opposite-state switching charge  $Q_{ossw}$  decreases and the opposite-state non-switching charge  $Q_{osns}$  increases, and finally the non-volatile charge  $P_{m'}$  decreases. Therefore, better retention behaviors in MOCVD-grown films must corresponds with less internal field induced inside the film during retention period. The magnitude of the internal field can be inferred from imprint (voltage shift) in the normal P-V hysteresis curves. In Fig. 8, the comparison of imprint in both CSD-grown films and MOCVD-grown films is suggested. The shift of coercive voltage is given in the absolute values. We could observe that imprint in CSD-grown films was much larger than in MOCVD-grown films. So, imprint may reflect both a sign of memory effect inside the capacitors and the decrease of non-volatile charge in opposite-state retention test. As seen in Fig. 9, the hysteresis curves showed larger depolarization at 0 V in accordance with the increase of imprint over the baking time.

Fig. 7. The reciprocal of the capacitance with thickness of the films was plotted in the graph. The extrapolation of the graph revealed that the capacitance of the interfacial passive layer was lager in the MOCVD-grown films than in the CSD-grown films

**Fig. 8.** The imprint over the baking time of the MOCVD-grown films and the CSD-grown films.

Fig. 9. The hysteresis curves over the baking time obtained from the capacitor written by "0" showed bigger depolarization in accordance with the increase of the imprint.

# III. CONCLUSIONS

The shrinkage of ferroelectric capacitors used for future high-density FRAM is becoming more challenging because many reliability issues still remain unsolved around the integration process. Based on our analysis on retention characteristics, CSD is not promising for fabricating thin planar devices. MOCVDgrown films showed much better performance on retention in thin films whose thickness is less than 100 nm. The difference in retention between both deposition methods seems to lie in the interfacial passive layer inside the capacitors. Retention loss in the opposite states can be closely related with imprint which is a sign of creation of the internal field. The internal field is correspondent with the accumulation of space charges at the interface, which was accelerated in CSD-grown films with both thicker interfacial layer and more defect density. Since discarding the inborn bad interface from CSD-grown films is much harder in thin films, an alternative way of deposition method should be recommended. MOCVD can be a good solution not only in planar devices but also in upcoming 3 dimensional devices due to its capability on conformal step coverage.

## REFERENCES

- [1] A. K. Sharma, Semiconductor Memories (IEEE, New York, 1997) p.387.

- [2] R. Ramesh, W. K. Chan, B. Wilkens, H. Gilchrist, T. Sands, J. M. Tarascon, V. G. Keramidas, D. K. Fork, J. Lee, and A. Safari, Appl. Phys. Lett. 61, 1537 (1992).

- [3] H. N. Al-Shareef, O. Auciello, and A. I. Kingon, J. Appl. Physics. 77, 2146 (1995).

- [4] J. M. Benedetto, R. A. Moore, and F. B. McLean, J. Appl. Phys. 75, 460 (1994).

- [5] T. Mihara, H. Yoshimori, H. Watanabe and C. A. Paz de Araujo, Jpn. J. Appl. Phys. 34, 2380 (1995).

- [6] R. Moazzami, N. Abt, Y. Nissan-Cohen, W. H. Shepherd, M. P. Brassington and C. Hu, *Dig. Tech. Pap. Symp.* (VLSI Technol., Oiso, Kanagawa, 1991) p.61.

- [7] B. S. Kang, Jong-Gul Yoon, D. J. Kim, T. W. Noh, T. K. Song, Y. K. Lee, J. K. Lee, and Y. S. Park, Appl. Phys. Lett. 82, 2124 (2003).

- [8] Youngsoo Park, June key Lee, Yong Kyun Lee, Ilsub Chung, Jung Soo Yong, and Young Ho Park, Integrated Ferroelectrics, 39, 231 (2001).

- [9] Kyu-Mann Lee, Hyeong-Geun An, June-Key Lee, Yong-

- Tak Lee, Sang-Woo Lee, Suk-Ho Joo, Sang-Don Nam, Kun-Sang Park, Moon-Sook Lee, Soon-Oh Park, Ho-Kyu Kang, and Joo-Tae Moon, Jpn. J. Appl. Phys. 40, 4979 (2001).

- [10] 10. M. Grossmann, O. Lohse, D. Bolten, U. Boettger, T. Schneller and R. Waser, J. Appl. Phys. 92, 2680 (2002).

- [11] 11. M. Grossmann, O. Lohse, D. Bolten, U. Boettger, and R. Waser, J. Appl. Phys. 92, 2688 (2002).

Sangmin Shin is a senior researcher in Materials and Devices

Laboratory in Samsung Advanced Institute of Technology. He received the Ph.D. degree in Physics from Seoul National University in 2002 with his study on ferroelectric and semiconductor devices by electrostatic force microscope. He had been working in Park Scientific Instruments Advanced Corporation from

2000 to 2001 and contributed the development of high-speed and high-precision atomic force microscope as a part of work in National Research Laboratory. Since he joined Samsung in 2002, he has been working in the development of ferroelectric random access memory(FRAM), especially in enhancing the reliability of the devices. His research interests include nanofabrication and nano-characterization with scanning probe microscopes and the development of storage and memory devices with smart, electric and magnetic materials.

Mirko Hofmann graduated from University of Technology Aachen (RWTH) in Germany in 1999. He is expected to get

the Diplom of Engneering in Electrical Engineering in RWTH in 2003. He has experienced different processes under clean-room conditions, fabrication of testing sensors, and assembling microstructures with PZT-cantilevers for piezoelectric devices. He worked as an intern researcher in Samsung Advanced

Institute of Technology in 2002 and assisted the characterisation of retention properties of PZT capacitors which were fabricated at different conditions.

Yong Kyun Lee received his BS and MS degree in Chemistry from Inha University in Korea in 1998 and 2000 respectively. Since he joined Samsung Advanced Institute of Technology (SAIT) in 1999, his research has been focused on the ferroelectric integration to date. He has joined the development

project of world first 32M FRAM.

June-Mo Koo is a researcher in Materials and Devices Laboratory in Samsung Advanced Institute of Technology. He received his master degree in Material Engineering from Kookmin University in Korea in 2002 with his study on ferroelectric and semiconductor devices. Since he joined

Samsung in 2002, he has been focused on PZT MOCVD Process for high-density FRAM application.

Choong-Rae Cho earned his BS and MS degree in physics at the department of Physics Education in Seoul National University in Korea in 1990 and 1992 respectively, and Ph. D degree in Physics from Royal Institute of Technology, Stockholm Sweden in 2001. He has mainly been involved in projects

concerning growth, characterization, and applications of novel ferroelectric thin films by PLD and MOCVD technique. He has joined Samsung Advanced Institute of Technology (SAIT) in 2002.

June Key Lee received his BS and MS degree in Chemistry from Korea Advance Institute of Technology (KAIST) in Korea in 1990 and 1992 respectively, and Ph.D degree in Material Science and Engineering from Virginia Tech in USA in 1999. Since he joined Samsung Advanced Institute of

Technology (SAIT) in 1992, his research has been focused on the ferroelectric integration to date. He has joined the development project of world first 1T-1C 64K FRAM, 4M FRAM, and 32M FRAM.

Young Soo Park received his BS and MS degree in Material Science and Engineering from Korea Univ. and Korea Advance Institute of Technology (KAIST) in Korea in 1986 and 1988 respectively, and Ph.D degree in Material Science and Engineering from Korea Advance Institute of Technology

(KAIST) in 2000. Since he joined Samsung Advanced Institute of Technology (SAIT) in 1991, he has been studied on the DLC films, diamond films and poly-Si TFT. He started FRAM research in 1995. He has joined the development project of world first 1T-1C 64K FRAM, 4M FRAM, and 32M FRAM. He is now involved in the development of low temperature MOCVD PZT deposition for high density FRAM application.

Kyu Mann Lee received his BS and MS degree in Materials Science and Engineering from Korea Advance Institute of Technology (KAIST) in Korea in 1991 and from Pohang University of Science and Technology (POSTECH) in Korea in 1993, respectively. He received the Ph.D

degree in Materials Science and Engineering from POSTECH in Korea in 1997. After he worked as a post-doctoral researcher for 2 years at Material Research Center in North Carolina State University in USA and in POSTECH in Korea, he joined the process development team of semiconductor R&D division in Samsung Electronics. His research has been focused on the ferroelectric integration and involved in the development project of 4M FRAM and 32M FRAM.

Yoon-Jong Song is a senior researcher in Advanced Technology Development Team in Samsung Electronics Co., Ltd., kyunggido, Korea since 1998. He received the BS degree in Materials Engineering from Hanyang University, and the Ph.D. degree in Materials Engineering and Science from Virginia

Polytechnic Institute and State University, in 1993 and 1998, respectively. He had been involved in developing 64kb, 4Mb, 32Mb FRAM devices. His current research interests include process integration and device reliability.